Изобретение относится к. блокировочным и предохранительным устройствам, предназначено для обнуления интегрирующего конденсатора аналоговых интеграторов и может быть использовано в устройствах автоматики и вычислительной техники.

Цель изобретения - повышение точности за счет устранения погрешности обнуления при включении и выключении источников 1штания.

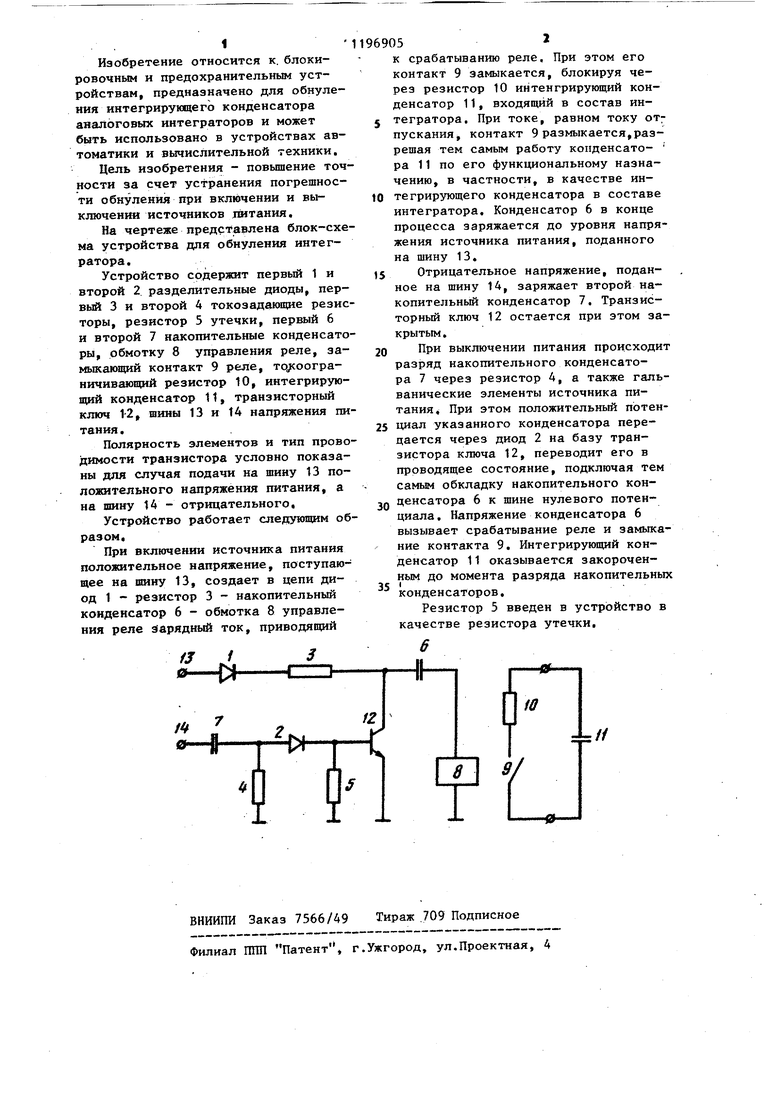

На чертеже представлена блок-схе ма устройства для обнуления интегратора.

Устройство содержит первый 1 и второй 2 разделительные диоды, первый 3 и второй 4 токозадакицие резис торы, резистор 5 утечки, первый 6 и второй 7 накопительные конденсато ры, обмотку 8 управления реле, замыкающий контакт 9 реле, то соограничивающий резистор 10, интегрирующий конденсатор 11, транзисторный ключ 1-2, шины 13 и 14 напряжения пи тания.

Полярность элементов и тип прово димости транзистора условно показаны для случая подачи на шину 13 положительного напряжения питания, а на шину 14 - отрицательного.

Устройство работает следующим об разом.

При включении источника питания положительное напряжение, поступающее на шину 13, создает в цепи диод 1 резистор 3 - накопительный конденсатор 6 - обмотка 8 управления реле зарядный ток, приводящий

1196905

к срабатыванию реле. При этом его контакт 9 замыкается, блокируя через резистор 10 интенгрирующий конденсатор 11, входящий в состав интегратора. При токе, равном току от пускания, контакт 9 размыкается,разрешая тем самым работу копденсатора 11 по его функциональному назначению, в частности, в качестве интегрирующего конденсатора в составе интегратора. Конденсатор 6 в конце процесса заряжается до уровня напряжения источника питания, поданного на шину 13,

Отрицательное напряжение, поданное на шину 14, заряжает второй накопительный конденсатор 7. Транзисторный ключ 12 остается при этом закрытым ,

При выключении питания происходит разряд накопительного конденсатора 7 через резистор 4, а также гальванические элементы источника питания При этом положительный потенциал указанного конденсатора передается через диод 2 на базу транзистора ключа 12, переводит его в проводящее состояние, подключая тем самым обкладку накопительного конденсатора 6 к шине нулевого потенциала , Напряжение конденсатора 6 вызывает срабатывание реле и замыкание контакта 9, Интегрирующий конденсатор 11 оказывается закороченным до момента разряда накопительных конденсаторов.

Резистор 5 введен в устройство в качестве резистора утечки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1979 |

|

SU824226A1 |

| Устройство для определения средневзвешенного значения функции | 1976 |

|

SU636626A1 |

| Устройство для включения реле при пониженном напряжении питания | 1981 |

|

SU957311A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИЗОЛЯЦИИ АККУМУЛЯТОРНОЙ БАТАРЕИ ЭЛЕКТРИЧЕСКОГО ТРАНСПОРТА | 1990 |

|

RU2010735C1 |

| Устройство для дистанционного управления | 1990 |

|

SU1783563A1 |

| Интегратор с запоминанием | 1984 |

|

SU1228122A1 |

| ИНТЕГРАТОР С ОБНУЛЕНИЕМ | 1991 |

|

RU2015556C1 |

| Импульсный генератор инфранизкой частоты | 1979 |

|

SU793303A1 |

| Генератор импульсов переменной амплитуды | 2017 |

|

RU2647700C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕЛЕ | 1988 |

|

RU2017330C1 |

УСТРОЙСТВО ДЛЯ ОБНУЛЕНИЯ ИНТЕГРАТОРА, содержащее последовательно соединенные разрядный резистор и замыкающий контакт реле, параллельно которым включен интегрирующий конденсатор интегратора, обмотка управления реле подключена одним выводом к шине нулевого потенциала, и шины напряжения питания, отличающееся тем, что, с .целью повьпиения точности за счет устранения погрешности обнуления при включении и выключении источников питания, в него введены два раздеI- uill лительных диода, транзисторный ключ, два токозадающих резистора, резистор утечки и два накопительных конденсатора, первая обкладка первого накопительного конденсатора подключена к второму выводу обмотки управления реле, а вторая обкладка через последовательно включенные первый токозадающий резистор и первый разделительный диод соединена с первой шиной нап1)яжения питания, второй накопительный конденсатор и второй разделительный диод соединены последовательно и включены между второй шиной напряжения питания и управляющим входом транзисторного ключа, включенного между второй обел кладкой первого накопительного конденсатора и шинной нулевого потенциала, соединенной через резистор утечки с управлякицим входом транзисторного ключа и через второй токозадающий резистор с общим высо водом второго накопительного конденсатора и второго разделительного О5 диода. СО

| Щербаков В.И., Грездов Г.И | |||

| Электронные схемы на операционных усилителях, - Киев, Техника, 1983, с.141 | |||

| Анисимов Б,В., Голубкин В.Н | |||

| Аналоговые вычислительные машины.М.: Высшая школа, 1971, с.161. |

Авторы

Даты

1985-12-07—Публикация

1984-06-15—Подача