Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано в системах автоматического регулирования, аналоговых вычислительных машинах, генераторах сигналов специальной формы.

Интегратор является обязательным элементом аналоговых вычислительных машин, широко используется для построения систем автоматического регулирования, при разработке генераторов специальной формы и др. В интеграторе наряду с выполнением функции интегрирования предусматривается возможность его обнуления. Интеграторы с обнулением обычно выполняются на дифференциальных усилителях с емкостной отрицательной обратной связью и с коммутационными элементами, обеспечивающими обнуление интегратора посредством разряда конденсатора емкостной отрицательной обратной связи. Кроме обеспечения возможности обнуления к интегратору предъявляются требования по точности при изменении напряжения выходного сигнала в широких пределах. При использовании интеграторов с постоянной времени несколько секунд и более возникает проблема обеспечения точности. В частности, на точность существенным образом начинают влиять цепи обнуления интегратора.

Например, описанный в [1] интегратор с обнулением содержит входные резисторы, дифференциальный усилитель, в цепи отрицательной обратной связи усилителя накопительный конденсатор и переключатель, выводы контактов которого соединены с выводами конденсатора, а вход управления является соответствующим входом интегратора с обнулением.

Сигнал, подлежащий интегрированию, поступает на сигнальный вход интегратора с обнулением. Напряжение входного сигнала преобразуется на входном резисторе в ток, который интегрируется на конденсаторе обратной связи усилителя. Для минимизации ошибки интегрирования конденсатор выбирается с максимальным значением сопротивления утечки. Однако такой интегратор с обнулением имеет низкую точность.

Наиболее близким к предлагаемому является устройство [2], которое содержит дифференциальный усилитель, неинвертирующий вход которого соединен с шиной нулевого потенциала устройства, а инвертирующий вход - с выходом устройства через накопительный конденсатор, причем вход устройства через масштабный резистор соединен с инвертирующим входом дифференциального усилителя, а обкладки накопительного конденсатора через первый и второй ключи соединены с шиной нулевого потенциала.

Предлагаемая схема интегратора с обнулением позволяет расширить диапазон входных напряжений за счет того, что переключатели, обеспечивающие режим обнуления, не оказывают дестабилизирующего воздействия при работе устройства в режиме интегрирования.

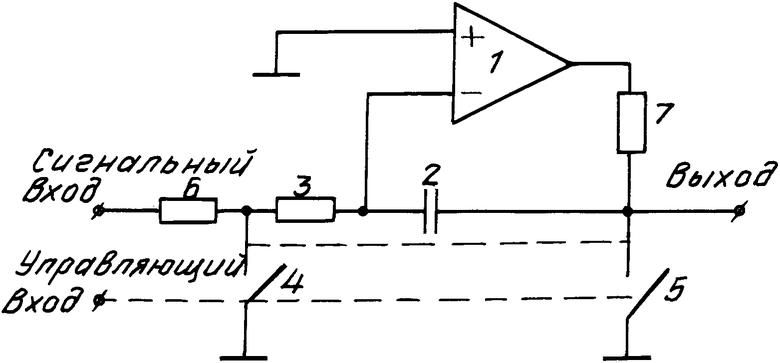

На чертеже приведена структурная схема предлагаемого интегратора с обнулением.

Интегратор с обнулением содержит дифференциальный усилитель 1, накопительный конденсатор 2, масштабный резистор 3, ключи 4 и 5, а также масштабный резистор 6 и ограничительный резистор 7.

Неинвертирующий вход усилителя 1 соединен с шиной нулевого потенциала интегратора, а инвертирующий вход - с накопительным конденсатором 2 и масштабным резистором 3, второй вывод которого соединен с первым контактом ключа 4. Второй контакт ключа 4 соединен с шиной нулевого потенциала интегратора, с которой также соединен первый контакт ключа 6, второй контакт которого соединен с вторым выводом накопительного конденсатора 2 и выходом интегратора. Входы управления ключей 4 и 5 объединены и являются управляющим входом интегратора, сигнальный вход которого соединен с вторым выводом резистора 3 и первым контактом ключа 4 через масштабный резистор 6, а выход усилителя 1 соединен с вторым выводом накопительного конденсатора 2, вторым контактом ключа 5 и выходом интегратора через ограничительный резистор 7.

Интегратор работает следующим образом.

На сигнальный вход интегратора с выхода генератора напряжения входного сигнала (на чертеже не показан) поступает напряжение входного сигнала, под действием которого протекает ток заряда конденсатора 2. Этот ток протекает через резистор 6, масштабный резистор 3, конденсатор 2, резистор 7 и замыкается на шину нулевого потенциала интегратора через эквивалентное выходное сопротивление усилителя 1, которым можно пренебречь ввиду его малости. При этом выходное напряжение интегратора является интегральной функцией от напряжения входного сигнала, а постоянная времени интегратора определяется выражением

τ = Rвх ˙С2 = (R6 + R3) ˙С2, где С2 - емкость конденсатора 2;

R3 - сопротивление резистора 3;

R6 - сопротивление резистора 6.

Необходимо, чтобы емкости накопительных конденсаторов интегратора и устройства-прототипа были равны, а сумма сопротивлений резисторов 3 и 6 интегратора равнялась сопротивлению резистора 3 устройства-прототипа. Резистор 7 на передаточную характеристику не влияет, так как его сопротивление включено не в цепь отрицательной обратной связи интегратора, а в выходную цепь дифференциального усилителя 1, что эквивалентно увеличению его выходного сопротивления, на котором происходит падение напряжения, которое несколько снижает диапазон выходных напряжений устройства. Так, например, для интегратора, выполненного на дифференциальном усилителе типа 544УД1А с диапазоном выходных напряжений в пределах от минус 10 (не более) до 10 В (не менее), при напряжении входного сигнала 10 В, сумме сопротивлений резисторов 3 и 6, равной 10 мОм, и сопротивлении резистора 7 5 кОм падение напряжения на резисторе 7 составит всего 50 мВ, т.е. 0,5% от диапазона выходных напряжений. В большинстве случаев этим падением напряжения можно пренебречь.

В предложенном интеграторе отсутствие в цепи заряда накопительного конденсатора 2 контактов как источника нестабильности позволяет избежать ограничений на напряжение входного сигнала.

Обнуление интегратора осуществляется посредством разряда конденсатора 2 через резистор 3, для чего ключи 4 и 5 устанавливаются в положение, при котором их контакты (первый и второй) оказываются замкнутыми. В этом случае замыкается цепь разряда конденсатора 2 через резистор 3, замкнутые контакты ключей 4 и 5 и шину нулевого потенциала интегратора.

В режиме обнуления резисторы 6 и 7 предохраняют от такого замыкания выход генератора напряжения входного сигнала и выход усилителя 1 соответственно.

При сравнении предлагаемого технического решения с прототипом выявлен следующий положительный эффект.

Применение в устройстве-прототипе переключателей, обеспечивающих разряд накопительного конденсатора через резистор, соединенный с инвертирующим входом усилителя, позволяет обеспечить высокую точность интегрирования. Однако наличие во входной цепи переключателя приводит к ограничению диапазона напряжений входного сигнала, при котором устройство сохраняет работоспособность, что является недостатком прототипа.

В предлагаемом интеграторе применение ограничителей тока и изменение схемы соединения ключей позволяют расширить допустимый диапазон входного напряжения вплоть до нулевого значения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор с обнулением | 1989 |

|

SU1674180A1 |

| Интегратор | 1984 |

|

SU1161963A1 |

| Интегратор | 1979 |

|

SU834715A1 |

| ИНТЕГРАТОР | 1990 |

|

RU2020580C1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Интегратор | 1983 |

|

SU1198546A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Интегратор | 1978 |

|

SU748439A1 |

| Интегратор | 1980 |

|

SU928369A1 |

Интегратор с обнулением относится к автоматике и аналоговой вычислительной технике и может быть использован в системах автоматического регулирования, аналоговых вычислительных машинах, генераторных сигналов специальной формы. Сущность изобретения: интегратор содержит дифференциальный усилитель 1, накопительный конденсатор 2, два масштабных резистра 3, 6, два ключа 4, 5, ограничительный резистор 7. 1 ил.

ИНТЕГРАТОР С ОБНУЛЕНИЕМ, содержащий дифференциальный усилитель, неинвертирующий вход которого соединен с шиной нулевого потенциала, а инвертирующий вход - с первой обкладкой накопительного конденсатора, информационный вход интегратора соединен с первым выводом первого масштабного резистора, вторая обкладка накопительного конденсатора соединена с выходом интегратора и через первый ключ с шиной нулевого потенциала, второй ключ, первый вывод которого соединен с шиной нулевого потенциала, а второй - с вторым выводом первого масштабного резистора, управляющий вход интегратора подключен к управляющим входам ключей, отличающийся тем, что выход дифференциального усилителя через ограничительный резистор соединен с второй обкладкой накопительного конденсатора, первая обкладка которого через второй масштабный резистор соединена с вторым выводом второго ключа.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Смолов В.Б | |||

| Функциональные преобразователи информации | |||

| Л., с.163. | |||

Авторы

Даты

1994-06-30—Публикация

1991-02-15—Подача