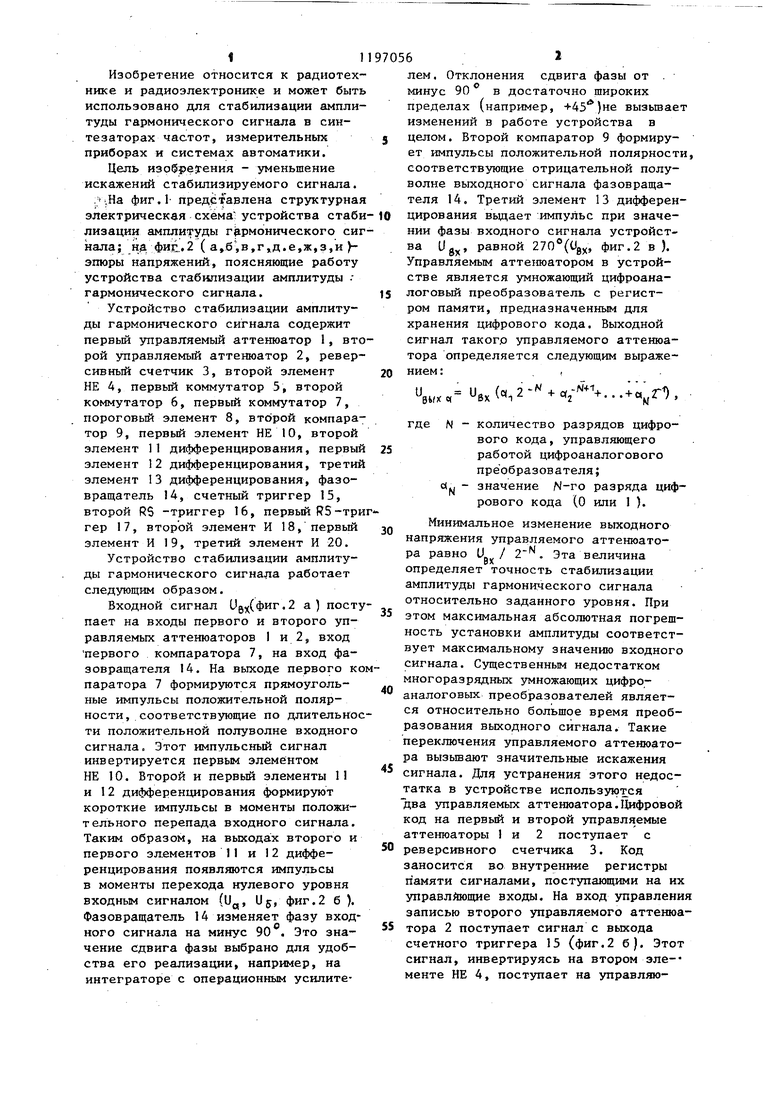

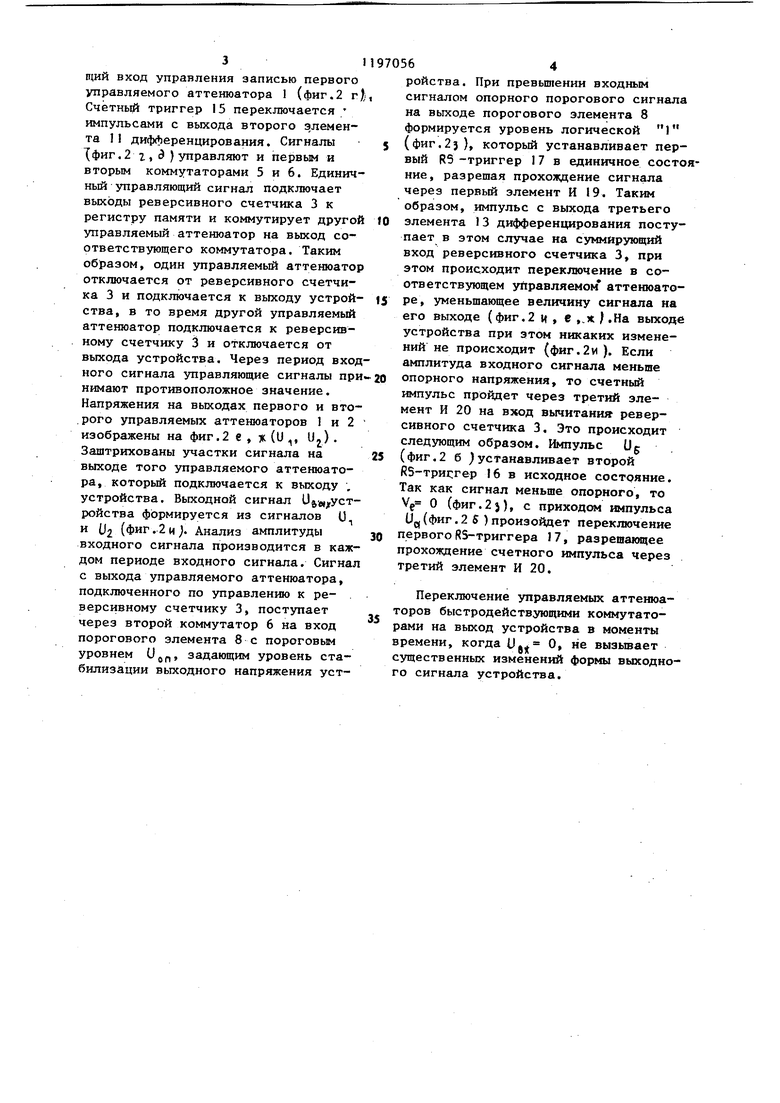

Изобретение относится к радиотех нике и радиоэлектронике и может быт использовано для стабилизации ампли туды гармонического сигнала в синтезаторах частот, измерительных приборах и системах автоматики. Цель изоб1ретения - уменьшение искажений стабилизируемого сигнала. .vHa фиг.1 представлена структурна электрическая схема- устройства стаби лизации амплитуды гармонического сиг нала; н.а фиг.2 ( а,б,в,.е,ж,з,и )эпюры напряжений, поясняющие работу устройства стабилизации амплитуды гармонического сигнала. Устройство стабилизации амплитуды гармонического сигнала содержит первый управляемый аттенюатор 1, вто рой управляемый аттенюатор 2, реверсивный счетчик 3, второй элемент НЕ А, первый коммутатор 5, второй коммутатор 6, первый коммутатор 7, пороговьй элемент 8, второй компара тор 9, первый элемент НЕ 10, второй элемент 11 дифференцирования, первый элемент 12 дифференцирования, третий элемент 13 дифференцирования, фазовращатель 14, счетный триггер 15, второй R5 -триггер 16, первый R5-три гер 17, второй элемент И 18, первый элемент И 19, третий элемент И 20. Устройство стабилизации амплитуды гармонического сигнала работает следующим образом. Входной сигнал ид(фиг.2 а) посту пает на входы первого и второго управляемых аттенюаторов I и 2, вход первого компаратора 7, на вход фазовращателя 14. На выходе первого ко паратора 7 формируются прямоугольные импульсы положительной полярности, соответствующие по длительнос ти положительной полуволне входного сигнала. Этот импульсный сигнал инвертируется первым элементом НЕ 10. Второй и первый элементы 11 и 12 дифференцирования формируют короткие импульсы в моменты положительного перепада входного сигнала. Таким образом, на выходах второго и первого эл.ементов 11 и 12 дифференцирования появляются импульсы в моменты перехода нулевого уровня входным сигналом (Ug, 1)5 Фиг.2 б ). Фазовращатель 14 изменяет фазу входного сигнала на минус 90°. Это значение сдвига фазы выбрано для удобства его реализации, например, на интеграторе с операционным усилите6лем. Отклонения сдвига фазы от . минус 90 в достаточно широких пределах (например, вызьшает изменений в работе устройства в целом. Второй компаратор 9 формирует импульсы положительной полярности, соответствующие отрицательной полуволне выходного сигнала фазовращателя 14. Третий элемент 13 дифференцирования вьщает импульс при значении фазы входного сигнала устройства Ug, равной (tJg, фиг. 2 в). Управляемым аттенюатором в устройстве является умножающий цифроаналоговый преобразователь с регистром памяти, предназначенным для хранения цифрового кода. Выходной сигнал такого управляемого аттенюатора определяется следующим выражением:. , Vc, uexK2..... где N - количество разрядов цифрового кода, управляющего работой цифроаналогового преобразователя; с(| - значение N-ro разряда цифрового кода (о или 1 ). Минимальное изменение выходного напряжения управляемого аттенюатора равно Ug / 2, Эта величина определяет точность стабилизации амплитуды гармонического сигнала относительно заданного уровня. При этом максимальная абсолютная погрешность установки амплитуды соответствует максимальному значению входного сигнала. Существенным недостатком многоразрядных умножающих цифроаналоговых преобразователей является относительно большое время преобразования выходного сигнала. Такие переключения управляемого аттенюатора вызьшают значительные искажения сигнала. Для устранения этого недостатка в устройстве используются два управляемых аттенюатора.Цифровой код на первый и второй управляемые аттенюаторы 1 и 2 поступает с реверсивного счетчика 3. Код заносится во внутренние регистры памяти сигналами, поступающими на их управлйющие входы. На вход управления записью второго управляемого аттенюатора 2 поступает сигнал с выхода счетного триггера 15 (фиг.2 б). Этот сигнал, инвертируясь на втором зле-менте НЕ 4, поступает на управляю31щий вход управления записью первого управляемого аттенюатора 1 (фиг.2 rj Счётный триггер 15 переключается импульсами с выхода второго элемента II дифференцироваиия. Сигналы фиг.2 г )управляют и первым и вторым коммутаторами 5 и 6. Единичный управляющий сигнал подключает выходы реверсивного счетчика 3 к регистру памяти и коммутирует другой управляемый аттенюатор на выход соответствующего коммутатора. Таким образом, один управляемый аттенюатор отключается от реверсивного счетчика 3 и подключается к выходу устройства, в то время другой управляемый аттенюатор подключается к реверсивному счетчику 3 и отключается от выхода устройства. Через период вход ного сигнала управляющие сигналы при нимают противоположное значение. Напряжения на выходах первого и второго управляемых аттенюаторов 1 и 2 изображены на фиг.2 е, ж(U , U). Заштрихованы участки сигнала на выходе того управляемого аттенюатора, который подключается к выходу , устройства. Выходной сигнал U et ycTройства формируется из сигналов (J и U2 (фиг.2 и J. Анализ амплитуды входного сигнала производится в каждом периоде входного сигнала. Сигнал с выхода управляемого аттенюатора, подключенного по управлению к реверсивному счетчику 3, поступает через второй коммутатор 6 на вход порогового элемента 8с пороговым уровнем Ugf,, задающим уровень стабилизации выходного напряжения уст64ройства. При превышении входным сигналом опорного порогового сигнала на выходе порогового элемента 8 формируется уровень логической 1 (фиг.2}), который устанавливает первый R5 -триггер 17 в единичное состояние, разрещая прохозвдение сигнала через первый элемент И 19. Таким образом, импульс с выхода третьего элемента 13 дифференцирования поступает в этом случае на суммирующий вход реверсивного счетчика 3, при этом происходит переключение в соответствующем управляемом аттенюаторе, уменьшающее величину сигнала на его выходе (фиг.2 ц , е ,.х КНа выходе устройства при этом никаких изменений не происходит (фиг.2и ). Если амплитуда входного сигнала меньше опорного напряжения, то счетный импульс пройдет через третий элемент И 20 на вход вычитаншг реверсивного счетчика 3, Это происходит следующим образом. Импульс (Jg (фиг.2 б устанавливает второй К5-три1:гер 16 в исходное состояние. Так как сигнал меньше опорного, то Vp О (фиг.2}), с приходом импульса ил(фиг.2S)произойдет переключение первогоRS-триггера 17, разрешакицее прохождение счетного импульса через третий элемент И 20. Переключение управляемых аттенюаоров быстродействующими коммутатоами на выход устройства в моменты ремени, когда iJ. О, не вызьгоает ущественных изменений формы выходноо сигнала устройства.

щрг miiijr

Uf.t

xfirnTTh

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля амплитуды гармонического сигнала | 1985 |

|

SU1337783A1 |

| Устройство для измерения гистерезиса @ характеристик | 1985 |

|

SU1247797A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЕВИАЦИИ ЧАСТОТЫ | 1998 |

|

RU2138828C1 |

| Устройство автоматической регулировки коэффициента передачи | 1982 |

|

SU1046909A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| Устройство сравнения напряжений | 1986 |

|

SU1420656A2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ЗАТУХАНИЯ МЕЖДУ АНТЕННАМ | 1995 |

|

RU2127889C1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОТНОСИТЕЛЬНЫХ УРОВНЕЙ ПОБОЧНЫХ КОЛЕБАНИЙ РАДИОПЕРЕДАТЧИКОВ | 1990 |

|

RU2033618C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗЫ РАДИОСИГНАЛА | 1992 |

|

RU2050552C1 |

УСТРОЙСТВО СТАБИЛИЗАЦИИ АМПЛИТУДЫ ГАРМОНИЧЕСКОГО СИГНАЛА, содержащее первый управляемый аттенюатор, вход которого является входом устройства, реверсивный счетчик , выходы разрядов которого соединены с соответствующими управляющими входами первого управляемого аттенюатора, пороговый элемент, первый элемент И, выход которого соединен с суммирующим входом реверсивного счетчика, соединенные последовательно первый компаратор первый элемент НЕ, первый элемент дифференцирования, второй элемент И, первый RS-триггер и третий элемент И, выход которого соединен с г вычитающим входом реверсивного счетчика, соединенные последовательно второй элемент дифференцирования,, вход которого соединен с выходом первого коммутатора, и второй | 5-триггер, выход которого соединен с другим входом второго элемента И, выход порогового элемента соединен с другими входами первого и второго RS-триггеров, другой выход первого RS-триггера соединен с входом первого элемента И, о т личающееся тем, что, с целью уменьшения искажений стабилизируемого сиг.нала, в него введены первый коммутатор, вход которого соединен с вькодом первого управляемого аттенюатора, выполненного в виде умножающего цифроаналогового преобразователя с регистром памяти, а выход является выходом устройства соединенные последовательно второй управляемый аттенюатор, выполненный в виде умножающего цифроаналогового преобразователя с регистром памяти, вход которого соединен с входом устройства, а управляющиевходы соединены с выходами соответствукяцих разрядов реверсивного счетчика, и второй коммутатор, выход которого соединен с входом порогового элемента, соединенные последовательно фазовращатель, вход которого соединен с (Л входом первого компаратора и входом устройства, второй компаратор и третий элемент дифференцирования, выход которого соединен с другими входами первого и третьего элементов И, соединенные последовательно счетный триггер, вход которого соединен со с выходом второго элемента дифференцирования, а выход соединен с входом о управления записью кода в регистр СП памяти второго управляемого аттенюОд атора, и управляющим входом первого коммутатора, и второй элемент НЕ, выход которого соединен с управляю- щим входом второго коммутатора и входом управления записью кода в регистр памяти первого управляемого аттенюатора, другой вход первого коммутатора соединен с выходом второго управляемого аттенюатора, а другой вход второго коммутатора соединен с выходом первого управляемого аттенюатора.

| Устройство автоматической регулировки коэффициента передачи | 1982 |

|

SU1046909A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-12-07—Публикация

1984-07-30—Подача