1

Изобретение относится к измерительной технике и может быть использовано для измерения амплитудного спектра периодических сигналов, в частности высших гармоник напряжений промыш- ленной электрической сети.

Цель изобретения - повышение быстродействия и точности измерений.за счет реализации цифрового управления величинами приращений амплитуды и фа- зы генератора компенсирующего сигнала при сохранении требуемого качества переходных процессов регулирования .

12

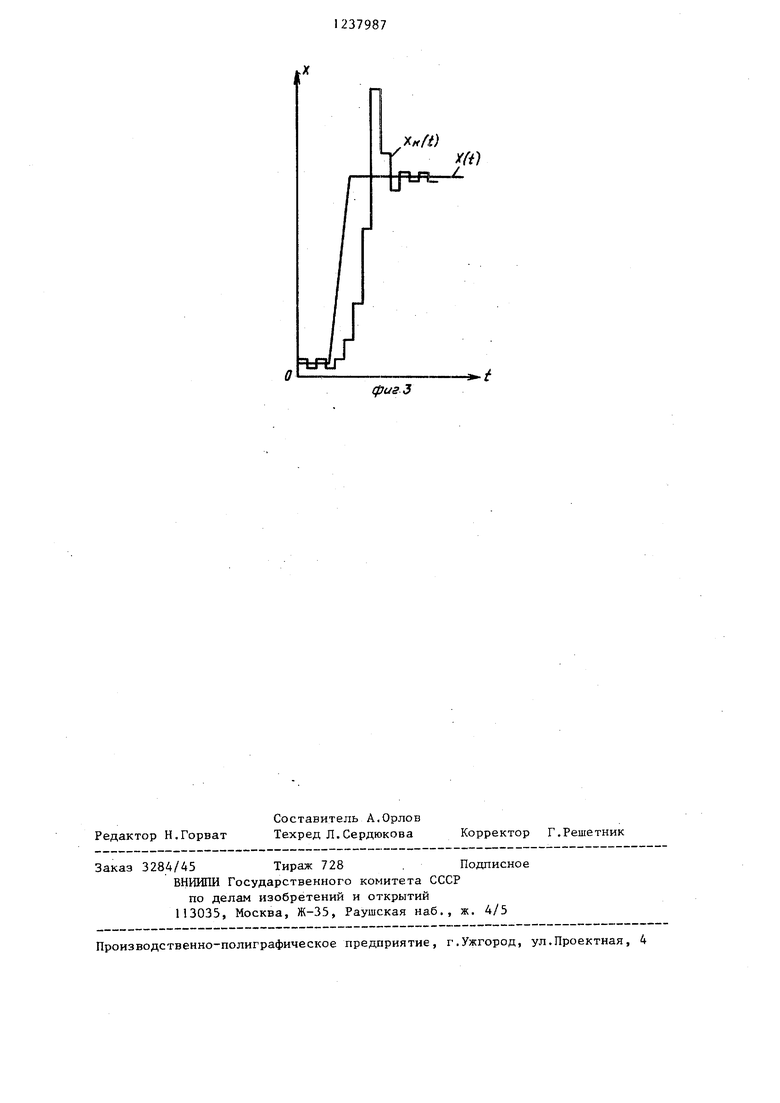

На фиг.1 приведена структурная схе- 5 ра 27 компенсирующего сигнала, блока

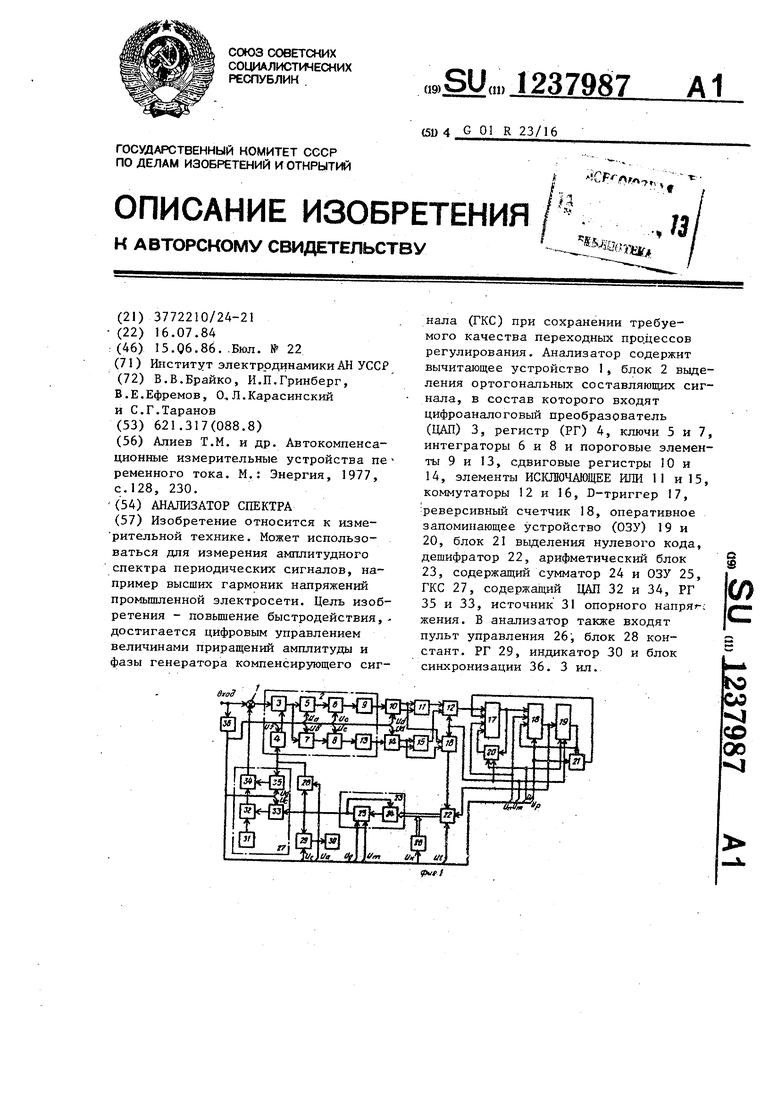

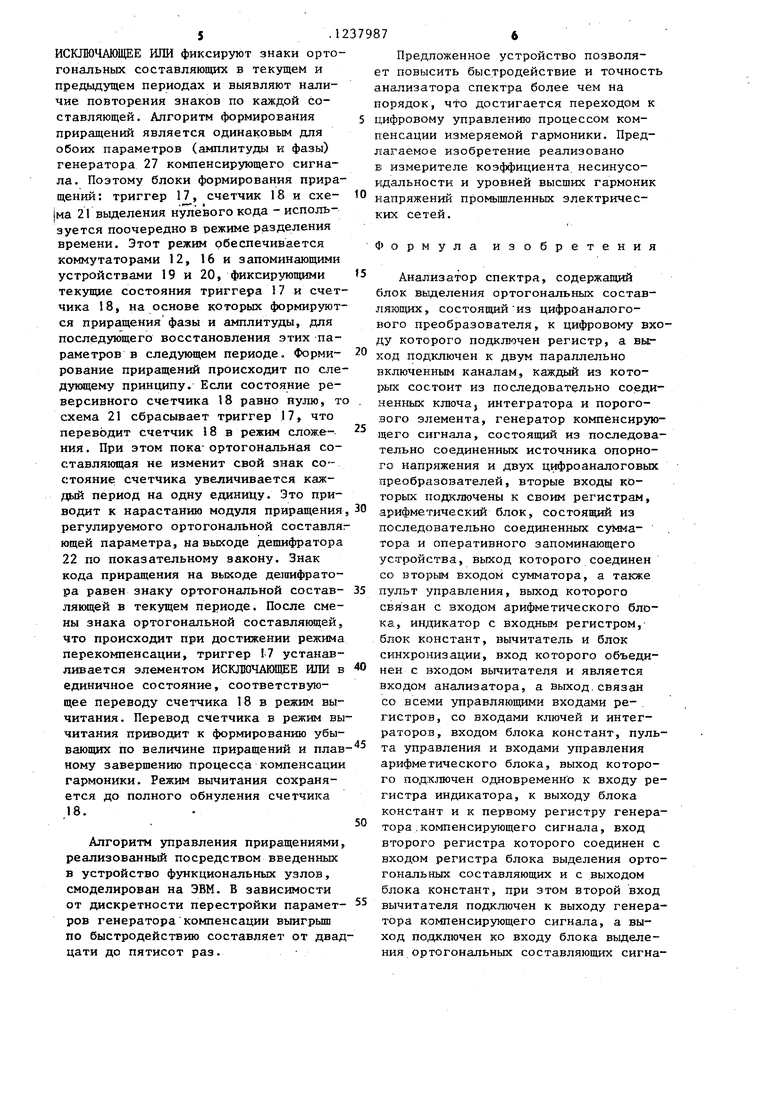

схема предлагаемого анализатора спектра; на фиг.2 - временная диаграмма управляющих импульсов блока синхронизации; на фиг.З - принцип фо формирования приращения переменной величины.

Анализатор спектра содержит соединенное последовательно со входом вычитающее устройство 1, блок 2 выделения ортогональных составляющих сигнала, содержащий цифроаналоговый пре образователь 3 с регистром 4 на цифровом входе и подключенные к выходу преобразователя 3 последовательно со .единенные юпоч 5 с интегратором 6 и ключ 7 с интегратором 8. Выход вычитающего устройства 1 соединен с аналоговым входом преобразователя 3. К выходу интегратора 6 подключены последовательно соединенные пороговый элемент 9, сдвиговый регистр 10, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11 и двухвходо- вый коммутатор 12. К выходу интегратора 8 подключены последовательно соединенные пороговый элемент 13, сдвиговый регистр 14 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15, выход которого соединен со вторым входом коммутатора 12. Помимо этого анализатор содержит подключенный к выходам сдвиговых регистров 10 и 14 двухвходовой коммутатор 16, К выходу коммутатора 12 подключены каскадно соединенные)- триггер 17, реверсивный счетчик 18 с оперативным запоминающим устройством 19, предназначенным для регенерации состояния счетчика, элемент

20памяти, предназначенный для регенерации состояния триггера 17. Для этого вход и выход элемента 20 памяти соединены соответственно с выходом и D-входом триггера 17., Схема

21выделения нулевого кода включена

5

7987. 2

между выходом запоминающего устройства 19 и входом сброса триггера 17. Выход реверсивного счетчика 18 соединен также с дешифратором 22, второй вход которого подключен к выходу коммутатора 16, Анализатор также содержит арифметический блок 23, состоящий из сумматора 24 с оперативным запоминающим устройством 25 на выходе. Второй вход сумматора 24 подключен посредством общей шины к выходам дешифратора 22 и пульса 26 управления.. Выход запоминающего устройства 25 соединен со входами тенерато

5

5

28 констант и регистра 29 с индикатором 30 на выходе. Генератор 27 компен сирующего сигнала содержит последовательно соединенные источник 31 опорного напряжения, цифроаналоговый преобразователь 32 с регистром 33 на цифрО зом входе и цифроаналоговый преобразователь 34 с регистром 35. Вход регистра 33 является входом регулировки амплитуды и подключен к выходу запоминающего устройства 25. Выход цифроаналогового преобразователя 34 является выходом генератора 27 и подключен ко второму входу вычитающего 0 устройства 1. Выход блока 28 констант подключен ко входам регистров 4 и 35. Для синхронизации узлов анализатора с периодом входного сигнала предназначен связанный со входом блок 36 синхронизации. Выходы блока 36 подключены ко входам регистров 4, 10, 14, 29, 33 и 35 кл:эчей 5 и 7, интеграторов 6 и 8, коммутаторов 12 и 16, триггера 17, счетчика 18, запоминающих уст|)ойств 19, 25 схемы 21 выдех ения нулевого кода элемента 20 пг1мяти дешифратора 22, пульта 26 упра1шения и блока 28 констант. Циф- роангшоговые преобразователи 3, 32 и 34 являются типовыми элементами и используются в качестве перемиожи- телей, один вход которых цифровой, а второй аналоговый. Реверсивный счетчик 18 имеет входы управления реверсом, тактировки, информационные входы и вход управления записью кодов по информационным входам, подключенные соответственно к выходам триггера 17, блока 36 синхронизации, оперативного запоминающего устройства 19 и блока 36 синхронизации.

Схема 21 выделения нулевого кода представляет собой стробирующий деS

0

5

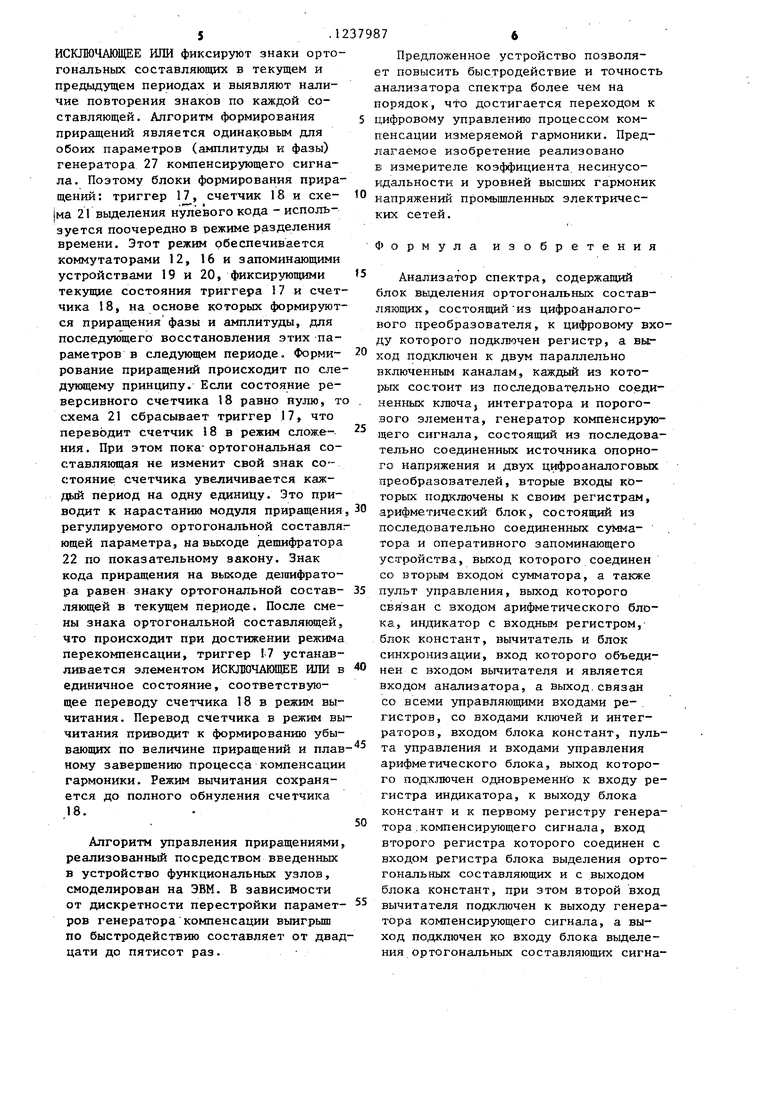

шифратор нулевого кода запоминающего устройства 19. Дешифратор 22 таблица показательной,функции с основанием степени равным двум. Показатель степени этой таблицы задается кодом реверсивного счетчика 18. В зависимости от выходного сигнала ком мутатора 16 дешифратор 22 формирует приращение положительной или отрицательной величины. Арифметический блок 23 реализован на основе накапливающего сумматора, образованного сумматором.24 и запоминающим устройством 25. При поступлении импульса записи на соответствующий вход запоминающего устройства 25 арифметический блок 23 осуществляет суммирование входного кода с общей шины с выходным кодом запоминающего устройства 25, адрес которого задается блоком 36 синхронизации, с последующей записью суммы по тому же адресу. Пульт 26 управления предназначен для задания кода номера гармоники. Блок 28 констант представляет собой постоянное запоминающее устройство, которое хранит таблицу синусов и косинусов в диапазоне О - 360 . Блок 36 синхронизации является типовым узлом спектроанализирующей аппаратуры и может быть реализован каскадньм соединением формирователя, умножителя частоты и распределителя импульсов. Блок 36 обеспечивает формирование последовательностей импульсов, изображенных на фиг.2, в течение каждого периода Т входного сигнала. Импульсы и используются для за№ 1кания ключа 5 и перевода блока 28 .констант в режим воспроизведения косинусов. Импульсы UL используются для замыкания ключа 7. Импульсы DC осуществляют сброс интеграторов 6, 8 и запись информации в регистры 29 и 33. Импульсы U(j производят сдвиг информации в регистрах 10 и 14. Импульсы U осуществляют запись информации в регистр 4. Импульсы Uo производят запись кодов в регистр 35 и запоминающее устройство 25. Импульс Ujj стробирует пульт 26 и управления. Импульс Ug стробирует дешифратор 22, Импульсы и управляют переключением коммутаторов 12, 16 и управляют адресными шинами запоминающих устройств 19, 20 и 25. Количество адресов и соответственно входов коммутаторов равно двум. При наличии импульса Uj коммутаторы пере- .

ключаются в верхнее по схеме положение. Импульсы и ( производят запись информации в триггер 17 и счетчик 18. Импульсы Up являются тактовыми для

счетчиков 18 и стробирующими для схемы 21 выделения нулевого кода. Импульсы и производят запись информации в запоминающие устройства 19 и 20.

Устройство работает следующим образом.

При поступлении на вход анализато- ра спектра периодического сигнала с периодом Т на выходах интегратора 6

и 8 блока 2 формируются соответственно напряжения косинусной и синусной ортогональных составляющих сигнала компенсации измеряемой гармоники. Измеряемая гармоника определяется

частотой выходного сигнала блока 28 констант, которая кратна частоте входного сигнала и определяется номером гармоники задаваемым с пульта 26 управления. Код номера гармоники через заданные интервалы времени суммируется с содержимым арифметического блока 23 по адресу хранения фазы раз за период, производя тем самым К-кратный опрос блока 28 констант

в течение периода Т. При этом на выходе блока 28 формируется цифровая синусоида .(косинусоида) К-й гармоники, нач альная фаза которой определя - ется кодом по этому адресу в начале

35 периода входного сигнала. Приращениями фазы управляет сигнал синусной ор- ,тогональной составляющей, Вькодной сигнал генератора 27 компенсации формируется из косинусного опорного сигг

40 нала блока 2, а амплитуда сигнала генератора 27 задается кодом цифро- аналогового преобразователя 32 и напряжением опорного источника 31. Регулировкой амплитуды генератора 27

45 управляет сигнал косинусной ортогональной составляющей. Цифроаналого- вьш преобразователь 3 используется в режиме разделения времени. Это достигается поочередной коммутацией

50 его выхода с помощью ключей 5 и 7 ко входам интеграторов 6 и 8 при одновременной смене вида опорных сигналов (синусный или косинусный) на втором входе преобразователя 3. Порого55 вые элементы 9 и 13 вьщеляют знаки полярностей ортогональных составляю- пщх, а сдвиговые регистры 10 и 14 в совокупности с элементами 11, 15 и

5.1237987

ИСКЛЮЧАЮЩЕЕ ИЛИ фиксируют знаки ортогональных составляющих в текущем и предьодущем периодах и выявляют наличие повторения знаков по каждой составляющей. Алгоритм формирования 5 приращений является одинаковьм для обоих параметров (амплитуды и фазы) генератора 27 компенсирующего сигнала. Поэтому блоки формирования приращений: триггер 17, счетчик 18 и схе- Ю |ма 2Гвьщеления нулевого кода -используется поочередно в режиме разделения времени. Этот режим обеспечивается коммутаторами 12, 16 и запоминающими устройствами 19 и 20, фиксирующими 5 текущие состояния триггера 17 и счетчика 18, на основе которых формируются приращения фазы и амплитуды, для последующего восстановления этих параметров в следующем периоде. Форми- 20 рование приращений происходит по следующему принципу. Если состояние реверсивного счетчика 18 равно нулю, то , схема 21 сбрасывает триггер 17 что переводит счетчик J 8 в режим сложе- 25 кия. При этом пока-ортогональная составляющая не изменит свой знак состояние счетчика увеличивается каждый период на одну единицу. Это приводит к нарастанию модуля приращения,30 регулируемого ортогональной составляг- ющей параметра, на выходе дешифратора 22 по показательному закону. Знак кода приращения на выходе дешифратора равен знаку ортогональной состав- 35 ляющей в текущем периоде. После смены знака ортогональной составляющей, что происходит при достижении режима перекомпенсации, триггер 17 устанавливается элементом ИСКЛЮЧАЮЩЕЕ ИЛИ в единичное состояние, соответствующее переводу счетчика 18 в режим вычитания. Перевод счетчика в режим вычитания приводит к формированию убыПредложенное устройство позволяет повысить быстродействие и точност анализатора спектра более чем на порядок, что достигается переходом к цифровому управлению процессом компенсации измеряемой гармоники. Предлагаемое изобретение реализовано Б измерителе коэффициента несинусоидальности и уровней высших гармони напряжений; промышленных электрических сетей.

Формула изобретени

Анализатор спектра, содержащий блок вьщеления ортогональных состав ляющих, состоящий ИЗ цифроаналого- вого преобразователя, к цифровому в ду которого подклзочен регистр, а вы ход подключен к двум параллельно включенным каналам, каждый из кото- IMjix состоит из последовательно соед ненных ключа, интегратора и порогового элемента, генератор компенсиру щего сигнала, состоящий из последов тельно соединенных источника опорно го напряжения и двух цифроаналоговы преобразователей, вторые входы которых подключены к своим регистрам, арифметический блок, состоящий из последовательно соединенных тора и оперативного запоминающего устройства, выход которого соединен со вторым входом сумматора, а также пульт управления, выход которого связан с входом арифметического бло ка, индикатор с входным регистром,- блок констант, вычитатель и блок синхронизации, вход которого объеди нен с входом вьгчитателя и является входом анализатора, а выход.связан со всеми управляющими входами ре- . гистров, со входами ключей и интеграторов, входом блока констант, пул

вающих по величине приращений и плав- та управления и входами управления

ному завершению процесса компенсации гармоники. Режим вычитания сохраняется до полного обнуления счетчика

18.

Алгоритм управления приращениями, реализованный посредством введенных в устройство функциональных узлов, смоделирован на ЭВМ. В зависимости от дискретности перестройки парамет- ров генератора компенсации выигрыш по быстродействию составляет от дващ цати до пятисот раз.

Предложенное устройство позволяет повысить быстродействие и точност анализатора спектра более чем на порядок, что достигается переходом к цифровому управлению процессом компенсации измеряемой гармоники. Предлагаемое изобретение реализовано Б измерителе коэффициента несинусоидальности и уровней высших гармоник напряжений; промышленных электрических сетей.

Формула изобретения

Анализатор спектра, содержащий блок вьщеления ортогональных составляющих, состоящий ИЗ цифроаналого- вого преобразователя, к цифровому вхду которого подклзочен регистр, а выг ход подключен к двум параллельно включенным каналам, каждый из кото- IMjix состоит из последовательно соединенных ключа, интегратора и порогового элемента, генератор компенсирующего сигнала, состоящий из последовательно соединенных источника опорного напряжения и двух цифроаналоговых преобразователей, вторые входы которых подключены к своим регистрам, арифметический блок, состоящий из последовательно соединенных тора и оперативного запоминающего устройства, выход которого соединен со вторым входом сумматора, а также пульт управления, выход которого связан с входом арифметического блока, индикатор с входным регистром,- блок констант, вычитатель и блок синхронизации, вход которого объединен с входом вьгчитателя и является входом анализатора, а выход.связан со всеми управляющими входами ре- . гистров, со входами ключей и интеграторов, входом блока констант, пульта управления и входами управления

арифметического блока, выход которого подключен одновременно к входу регистра индикатора, к выходу блока констант и к первому регистру генератора .компенсирующего сигнала, вход второго регистра которого соединен с входом регистра блока выделения ортогональных составляющих и с выходом блока констант, при этом второй вход вычитателя подключен к выходу генератора компенсирующего сигнала, а выход по,цслючен ко входу блока вьщеления ортогональных составляющих сигнала, о тличающий ся тем, что, с целью повьпления быстродействия и точности измерений в него введены два двухвходовых коммутатора, два элемента ИСКЛЮЧАЮГДЕЕ ИЛИ, последовательно соединенные D -триггер с элементом памяти в цепи обратной связи, реверсивный счетчик, оперативное запоминающее устройство и схема

со вторыми входами своих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого двух- входового коммутатора подключен к входу Б-триггера, второй вход которого соединен с выходом схемы выделения нулевого кода, вьпсод оперативного запоминающего устройства соединен со вторым входом реверсивного счетчика, выход которого подключен к девьщеления нулевого кода, а также де- Ю шифратору, второй вход дешифратора шифратор и два сдвиговых регистра, соединен с выходом второго двухвходового коммутатора, а его выход подключен к входу арифметического блока, выход блока синхронизации подклю- 15 чей также к управляющим входам сдвигов.ых

подключенных к выходам пороговых элементов, при этом выходы первого двух- входового коммутатора подключены к первым выходам обоих сдвиговых pe-j

гистров через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, а входы второго двухвходового коммутатора подключены непосредствен- . но к этим же входам - двиговых регистров, вторые входы которых соединены 20 кода дешифратора.

регистров, коммутаторов,Р-триггера, реверсивного счетчика, элемента памяти, оперативного запоминающего устройства, схемы выделения нулевого

со вторыми входами своих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого двух- входового коммутатора подключен к входу Б-триггера, второй вход которого соединен с выходом схемы выделения нулевого кода, вьпсод оперативного запоминающего устройства соединен со вторым входом реверсивного счетчика, выход которого подключен к девого коммутатора, а его выход подключен к входу арифметического блока, выход блока синхронизации подклю- чей также к управляющим входам сдвигов.ых

регистров, коммутаторов,Р-триггера, реверсивного счетчика, элемента памяти, оперативного запоминающего устройства, схемы выделения нулевого

фие.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор спектра | 1985 |

|

SU1287033A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Приемник сигналов офсетной фазовой манипуляции | 1987 |

|

SU1434559A1 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

| ИНТЕРПОЛЯТОР | 1970 |

|

SU272415A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1985 |

|

SU1414127A1 |

Изобретение относится к изме- рительной технике. Может использоваться для измерения амплитудного спектра периодических сигналов, например высших гармоник напряжений промьшшенной электросети. Цель изобретения - повышение быстродействия, достигается цифровым управлением величинами приращений амплитуды и фазы генератора компенсирзтощего сигнала (ГКС) при сохранении требуемого качества переходных процессов регулирования. Анализатор содержит вычитающее устройство 1, блок 2 выделения ортогональных составляющих сигнала, в состав которого входят цифроаналоговый преобразователь (ЦАП) 3, регистр (РГ) 4, ключи 5 и 7, интеграторы 6 и 8 и пороговые элементы 9 к 13, сдвиговые регистры 10 и 14, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11 и 15, коммутаторы 12 и 16, D-триггер 17, реверсивный счетчик 18, оперативное запоминающее устройство (ОЗУ) 19 и 20, блок 21 выделения нулевого кода, дешифратор 22, арифметический блок 23, содержащий сумматор 24 и ОЗУ 25, ГКС 27, содержащий ЦДЛ 32 и 34, РГ 35 и 33, источник 31 опорного напря -; жения. В анализатор также входят пульт управления 26, блок 28 констант. РГ 29, индикатор 30 и блок синхронизации 36. 3 ил. I (Л С ( со 00 vj

Редактор Н.Горват

Составитель А.Орлов Техред Л.Сердюкова

Заказ 3284/45 Тираж 728 . Подписное ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., ж. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор Г.Решетник

| Алиев Т.М | |||

| и др | |||

| Автокомпенсационные измерительные устройства пе ременного тока | |||

| М.: Энергия, 1977, с.128, 230. |

Авторы

Даты

1986-06-15—Публикация

1984-07-16—Подача