поступает на выход. Также поступают на выход устройства другие разряды цифровых кодов, хранящиеся в БП 3. 1197147 Блок 7 синхронизации вырабатьшает управляющие сигналы для всех блоков устройства. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1982 |

|

SU1019668A1 |

| Устройство формирования сигнала для управления столбцами телевизионного матричного экрана | 1984 |

|

SU1185655A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Осциллограф с матричным экраном | 1983 |

|

SU1129529A1 |

| Устройство для управления матричным телевизионным экраном | 1982 |

|

SU1107337A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

| Устройство управления столбцами телевизионного матричного экрана | 1984 |

|

SU1246414A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство отображения телевизионной информации | 1986 |

|

SU1394464A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162248C2 |

Изобретение относится к телевидению. Видеосигнал поступает на аналого-цифровой преобразователь (АЦП) .1. Старшие (Ц -1) разряды цифрового кода через мультиплексор 2, преобразующий код в последовательную форму, поступают на блок памяти (БП) 3. На адресные входы БП 3 с блока 7 синхронизации поступают последовательно изменяющиеся |Коды адреса.Младший разряд цифрового кода с АЦП 1 через управляемьй переключатель 4 записьшается в сдвиговьй регистр (СР) 5. С приходом на буферный регистр 6 импульса разрешения записи, совпадающего по фазе со строчным гасящим импульсом, информация, записанная в СР 5, переписьшается в буферный регистр 6 и поступает на выходы устройства. Одновременно из БП 3 через управляемый . переключатель 4 переписываются в PC 5 вторые разряды записанного сигнала. По импульсу записи в буфер(Л ный регистр 6 переписывается информация о вторых разрядах,с PC 5 и Выходы. с с

1

Изобретение относится к телевидению и может использоваться в устройствах отображения информации на жидкокристаллических и светодиодных матричных экранах.

Цель изобретения - упрощение устройства при одновременном снижении требований к быстродействию блика памяти и сдвигового регистра.

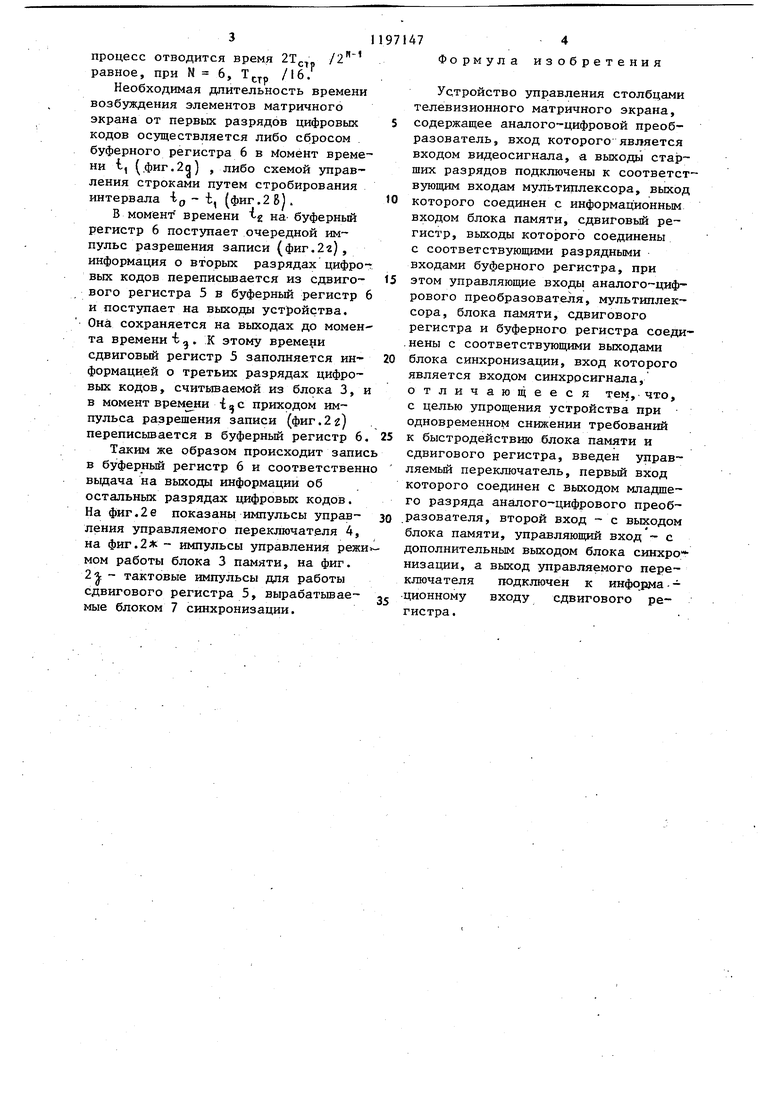

На фиг.1 приведена структурная электрическая схема устройства управления столбцами телевизионного матричного экрана; на фиг.2 - диаграммы, поясняющие его работу.

Устройство управления столбцами, телевизионного матричного экрана содержит аналого- цифровой преобразователь. 1, мультиплексор 2, блок 3 памяти, управляемый переключатель 4 сдвиговый регистр 5, буферный регист 6 и блок 7 синхронизации.

Устройство работает следующим образом.

Телевизионный видеосигнал (фиг.2а с входа устройства поступает на аналого-цифровой преобразователь 1, на выходе которого вырабатьшается N-разрядный цифровой код, соответствующий мгновенному значению телевизионного сигнала в момент прихода тактового импульса с блока 7 синхронизации . За время активной части теле визионной строки на управляющий вход аналого-.цифрового преобразователя 1 поступает К тактовых импульсов фиг.25 . В соответствии с этими импульсами за одну строку из видеосигнала производится К выборок для отображения их на плоском экране, содержащем К столбцов. С выхода аналого-цифррвого преобразователя 1 старшие (м -1 разряды цифрового кода поступают на мультиплексор 2, который преобразует цифровые коды выборок сигнала в последовательную форму. С выхода мультиплексора 2 цифровой сигнал поступае-Г на информационный вход блока 3 памяти. На адресные входы блока 3 с блока 7 синхронизации поступают последовательно изменяющиеся коды адреса, и

каждый бит информации размещается в соответствующей ячейке блока 3. В то же время информация, формирзпощаяся на млаДшем выходном разряде аналого-цифрового преобразователя

I , через управляемый переключатель 4 записьюаетсяв сдвигрвьй регистр 5.

Для управления столбцами матричного экрана применяется широтно-импульсная модуляция. При этом на выходы

устройства выставляются сначала младшие разряды всех выборок телевизионного видеосигнала на время, пропорциональное их весу в цифровом коде. Затем на выходы выставляются

следующие по старшинству разряды на время, пропорциональное их весу в цифровом коде (в 2 раза превьшающее предыдущее, и т.д. (фиг.28). Время, за которое на выходы выставляются последние разряды, составляет одну телевизионную строку при цикле считьшания в две телевизионных строки), а время, на которое выставляются на выходы младшие разряды,

составляет 2Тстр /2 , где

период строчной развертки. В приведенном на фиг.2 примере N 6 и это время составляет Тетр /32.

Процесс считьшания информации на

выходы устройства начинается с

приходом на управляющий вход разрешения записи буферного регистра 6 импульса, совпадающего по фазе с фронтом строчного гасящего импульса в телевизионном сигнале (фиг.2г). При этом информация, записанная в сдвиговомрегистре 5, переписьшается в буферньш регистр 6 и поступает на выходы устройства. Одновременно начинается считывание из блока 3 вторых разрядов записанного сигнала в сдвиговый регистр 5. На этот процесс отводится время 21 /2 равное, при N 6, Т Необходимая длительность времени возбуждения элементов матричного экрана от первых разрядов цифровых кодов осуществляется либо сбрросом . буферного регистра 6 в Момент време ни t, (,фиг.2а) , либо схемой управления строками путем стробирования интервала о (фиг.2 В. В момент времени г. на- буферный регистр 6 поступает очередной импульс разрешения записи (фиг.2г), информация о вторых разрядах цифро вых кодов переписьшается из сдвигового регистра 5 в буферный регистр и поступает на выходы устройства. Она сохраняется на выходах до момен та времени i . К этому времени сдвиговый регистр 5 заполняется информацией о третьих разрядах цифровых кодов, считываемой из блока 3, в момент времени i с прихрдом импульса разрешения записи (фиг.2г) переписывается в буферный регистр 6 Таким же образом происходит запи в буферный регистр 6 и соответствен вьщача на выходы информации об остальных разрядах цифровых кодов. На фиг.2е показаны импульсы управления управляемого переключателя 4, на фиг.2 - импульсы управления реж мом работы блока 3 памяти, на фиг. 2 Ч: - тактовые импульсы для работы сдвигового регистра 5, вырабатьшаемые блоком 7 синхронизации. 74 Формула изобретения Устройство управления столбцами телевизионного матричного экрана, содержащее аналого-цифровой преобразователь, вход которого является входом видеосигнала, а выходы старших разрядов подключены к соответствующим входам мультиплексора, выход которого соединен с информационным входом блока памяти, сдвиговьй регистр, выходы которого соединены с соответствующими разрядными входами буферного регистра, при этом управляющие входы аналого-цифрового преобразователя, мультиплек сора, блока памяти, сдвигового регистра и буферного регистра соединены с соответствующими выходами блока синхронизации, вход которого является входом синхросигнала, отличающееся тем, что, с целью упрощения устройства при одновременном снижении требований к быстродействию блока памяти и сдвигового регистра, введен управляемьй переключатель, первьй вход которого соединен с выходом младшего разряда аналого-цифрового преобразователя, второй вход - с выходом блока памяти, управляющий вход - с дополнительным выходом блока синхро низации, а выход управляемого переключателя подключен к инфориа-ционному входу сдвигового регистра.

f инп. t xaiKieu novxe .2

| Устройство для отображения информации | 1982 |

|

SU1019668A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США №4210934, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-12-07—Публикация

1984-08-14—Подача