сигнала, который через ЦА11 5 поступает на выход. С помощью блока 12 формирования сигналов обращения, элемента ИЛИ 13, триггера 11 и блока 10 формирования сигналов выборИзобретение относится к технике телевидения и может использоваться для сопряжения скорости развертки малокадровьк систем со скоростью развертки широковещательных телевизионных систем.

Цель изобретения - снижение потребляемой мощности.

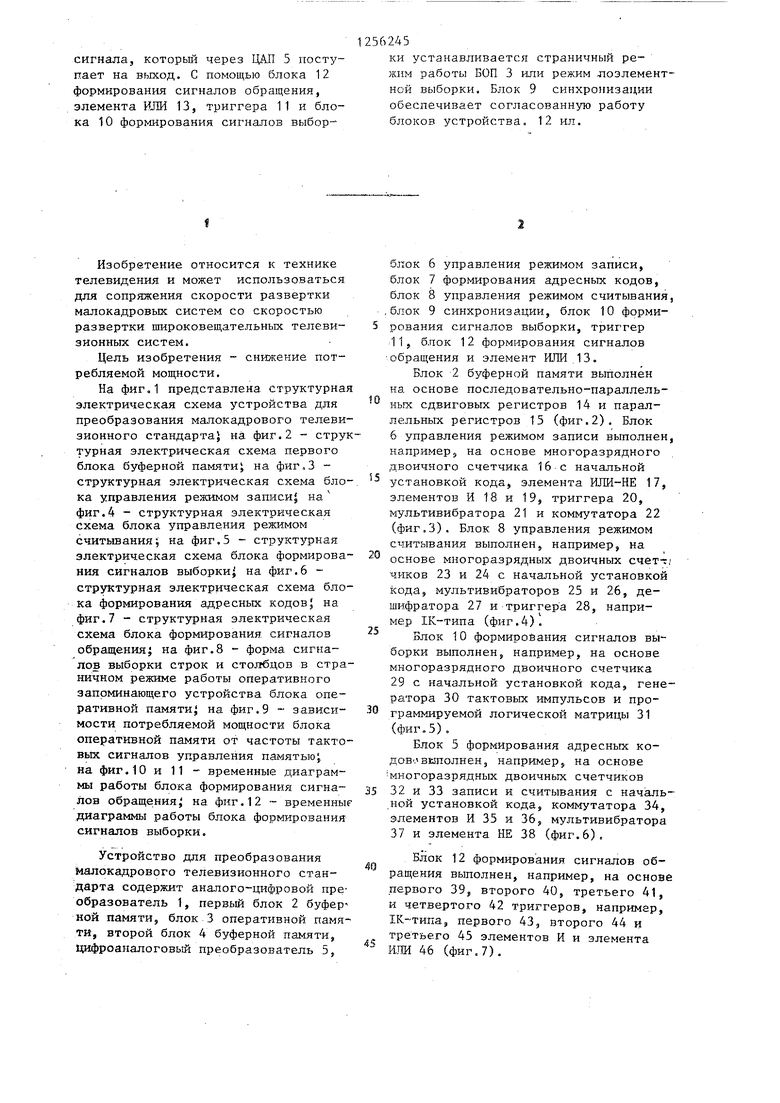

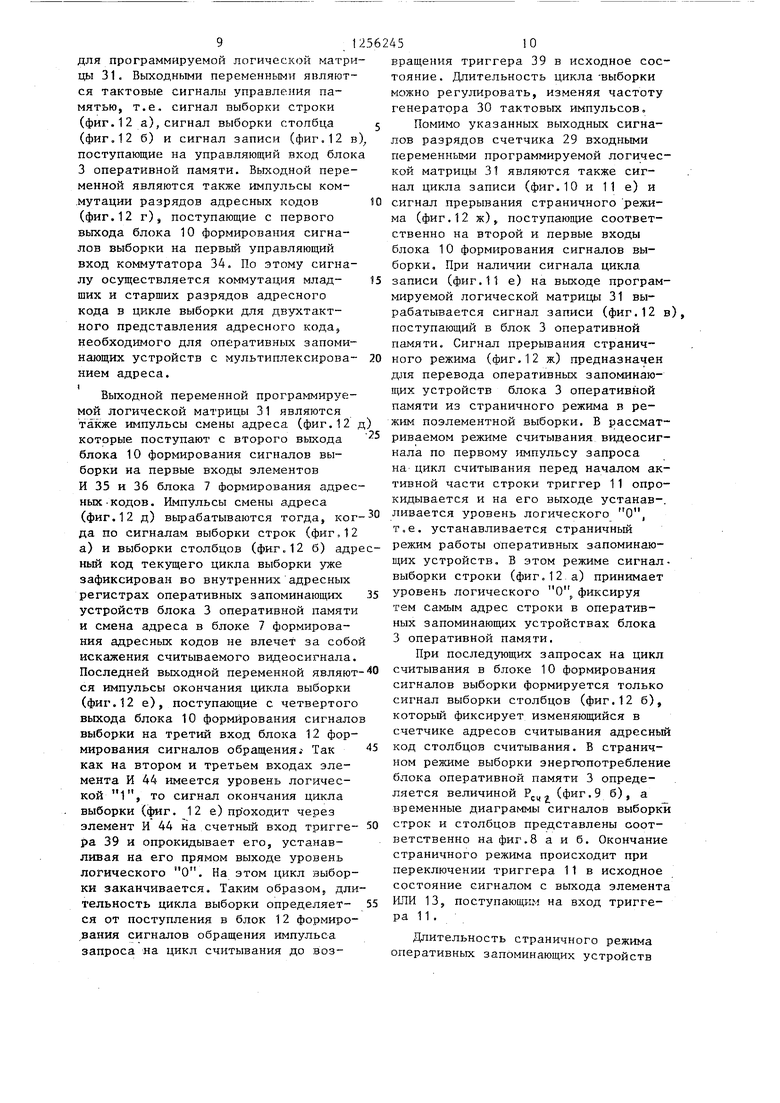

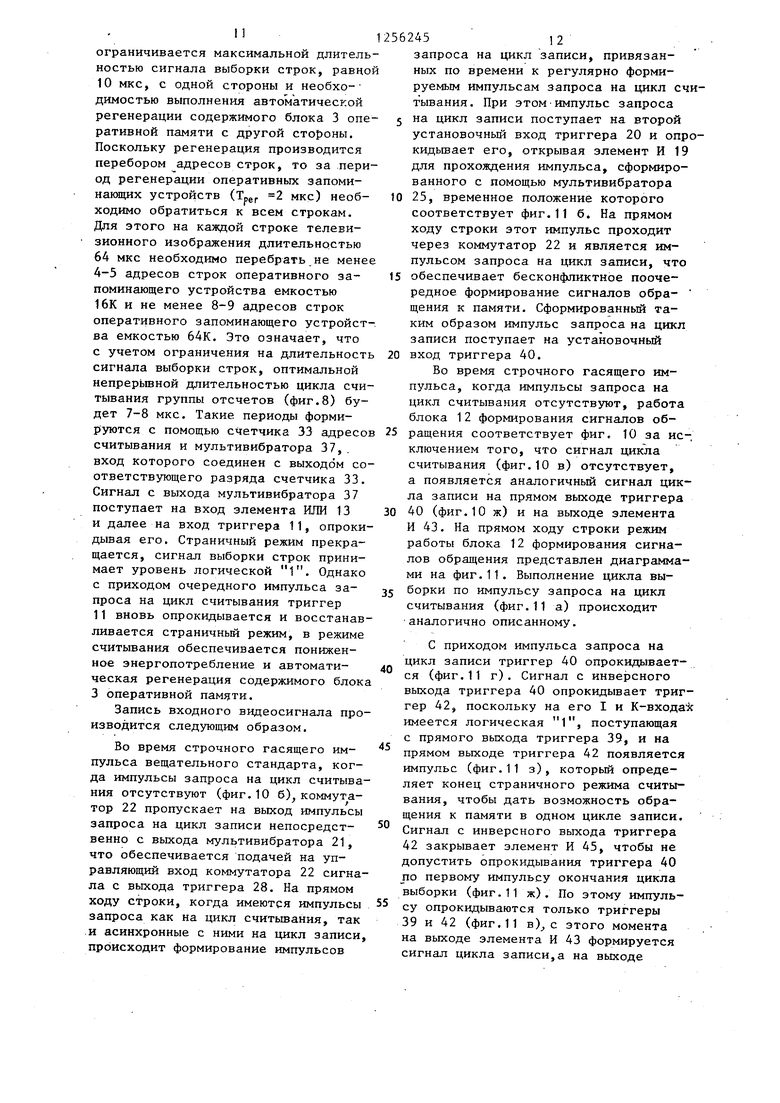

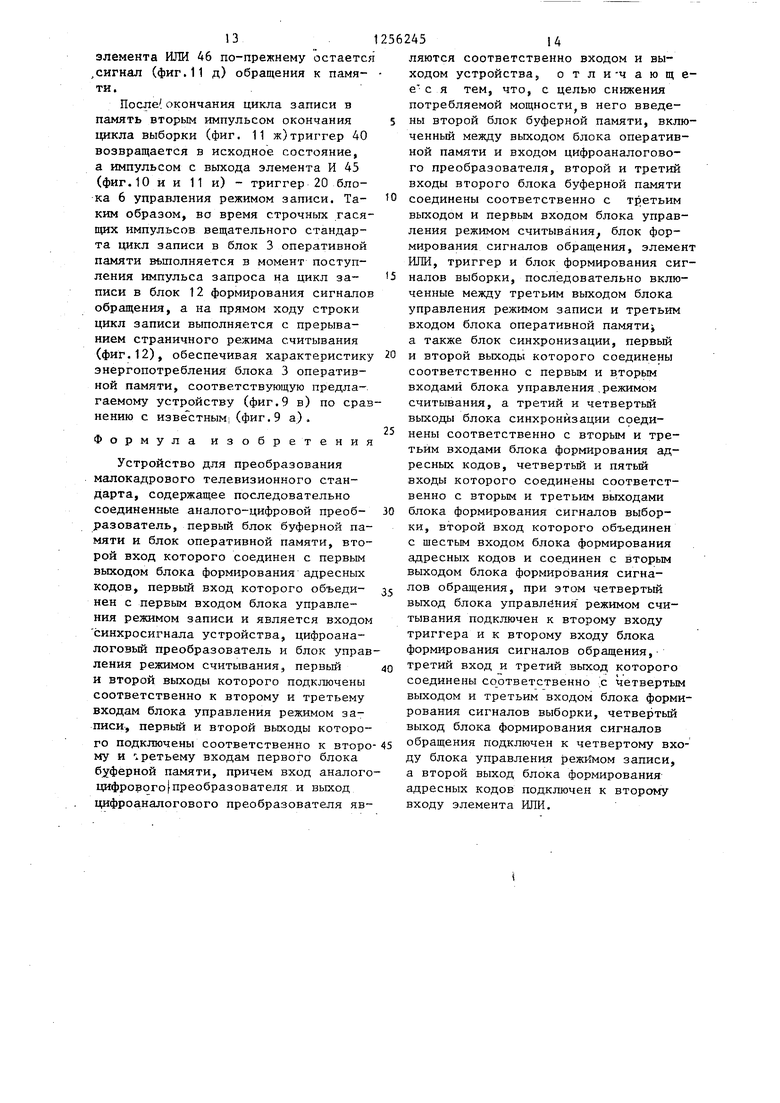

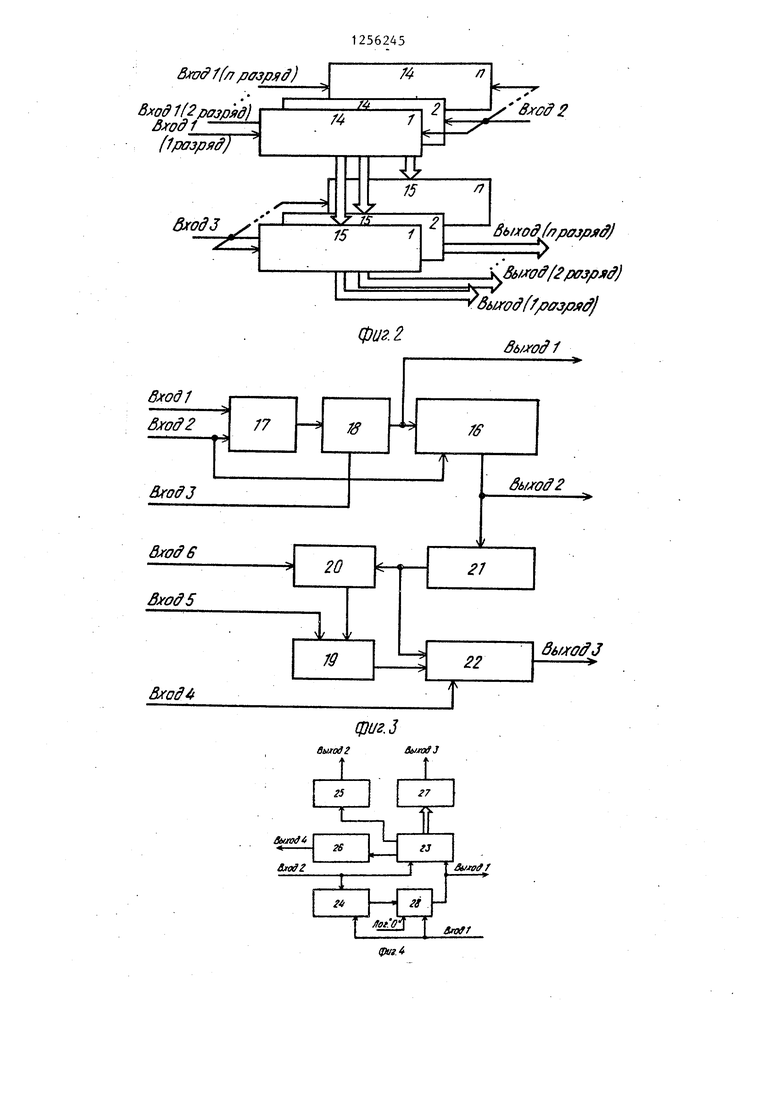

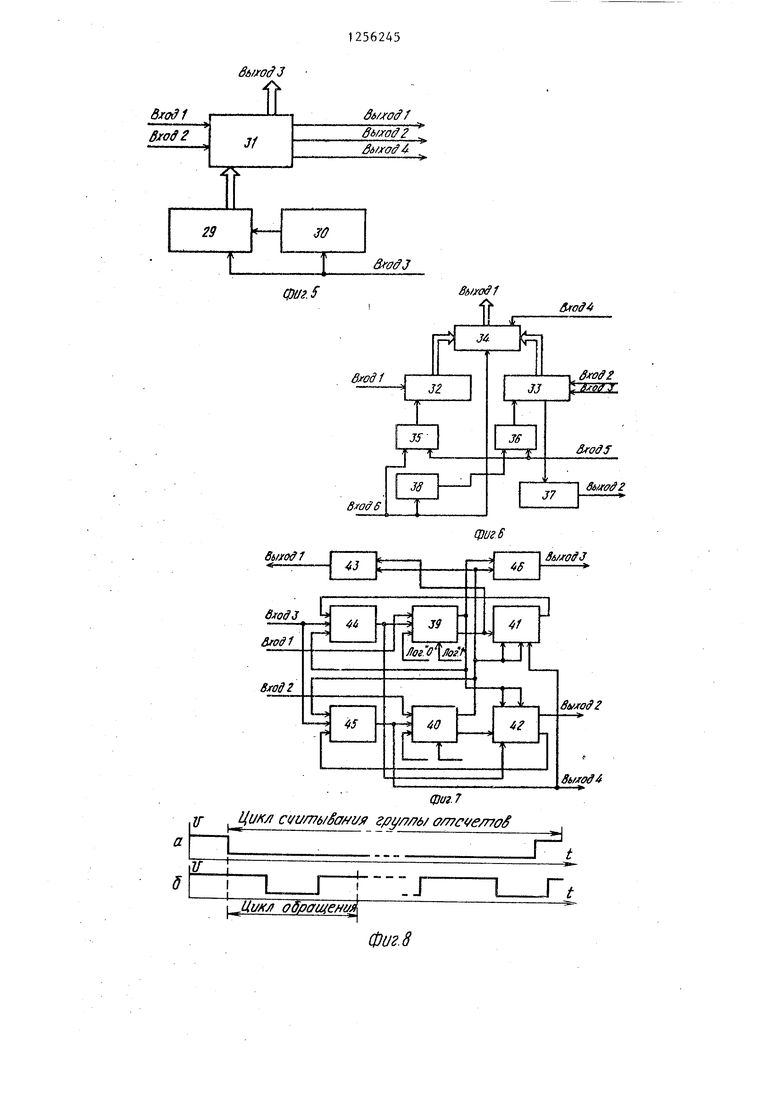

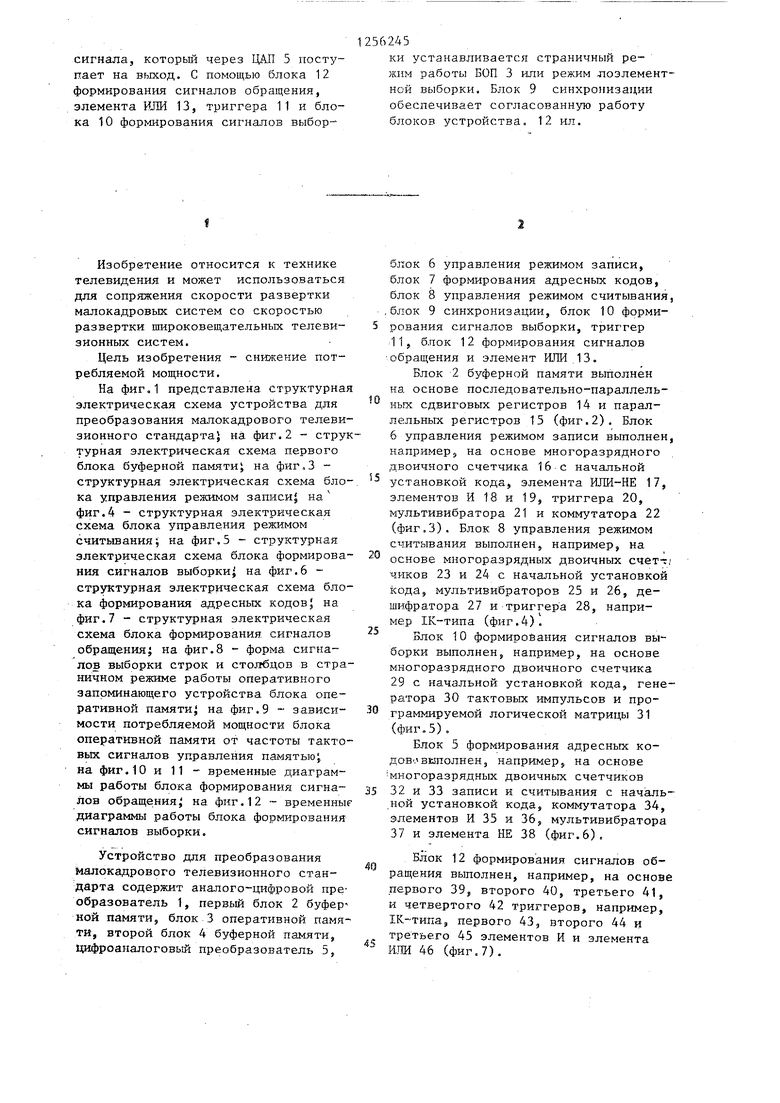

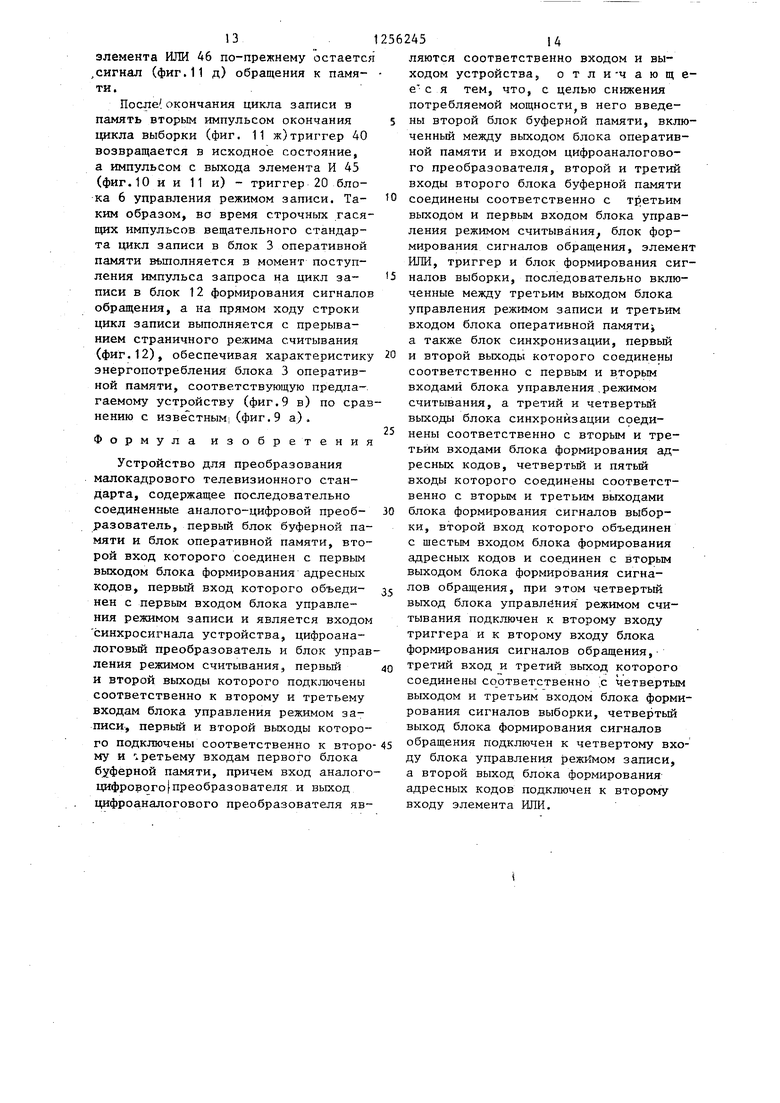

На фиго1 представлена структурная электрическая схема устройства для преобразования малокадрового телевизионного стандарта на фиг.2 - структурная электрическая схема первого блока буферной памяти на фиг.З - структурная электрическая схема блока управления режимом записи на фиг.4 - структурная электрическая схема блока управления режимом считьшания на фиг.5 - структурная электрическая схема блока формирования сигналов выборкиJ на фиг.6 - структурная электрическая схема блока формирования адресных кодовJ на фиг.7 - структурная электрическая схема блока формирования сигналов обращения; на фиг.8 - форма сигналов выборки строк и столбцов в страничном режиме работы оперативного запоминающего устройства блока оперативной памяти на фиг.9 - зависимости потребляемой мощности блока оперативной памяти от частоты тактовых сигналов управления памятью на фиг,10 и 11 - временные диаграммы работы блока формирования сигналов обращения на фиг.12 - временные диаграммы работы блока формирования сигналов выборки.

Устройство для преобразования малокадрового телевизионного стандарта содержит аналого-цифровой преобразователь 1, первый блок 2 буфер ной памяти, блок 3 оперативной памяти, второй блок 4 буферной памяти, дифроаналоговый преобразователь 5,

ки устанавливается страничный режим работы БОП 3 или режим лоэлемент- ной выборки. Блок 9 синхронизации обеспечивает согласованную работу блоков устройства. 12 ил.

5

5

0

5

блок 6 управления режимом записи, блок 7 формирования адресных кодов, блок 8 управления режимом считывания, ,блок 9 синхронизации, блок 10 формирования сигналов выборки, триггер 115 блок 12 формирования сигналов обращения и элемент ИЛИ 13.

Блок 2 буферной памяти вьшолнен на основе последовательно-параллель- ньЕх сдвиговых регистров 14 и параллельных регистров 15 (фиг.2). Блок 6 управления режимом записи выполнен, например, на основе многоразрядного двоичного счетчика 16 с начальной установкой кода, элемента ИЛИ-НЕ 17, элементов И 18 и 19, триггера 20, мультивибратора 21 и коммутатора 22 (фиг.З). Блок 8 управления режимом считывания выполнен, например, на основе многоразрядных двоичных счет-г; чиков 23 и 24 с начальной установкой кода, мультивибраторов 25 и 26, дешифратора 27 и триггера 28, например 1К-типа (фиг.4).

Блок 10 формиройания сигналов выборки выполнен, например, на основе м:ногоразрядного двоичного счетчика 29 с начальной установкой кода, генератора 30 тактовых импульсов и программируемой логической матрицы 31 (фиг,5).

Блок 5 формирования адресных ко- дововыполнен5 например, на основе многоразрядных двоичных счетчиков 32 и 33 записи и считывания с началь- .ной установкой кода, коммутатора 34, элементов И 35 и 36, мультивибратора 37 и элемента НЕ 38 (фиг.6),

Блок 12 формирования сигналов обращения выполнен, например, на основе первого 39J второго 40, третьего 41, и четвертого 42 триггеров, например, , первого 43, второго 44 и третьего 45 элементов И и элемента ИЛИ 46 (фиг.7).

3

Устройство работает следующим образом.

В аналого-цифровом преобразователе 1 видеосигнал преобразуется ё цифровую форму. С выхода аналого-цифрового преобразователя 1 цифровой видеосигнал поступает на первый вход первого блока 2 буферной памяти, где производитсй его временное разуплотнение с целью обеспечения записи разуплотненного видеосигнала, поступающего с выхода первого блока 2 буферной памяти на вход блока 3 оперативной памяти. Считываемый видеосигнал с выхода блока 3 оперативной памяти поступает на первый вход второго блока 4 буферной па1 1яти, где осуществляется его временное уплотнение с целью формирования видеосигнала в соответствии с вещательным или близким к нему стандартом. С выхода второго блока буферной памяти цифровой видеосигнал поступает на вход дифроаналогового преобразователя 5, где преобразуется в аналоговую форму и поступает далее на выход устройства. Наличие в устройстве двух блоков буферной памяти на входе и выходе блока 3 оперативной памяти позволяет осуществлять одновременно запись и считывание видеосигналов с различными стандартами разложения изображений, а также согласовать сравнительно низкие частоты обращения к динамическим оперативным запоминающим устройствам блока 3 оперативной памяти с высокой частотой дискретизации выходного видеосигнала вещательного или близкого к нему стандарта.

Запись видеосигнала входного стандарта разложения изображения осуществляется следующим образом.

Отсчеты входного видеосигнала в виде п-разрядных слов (обычно пб8) поступают с выхода аналого- цифрового преобразователя 1 на информационные входы п последовательно-параллельных сдвиговых регистров 14. Разрядность последовательно- параллельных сдвиговых регистров 14 и параллельных регистров 15 вы- бирается равной разрядности парал- .лельно-последовательных регистров второго блока 4 буферной памяти. Запись входных отсчетов видеосигнала в последовательно-параллельные регистры 14 осуществляется по посту2454

пающим на их тактовые входы импульсам, частота которых соответствует частоте дискретизации входного видеосигнала. Совокупность тактовых импуль- сов, определяющих структуру отсчетов в пределах прямых ходов строк и кадра записываемого изображения и подаваемых на тактовые входы последовательно-параллельных сдвиговых регистров

14, формируется с помощью элемента И 18, на первый вход которого подается смесь строчных и кадровых гасящих импульсов записи отрицательной полярности, а на второй вход поступает

непрерывная последовательность импульсов с частотой дискретизации входного видеосигнала, привязанных по фазе к строчным гасящим импульсам. Смесь строчных и кадровых гасящих

импульсов записи формируется с помощью элемента ИЛИ-НЕ 17, на первый и второй входы которого подаются соответственно кадровый и строчный гасящие импульсы записи положительной полярности. В момент полного

заполнения последовательно-параллельных регистров 14 их содержимое переписывается в параллельные регистры

15,на тактовые входы которых подает- ся сигнал перезаписи. Сигнал перезаписи поступает со старшего разряда счетчика 16, коэффициент счета которого соответствует разрядности регистров первого блока 2 буферной памяти.

Во время обратного хода строк записи счетчик 16 устанавливается в нулевое состояние подачей на его управляющий вход установки начального кода строчного гасящего импульса записи. Во

время прямого хода строк записи счетчик 16 изменяет свое состояние синхронно с заполнением последовательно - параллельных сдвиговых регистров 14. Сигнал перезаписи, формирующийся

на выходе старшего разряда счетчика

16,поступает, кроме того, на вход мультивибратора 21, где формируется импульс запроса на цикл записи, который через коммутатор 22 поступает

на первый вход блока 12 формирования сигналов обращения. В результате в цикле записи содержимое параллельных регистров 15 записывается в блок 3 оперативной памяти по адресному коду

записи, выработанному в блоке 7 формирования адресных кодов.

Адресные коды записи формируются с помощью счетчика 32 адресов записи, которьй устанавливается в нуле- рое состояние при подаче на его управляющий вход установки начального кода кадрового гасящего импульса. Сое тояние Счетчика 32 изменяется на единицу в конце каждого цикла записи по импульсу смены адреса, поступающему на первый вход элемента И 35, на второй вход которого во время цикла за.писи поступает логическая 1. В ре

зультате импульс перезаписи с выхода элемента И 35 подается на тактовый вход счетчика 32 адресов записИа при этом на выходах разрядов счетчика 32 устанавливается адресный код запи- си для следующего цикла записи. С выходов разрядов счетчика 32 адресов записи через коммутатор 34 адресные коды записи поступают на второй :эход блрка 3 оперативной памяти. Коммуна- ция адресных кодов записи и считывания производится подачей на второй управляющий вход коммутатора 34 сигнала цикла записи (фиг.11 е).

Считывание видеосигнал:а с выходным стандартом разложения изображения осуществляется следующим образом ,

Отсчеты выходного разуплотненного видеосигнала с выхода блока 3 оперативной памяти поступают на первый вход второго блока 4 буферной памяти. Тактовые импульсы сдвига с частотой .дискретизации выходного видеосигнала, т.е. для вещательного стандарта равной 13,5 МГц, подаются на тактовые входы параллельно-последовательных сдвиговых регистров второго блока 4 буферной памяти с первого выхода блока 9 синхронизации.

Перевод параллельно-последовательйых регистров второго блока 4 буферной памяти в режим параллельного занесения отсчетов разуплотненного видеосигнала производится по сигналуJ поступающему с выхода дешифратора .27 блока 8 управления режимом считывания. Для формирования этого сигнала на управляющий вход установки начального кода счётчика 24 и вход установки триггера 28 подаются строчные синхронизирующие импульсы вещательного стандарта с второго выхода блока 9 синхронизации. При этом счетчик 24 обнуляется, а на выходе триггера 28 устанавливается уровень логичес- кой 1. На тактовый вход счетчика 24 подаются импульсы частоты дискре- тизадии выз одного видеосигнала. Коэф

0

5 0

5

0

О О 5 х

фициент счета счетчика 24 выбирается таким образом, чтобы положительный перепад сигнала старшего разряда счетчика 24, поступающего на счетный вход триггера 28 устанавливал на выходе триггера 28 уровень логического

О до нач.ала активной части строки выходной развертки. В результате на

выходе триггера 28 формируются импульсы положительной полярности, передние фронты которых совпаданзт с началом строчных синхронизирующих импульсов, а задние фронты опережают начало активной части строк на время, достаточное для осуществления цикла считывания разуплотненного видеосигнала из блока 3 оперативной памяти во второй блок 4 буферной памяти.

Сигнал с выхода триггера 28 обнуляет счетчик 23, поступая на его управляющий вход установки начального кода, а на тактовый вход счетчика 23 подаются И1«1пульсы частоты дискретизации выходного видеосигнала. Коэф- сЬициент счета счетчика 23 соответствует разрядности регистров второго , блока 4 буферной памяти, которая должна быть достаточной, чтобы при максимальной частоте дискретизации выходного видеосигнала периода вывода содержимого второго блока 4 буферной памяти на выход устройства было достаточно для вьтолнения двух циклов выборки памяти, например цикла записи и цикла считывания. Таким образом, на выходе дешифратора 27 формируется сигнал длительностью в один период дискретизации, периодически переводящий параллельно-последовательные сдвиговые регистры второго блока 4 буферной памяти в режим параллельного занесения.

Первое занесение разуплотненного i видеосигнала производится в момент иач ала активной части строки. Каждому занесению разуплотненного видеосигнала во второй блок 4 буферной памяти предшествует формирование импульса запроса на цикл считывания, который опережает момент занесения на время, необходимое для формирования тактовых сигналов управления памятью, обеспечивающих наличие считываемого видеосигнала на выходе блока 3 оперативной памяти к моменту занесения. Импульс запроса на цикл считывания формируется с помощью мультивибратора 26, вход которого соединен с выходом соответствующего разряда счетчика 23.

Разуплотненный видеосигнал считывается из блока 3 оперативной памя- ти в соответствии с адресными.кодами считывания, формируемыми в счетчике 33 адресов считывания блока 7 формирования адресных кодов. Поскольку в вещательном стандарте предусматри- вается чересстрочное разложение изображения, счетчик 33 адресов считывания имеет два начальных состояния. В первом поле кадра считывания счетчик 33 адресов считывания обнуляется по гасящему импульсу поля, поступающему с третьего выхода блока 9 синхронизации на управляющий вход установки начального кода счетчика 33, и по сигналу опознавания полей, пос- тупающему с четвертого выхода блока 9 синхронизации на соответствующие разряды информационного входа параллельной установки кода счетчика 33. Сигнал опознавания полей скважности, равной двум, имеет отрицательную полярность в первом поле и положительную полярность во втором поле, причем переключение сигнала опознавания полей осуществляется синфазно с гасящими импульсами полей. В результате по гасящему импульсу второго поля на выходах ,ра рядов счетчика 33 устанавливается начальный адресный код второго поля. Таким образом, в массиве ячеек памяти блока 3 оперативной памяти образуются области, раздельно адресуемые в первом и втором полях кадра считываемого изображения.

Смена адресных кодов считывания производится с приходом импульса смены адреса, поступающего на первый вход элемента И 36 и далее на тактовый вход счетчика 33. Прохождение импульса смены адреса через элемент И 36 допускается только в циклах считывания. Для этого на второй вход элемента И 36 подается проинвертиро- ванный на элементе НЕ 38 сигнал цик- ла записи. Во время циклов считывания адресные коды с выходов разрядов счетчика 33 адресов считьшания поступают через коммутатор 34 на адресные входы блока 3 оперативной памя- ти. Таким о брав ом на выходе предлагаемого устройства обеспечивается непрерывное считывание видеосигнала

в соответствии с вещательным или близким к нему стандартом.

Процессы записи входного и считы- в ание выходного видеосигналов с временным разуплотнением и уплотнением обеспечиваются адекватным формированием тактовых сигналов управления оперативными запоминающими устройствами динамического типа блока 3 оперативной памяти. Режим выборки памяти начинается с поступления в блок 12 формирования сигналов обращения импульсов запроса на цикл записи и цикл считывания.

Рассмотрим сначала выполнение циклов считывания, частота которых в преобразователе малокадрового телевизионного стандарта сзтцественно выше, чем частота циклов записи.

Импульс запроса на цикл считьшания (фиг. 10а) поступает на установочный вход триггера 39 блока 12 формирования сигналов обращения. При этом на прямом выходе триггера 39 устанавливается уровень логической 1 (фиг.10 в). На прямых выходах остальньгх триггеров 40-42 поддерживается уровень логического О (фиг.10 г и з). Поскольку в этом случае на выходе элемента И 43 сигна записи положительной полярности отсутствует (фиг.10 е). То коммутатор 34 в блоке 7 формирования адресных кодов пропускает на адресные входы блока 3 оперативной памяти адресные коды считывания, а элемент И 36 открывается для прохождения импульса смены адреса считывания.

Сигнал цикла считывания положительной полярности с прямого выхода триггера 39 поступает на первый вход элемента ИЛИ 46, выходной сигнал (фиг.10 д) которого подается на стробирующий вход генератора 30 тактовых импульсов и на управляющий вход установки начального кода счетчика 29 блока 10 формирования сигналов выборки. В отсутствие сигнала (фиг.10 д) счетчик 29 находится в нулевом состоянии, а генератор 30 тактовых импульсов выключен. С приходом сигнала (фиг.10 д) возбуждается генератор 30 тактовых импульсов, с выхода которого тактовые импульсы поступают на тактовый вход счетчика 29, который начинает изменять свое состояние. Выходы разрядов счетчика 29 являются входными переменными

для программируемой логической матрицы 31. Выходными переменными являются тактовые сигналы управления памятью, т.е. сигнал выборки строки (фиг.12 а), сигнал выборки столбца (фиг. 12 б) и сигнал записи (фиг. 12 в поступающиб; на управляющий вход блок 3 оперативной памяти. Вькодной переменной являются также импульсы ком- .мутации разрядов адресных кодов (фиг.12 г), поступающие с первого выхода блока 10 формирования сигналов выборки на первый управляющий вход коммутатора 34. По этому сигналу осуществляется коммутация млад- ших и старших разрядов адресного кода в цикле выборки для двухтактного представления адресного кода, необходимого для оперативных запоминающих устройств с мультиплексирова-

нием адреса. I

Выходной переменной программируемой логической матрицы 31 являются также импульсы смены адреса (фиг.12 которые поступают с второго выхода блока 10 формирования сигналов выборки на первые входы элементов И 35 и 36 блока 7 формирования адресных кодов. Импульсы смены адреса (фиг.12 д) вырабатываются тогда, ког да по сигналам выборки строк (фиг.12 а) и выборки столбцов (фиг.12 б) адрный код текущего цикла выборки уже зафиксирован во внутренних адресных регистрах оперативных запоминающих устройств блока 3 оперативной памяти и смена адреса в блоке 7 формирования адресных кодов не влечет за собо искажения считьшаемого видеосигнала. Последней выходной переменной являют ся импульсы окончания цикла выборки (фиг,12 е), поступающие с четвертого выхода блока 10 формирования сигнало выборки на третий вход блока 12 формирования сигналов обращения.- Так как на втором и третьем входах элемента И 44 имеется уровень логической 1, то сигнал окончания цикла выборки (фиг. 12 е) пр оходит через элемент И 44 на счетный вход тригге- ра 39 и опрокидывает его, устанавливая на его прямом выходе уровень логического О. На этом цикл выборки заканчивается. Таким образом, длительность цикла выборки определяет- ся от поступления в блок 12 формирования сигналов обращения импульса запроса на цикл считывания до возвращения триггера 39 в исходное состояние. Длительность цикла-выборки можно регулировать, изменяя частоту генератора 30 тактовых импульсов.

Помимо указанных выходных сигналов разрядов счетчика 29 входными переменными программируемой логической матрицы 31 являются также сигнал цикла записи (фиг.10 и 11 е) и сигнал прерывания страничного режима (фиг.12 ж), поступающие соответственно на второй и первые входы блока 10 формирования сигналов выборки. При наличии сигнала цикла записи (фиг.11 е) на выходе программируемой логической матрицы 31 вырабатывается сигнал записи (фиг.12 в поступающий в блок 3 оперативной памяти. Сигнал прерывания страничного режима (фиг.12 ж) предназначен для перевода оперативных запоминающих устройств блока 3 оперативной памяти из страничного режима в режим поэлементной выборки. В рассматриваемом режиме считывания видеосигнала по первому импульсу запроса на цикл считывания перед началом активной части строки триггер 11 опрокидывается и на его выходе устанав-. ливается уровень логического О, т.е. устанавливается страничный режим работы оперативных запоминающих устройств, В этом режиме сигнал выборки строки (фиг.12 а) принимает уровень логического 0, фиксируя тем самым адрес строки в оперативных запоминающих устройствах блока 3 оперативной памяти.

При последующих запросах на цикл считывания в блоке 10 формирования сигналов выборки формируется только сигнал выборки столбцов (фиг,12 б), который фиксирует изменяющийся в счетчике адресов считывания адресный код столбцов считывания. В страничном режиме выборки энергопотребление блока оперативной памяти 3 определяется величиной (фиг.9 б), а временные диаграммы сигналов выборки строк и столбцов представлены соответственно на фиг.8 а и б. Окончание страничного режима происходит при переключении триггера 11 в исходное состояние сигналом с выхода элемента ИЛИ 13, поступающим на вход триггера 11.

Длительность страничного режима оперативньк запоминающих устройств

II

ограничивается максимальной длительностью сигнала выборки строк, равной

10МКС, с одной стороны и необхо- димостью выполнения автоматической регенерации содержимого блока 3 оперативной памяти с другой стороны. Поскольку регенерация производится перебором адресов строк, то за период регенерации оперативных запоминающих устройств (Тре 2 мкс) необходимо обратиться к всем строкам, Для этого на каждой строке телевизионного изображения длительностью 64 МКС необходимо перебрать не менее 4-5 адресов строк оперативного запоминающего устройства емкостью

16К и не менее 8-9 адресов строк оперативного запоминающего устройства емкостью 64К. Это означает, что с учетом ограничения на длительность сигнала выборки строк, оптимальной непрерьшной длительностью цикла считывания группы отсчетов (фиг.8) будет 7-8 МКС. Такие периоды формируются с помощью счетчика 33 адресов считывания и мультивибратора 37,. вход которого соединен с выходом соответствующего разряда счетчика 33. Сигнал с выхода мультивибратора 37 поступает на вход элемента ИЛИ 13 и далее на вход триггера 11, опрокидывая его. Страничный режим прекращается, сигнал выборки строк принимает уровень логической 1. Однако с приходом очередного импульса запроса на цикл считывания триггер

11вновь опрокидывается и восстанавливается страничный режим, в режиме считывания обеспечивается пониженное энергопотребление и автоматическая регенерация содержимого блока 3 оперативной памяти.

Запись входного видеосигнала производится следующим образом.

Во время строчного гасящего импульса вещательного стандарта, когда импульсы запроса на цикл считывания отсутствуют (фиг.10 б)коммутатор 22 пропускает на выход импульсы запроса на цикл записи непосредственно с выхода мультивибратора 21, что обеспечивается подачей на управляющий вход коммутатора 22 сигнала с выхода триггера 28. На прямом ходу строки, когда имеются импульсы запроса как на цикл считьюания, так и асинхронные с ними на цикл записи, происходит формирование импульсов

5624512

запроса на цикл записи, привязанных по времени к регулярно формируемым импульсам запроса на цикл считывания. При этом Импульс запроса 5 на цикл записи поступает на второй установочный вход триггера 20 и опро- кидьшает его, открывая элемент И 19 для прохождения импульса, сформированного с помощью мультивибратора

10 25, временное положение которого соответствует фиг.11 б. На прямом ходу строки этот импульс проходит через коммутатор 22 и является импульсом запроса на цикл записи, что

15 обеспечивает бесконфликтное поочередное формирование сигналов обращения к памяти. Сформированный таким образом импульс запроса на цикл записи поступает на установочный

20 вход триггера 40.

Во время строчного гасящего импульса, когда импульсы запроса на цикл считывания отсутствуют, работа блока 12 формирования сигналов об5 ращения соответствует фиг, 10 за ис-, ключением того, что сигнал цикла считывания (фиг.10 в) отсутствует, а появляется аналогичный сигнал цикла записи на прямом выходе триггера

0 40 (фиг.10 ж) и на выходе элемента И 43. На прямом ходу строки режим работы блока 12 формирования сигналов обращения представлен диаграммами на фиг.11. Выполнение цикла вы5 борки по импульсу запроса на цикл считывания (фиг.11 а) происходит аналогично описанному.

С приходом импульса запроса на цикл записи триггер 40 опрокидывает ся (фиг.11 г). Сигнал с инверсного выхода триггера 40 опрокидывает триггер 42, поскольку на его I и K-вxoдa:k имеется логическая 1, поступающая с прямого выхода триггера 39, и на прямом выходе триггера 42 появляется импульс (фиг.11 з), который определяет конец страничного режима считывания, чтобы дать возможность обращения к памяти в одном цикле записи. Сигнал с инверсного выхода триггера 42 закрывает элемент И 45, чтобы не допустить опрокидывания триггера 40 по первому импульсу окончания цикла выборки (фиг.11 ж). По этому импульсу опрокидываются только триггеры 39 и 42 (фиг.11 в) с этого момента на выходе элемента И 43 формируется сигнал цикла записи,а на выходе

131

элемента ИЖ 46 по-прежнему остается ,сигнал (фиг. 11 д) oбpaD eния к памяти.

После , окончания цикла записи в память вторым импульсом окончания цикла выборки (фиг. 11 ж)триггер 40 возвращается в исходное состояние, а импульсом с выхода элемента И 45 (фиг.10 и и 11 и) - триггер 20 блока 6 управления режимом записи. Таким образом, во время строчных гасящих импульсов вещательного стандарта цикл записи в блок 3 оперативной памяти в шолняется в момент поступления импульса запроса на цикл записи в блок 12 формирования сигналов обращения, а на прямом ходу строки цикл записи выполняется с прерыванием страничного режима считывания (фиг.12), обеспечивая характеристику энергопотребления блока 3 оперативной памяти, соответствующую предлагаемому устройству (фиг.9 в) по сравнению с изве стным: (фиг. 9 а).

Формула изобретения

Устройство для преобразования малокадрового телевизионного стандарта, содержащее последовательно соединенные аналого-цифровой преобразователь, первый блок буферной памяти и блок оперативной памяти, второй вход которого соединен с первьм выходом блока формирования адресных кодов, первый вход которого объединен с первым входом блока управления режимом записи и является входом синхросигнала устройства, цифроана- логовый преобразователь и блок управления режимом считывания, первый и второй выходы которого подключены соответственно к второму и третьему входам блока управления режимом записи, первый и второй выходы которого подключены соответственно к второ му и -третьему входам первого блока буферной памяти, причем вход аналого цифровогоIпреобразователя и выход 1Ц1фроа.налогового преобразователя яв

5624514

ляются соответственно входом и выходом устройства, отли-чающе- е с я тем, что, с целью снижения потребляемой мощности в него введе- 5 ны второй блок буферной памяти, включенный между выходом блока оперативной памяти и входом цифроаналогово- го преобразователя, второй и третий входы второго блока буферной памяти

0 соединены соответственно с третьим выходом и первьпч входом блока управления режимом считывания блок формирования сигналов обращения, элемент ИЛИ, триггер и блок формирования сиг 5 налов выборки, последовательно включенные между третьим выходом блока управления режимом записи и третьим входом блока оперативной памяти а также блок синхронизации, первьй

0 и второй выходы которого соединены соответственно с первым и вторым входами блока управления.режимом считывания, а третий и четвертый выходы блока синхронизации среди5 йены соответственно с вторым и третьим входами блока формирования адресных кодов, четвертый и пятый входы которого соединены соответственно с вторым и третьим выходами

0 блока формирования сигналов выбор35

40

45

ки, второй вход которого объединен с шестым входом блока формирования адресных кодов и соединен с вторым выходом блока формирования сигналов обращения, при зтом четвертый выход блока управления режимом считывания подключен к второму входу триггера и к второму входу блока формирования сигналов обращения, третий вход и третий выход которого соединены соответственно с четвертым выходом и третьим входом блока формирования сигналов выборки, четвертый выход блока формирования сигналов обращения подключен к четвертому входу блока управления режимом записи, а второй выход блока формирования адресных кодов подключен к второму входу элемента ИЛИ.

6}(0d1

6;foff2

77

BJTodJ

фиг. 2

7S

/ff

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования телевизионного стандарта | 1986 |

|

SU1343562A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Преобразователь телевизионного стандарта | 1981 |

|

SU1016850A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для формирования видеосигнала | 1986 |

|

SU1411808A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для отображения информации | 1989 |

|

SU1695373A1 |

Изобретение может использоваться для сопряжения скорости развертки малокадровых систем со скоростью развертки шфоковещательных телевизионных систем и обеспечивает снижение потребляемой мощности. Видеосигнал проходит через АЦП 1 и записывается по сигналам блока 6 управления режимом записи в первый блок 2 буферной памяти (ББП). В этом блоке происходит временное разуплотнение сигнала, которьй поступает на блок 3 оперативной памяти (БОИ). Разуплотнен- ньй цифровой сигнал считьтается из БОИ 3 в соответствии с адресными кодами считьюания, формируемыми блоком 7 формирования адресных кодов,и заносится во второй ББП 4. В этом блоке происходит временное уплотнение с целью формирования видеосигнала в соответствии с вещательным стандартом. С второго ББП 4 по сигналам блока 8 управления режимом считывания происходит считывание видео(feuTjaf (Л С

djroffe

BwdS

21

22

Bjfod4

/V

Su/jroc J

вЫ}Г0 1

«

3&/jfO J

Фиг. 8

СУ/

Цумы cvu/776/ёа- l uM записи ния

J

т

Л

JL

JL

фиг. 12

Составитель А. Прозоровский Редактор И. Шулла Техред М.Ходанич Корректор И.Мускэ

Заказ 4838/59 .Тираж 624Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

физ.П

Ц( CV(//776fScr U

S

т.

JL

JL

JL

Л t

| Устройство для преобразования теле-ВизиОННОгО СТАНдАРТА | 1979 |

|

SU813813A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Преобразователь телевизионного стандарта | 1981 |

|

SU1016850A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-09-07—Публикация

1985-04-08—Подача