1

Изобретение относится к вычислительной технике, автоматике и радиотехнике и может быть использовано как самостоятельное устройство или.в составе сложных фильтров.

Цель изобретения - повышение точности и расширение ,рабо«г го диапазона ЯСтот цифрового интегратора.

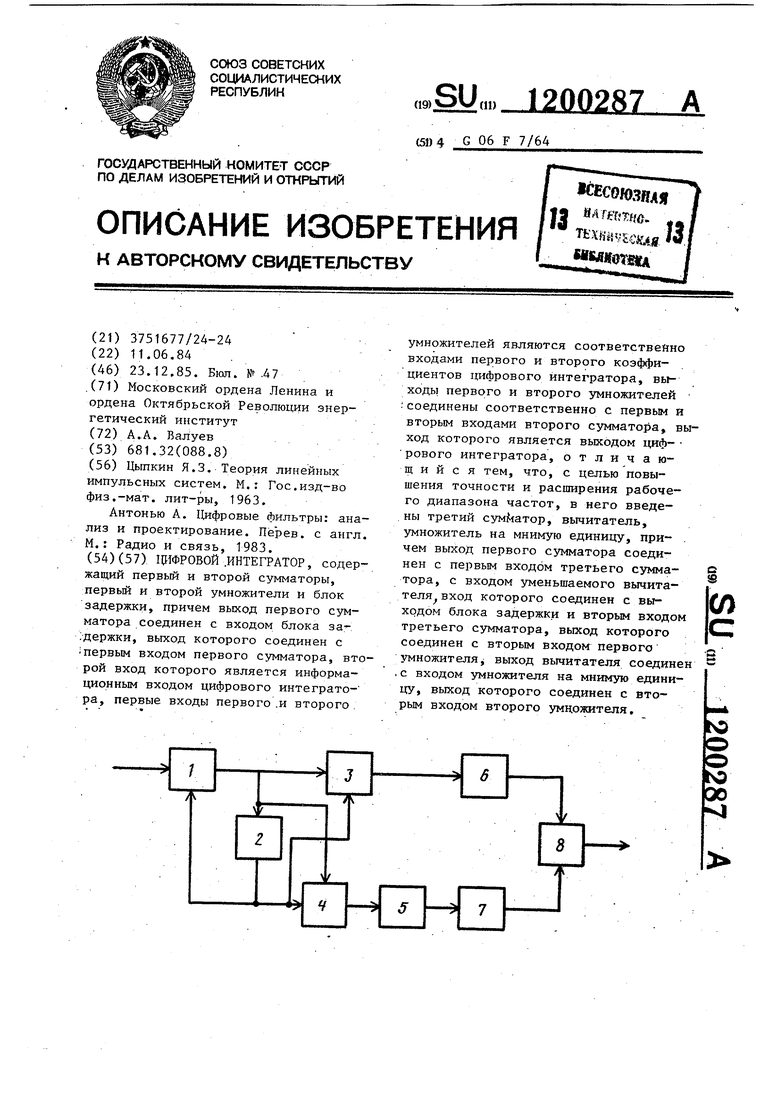

изображена ;функциональ ная схема цифрового ин -ёг ратора.

Инт -датор содержит йфвьй сумматор 1,,блок2 задержки, третий сумма тор 3,|вьгчит5теЛь; 4; умножитель 5 на мн,имую .единицу , первый 6 и второй 7 умножители, второй сумматор 8.

Предлагаемый интегратор реализует дискретную передаточную функцию следующего вида:

.0. QO

4uUl

-1

где Q.-ot-jpiao a 06 + J( ;

существенной особенностью которой является наличие комплексно-сопряженных коэффициентов а, и q , В итоге ФЧХ такого цифрового интегратора совпадает с ФЧХ аналогового интегратора гдеу9 )Т+2 srctg и( |i / ог ) м . Расширение рабочего диапазона нормированных частот за пределы, определяемые импульсной теоремой Котельникова, - важное свойство предлагаемого цифрового интегра тора. Нахождение ог тимальных значе200287 2

НИИ коэффициентов ot и и позволяет обеспечить также высокую степень близости АЧХ аналогового и предлагаемого цифрового интегратора.

5 Интегратор работает следующим образом.

Входная цифровая последовательность x)Ct), где tt kT; k 0,1, 2,..., поступает на вход сумматора 1, на выходе которого образуется последовательность W, поступающая на вход блока 2 задержки, на первый вход третьего сумматора 3 и на суммирующий вход Йычитателя 4.

15 С выхода .блока 2 задержки последовательность ц, .(значение w 0) . . ff .. . I .

поступает на вторые входы первого 1 и третьего 3 сумматоров и вычитающий вход вычитателя 4. В результате на

20 выходе сумматора 1 образуется после- довательность w х. На выходе сумматора 3 образуется последовательность v w + , которая поступает на второй вход умножителя 6. На выходе вычитателя образуется последовательность у w - W,., , которая поступает на вход умножителя 5 на мнимую единицу, и на его выходе пелучается по-1 1t/2

30 следовательность е у JVk которая поступает на второй вход умножителя 7. Коэффициенты ot и и поступают на первые входы соо тветственно умножителей 6 и 7. С выходов умно, жителей последовательности ; v и Л/5Ук поступают на первый и второй . выходы сумматора 9, который является выходом интегратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЛЕДЯЩИЙ ИЗМЕРИТЕЛЬ СКОРОСТИ СБЛИЖЕНИЯ | 1995 |

|

RU2087007C1 |

| Спектральный анализатор | 1977 |

|

SU789866A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Фурье-Чебышеву | 1983 |

|

SU1136181A1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| СПОСОБ ФОРМИРОВАНИЯ КВАДРАТУРНЫХ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 1999 |

|

RU2168281C2 |

| Устройство для вычисления быстрого преобразования фурье с основанием 4 | 1984 |

|

SU1185349A1 |

| Устройство для определения частотных характеристик линейных систем регулирования | 1976 |

|

SU648951A1 |

| ПЕЛЕНГАТОР | 1990 |

|

RU2006872C1 |

| Измеритель параметров фазочастотной характеристики четырехполюсников | 1983 |

|

SU1190306A2 |

| Устройство для определения спектральных коэффициентов разложения случайного процесса по функциям Хаара | 1980 |

|

SU935814A1 |

ЦИФРОВОЙ .ИНТЕГРАТОР, содержащий первый и второй сумматоры, первый и второй умножители и блок задержки, причем выход первого сумматора соединен с входом блока заг /держки, выход которого соединен с первым входом первого сумматора, второй вход которого является информационным входом цифрового интегратора, первые входы первого .и второго. умножителей являются соответствейно входами первого и второго коэффициентов цифрового интегратора, выходы первого и второго умножителей . соединены соответственно с первым и вторым входами второго сумматора, выход которого является выходом циф- рового интегратора, о т л и ч а rant и и с я тем, что, с целью повышения точности и расширения рабочего диапазона частот, в него введены третий cyM iaTop, вычитатель, умножитель на мнимую единицу, при- . чем выход первого сумматора соедиi нен с первым входом третьего сумматора, с входом уменьшаемого вычита- СЛ теля вход которого соединен с выходом блока задержки и вторым входом С третьего сумматора, выход которого соединен с вторым входом первого а умножителя выход вычитателя соединен Г ,с входом умножителя на мнимую единицу, выход которого соединен с вторым входом второго умножителя. ND о О 0 6 00 KJ

| Цыпкин Я,3, Теория линейных импульсных систем, М,: Гос,изд-во физ,-мат, лит-ры, 1963, Антонью А, Цифровые фильтры: анализ и проектирование, Пёрев, с англ, М,: Радио и связь, 1983, |

Авторы

Даты

1985-12-23—Публикация

1984-06-11—Подача