Область техники

Изобретение относится к области радиотехники, а более конкретно к способам и устройствам квадратурной демодуляции.

Уровень техники

Квадратурная демодуляция широко используется в системах связи и радиолокации, поскольку обеспечивает эффективное представление полосового сигнала и позволяет непосредственно оценить амплитуду и фазу сигнала. В настоящее время широко распространены аналоговые квадратурные демодуляторы.

Известно классическое решение аналогового квадратурного демодулятора (см. Digital signal processing in vlsi. Richard J. Higgins Georgia Institute of Technology. Prentice Hall. Englewood Cliffs, NJ 07632) [1], блок-схема которого изображена на фиг. 1.

Это устройство содержит:

1 - аналоговый квадратурный демодулятор,

2 - первый аналоговый фильтр низкой частоты (ФНЧ),

3 - второй аналоговый фильтр низкой частоты (ФНЧ),

4 - первый аналого-цифровой преобразователь (АЦП),

5 - второй аналого-цифровой преобразователь (АЦП),

6 - первый цифровой фильтр низкой частоты (ФНЧ),

7 - второй цифровой фильтр низкой частоты (ФНЧ).

Устройство (фиг. 1) работает следующим образом.

Входной сигнал демодулятора, расположенный на некоторой промежуточной частоте, подвергается аналоговому гетеродинированию - смешивается с двумя синусоидальными сигналами, сдвинутыми относительно друг друга на 90 градусов в двух независимых каналах. Выходные сигналы гетеродинов фильтруются аналоговыми фильтрами 2 и 3 для удаления побочных продуктов преобразования и внеполосных шумов и подаются на входы аналогово-цифровых преобразователей (АЦП) 4 и 5. Оцифрованный сигнал с выходов АЦП 4 и 5 фильтруется дополнительными цифровыми фильтрами 6 и 7.

Аналоговый квадратурный демодулятор (фиг. 1) обладает следующими недостатками:

- Шумы аналогового квадратурного преобразования (фазовые),

- Наличие двух аналоговых ФНЧ,

- Неидентичность характеристик (АЧХ и ФЧХ) аналоговых ФНЧ, приводящая к потере ортогональности выходных сигналов,

- Нелинейность фазо-частотной характеристики аналоговых ФНЧ,

- Наличие двух АЦП,

- Неидентичность характеристик (АЧХ) АЦП, приводящая к потере ортогональности выходных сигналов,

- Нестабильность параметров аналоговых узлов от температуры, приводящая к дисбалансу каналов,

- Необходимость коррекции постоянной составляющей в выходном сигнале,

- Высокие аппаратные затраты на цифровую фильтрацию (наличие двух цифровых ФНЧ).

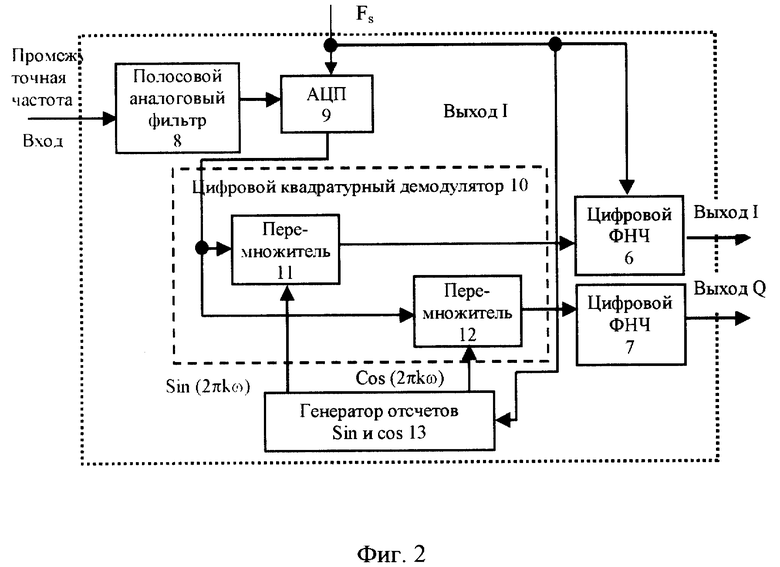

Известным решением для цифрового квадратурного демодулятора является устройство, описанное в патенте США N 05493581 Digital Down Converter AND Method. Int. C16 H 04 В 1/10, [2], блок-схема которого показана на фиг. 2.

Это устройство содержит:

8 - полосовой аналоговый фильтр,

9 - аналого-цифровой преобразователь (АЦП),

10 - цифровой квадратурный демодулятор, содержащий первый 11 и второй 12 цифровые перемножители,

6 - первый цифровой фильтр низкой частоты (ФНЧ),

7 - второй цифровой фильтр низкой частоты (ФНЧ),

13 - генератор отсчетов sin и cos.

Основными недостатками цифрового демодулятора являются

- шумы цифрового квадратурного преобразования (фазовые) при малой разрядности Sin и Cos отсчетов гетеродина, приводящие к потере ортогональности выходных сигналов;

- высокие аппаратные затраты на цифровое гетеродинирование (цифровые умножители);

- необходимость коррекции постоянной составляющей в выходном сигнале;

- высокие аппаратные затраты на цифровую фильтрацию (наличие двух цифровых ФНЧ).

Существуют и другие подходы к решению поставленной задачи, приводящие к сокращению аппаратных затрат при реализации устройства.

Наиболее близким техническим решением к предлагаемому изобретению является изобретение по патенту США N 5,504,455 "Efficient Digital Quadrature Demodulator", Int. Cl. H 03 D 3/00, [3], которое выполняет функцию квадратурного демодулятора, используя эффект гетеродинирования сигнала, расположенного на несущей частоте 0,25 Fs при его децимации.

Способ формирования квадратурных каналов по этому изобретению заключается в следующем:

1. Переносят спектр принимаемого сигнала на частоту ± 0,25 • Fs + n• Fs , где Fs - частота дискретизации, n= ..., - 2, -1, 0, 1, 2, ... - любое целое число.

2. Осуществляют дискретизацию и квантование входного сигнала.

3. Вычисляют N коэффициентов для фильтрации нижних частот вплоть до частоты Fs/8.

4. Разделяют поток отсчетов сигнала на два потока: поток четных отсчетов и поток нечетных отсчетов, переходя таким образом к частоте дискретизации  и перенося спектр сигнала на частоту

и перенося спектр сигнала на частоту

5. Вычисляют коэффициенты фильтрации четных отсчетов путем умножения коэффициентов фильтрации нижних частот на  и отбрасывания каждого второго отсчета, начиная со второго. Вычисляют коэффициенты фильтрации нечетных отсчетов путем умножения коэффициентов фильтрации нижних частот на

и отбрасывания каждого второго отсчета, начиная со второго. Вычисляют коэффициенты фильтрации нечетных отсчетов путем умножения коэффициентов фильтрации нижних частот на  и отбрасывания каждого второго отсчета, начиная с первого. Здесь

и отбрасывания каждого второго отсчета, начиная с первого. Здесь

6. Осуществляют фильтрацию верхних частот потоков четных и нечетных отсчетов, используя вычисленные коэффициенты фильтрации. Осуществляют децимацию каждого из фильтрованных потоков в два раза, перенося тем самым спектр сигнала на нулевую частоту. Квадратурный демодулятор согласно этому источнику содержит (см. фиг. 3):

8 - полосовой аналоговый фильтр,

9 - аналоговый цифровой преобразователь,

14 - коммутатор,

15 - квадратурный фильтр верхней частоты,

16 - синфазный фильтр верхней частоты,

17 и 18 - соответственно первый и второй действительные дециматоры, образующие комплексный дециматор 19.

Таким образом способ формирования квадратурных каналов и устройство для его реализации, описываемые в [3], предполагают, что сигнал с полосой B < Fs/4 расположен на частоте Fs/4. Выход АЦП 9 поочередно переключается на вход I и Q каналов таким образом, что четные отсчеты поступают на вход 1 канала, а нечетные - на вход Q канала. При этом осуществляют децимацию сигнала в два раза и переносят спектр сигнала на частоту Fs/2.

Полученный в результате указанного преобразования сигнал подается на входы фильтров верхних частот 15 и 16. Указанные фильтры получаются из фильтра нижних частот с полосой пропускания 0,25Fs. Коэффициенты фильтров высокой частоты (ФВЧ) получаются умножением коэффициентов фильтра нижних частот на отсчеты sin(kπ/2) и cos(kπ/2) для фильтров I и Q каналов соответственно и отбрасыванием нулевых отсчетов (децимацией). Выходной сигнал независимых каналов подвергается повторному прореживанию по времени - децимацией в 2 раза. При этом выходной сигнал устройства оказывается перенесенным на нулевую частоту и децимированным относительно входного сигнала в 4 раза.

Описанный прототип безусловно обладает преимуществами по сравнению с ранее описанными техническими решениями [1] и [2], к таким преимуществам можно отнести следующее:

- отсутствие постоянной составляющей в выходном сигнале,

- сокращено в два раза количество вычислений при фильтрации.

Однако существенными недостатками этого изобретения является то, что:

- выходная частота дискретизации оказывается в четыре раза ниже входной, при этом в некоторых системах связи требуется как минимум четырехкратная передискретизация для обеспечения временного слежения и, следовательно, при применении прототипа исходная частота дискретизации должна выбираться по крайней мере в 16 раз выше минимально возможной по теореме Котельникова (см. С.И.Баскаков. Радиотехнические цепи и сигналы. М. "Высшая школа". 1988, стр. 116-117) [4] , что приводит к резкому удорожанию аппаратуры и увеличению энергопотребления,

- первым каскадом устройства является дециматор, а поскольку предварительная цифровая фильтрация перед дециматором отсутствует, требования к предварительной аналоговой фильтрации ужесточаются в части повышения избирательности фильтра при тех же требованиях на его фазово-частотную характеристику, при этом в ряде случаев требования могут быть невыполнимы или слишком дороги при реализации, а при невыполнении требований устройство потеряет эффективность вследствие проникновения внеполосных помех в полосу полезного сигнала при децимации;

- предлагаемые в прототипе фильтры 15 и 16 не обеспечивают достаточной фильтрации для формирования канала, что вызывает необходимость в дополнительной цифровой фильтрации, а вследствие этого сохраняются высокие аппаратные затраты на цифровую фильтрацию (наличие двух цифровых ФНЧ);

- для получения лучшего соотношения сигнал-шум в полосе полезного сигнала необходимо брать максимально-возможную частоту дискретизации на этапе фильтрации, а в прототипе частота дискретизации в фильтрах равна Fs/2.

Сущность изобретения

Задачи, на решение которых направлены заявляемый способ формирования квадратурных каналов и устройство для его реализации (варианты), формулируются как:

- понижение требований к аналоговой фильтрации за счет сохранения частоты дискретизации в фильтрах Fs;

- сохранение выходной частоты дискретизации Fs;

- минимизация аппаратных затрат на реализацию канальных фильтров;

- минимизация аппаратных затрат на гетеродинирование сигнала;

- сохранение преимуществ прототипа в части отсутствия постоянной составляющей в выходном сигнале.

Решение этих задач в совокупности позволяет получить экономию ресурсов и улучшить основные технические характеристики.

Поставленная задача достигается за счет того, что:

В способ формирования квадратурных каналов по первому варианту, заключающийся в том, что переносят спектр принимаемого сигнала на частоту ± 0,25 • Fs + n • Fs, где Fs - частота дискретизации, n - любое целое число, осуществляют дискретизацию и квантование входного сигнала, вычисляют N коэффициентов для фильтрации нижних частот, осуществляют перенос спектра сигнала на нулевую частоту, дополнительно вводят следующую последовательность операций:

коэффициенты для фильтрации нижних частот вычисляют до частоты Ω, где  где B - полоса сигнала, а Ω выбирают, исходя из требований основной селекции,

где B - полоса сигнала, а Ω выбирают, исходя из требований основной селекции,

вычисляют комплексные коэффициенты фильтрации путем умножения вычисленных коэффициентов фильтрации нижних частот на  где

где

осуществляют основную селекцию сигнала с использованием вычисленных комплексных коэффициентов фильтрации, одновременно подавляя зеркальную копию спектра сигнала, относительно нулевой частоты,

в каждом втором комплексном отсчете меняют местами реальную и мнимую части, после чего для каждой четверки отсчетов меняют на противоположный знак реальной части второго и третьего и знак мнимой части третьего и четвертого отсчетов, осуществляя таким образом перенос спектра сигнала на нулевую частоту,

причем коэффициенты для фильтрации нижних частот вычисляют любым известным способом, например способом Фурье.

В способ формирования квадратурных каналов по второму варианту, заключающийся в том, что переносят спектр принимаемого сигнала на частоту ± 0,25 • Fs + n • Fs, где Fs - частота дискретизации, n - любое целое число, осуществляют дискретизацию и квантование входного сигнала, вычисляют N коэффициентов для фильтрации нижних частот, осуществляют перенос спектра сигнала на нулевую частоту путем децимации, дополнительно вводят следующую последовательность операций:

вычисляют коэффициенты для фильтрации нижних частот до частоты Ω, где  где B - полоса сигнала, a Ω выбирают, исходя из требований основной селекции,

где B - полоса сигнала, a Ω выбирают, исходя из требований основной селекции,

вычисляют комплексные коэффициенты фильтрации путем умножения вычисленных коэффициентов фильтрации нижних частот на  где

где  осуществляют основную селекцию сигнала с использованием вычисленных комплексных коэффициентов фильтрации, одновременно подавляя зеркальную копию спектра сигнала, относительно нулевой частоты,

осуществляют основную селекцию сигнала с использованием вычисленных комплексных коэффициентов фильтрации, одновременно подавляя зеркальную копию спектра сигнала, относительно нулевой частоты,

осуществляют четырехкратную децимацию сигнала,

причем коэффициенты для фильтрации нижних частот вычисляют любым известным способом, например способом Ремеза.

Эта задача решается также за счет того, что в устройство формирования квадратурных каналов по первому варианту, содержащее последовательно соединенные полосовой аналоговый фильтр и аналого-цифровой преобразователь, а также блок коммутации, при этом вход полосового аналогового фильтра является первым, информационным, входом устройства, второй вход аналого-цифрового преобразователя и первый вход блока коммутации объединены, образуя второй вход устройства, который является входом тактовой частоты дискретизации сигнала.

Дополнительно вводят следующие отличительные признаки:

введены полосовой комплексный фильтр, первый вход которого соединен с выходом аналого-цифрового преобразователя, второй вход подключен ко второму входу устройства, первый и второй выходы полосового комплексного фильтра соединены соответственно со вторым и третьим входами блока коммутации,

блок коммутации содержит первый и второй инверторы, двоичный счетчик и мультиплексор, при этом первый и третий входы мультиплексора и входы первого и второго инвертора объединены и являются соответственно первым и вторым входами блока коммутации, выход первого инвертора подключен ко второму входу мультиплексора, четвертый вход которого соединен с выходом второго инвертора, пятый вход мультиплексора соединен с выходом двоичного счетчика, вход которого является первым входом блока коммутации, первый и второй выходы мультиплексора являются выходами блока коммутации и соответственно первым и вторым выходами устройства.

Эта задача решается также за счет того, что в устройство формирования квадратурных каналов по второму варианту, содержащее последовательно соединенные полосовой аналоговый фильтр и аналого-цифровой преобразователь, а также комплексный дециматор, образованный первым и вторым действительными дециматорами, при этом вход полосового аналогового фильтра является первым, информационным, входом устройства, второй вход аналого-цифрового преобразователя и первый вход комплексного дециматора объединены, образуя второй вход устройства, который является входом тактовой частоты дискретизации сигнала, первый и второй выходы комплексного дециматора являются соответственно первым и вторым выходами устройства, дополнительно вводят следующие отличительные признаки:

введен полосовой комплексный фильтр,

первый вход полосового комплексного фильтра соединен с выходом аналого-цифрового преобразователя,

второй вход полосового комплексного фильтра подключен ко второму входу устройства,

первый и второй выходы полосового комплексного фильтра подключены соответственно ко второму и третьему входам комплексного дециматора.

Первый и второй варианты реализации заявляемого устройства позволяют решить поставленную задачу и получить эквивалентный эффект.

Для заявляемой структуры вариантов исполнения устройства предлагаются два варианта выполнения полосового комплексного фильтра (для фильтра любого порядка (общий случай) и нечетного порядка с симметричными значениями действительной части коэффициентов и антисимметричными значениями мнимой части коэффициентов).

Полосовой комплексный фильтр по первому варианту содержит линию задержки, содержащую N последовательно соединенных элементов задержки, первый вход линии задержки является первым входом полосового комплексного фильтра, а N выходов линии задержки соединены с соответствующими им N перемножителями, выходы каждого из N нечетного перемножителя подключены к первому сумматору, выходы каждого из N четного перемножителя подключены ко второму сумматору, выход первого сумматора соединен с первым входом первого регистра, выход которого является первым выходом устройства, образуя реальную часть комплексного выходного сигнала полосового комплексного фильтра, выход второго сумматора соединен с первым входом второго регистра, выход которого является вторым выходом устройства, образуя мнимую часть комплексного выходного сигнала полосового комплексного фильтра, второй вход линии задержки и вторые входы первого и второго регистров объединены и являются вторым входом полосового комплексного фильтра.

Полосовой комплексный фильтр нечетного порядка с симметричными значениями действительной части коэффициентов и антисимметричными значениями мнимой части коэффициентов, по второму варианту, содержит последовательно соединенные первую и вторую линии задержки, каждая из которых содержит по (N+1)/2 последовательно соединенных элементов задержки, ветвь вычисления реальной части сигнала, которая содержит последовательно соединенные М сумматоров и соответственно им М перемножителей и последовательно соединенные выходной сумматор и регистр, выход которого является первым выходом полосового комплексного фильтра, образующим реальную часть комплексного выходного сигнала, ветвь вычисления мнимой части сигнала, которая содержит последовательно соединенные L вычитателей и соответственно им L перемножителей и последовательно соединенные выходной сумматор и регистр, выход которого является вторым выходом полосового комплексного фильтра, образующим мнимую часть комплексного выходного сигнала, первый вход первой линии задержки является первым входом полосового комплексного фильтра, вторые входы первой и второй линий задержки, вторые входы первого и второго регистров объединены и являются вторым входом полосового комплексного фильтра, нечетные выходы первой и второй линий задержки соединены с соответствующими им входами сумматоров ветви вычисления реальной части сигнала, четные выходы первой и второй линий задержки соединены с соответствующими им входами вычитателей ветви вычисления мнимой части сигнала.

Так как операцию переноса спектра сигнала на нулевую частоту в вариантах способа осуществляют различным путем, то для реализации способа по первому варианту, когда осуществляют комплексное гетеродинирование с сохранением частоты дискретизации, используют в устройстве полосовой комплексный фильтр (любой из предложенных вариантов исполнения) и блок коммутации, выполненные описанным способом.

А для реализации способа по второму варианту, когда осуществляют четырехкратную децимацию с понижением частоты дискретизации, используют в устройстве полосовой комплексный фильтр (любой из предложенных вариантов исполнения) и комплексный дециматор.

Сопоставительный анализ заявляемого способа формирования квадратурных каналов и устройства для его реализации по первому и второму вариантам с прототипом показывает, что заявляемые технические решения отличаются новой последовательностью введенных существенных признаков изобретения, которые позволяют решить актуальную задачу для технических решений данного класса, т. е. сохранить частоту дискретизации в фильтрах Fs, понижая тем самым требования на аналоговую фильтрацию, сохранить выходную частоту дискретизации Fs, минимизировать аппаратные затраты на реализацию канальных фильтров, минимизировать аппаратные затраты на гетеродинирование сигнала, сохранить преимущества в части отсутствия постоянной составляющей в выходном сигнале, что в совокупности позволяет получить экономию ресурсов и улучшить основные технические характеристики.

Перечень фигур чертежей

Описание изобретения поясняется графическими материалами.

На фиг. 1 показана блок-схема аналогового квадратурного демодулятора (аналог).

На фиг. 2 изображена блок-схема цифрового квадратурного демодулятора (аналог).

На фиг. 3 показана блок-схема цифрового квадратурного демодулятора (прототип).

На фиг. 4 - устройство формирования квадратурных каналов по первому варианту (заявляемое устройство).

На фиг. 5 - устройство формирования квадратурных каналов по второму варианту (заявляемое устройство).

На фиг. 6 - блок-схема полосового комплексного фильтра, приведена как пример реализации в структуре заявляемого устройства и по первому, и по второму вариантам исполнения.

На фиг. 7 - блок-схема полосового комплексного фильтра нечетного порядка с симметричными значениями действительной части коэффициентов и антисимметричными значениями мнимой части коэффициентов, приведена как пример реализации в структуре заявляемого устройства и по первому, и по второму вариантам исполнения.

На фиг. 8 - показана блок-схема блока коммутации (для заявляемого устройства по первому варианту). В конце описания приведена таблица переключения мультиплексора (поясняющая работу блока коммутации 14).

Сведения, подтверждающие возможность осуществления изобретения.

Для реализации заявляемого способа используют, например, устройство формирования квадратурных каналов по первому варианту (фиг. 4), которое содержит: последовательно соединенные полосовой аналоговый фильтр 8 и аналого-цифровой преобразователь 9, блок коммутации 14, при этом вход полосового аналогового фильтра 8 является первым, информационным, входом устройства, второй вход аналого-цифрового преобразователя 9 и первый вход блока коммутации 14 объединены, образуя второй вход устройства, который является входом тактовой частоты дискретизации сигнала, полосовой комплексный фильтр 20, первый вход которого соединен с выходом аналого-цифрового преобразователя 9, второй вход подключен ко второму входу устройства, первый и второй выходы полосового комплексного фильтра 20 соединены соответственно со вторым и третьим входами блока коммутации 14, блок коммутации 14 (фиг. 8) содержит первый 41 и второй 42 инверторы, двоичный счетчик 43 и мультиплексор 44, при этом первый и третий входы мультиплексора 44 и входы первого 41 и второго 42 инверторов объединены и являются соответственно вторым и третьим входами блока коммутации 14, выход первого 41 инвертора подключен ко второму входу мультиплексора 44, четвертый вход которого соединен с выходом второго инвертора 42, пятый вход мультиплексора 44 соединен с выходом двоичного счетчика 43, вход которого является первым входом блока коммутации и подключен ко второму входу устройства, первый и второй выходы мультиплексора 44 являются выходами блока коммутации 14 и соответственно первым и вторым выходами устройства.

Для реализации заявляемого способа может быть также использовано устройство формирования квадратурных каналов по второму варианту (фиг. 5), которое содержит: последовательно соединенные полосовой аналоговый фильтр 8 и аналого-цифровой преобразователь 9, а также комплексный дециматор 19, образованный первым и вторым действительными дециматорами, при этом вход полосового аналогового фильтра 8 является первым, информационным, входом устройства, второй вход аналого-цифрового преобразователя 9 и первый вход комплексного дециматора 19 объединены, образуя второй вход устройства, который является входом тактовой частоты дискретизации сигнала, первый и второй выходы комплексного дециматора 19 являются соответственно первым и вторым выходами устройства, полосовой комплексный фильтр 20, первый вход которого соединен с выходом аналого-цифрового преобразователя 9, второй вход подключен ко второму входу устройства, а первый и второй выходы подключены соответственно ко второму и третьему входам комплексного дециматора 19.

Полосовой комплексный фильтр (фиг. 6) содержит линию задержки 21, содержащую N последовательно соединенных элементов задержки, первый вход линии задержки 21 является первым входом полосового комплексного фильтра 20, а N выходов линии задержки соединены с соответствующими им N перемножителями 22-1 - 22-N, выходы каждого из N нечетного перемножителя подключены к первому сумматору 23, выходы каждого из N четного перемножителя подключены ко второму сумматору 25, выход первого сумматора 23 соединен с первым входом первого регистра 24, выход которого является первым выходом устройства, образуя реальную часть комплексного выходного сигнала полосового комплексного фильтра 20, выход второго сумматора 25 соединен с первым входом второго регистра 26, выход которого является вторым выходом устройства, образуя мнимую часть комплексного выходного сигнала полосового комплексного фильтра 20, второй вход линии задержки 21 и вторые входы первого 24 и второго 26 регистров объединены и являются вторым входом полосового комплексного фильтра 20.

Полосовой комплексный фильтр 20 нечетного порядка с симметричными значениями действительной части коэффициентов и антисимметричными значениями мнимой части коэффициентов (фиг. 7) содержит последовательно соединенные первую 27 и вторую 29 линии задержки, каждая из которых содержит по (N+1)/2 последовательно соединенных элементов задержки, соответственно 28-1 - 28-(N+1)/2 и 30-1 - 30-(N+1)/2 ветвь вычисления реальной части сигнала 31, которая содержит последовательно соединенные М сумматоров 32-1 - 32-М и соответственно им М перемножителей 33-1 - 33-М и последовательно соединенные выходной сумматор 34 и регистр 35, выход которого является первым выходом полосового комплексного фильтра 20, образующим реальную часть комплексного выходного сигнала, ветвь вычисления мнимой части сигнала 36, которая содержит последовательно соединенные L вычитателей 37-1 - 37-L и соответственно им L перемножителей 38-1 - 38-L и последовательно соединенные выходной сумматор 39 и регистр 40, выход которого является вторым выходом полосового комплексного фильтра 20, образующим мнимую часть комплексного выходного сигнала, первый вход первой 27 линии задержки является первым входом полосового комплексного фильтра 20, вторые входы первой 27 и второй 29 линий задержки, вторые входы первого 35 и второго 40 регистров объединены и являются вторым входом полосового комплексного фильтра 20, нечетные выходы первой 27 и второй 29 линий задержки соединены с соответствующими им входами сумматоров 32-1 - 32-М ветви вычисления реальной части сигнала 31, четные выходы первой 27 и второй 29 линий задержки соединены с соответствующими им входами вычитателей 37-1 - 37-L ветви вычисления мнимой части сигнала 36.

При формировании ветвей вычисления реальной и мнимой частей сигнала должно быть соблюдено следующее равенство: M+L = (N+1)/2, а M=L+1.

Способ формирования квадратурных каналов по первому варианту реализуют, используя устройство, блок-схема которого показана на фиг. 4.

Предполагается, что входной действительный сигнал с полосой не более Fs/2 расположен на любой из несущих частот ωн ± 0,25 • Fs + n•Fs, где Fs - частота дискретизации, n - любое целое число, осуществляют дискретизацию и квантование входного сигнала.

Затем входной сигнал подвергают полосовой аналоговой фильтрации в блоке 8 для подавления частотных составляющих сигнала, лежащих вне полосы [ωн-0,5Fs; ωн+0,5Fs].

Выполняют аналого-цифровое преобразование сигнала в блоке 9.

Осуществляют комплексную полосовую фильтрацию в блоке 20. Пример реализации полосового комплексного фильтра приведен на фиг. 6 и 7.

Для полосового комплексного фильтра (фиг. 6) отсчеты входного сигнала, хранящиеся в линии задержки 21, умножаются на отсчеты импульсной характеристики комплексного фильтра. Сумматор 23 суммирует результаты перемножения на реальную часть комплексных отсчетов импульсной характеристики фильтра.

Сумматор 25 соответственно суммирует результаты перемножения на мнимую часть комплексных отсчетов импульсной характеристики фильтра.

Результаты суммирования записывают соответственно в регистры 24 и 26.

Выходной сигнал регистров представляет собой выходной комплексный сигнал полосового комплексного фильтра 20 на блок коммутации 14.

Для полосового комплексного фильтра 20 нечетного порядка с симметричными значениями действительной части коэффициентов и антисимметричными значениями мнимой части коэффициентов (фиг. 7) отсчеты входного сигнала, хранящиеся в линиях задержки 27 и 29, попарно суммируются следующим образом. Для вычисления реальной части сигнала используют сумматоры 32-1 - 32-М, на входы которых поступают отсчеты сигнала с нечетных элементов первой 27 и второй 29 линий задержки и умножаются на реальную часть комплексных отсчетов импульсной характеристики фильтра. Результаты умножения суммируются в выходном сумматора 34, записываются в регистр 35.

Для вычисления мнимой части сигнала используют вычитатели 37-1 - 37-L, на входы которых поступают отсчеты сигнала с четных элементов первой 27 и второй 29 линий задержки и умножаются на мнимую часть комплексных отсчетов импульсной характеристики фильтра. Результаты умножения суммируются в выходном сумматора 39, записываются в регистр 40. Следует отметить, что вычитатели 37-1 - 37-L должны быть подключены следующим образом. Каждый нечетный вычитатель осуществляет вычитание отсчета сигнала второй линии задержки 29 из отсчета сигнала первой линии задержки 27. А каждый четный вычитатель - наоборот.

Выходной сигнал регистров 35 и 40 представляет собой выходной комплексный сигнал полосового комплексного фильтра 20 на блок коммутации 14.

Отсчеты импульсной характеристики полосового комплексного фильтра вычисляют следующим образом. Вычисляют N коэффициентов фильтрации нижних частот, причем коэффициенты для фильтрации нижних частот вычисляют любым известным способом, например способом Фурье.

Коэффициенты для фильтрации нижних частот вычисляют до частоты Ω, где  где B - полоса сигнала, a Ω выбирают, исходя из требований основной селекции. Если количество полученных коэффициентов - порядок фильтра четно или коэффициенты несимметричны относительно центрального коэффициента (при нечетном порядке), то следует использовать блок-схему полосового комплексного фильтра 20 (фиг. 6).

где B - полоса сигнала, a Ω выбирают, исходя из требований основной селекции. Если количество полученных коэффициентов - порядок фильтра четно или коэффициенты несимметричны относительно центрального коэффициента (при нечетном порядке), то следует использовать блок-схему полосового комплексного фильтра 20 (фиг. 6).

Если количество полученных коэффициентов - порядок фильтра нечетно и коэффициенты симметричны относительно центрального коэффициента, то следует использовать блок-схему полосового комплексного фильтра 20 (фиг. 7).

Вычисляют комплексные коэффициенты фильтрации путем умножения вычисленных коэффициентов фильтрации нижних частот на  где

где

Полученные коэффициенты фильтрации K1...Кn являются импульсной характеристикой полосового комплексного фильтра 20 и используются в перемножителях 22-1 - 22-N (фиг. 6). Полученные коэффициенты фильтрации  используются в перемножителях 33-1 - 33-М - 38-1 - 38 L (см. фиг. 7).

используются в перемножителях 33-1 - 33-М - 38-1 - 38 L (см. фиг. 7).

Таким образом осуществляют основную селекцию сигнала с использованием вычисленных комплексных коэффициентов фильтрации, одновременно подавляя зеркальную копию спектра сигнала, относительно нулевой частоты.

В блоке коммутации 14 в каждом входном втором комплексном отсчете меняют местами действительную и мнимую части, после чего для каждой четверки отсчетов меняют на противоположный знак действительной части второго и третьего и знак мнимой части третьего и четвертого отсчетов, осуществляя таким образом перенос спектра сигнала на нулевую частоту. Для выполнения этих операций используют первый 41 и второй 42 инверторы, двоичный счетчик 43 и мультиплексор 44 (четыре в одном направлении). Мультиплексор работает в соответствии с таблицей переключения.

Способ формирования квадратурных каналов по второму варианту реализуют, используя устройство, блок-схема которого показана на фиг. 5.

Предполагается, что входной действительный сигнал с полосой не более Fs/2 расположен на любой из несущих частот ωн ± 0,25 • Fs + n • Fs, где Fs - частота дискретизации, n - любое целое число, осуществляют дискретизацию и квантование входного сигнала. Затем входной сигнал подвергают полосовой аналоговой фильтрации в блоке 8 для подавления частотных составляющих сигнала, лежащих вне полосы

[ωн-0,5Fs; ωн+0,5Fs].

Выполняют аналого-цифровое преобразование сигнала в блоке 9.

Осуществляют комплексную полосовую фильтрацию в блоке 20. Пример реализации полосового комплексного фильтра для нечетного и четного порядка приведен на фиг. 6 и 7.

Для полосового комплексного фильтра (фиг. 6) отсчеты входного сигнала, хранящиеся в линии задержки 21, умножаются на отсчеты импульсной характеристики комплексного фильтра. Сумматор 23 суммирует результаты перемножения на реальную часть комплексных отсчетов импульсной характеристики фильтра.

Сумматор 25 соответственно суммирует результаты перемножения на мнимую часть комплексных отсчетов импульсной характеристики фильтра.

Результаты суммирования записывают соответственно в регистры 24 и 26.

Выходной сигнал регистров представляет собой выходной комплексный сигнал полосового комплексного фильтра 20 на блок коммутации 14.

Для полосового комплексного фильтра 20 нечетного порядка с симметричными значениями действительной части коэффициентов и антисимметричными значениями мнимой части коэффициентов (фиг. 7) отсчеты входного сигнала, хранящиеся в линиях задержки 27 и 29, попарно суммируются следующим образом. Для вычисления реальной части сигнала используют сумматоры 32-1 - 32-М, на входы которых поступают отсчеты сигнала с нечетных элементов первой 27 и второй 29 линий задержки и умножаются на реальную часть комплексных отсчетов импульсной характеристики фильтра. Результаты умножения суммируются в выходном сумматоре 34, записываются в регистр 35.

Для вычисления мнимой части сигнала используют вычитатели 37-1 - 37-L, на входы которых поступают отсчеты сигнала с четных элементов первой 27 и второй 29 линий задержки и умножаются на мнимую часть комплексных отсчетов импульсной характеристики фильтра. Результаты умножения суммируются в выходном сумматора 39, записываются в регистр 40. Следует отметить, что вычитатели 37-1 - 37-L должны быть подключены следующим образом. Каждый нечетный вычитатель осуществляет вычитание отсчета сигнала второй линии задержки 29 из отсчета сигнала первой линии задержки 27. А каждый четный вычитатель - наоборот.

Выходной сигнал регистров 35 и 40 представляет собой выходной комплексный сигнал полосового комплексного фильтра 20 на комплексный дециматор 19.

Отсчеты импульсной характеристики полосового комплексного фильтра вычисляют следующим образом. Вычисляют N коэффициентов фильтрации нижних частот, причем коэффициенты для фильтрации нижних частот вычисляют любым известным способом, например способом Ремеза.

Коэффициенты для фильтрации нижних частот вычисляют до частоты Ω, где  где B - полоса сигнала, a Ω выбирают, исходя из требований основной селекции. Если количество полученных коэффициентов - порядок фильтра четно или коэффициенты несимметричны относительно центрального коэффициента (при нечетном порядке), то следует использовать блок-схему полосового комплексного фильтра 20 (фиг. 6).

где B - полоса сигнала, a Ω выбирают, исходя из требований основной селекции. Если количество полученных коэффициентов - порядок фильтра четно или коэффициенты несимметричны относительно центрального коэффициента (при нечетном порядке), то следует использовать блок-схему полосового комплексного фильтра 20 (фиг. 6).

Если количество полученных коэффициентов - порядок фильтра нечетно и коэффициенты симметричны относительно центрального коэффициента, то следует использовать блок-схему полосового комплексного фильтра 20 (фиг. 7).

Вычисляют комплексные коэффициенты фильтрации путем умножения вычисленных коэффициентов фильтрации нижних частот на  где

где

Полученные коэффициенты фильтрации K1... Kn являются импульсной характеристикой полосового комплексного фильтра 20 и используются в перемножителях 22-1 - 22-N (фиг. 6). Полученные коэффициенты фильтрации  используются в перемножителях 33-1 - 33-М - 38-1 - 38 L (см. фиг. 7).

используются в перемножителях 33-1 - 33-М - 38-1 - 38 L (см. фиг. 7).

Таким образом осуществляют основную селекцию сигнала с использованием вычисленных комплексных коэффициентов фильтрации, одновременно подавляя зеркальную копию спектра сигнала, относительно нулевой частоты.

В комплексном дециматоре 19 осуществляют четырехкратную децимацию сигнала.

Заявляемые способ формирования квадратурных каналов и устройство для его реализации (варианты) по сравнению с известными техническими решениями в данной области техники позволяют получить следующие преимущества.

Например, сравним с аналогом (фиг. 2), который содержит комплексный перемножитель и два фильтра низких частот с действительными коэффициентами.

Положим количество коэффициентов фильтра равным N. Тогда для обработки одного отсчета входного сигнала требуется выполнить

действительных умножений и

действительных сложений. Полагая одно действительное умножение или сложение одной элементарной вычислительной операцией, определим общее число элементарных операций в общепринятой схеме равным 6+4 • N.

Заявляемое изобретение не содержит комплексного перемножителя.

Полосовой комплексный фильтр, используемый в нашей блок-схеме, строится путем умножения действительных отсчетов исходного фильтра нижней частоты на отсчеты комплексной экспоненты ej•0,25•2π•i, где

Следует отметить, что в нашем случае все четные отсчеты в действительной части и все нечетные отсчеты в мнимой части полученного комплексного полосового фильтра обращаются в ноль, что примерно в два раза сокращает общее количество требуемых умножений при практической реализации. При этом для обработки одного отсчета входного сигнала требуется выполнить  действительных умножений и столько же действительных сложений, т.е.

действительных умножений и столько же действительных сложений, т.е.  вычислительных операций. Таким образом, предлагаемое изобретение позволяет более чем в два раза сократить количество требуемых вычислений.

вычислительных операций. Таким образом, предлагаемое изобретение позволяет более чем в два раза сократить количество требуемых вычислений.

Таким образом, заявляемые способ формирования квадратурных каналов и устройство для его реализации (варианты) обладают существенными преимуществами по сравнению с известными техническими решениями и позволяют:

- сохранить частоту дискретизации в фильтрах Fs, понижая тем самым требования на аналоговую фильтрацию,

- сохранить выходную частоту дискретизации Fs,

- минимизировать аппаратные затраты на реализацию канальных фильтров,

- минимизировать аппаратные затраты на гетеродинирование сигнала,

- сохранить преимущества в части отсутствия постоянной составляющей в выходном сигнале,

что в совокупности позволяет получить экономию ресурсов и улучшить основные технические характеристики.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| МНОГОКАНАЛЬНЫЙ ПЕРЕПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ПРИЕМНЫЙ ТРАКТ | 2004 |

|

RU2289202C2 |

| СПОСОБ ЧАСТОТНО-ВРЕМЕННОЙ СИНХРОНИЗАЦИИ СИСТЕМЫ СВЯЗИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2003 |

|

RU2304359C2 |

| СПОСОБ ФОРМИРОВАНИЯ ДИАГРАММЫ НАПРАВЛЕННОСТИ | 2011 |

|

RU2495447C2 |

| СПОСОБ ВЫРАВНИВАНИЯ КАНАЛОВ МНОГОКАНАЛЬНОЙ ПРИЕМНОЙ СИСТЕМЫ (ВАРИАНТЫ) | 2004 |

|

RU2289885C2 |

| ЦИФРОВОЙ OFDM ДЕМОДУЛЯТОР С ДЕЦИМАЦИЕЙ ЧАСТОТЫ ДИСКРЕТИЗАЦИИ | 2017 |

|

RU2644609C1 |

| СПОСОБ ПРИЕМА МНОГОЛУЧЕВОГО СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2297713C2 |

| Устройство формирования и обработки широкополосных сигналов | 2018 |

|

RU2691733C1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| Цифровое устройство преобразования групповых сигналов систем связи с частотным разделением каналов | 1983 |

|

SU1145485A1 |

Изобретение относится к области радиотехники и может использоваться в системах связи и радиолокации. Способ формирования квадратурных каналов характеризуется тем, что переносят спектр принимаемого сигнала на требуемую частоту, осуществляют дискретизацию и квантование входного сигнала, вычисляют коэффициенты для фильтрации, осуществляют перенос спектра на нулевую частоту. Устройство формирования квадратурных каналов содержит аналоговый фильтр, аналого-цифровой преобразователь, блок коммутации и полосовой комплексный фильтр. Устройство формирования квадратурных каналов (варианты) содержит полосовой аналоговый фильтр, аналого-цифровой преобразователь, комплексный дециматор, полосовой комплексный фильтр. Достигаемый технический результат - снижение требований к аналоговой фильтрации при сохранении частоты дискретизации, минимизация аппаратных затрат. 4 с. и 6 з.п. ф-лы, 8 ил., 1 табл.

где k = 0, N - 1,

осуществляют основную селекцию сигнала с использованием вычисленных комплексных коэффициентов фильтрации, одновременно подавляя зеркальную копию спектра сигнала, относительно нулевой частоты, в каждом втором комплексном отсчете меняют местами реальную и мнимую части, после чего для каждой четверки отсчетов меняют на противоположный знак реальной части второго и третьего и знак мнимой части третьего и четвертого отсчетов, осуществляя таким образом перенос спектра сигнала на нулевую частоту.

где k = 0, N - 1,

осуществляют основную селекцию сигнала с использованием вычисленных комплексных коэффициентов фильтрации, одновременно подавляя зеркальную копию спектра сигнала, относительно нулевой частоты, осуществляют четырехкратную децимацию. последовательно соединенных элементов задержки, ветвь вычисления реальной части сигнала, которая содержит последовательно соединенные М сумматоров и соответственно им М перемножителей и последовательно соединенные выходной сумматор и регистр, выход которого является первым выходом полосового комплексного фильтра, образующим реальную часть комплексного выходного сигнала, ветвь вычисления мнимой части сигнала, которая содержит последовательно соединенные L вычитателей и соответственно им L перемножителей и последовательно соединенные выходной сумматор и регистр, выход которого является вторым выходом полосового комплексного фильтра, образующим мнимую часть комплексного выходного сигнала, первый вход первой линии задержки является первым входом полосового комплексного фильтра, вторые входы первой и второй линий задержки, вторые входы первого и второго регистров объединены и являются вторым входом полосового комплексного фильтра, нечетные выходы первой и второй линий задержки соединены с соответствующими им входами сумматоров ветви вычисления реальной части сигнала, четные выходы первой и второй линий задержки соединены с соответствующими им входами вычитателей ветви вычисления мнимой части сигнала.

последовательно соединенных элементов задержки, ветвь вычисления реальной части сигнала, которая содержит последовательно соединенные М сумматоров и соответственно им М перемножителей и последовательно соединенные выходной сумматор и регистр, выход которого является первым выходом полосового комплексного фильтра, образующим реальную часть комплексного выходного сигнала, ветвь вычисления мнимой части сигнала, которая содержит последовательно соединенные L вычитателей и соответственно им L перемножителей и последовательно соединенные выходной сумматор и регистр, выход которого является вторым выходом полосового комплексного фильтра, образующим мнимую часть комплексного выходного сигнала, первый вход первой линии задержки является первым входом полосового комплексного фильтра, вторые входы первой и второй линий задержки, вторые входы первого и второго регистров объединены и являются вторым входом полосового комплексного фильтра, нечетные выходы первой и второй линий задержки соединены с соответствующими им входами сумматоров ветви вычисления реальной части сигнала, четные выходы первой и второй линий задержки соединены с соответствующими им входами вычитателей ветви вычисления мнимой части сигнала. последовательно соединенных элементов задержки, ветвь вычисления реальной части сигнала, которая содержит последовательно соединенные М сумматоров и соответственно им М перемножителей и последовательно соединенные выходной сумматор и регистр, выход которого является первым выходом полосового комплексного фильтра, образующим реальную часть комплексного выходного сигнала, ветвь вычисления мнимой части сигнала, которая содержит последовательно соединенные L вычитателей и соответственно им L перемножителей и последовательно соединенные выходной сумматор и регистр, выход которого является вторым выходом полосового комплексного фильтра, образующим мнимую часть комплексного выходного сигнала, первый вход первой линии задержки является первым входом полосового комплексного фильтра, вторые входы первой и второй линий задержки, вторые входы первого и второго регистров объединены и являются вторым входом полосового комплексного фильтра, нечетные выходы первой и второй линий задержки соединены с соответствующими им входами сумматоров ветви вычисления реальной части сигнала, четные выходы первой и второй линий задержки соединеня с соответствующими им входами вычитателей ветви вычисления мнимой части сигнала.

последовательно соединенных элементов задержки, ветвь вычисления реальной части сигнала, которая содержит последовательно соединенные М сумматоров и соответственно им М перемножителей и последовательно соединенные выходной сумматор и регистр, выход которого является первым выходом полосового комплексного фильтра, образующим реальную часть комплексного выходного сигнала, ветвь вычисления мнимой части сигнала, которая содержит последовательно соединенные L вычитателей и соответственно им L перемножителей и последовательно соединенные выходной сумматор и регистр, выход которого является вторым выходом полосового комплексного фильтра, образующим мнимую часть комплексного выходного сигнала, первый вход первой линии задержки является первым входом полосового комплексного фильтра, вторые входы первой и второй линий задержки, вторые входы первого и второго регистров объединены и являются вторым входом полосового комплексного фильтра, нечетные выходы первой и второй линий задержки соединены с соответствующими им входами сумматоров ветви вычисления реальной части сигнала, четные выходы первой и второй линий задержки соединеня с соответствующими им входами вычитателей ветви вычисления мнимой части сигнала.

| US 5493581 A, 20.02.1996 | |||

| US 5504455 A, 02.04.1996 | |||

| Устройство для детектирования частотно-модулированного сигнала | 1985 |

|

SU1261080A1 |

| US 4980648, 25.12.1990 | |||

| 1968 |

|

SU415406A1 | |

Авторы

Даты

2001-05-27—Публикация

1999-08-18—Подача