входам первого сумматора и второго вьгчитателя вычислительного блока, выход мнимой части операнда первого блока памяти подключен к первым вход четвертого сумматора и четвертого вычитателя вычислительного блока, вторые входы которых подключены к выходу мнимой части операнда третьег блока памяти, выход реальной части операнда которого подключён к вторым входам первого сумматора,и второго вычитателя вычислительного блока, причем блок формирования управлякицих импульсов содержит генератор тактовых импульсов, элемент задержки, первый и второй элементы И, элемент ИЛИ и элемент НЕ, выход которого подключен к первому входу первого элемента И, выход кот-орого подключен к первому входу элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, первый вход которого подключен к выходу элемента задержки, выход генератора тактовых импульсов подключен к второму входу первого элемента И, при этом первый и второй блоки вычисления адреса содержат первый и второй элементы НЕ, первый, второй и третий элементы И, преобразователь прямого кода в дополнительный и счетчик, информационный выход которого подключен к информационному входу преобразователя прямого кода в дополнительный, вход синхронизации которого соединен с первыми входами первого и второго элементов И, входам первого элемента НЕ и подключен к вь1ходу Р-го разряда счетчика, выход (Р+1)-го разряда счетчика подключен к второму входу первого элемента И и входу второго элемента НЕ, выход которого подключен к второму входу второго элемента И и первому входу третьего элемента И, второй вход которого подключен к входу первого элемента НЕ, выход первого элемента И подключей к входу установки в О счетчика, информационные выходы счетчиков первого и второго блоков вычисления адреса подключены к адресным входам соответственно первого и второго блоков памяти, входы разрешения записи которы подключены соответственно к выходу (Р-ь1)-го разряда счетчика первого блока вычисления адреса и выходу третьего элемента И второго блока вьгчисления адреса, выходы преобразователей прямого кода в дополнительны которых подключены к адресным входам соответственно третьего и четвертого блоков памяти, входы разрешения записи которых подключены соответственно к выходу второго элемента И первого блока вычисления адреса и выходу (Р+1)-го разряда счетчика второго блока вычисления адреса, выходы {р+|)-го разряда счетчиков первого и второго блоков вычисления адреса подключены к входам разрешения считывания соответственно третьего и второго блоков памяти а выход третьеГо элемента И первого и выход второг элемента И второго блоков вычисления адреса подключены к входам разрешения считывания соответственно первого и четвертого блоков памяти, выкод первого элемента И первого блока вычисления адреса подключен к входу элемента задержки блока формирования управляющих импульсов, выход генератора тактовых импульсов которого подключен к счётному входу счетчика первого блока вычисления адреса, выход (Р+1)-го разряда счетчика которого подключен к второму входу второго элемента И блока формирования управляющих импульсов и установочном входу (Р + О-го разряда счетчика второго блока вычисления адреса, выход (Р+1)-го разряда счетчика которого подключен к входу элемента НЕ блока формирования управляющих импульсов, выход элемента ИЛИ которого подключен к счетному входу счетчика второго блока вычисления адреса, выход первого элемента И которого подключен к установочному входу (Р+1)-го разряда счетчика первого блока вычисления адреса.

11136

Изобретение относится к вычислительной технике и может быть ис- пользовано для цифровой обработки сигналов, спектрального анализа различных процессов, в .особенности 5 в таких областях, как радиолокация, доштеровские системы измерений, гидролокация , системы с повышенной разрешающей способностью анализа сигналов.О

Известно устройство, содержащее блок ввода данных, два запоминающих устройства, блок вычитания, сумматор, блок умножения, блок экспоненциальных функций и синхронизатор lj . 15

Недостатком устройства является необходимость значительного увеличения оборудования для улучшения частотного разрешения путем увеличения числа отсчетов в выборке N.. 20

Наиболее близким к изобретению техническим решением является устройство, реализующее алгоритм быстрого преобразования Фурье (БПФ), содержащее аналого-цифровой преобразова- 25 тель, два блока памяти, два блока вычисления адреса, вычислительный блок и блок весовых функций. При этом вход аналого-цифрового прёобра- . зователя соединен с входом устройст- зо ва, а выход - с первым входом первого блока памяти, второй вход которого соединен с выходом первого блока вычисления адреса, а выход подключен к первому входу вычислительного бло- ,„ ка, втарой и третий входы которых по; 1соединены к блоку весовых функций, первый выход вычислительного блока подключен к первому входу второго блока памяти, а второй и третий о выходы - соответственно к входам блоков вычисления адреса, выход которого подключен к второму входу второго блока памяти, первый выход которого соединен с выходом устройства д а второй выход второго блока памяти подключен к четвертому входу вычислительного блока 23 .

Процедура вычисления коэффициентов Фурье по алгоритмам БПФ сводится к 50 вычислению спектра в равноотстоящих точках на оси частот. Она представляет собой грубый набор фильтров первого порядка, равноотстоящих по оси частот. При анализе сигналов, содер- 55 жяпщх частоты, близкорасположенные одна к другой, тяжело подобрать фильтры так, чтобы их собственные

12

резонансные частоты совпадали с составляющими сигнала. Ввиду этого появляется неопредепенность оценки спектра из-за размытия спектра. Увеличение разрешения ведет к усложнению устройства.

Устранение этого недостатка возможно, если использовать набор фильтров с неравномерным расположением по

оси частот, заданный по закону агссоз i. i При этом в заданном частотном диапазоне всегда найдется по крайней мере два фильтра, расстояние между которыми по оси частот близко к расстоянию составляюпСих сигнала. С другой стороны, с помощью гетеродинного преобразователя сигнал всегда можно сместить на нужньй участок частотной шкалы так, чтобы отклики этих фильтров были максимальны, что соответст- : вуеТ совпадению спектральных компонент сигналов с набранными фильтрами.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что устройство для ортогонального йреобразования цифровых сигналов по Фурье-Чебьш1еву,содержащее первый блок памяти, информационный вход которого подключен к выходу аналого-цифрового преобразователя, вход которого является информационным входом устройства, вычислительный блок, второй блок памяти, информационный выход которого является первым информационным выходом устройства, блок постоянной памяти, первый и второй блоки вычисления адреса, содержит также третий.и четвертьш блоки памяти, первый и второй комбинационные сумматоры и блок (формирования управляющих импульсов, при этом информационный вход третьего блока памяти подключен к выходу аналого-цифрового преобразователя, выходы первого и второго комбинационных сумматоров подключены к информационным входам соответственно второго и четвертого блоков памяти, информац онный выход четвертого блока памяти является вторым информациоиньм выходом устройства, причем вычислитель- . ный блок содержит первый, второй, третий и четвертый сумматоры, первый, второй, третий и четвертый вычитатели, первый, второй, третий и четвёртый умножители, выход первого сумматора подключен к первому, входу первого умножителя, выход которого подключён к первым входам второго сумматора и первого зычитателя, выходы которых подключены к первым входам соответственно первого и второго комбинационных сумматоров, выход второго вычитателя подключен к первому входу второго умножителя, выход которого подключен к первым входам третьего сумматора и третьего вычитателя, выходы которых подключены к вторым входам соответственно второго и первого комбинационных сумматоров, выход четвертого сумматора подключен к первому входу третьего умножителя, выход которого подключен к вторым входам третьего сумматора и третьего вычитателя, выход четвертого вычитателя подключен к первому входу четвертого умножителя, выход которого подключен к вторым входам второго сумматора и первого вычитателя, вторые входы. первого и третьего умножителей вычислительного блока подключены к выходу реальной части числа блока постоянной памяти, выход мнимой части числа которого подключен к вторым входам второго и четвертого умножителей вычислительного блока, выход реальной части операнда первого блока памяти Iподключен к первым входам первого сумматора и второго вычитателя вычислительного блока, выход мнимой части операнда первого блока памяти подключен к первым входам четвертого сумматора и четвертого вычитателя вычислительного блока, вторые входы которых подключены к выходу мнимой части операнда третьего блока памяти, выход реальной части операнда которого подключен к вторым входам первого сумматора и второго вычитателя вычислительного блока, причем блок формирования управляющих, импульсов содержит генератор тактовых импульсов, элемент задержки, первый и второй элементы И, элемент ИЛИ и элемент НЕ выход которого подключен к первому входу первого элемента И, выход которого подключен к первому входу элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, первый вход которого подключен к выходу элемента задержки, выход генератора тактовых импульсов подключен к второму входу первого элемента И, при этом первый и второй блоки вьтчисления адреса содержат первый и второй элементы НЕ, первый, второй и третий элементы И, преобразователь прямого кода в дополнительный и счетчик, информа;ционный выход которого подключен к информационному входу преобразователя прямого кода в доцолнительный, вход синхронизации которого соединен с первыми входами первого и второго элементов И, входом первого элемента НЕ и подключен к выходу Р-го разряда счетчика, выход (р+1)-го разряда счетчика подключен к второму входу первого элемента И и входу второго элемента НЕ, выход которого подключен к второму входу второго элемента И и первому входу третьего элемента И, второй вход которого подключен к входу первого элемента НЕ, выход первого элемента И подключен к входу установки в О счетчика, информационные выходы счетчиков первого и второго блоков вычисления адреса подключены к адресным входам соответственно первого и второго блоков памяти, входы разрешения записи которых подключены соответственно к выходу ()-го разряда счетчика первого блока вычисления адреса и выходу третьего элемента И второго блока вычисления адреса, выходы преобразователей прямого кода в дополнительный которых подключена к адресным входам соответственно третьего и четвертого блоков памяти, входы разрешения записи которых подключены соответственно к выходу второго элемента И первого блока вычисления адреса и выходу (Р+1)-го разряда счетчика второго блока вычисления адреса, выходы (Р+1)го разряда счетчиков первого и второго блоков вычисления адреса подключены к входам разрешения считывания соответственно третьего и второго блоков памяти, а выход третье) элемента И первого и выход второго элемента И второго блоков вычисления адреса подключены к входам разрешения считьгоания соответственно первого и четвертого блоков памяти, выход первого элемента И первого блока вычисления .адреса подключен к входу элемента задержки блока формирования управляювщх импульсов, выход генератора тактовых импульсов которого подключен к счетному входу счетчика первого блока вычисления адреса, выход (Р+1)-го разряда счетчика которого подключен к второму входу второго элемента И блока формирования управляющих импульсов и установочному входу (Р+1)-го разряда счетчика второго блока вычисления адреса, выход (Р+1)- 5 го разряда счетчика которого подключен к входу элемента НЕ блока формирования управляюпщх импульсов, вывод элемента ИШ которого подключен к счетному входу счетчика второго бло- 10 ка вычисления адреса, выход первого элемента И которого подключен к установочному входу {Р+1)-го разряда счетчика первого блока вычисления адреса.15

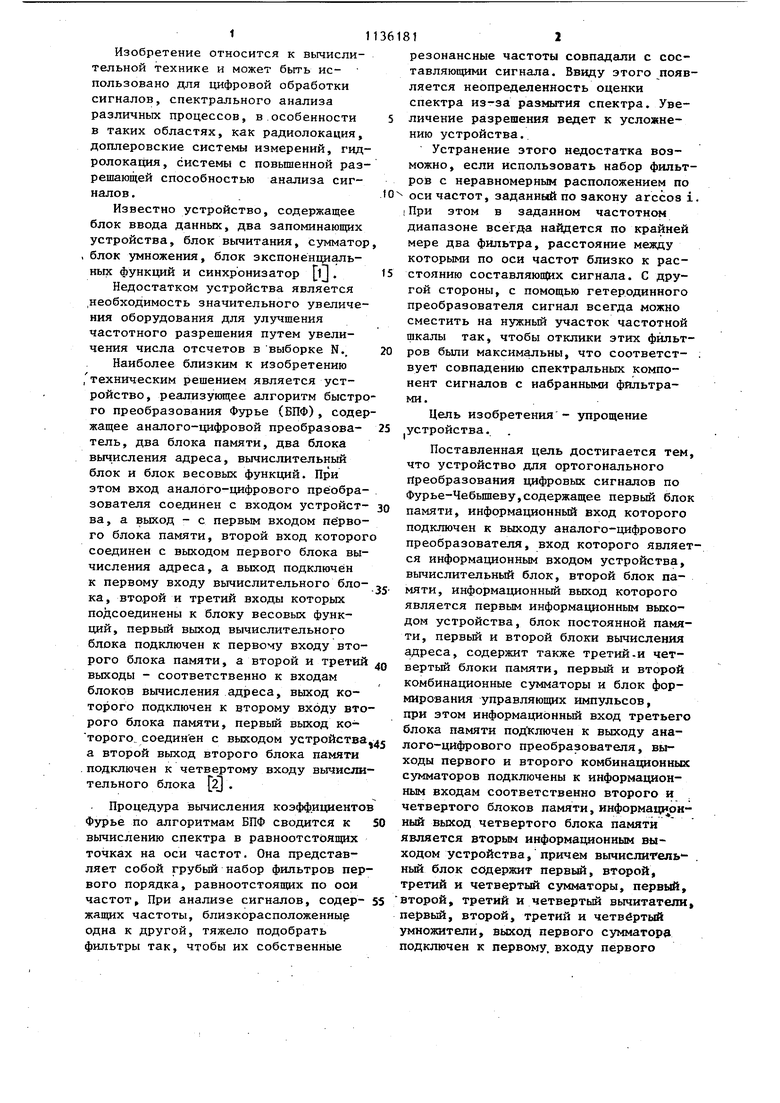

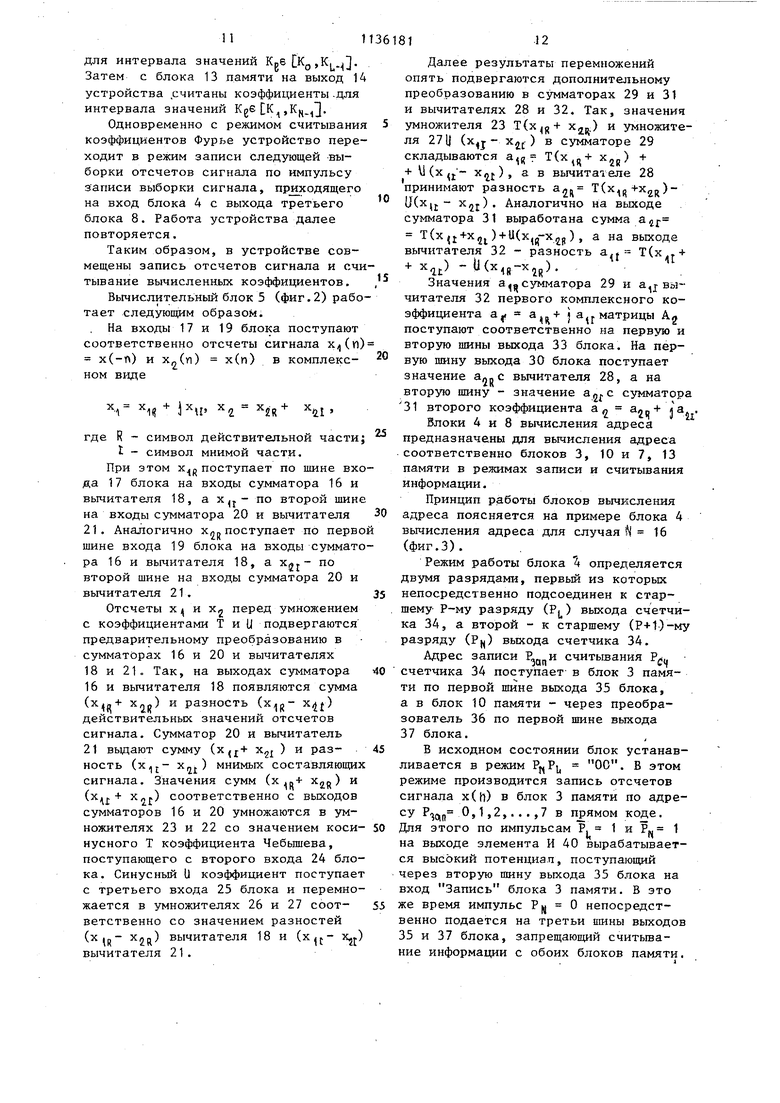

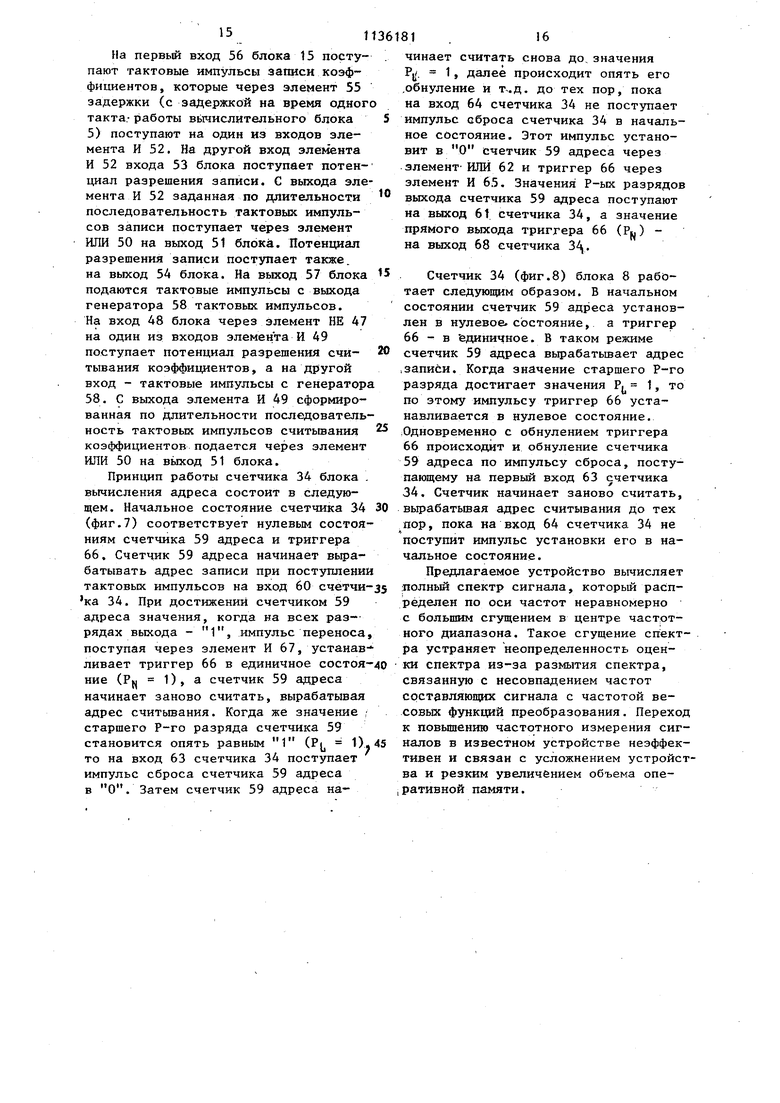

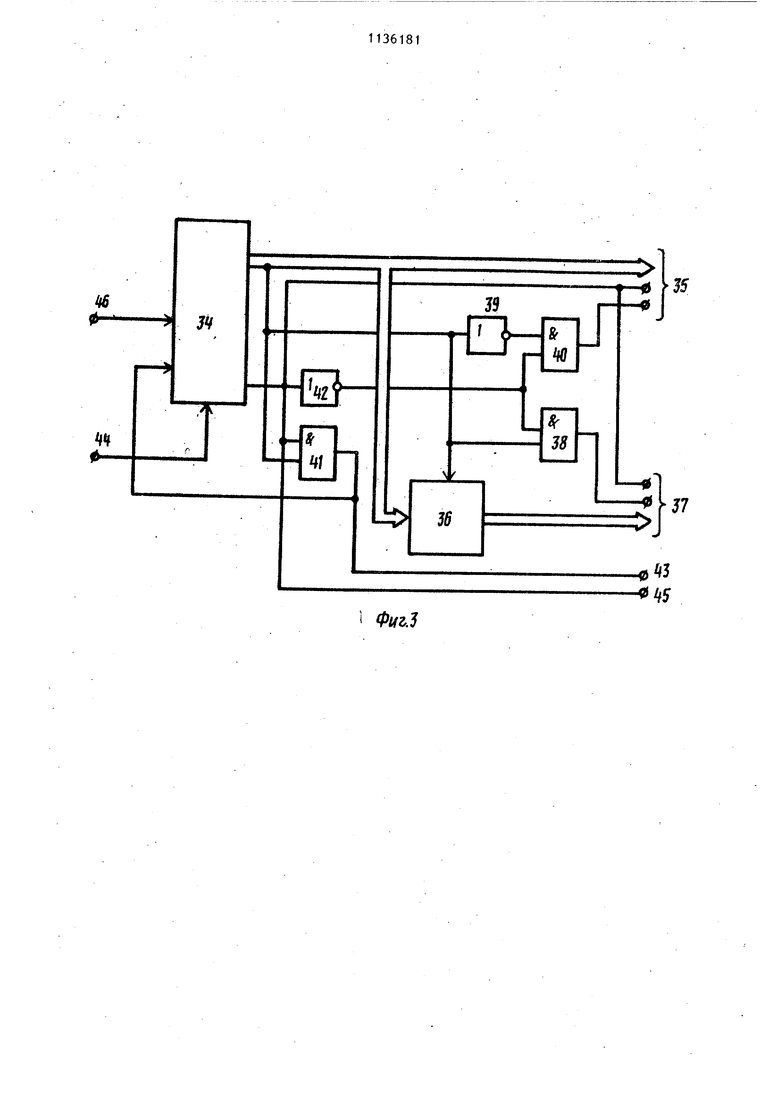

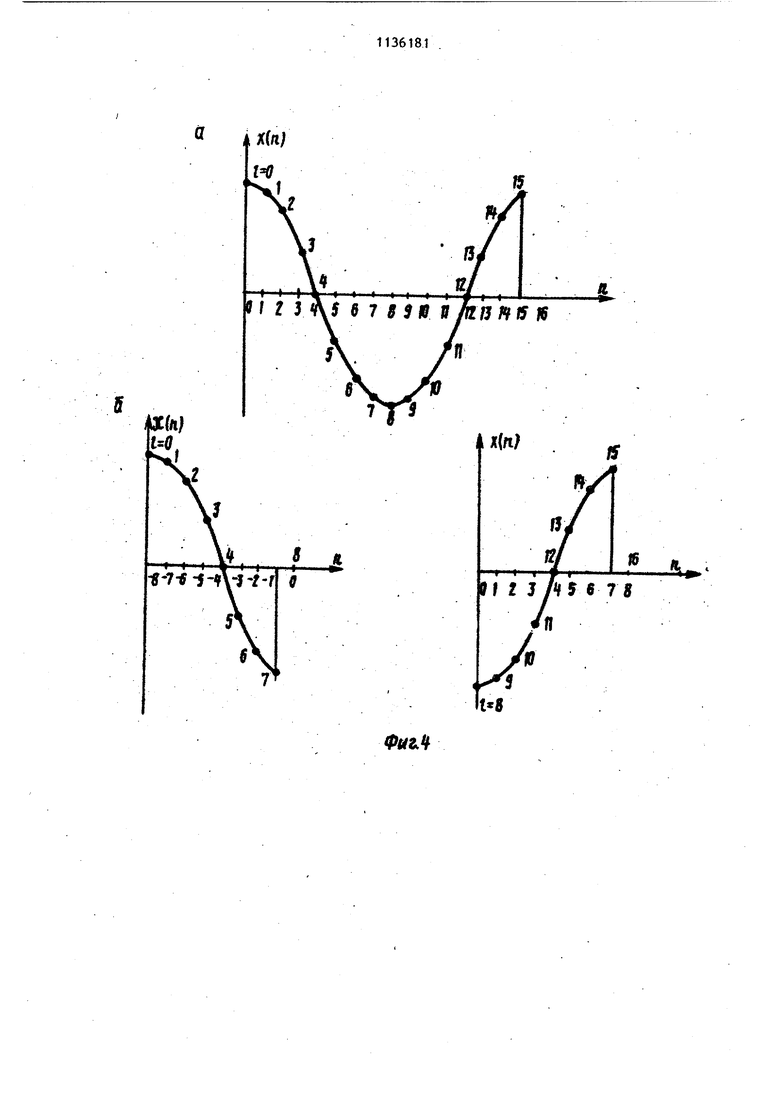

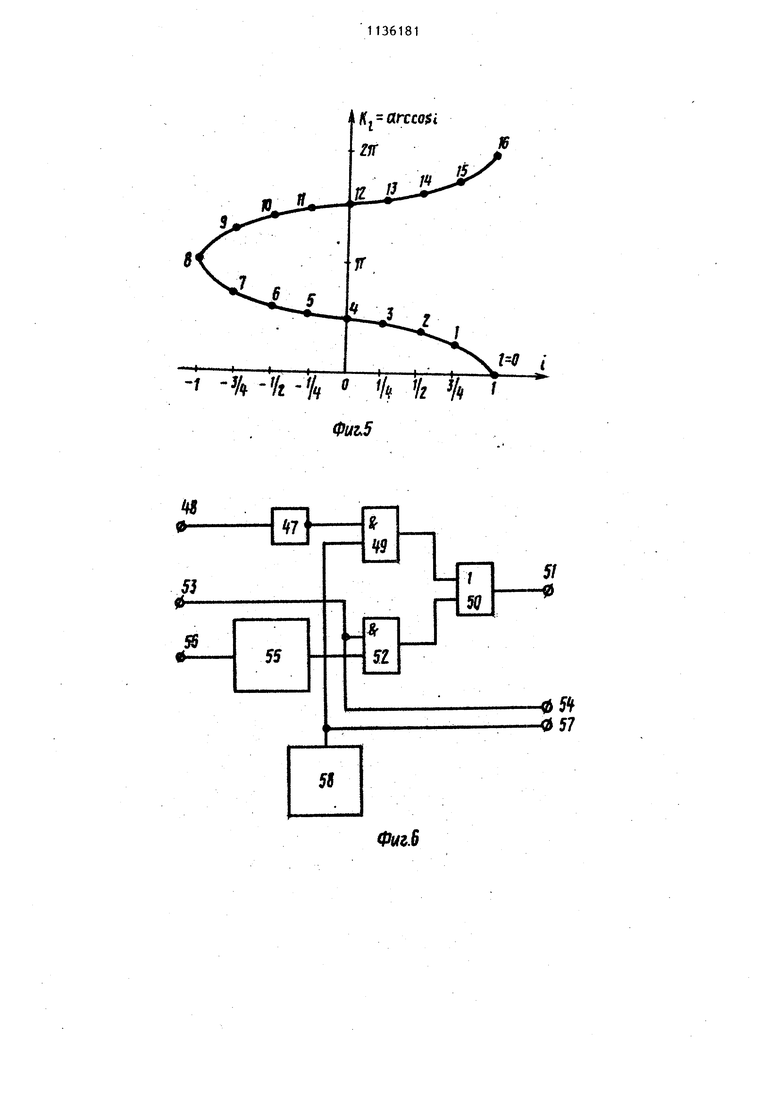

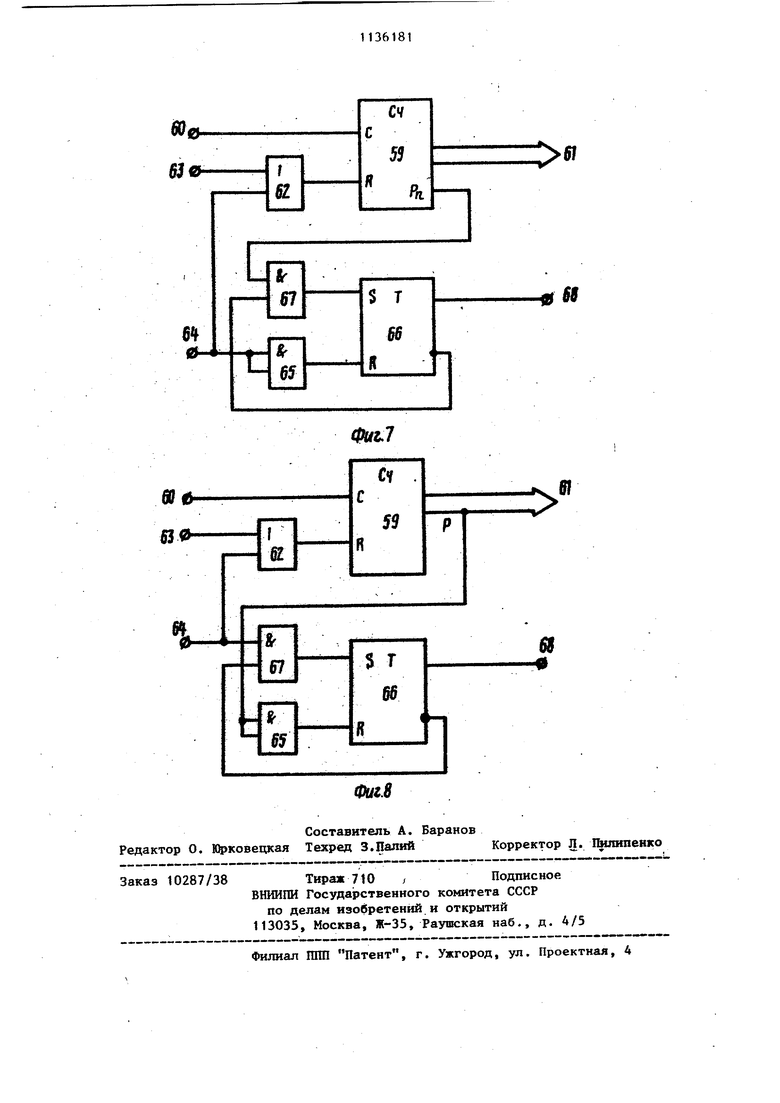

На фиг.1 представлена блок-схема устройства для ортогонального преобразования цифровых сигналов по ФурьеЧебышеву на фиг.2 - блок-схема вычислительного блока; на фиг.З - . 20 структурная схема блока вычисления адреса; на фиг.4 - последовательность отсчетов сигнала с учетом их симметрии; на фиг.З - последовательност, спектральных составляющих, упорядо- 25 ченная по закону arccos i; на фиг.6 структурная схема блока формирования управляюпщх импульсов; на 4)иг.7 структурная схема счетчика первого блока вычисления адреса; на фиг.8 - о структурная схема счетчика второго блока вычисления адреса.

Устройство содержит аналого-цифровой преобразователь 1, информационный вход 2, блок 3 памяти, блок 4 вычис-., ления адреса, вычислительный блок 5, блок 6 постоянной памяти, блок 7 памяти, блок 8 вычисления адреса, информационный выход 9, блок 10 памяти, комбинационные с маторы 11 и 12 блок 13 памяти, информационный выход 14 и блок 15 формирования управления импульсов.

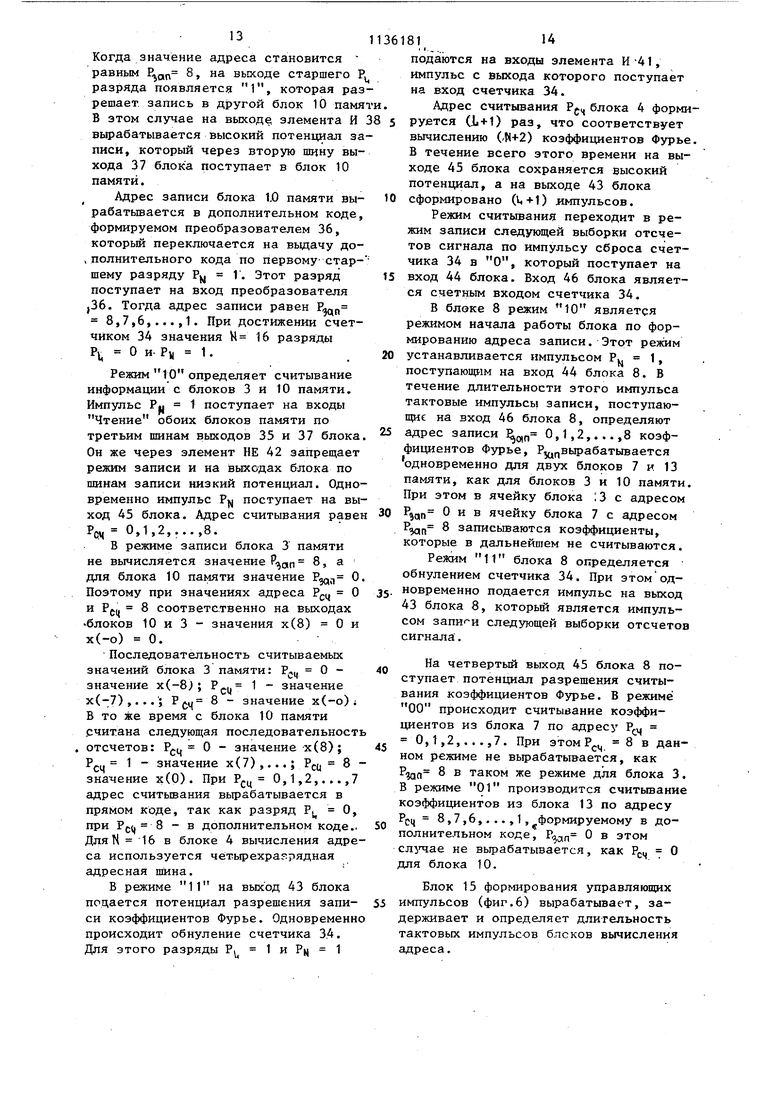

Вычислительный блок 5 (фиг.2) содержит сумматор 16, вход 17, вычита- д, тель 18, вход 19, сумматор 20, вычитатель 21, умножители 22 и 23, входы 24 и 25, умножители 26 и 27, вычитатель 28, сумматор 29, выход 30, сумматор 31, вычитатель 32 и выход 3 Блок 4 вычисления адреса (фиг.З) содержит счетчик 34, выход 35, преобразователь 36 прямого кода в дополнительный, выход 37, элемент И 38, элемент НЕ 39, элемент И 40, элемент 55 И 41, элемент НЕ 42, выход 43, вход 44, выход 45 и вход 46. Первая, вторая и третья шины первого выхода блока 4 подключены соответственно к адресному входу, входам Запись и Чтение блока 3 памяти. Те же шины второго выхода блока 4 подключены аналогичным образом к таким же входам блока 10 памяти.

Блок 8 вычисления адреса аналогичен конструктивно блоку 4 вычисления адресу. При этом первая, вторая и третья шины первого выхода блока 8 подключены соответственно к адресному входу, входам Чтение и Запись блока 7 памяти, а те же шины второго выхода - аналогично к тем же входам второго входа блока 13 памяти.

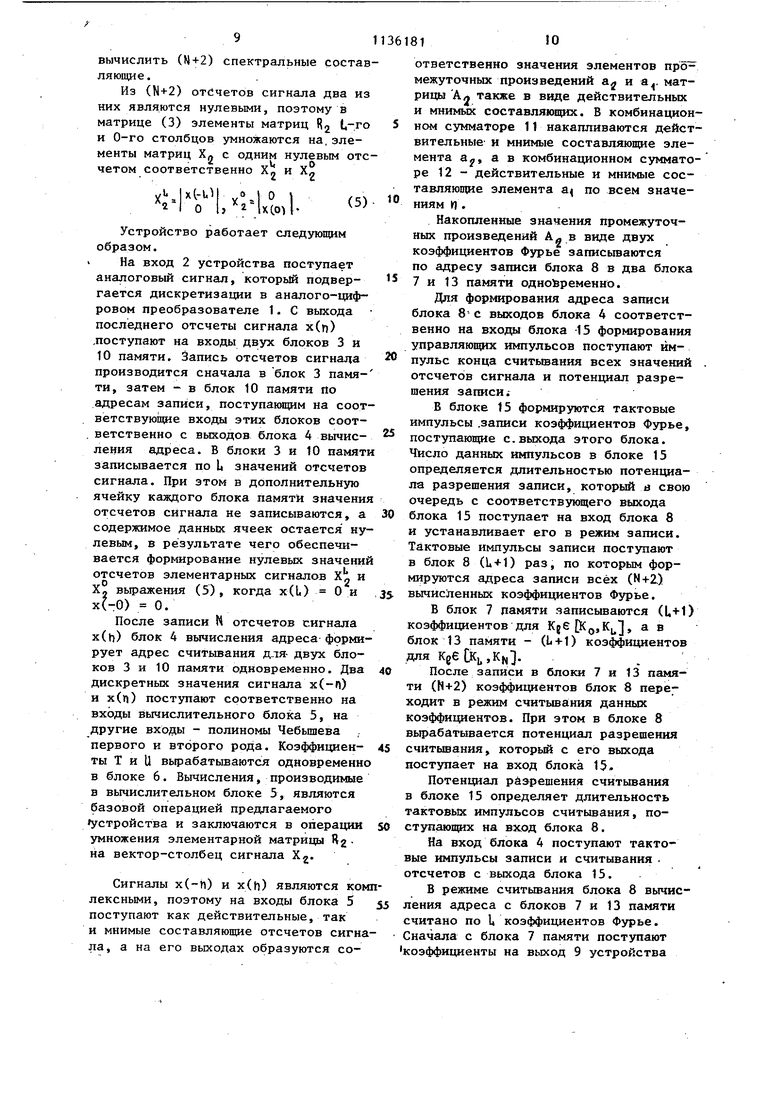

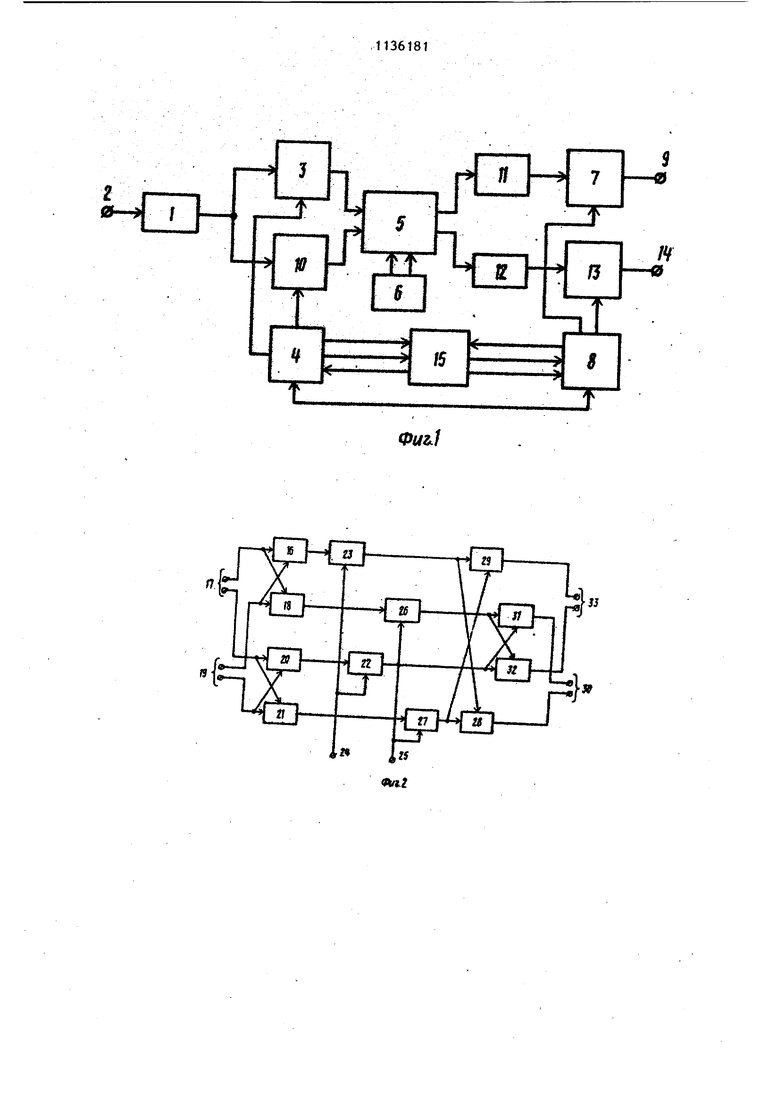

Блок 15 формирования управляющих импульсов (фиг.6) содержит элемент НЕ 47, вход 48, элемент И 49, элемент ИЛИ 50, выход 51,элемент И 52, вход 53, выход 54, элемент 55 задержки, вход 56, выход 57 и генератор 58 тактовых импульсов.

Счетчик 34 блока 4 (фиг. 8 и 9) содержит счетчик 59 адреса, вход 60, выход 61, элемент ИЛИ 62, входы 63 и 64, элемент И.65, триггер 66, элемент И 67 и выход 68.

Счетчик 34 блока 8 выполнен конструктивно аналогично счетчику 34 блока 4. Однако первый вход элемента И 67 подключен к второму входу 64 счетчика 34, а первый и второй входы элемента И 65 подключены к старшему Р-му разряду выхода счетчика 59 адреса.

Блоки 3, 7, 10 и 13 памяти состоят из ОЗУ комплексных чисел, в ячейках которых хранятся действительные и мнимые составляющие комплексных чисел. Объем памяти каждого блока памяти составляет я-+1 ячеек.

Алгоритм преобразования Фурье-Чебьшева вычисляет коэффициенты Фурье с неравномерным частотным представлением. Это частотное представление задается по закону Kt arccos i, где i - нормированная безразмерная частота, задаваемая в интервалах C+I.-Q для KgeCo.i ,,L и -1,1J для Kget-5,21, ,N, .

В предлагаемом устройстве вычисление коэффициентов преобразования Фурье заменяется преобразованием Фурье-Чебышева с весовьми функциями вида

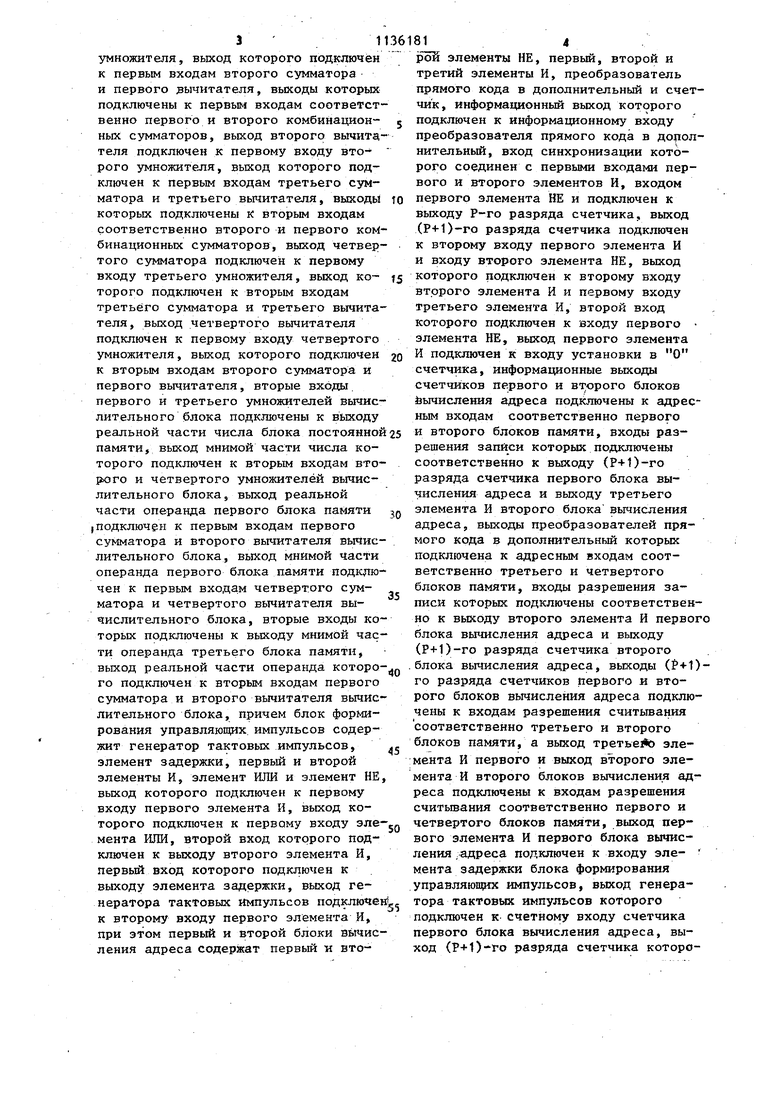

exp(jn arccos i)T(i)-jU (i) ( 1) где T,(i)cos(n arccos i) и U(i) sin (n arccos i) - соответственно косинусная и синусная составляющие, являющиеся ортогональными полиномами Чебышева первого и второго рода; n - временная безразмерная послед вательность, n 0,+1,±2,...,+L. Анализируемый сигнал, представленный в виде дискретных отсчётов x(ti) косинусоиды для N 16 показан на фиг. 4а. На фиг.4В и At показаны те же дискретные отсчеты, но с учето симметрии и сигнала относительно центра интервала Го,К;. На фиг. 4о показаны отсчеты для отрицательных значений n, а на фиг.4Ь - положитель ных значений П. При этом на фиг.40| номера дискретных отсчетов х(п) совпадают со значениями n, а для фиг.4К и 4Ь они соответственно равны п -8,-7,-6,...,-О, ,1,2,...,8 ff f 999999 „ n 1 о я - Q Q 1л и 11- VJ,l,jC,...,O, i/- P,3,IU,,.,.

Нормированная частота i для arccos i вычисляется из соотношения

i.t4-.

где 2 0,2,4,... ,li.

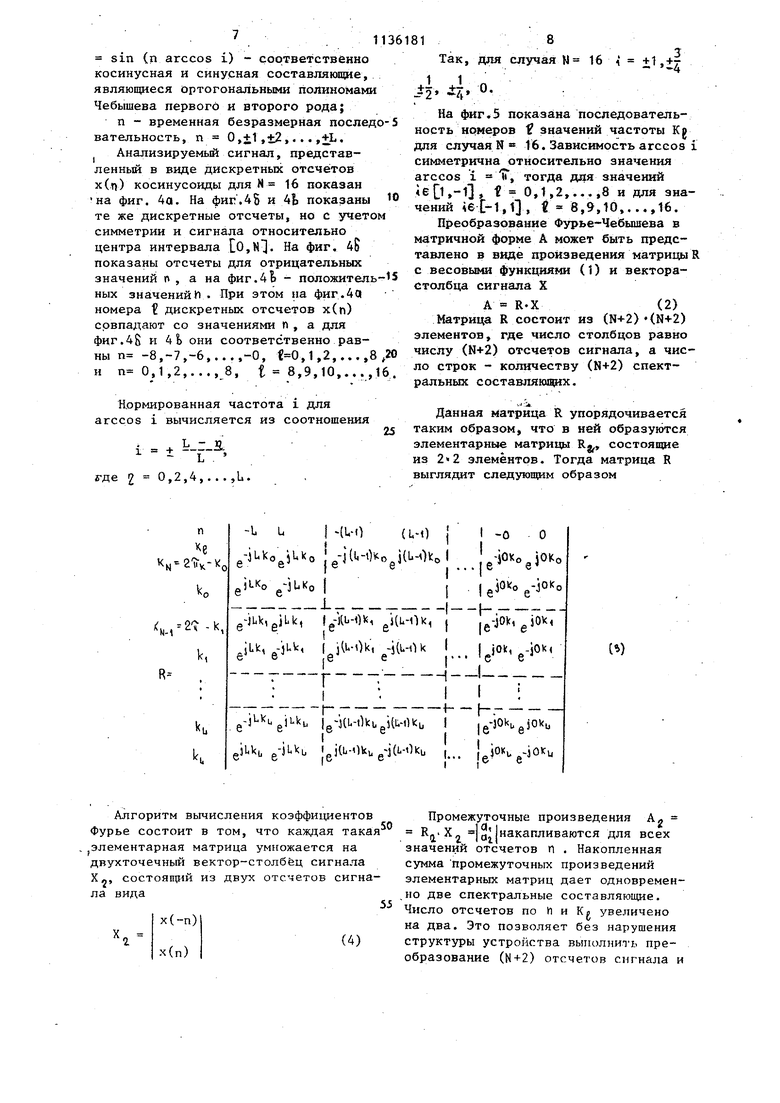

Данная матрица R упорядочивается таким образом, что в ней образуются элементарные матрицы Rg, состоящие из элементов. Тогда матрица R выглядит следующим образом 16 м i1,if Так, для случая N ±2 4 На фиг.5 показана последовательность нрмеров f значений частоты Kg для случая N 16. Зависимость arccos i симметрична относительно значения arccos i и, тогда для значений , f 0,1,2,...8 и для значений v6l-1,l, i 8,9,10,. ..,16. Преобразование Фурье-Чебышева в матричной форме А может быть представлено в виде произведения матрицы R с весовыми функциями (t) и векторастолбца сигнала X А R.X(2) Матрица R состоит из (N-«-2)(N+2) элементов, где число столбцов равно числу (N+2) отсчетов сигнала, а чисf лЧ ло строк - количеству (и+2) спектральных составлякз1Щ1х,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1427386A1 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

| Устройство для вычисления мультипликативной свертки | 1987 |

|

SU1451723A2 |

| Устройство для быстрого преобразования Фурье | 1983 |

|

SU1130872A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1982 |

|

SU1086437A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

УСТРОЙСТВО ДЛЯ ОРТОГОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ ПО, ФУРЬЕ-ЧЕВЫШЕВУ, содержащее первый блок памяти, информационный вход которого подключен к выходу анадого101ФРОВОГО преобразователя, вход которого является.информационным входом устройства, вычислительный блок, вто-, рой блок памяти, информационный выход которого является первым информационным выходом устройства, блок постоянной памяти, первый и второй блоки вычисления адреса, отличающееся тем, что, с целью упрощения устройства, оно содержит третий и четвертый блоки памяти, первый и второй комбинационные сумматоры и блок формирования управляющих импульсов, при этом инфбрматдионный вход третьего блока памяти подключен к выходу аналого-цифрового преобразователя , выходы первого и второго комбинацнонньгк сумматоров подключены к информационным входам соответственно второго и четвертого, блоков памяти, информационный выход четвертого блока памяти является вторым информационным выходом устройства,причем вычислительный блок содержит первый, второй,третий и четвертый суыматогы, первый, второй, третий и четвертый вычитатели, первый, второй, третий и четвёртый умножители, выход первого сумматора подключен к первому входу первого умножителя, выход которого подключен к перяым входам второго сумматора и первого вычитателя, выходы которых подключены соответственно к первым входам первого и второго комбинационных сумматоров, выход второго вычитателя подключен к первому входу второго умножителя, (/) выход которого подключен к первым входам третьего сумматора и третьего вычитатгля, вых.1.ды которых подключеО ны к вторым входам соответственно с второго и первого комбинационных сумматоров, выход четвертого сумматора подключен к первому входу третьего 00 05 умножителя, выход которого подключен к вторым входам третьего сумматора и третьего вычитателя, выход четвертого 00 вычитателя подключен к- первому входу четвертого умножителя, выход которого подключен к вторым входам второго сумматора и первого вычитателя, вторые входы первого и третьего умножителей вычислительного блока подключены к выходу реальной части числа . блока постоянной памяти, выход мнимой части числа которого подключен к вторым входам второго и четвертого умножителей вычислительного бяока, выход реальной части операнда первого блока памяти пе дключен к первым

n

ч

,., 27 -k,

k, RАлгоритм вычисления коэффициентов Фурье состоит в том, что каждая такая элементарная матрица умножается на двухточечный вектор-столбец сигнала Х„, СОСТОЯП1ИЙ из двух отсчетов сигнала вида

C%) Промежуточные произведения Ая RIJ. Х накапливаются для всех значений отсчетов г| . Накопленная сумма Промежуточных произведений элементарных матриц дает одновременно две спектральные составляющие. Число отсчетов по h и Ко увеличено на два. Это позволяет без нарушения структуры устройства выполнить преобразование (N+2) отсчетов сигнала и 9 вычислить (М+2) спектральные состав ляющие. Из (N+2) отйчетов сигнала два из них являются нулевыми, поэтому в матрице (3) элементы матриц Rj t-ro и 0-го столбцов умножаются на,элементы матриц Xft с одним нулевым отс четом соответственно Х„ и Х Устройство работает следующим образом. На вход 2 устройства поступает аналоговый сигнал, который подвергается дискретизации в аналого-цифровом преобразователе 1. С выхода последнего отсчеты сигнала х(п) .поступают на входы двух блоков 3 и 10 памяти. Запись отсчетов сигнада производится сначала в блок 3 памяти, затем - в блок 10 памяти по .адресам записи, поступающим на соот ветствующие входы этих блоков соот. ветственно с выходов блока 4 вычисления адреса. В блоки 3 и 10 памят записывается по L значений отсчетов сигнала. При этом в дополнительную ячейку каждого блока памяти значени отсчетов сигнала не записываются, а содержимое данных ячеек остается ну левым, в результате чего обеспечивается формирование нулевых значени отсчетов элементарных сигналов Х и X, выражения (5), когда х(Ь) О и х(-0) 0. После записи Н отсчетов сигнала x(t) блок 4 вычисления адреса фррми рует адрес считывания для- двух блоков 3 и 10 памяти одновременно. Два дискретных значения сигнала х(-п) и x(ii) поступают соответственно на входы вычислительного блока 5, на другие входы - полиномы Чебышева первого и второго рода. Коэффициенты Т и U вьфабатываются одновременн в блоке 6. Вычисления, производимые в вычислительном блоке 5, являются базовой операцией предлагаемого устройства и заключаются в операции умножения элементарной матрицы Hg на вектор-столбец сигнала Х. Сигналы х(-п) и x(h) являются ко лексными, поэтому на входы блока 5 поступают как действительные, так и мнимые составляющие отсчетов сигн ла, а на его выходах образуются соответственно значения злементов промежуточных произведений а и а. матрицы Ал также в виде действительных и мнимых составляющих. В комбинационном сумматоре 11 накапливаются действительные и мнимые составляющие элемента а, а в комбинационном сумматоре 12 - действительные и мнимые составляющие элемента а по всем значениям ц . Накопленные значения промежуточных произведений А- в виде двух коэффициентов Фурье записываются по адресу записи блока 8 в два блока 7 и 13 памяти одновременно. Для формирования адреса записи блока 8 с выходов блока 4 соответственно на входы блока 15 формирования управляющих импульсов поступают импульс конца считывания всех значений . отсчетов сигнала и потенциал разрешения записи .В блоке t5 формируются тактовые импульсы .записи коэффициентов Фурье, поступающие с. выхода этого блока. Число данных импульсов в блоке 15 определяется длительностью потенциала разрешения записи, который а свою очередь с соответствукнцего выхода блока 15 поступает на вход блока 8 и устанавливает его в режим записи, тактовые импульсы записи поступают в блок 8 () раз, по которым формируются адреса записи всех (N+Z) вычисленных коэффициентов Фурье. В блок 7 памяти записываются (L+D коэффициентов для ,K, а в блок 13 памяти - (Ь+1) коэффициентов для Kg€C4,KN После записи в блоки 7 и 13 памяти (N+2) коэффициентов блок 8 переходит в режим считывания данных коэффициентов. При этом в блоке 8 вьфабатывается потенциал разрешения считывания, который с его выхода поступает на вход блока 15 Потенциал разрешения считывания в блоке 15 определяет длительность тактовых импульсов считывания, поступающих на вход блока 8. На вход блока 4 поступают тактовые импульсы записи и считывания . отсчетов с выхода блока 15. В режиме считывания блока 8 вычисления адреса с блоков 7 и 13 памяти считано по I коэффициентов Фурье. Сначала с блока 7 памяти пост5тают коэффициенты на выход 9 устройства 111 для интервала значений ,К,.Л. Затем с блока 13 памяти на выход 14 устройства считаны коэффициенты -для интервала значений KgS К ,K(j., Одновременно с режимом считывания коэффициентов Фурье устройство переходит в режим записи следующей выборки отсчетов сигнала по импульсу записи выборки сигнала, привходящего на вход блока 4 с выхода третьего блока 8. Работа устройства далее повторяется. Таким образом, в устройстве совмещены запись отсчетов сигнала и счи тывание вычисленных коэффициентов, Вычислительный блок 5 (фиг.2) рабо тает следующим образом. На входы 17 и 19 блока поступают соответственно отсчеты сигнала х(п) х(-г) и х„(л) х(п) в комплексном виде N 1« где R - символ действительной части 1 - символ мнимой части. При этом поступает по шине вхо да 17 блока на входы сумматора 16 и вычитателя 18, а по второй шине на входы сумматора 20 и вычитателя 21. Аналогично Хп| поступает по перво шине входа 19 блока на входы суммато ра 16 и вычитателя 18, а по второй шине на входы сумматора 20 и вычитателя 21. Отсчеты X;( и Xj перед умножением с коэффициентами Т и U подвергаются предварительному преобразованию в сумматорах 16 и 20 и вычитателях 18 и 21. Так, на выходах сз матора 16 и вычитателя 18 появляются сумма (Хц+ Q.R разность (Xj|,j- ) действительных значений отсчетов сигнала. Сумматор 20 и вычитатель 21 вьщают сумму (Х(+ ) и разность ( Xnj) мнимых составляющи сигнала. Значения сумм (х ) и ( 9t соответственно с выходов сумматоров 16 и 20 умножаются в умножителях 23 и 22 со значением косинусного Т коэффициента Чебьш1ева, поступающего с второго входа 24 блока. Синусный О коэффициент поступает с третьего входа 25 блока и перемножается в умножителях 26 и 27 соответственно со значением разностей ( Xjn) вычитателя 18 и (хц- Xjj) вычитателя 21. 1 Далее результаты перемножений опять подвергаются дополнительному преобразованию в сумматорах 29 и 31 и вычитателях 28 и 32. Так, значения умножителя 23 T(xio+ Хяп.) и умножитеЛЯ 2711 ( - Xjf ) в с мматоре 29 складываются а( Т(х.п+ х.) + + Vi (х ц- ), а в вычитателе 28 принимают разность а2ц T(x,g+X5,a)U(x(j - ). Аналогично на выходе сумматора 31 выработана сумма 3 Т(хц+Х2) + и(х,-Х2р) , а на выходе вычитателя 32 - разность а( T(x., х...) - ll(x.B-x«o). 18 IRЗначения а сумматора 29 и вычитателя 32 первого комплексного коэффициента а J . матрицы Ag поступают соответственно на первую и вторую шины выхода 33 блока. На первую шину выхода 30 блока поступает значение а„„с вычитателя 28, а на вторую шину - значение ajfC сумматора 31 второго коэффициента а Эя„ + ia . Блоки 4 и 8 вычисления адреса предназначены для вычисления адреса соответственно блоков 3, 10 и 7, 13 памяти в режимах записи и считывания информации. Принцип работы блоков вычисления адреса поясняется на примере блока 4 вычисления адреса для случая N 16 (фиг.З). Режим работы блока определяется двумя разрядами, первьш из которых непосредственно подсоединен к старшему Р-му разряду (Pj) выхода счетчика 34, а второй - к старшему ()-му разряду (Р|) выхода счетчика 34. Адрес записи Р,д„и считывания счетчика 34 поступает в блок 3 памяти по первой шине выхода 35 блока, а в блок 10 памяти - через преобразователь 36 по первой шине выхода 37 блока. В исходном состоянии блок устанавливается в режим , 00. В этом режиме производится запись отсчетов сигнала х(Ц) в блок 3 памяти по адресу Рздп ,...,7 в прямом коде. и Р„ 1 Для этого по импульсам Р, 1 на выходе элемента И 40 вырабатывается высокий потенциал, поступающий через вторую шину выхода 35 блока на вход Запись блока 3 памяти. В это же время импульс Р О непосредственно подается на третьи цшны выходов 35 и 37 блока, запрещающий считьшание информации с обоих блоков памяти.

1311361811

Когда значение адреса становится подаются на входы элемента И-41,

равным 8, на выходе старшего Р импульс с выхода которого поступает

разряда появляется 1, которая раз-на вход счетчика 34.

решает, запись в другой блок 10 памяти. Адрес считьгоания Р,, блока 4 формиВ этом случае на выходе; элемента И 38 зРуется Ui + 1) раз, что соответствует

вырабатывается высокий потенциал за-вычислению CW+2) коэффициентов Фурье.

писи, который через вторую пщну выхода 37 блока поступает в блок 10 памяти. Адрес записи блока 1,0 памяти вы- О рабатывается в дополнительном коде, формируемом преобразователем 36, который переключается на выдачу до,полнительного кода по первому старшему разряду Р 1. Этот разряд поступает на вход преобразователя j36. Тогда адрес записи равен 8,7,6,...,1. При достижении счетчиком 34 значения М 16 разряды Pj, О и- РК 1. Режим 10 определяет считывание информации с блоков 3 и 10 памяти . Импульс PIJ 1 постзшает на входы Чтение обоих блоков памяти по третьим шинам выходов 35 и 37 блока Он же через элемент НЕ 42 запрещает режим записи и на выходах блока по шинам записи низкий потенциал. Одновременно импульс Pjg поступает на выход 45 блока. Адрес считывания равен РО 0,1,2,... ,8. В режиме записи блока 3 памяти не вычисляется значение 8, а для блока 10 памяти значение Рэап 0 Поэтому при значениях адреса Р. О и Pf.. 8 соответственно на выходах блоков 10 и 3 - значения х(8) О и х(-о) 0. Последовательность считываемых значений блока 3 памяти: Р.,ц О значение х( PCD значение х(-7),...; 8 - значение х(-о) i В то же время с блока 10 памяти считана следующая последовательность . отсчетов: О - значение х(8); Р,ц 1 - значение х(7),...; 8 значение х(0). При О,1,2,...,7 адрес считьшания вырабатывается в прямом коде, так как разряд Р 0, при Pgjj 8 - в дополнительном коде., Для N 16 в блоке 4 вычисления адреса используется чётырехра ;рядная адресная шИна. В режиме 11 на выход 43 блока подается потенциал разрешения записи коэффициентов Фурье. Одновременно происходит обнуление счетчика 3.4. Для этого разряды Р 1 и Рц 1

В течение всего этого времени на выходе 45 блока сохраняется высокий потенциал, а на выходе 43 блока сформировано (U-t-l) ямпульсов. Режим считывания переходит в режим записи следующей выборки отсчетов сигнала по импульсу сброса счетчика 34 в О, который поступает на вход 44 блока. Вход 46 блока является счетным входом счетчика 34. В блоке 8 режим 10 является режимом начала работы блока по формированию адреса записи. Этот реясим устанавливается импульсом Р 1, поступающим на вход 44 блока 8. В течение длительности этого импульса тактовые импульсы записи, поступающие на вход 46 блока 8, определяют адрес записи g,f, 0,1,2,...,8 козффициентов Фурье, Р ц вырабатывается одновременно для двух блоков 7 и 13 памяти, как для блоков 3 и 10 памяти. При этом в ячейку блока ;3 с адресом О и в ячейку блока 7 с адресом Рэап записываются коэффициенты, которые в дальнейшем не считываются, Режим 11 блока 8 определяется обнулением счетчика 34. При этом одповременно подается импульс на выход 43 блока 8, который является импульСОМ запи- и следующей выборки отсчетов сигнала , На четвертый выход 45 блока 8 поступает потенциал разрешения считывания коэффициентов Фурье. В режиме 00 происходит считывание коэффициентов из блока 7 по адресу P 0,1,2,...,7. При этом Р.ц 8 в данном режиме не вьфабатывается, как адп таком же режиме для блока 3. В режиме 01 производится считывание коэффициентов из блока 13 по адресу РСЦ 8,7,6,...,1.формируемому в дополнительном коде, этом слзчае не вырабатывается, как Pj; О для блока 10. Блок 15 формирования управляющих импульсов (фиг.6) вырабатывает, задерживает и определяет длительность тактовых импульсов б.псков вычисления адреса. 151 На первый вход 56 блока 15 поступают тактовые импульсы записи коэффициентов , которые через элемент 55 задержки (с задержкой на время одног такта.- работы вьиислительного блока 5) поступают на один из входов элемента И 52, На другой вход элемента И 52 входа 53 блока поступает потенциал разрешения записи. С выхода эле мента И 52 заданная по длительности последовательность тактовых импульсов записи поступает через элемент ИЛИ 50 на выход 51 блока. Потенциал разрешения записи поступает также, на выход 54 блока. На выход 57 блока подаются тактовые импульсы с выхода генератора 58 тактовых импульсов. На вход 48 блока через элемент НЕ 47 на один из входов элемента И 49 поступает потенциал разрешения считывания коэффициентов, а на другой вход - тактовые импульсы с генератор 58. С выхода элемента И 49 сформированная по длительности последователь ность тактовых импульсов считьшания коэффициентов подается через элемент ИЛИ 50 на выход 51 блока. Принцип работы счетчика 34 блока , вычисления адреса состоит в следующем. Начальное состояние счетчика 34 (фиг.7) соответствует нулевым состоя ниям счетчика 59 адреса и триггера 66. Счетчик 59 адреса начинает вьфа батывать адрес записи при поступлении тактовых импульсов на вход 60 счетчи ка 34. При достижений счетчиком 59 адреса значения, когда на всех раз- рядах выхода - 1, импульс переноса поступая через элемент И 67, уставав ливает триггер 66 в единичное состоя ние (P(j 1), а счетчик 59 адреса начинает заново считать, вырабатьюая адрес считьгоания. Когда же значение старшего Р-го разряда счетчика 59 становится опять равным 1 (Р 1) то на вход 63 счетчика 34 поступает импульс сброса счетчика 59 адреса в О. Затем счетчик 59 адреса на1чинает считать снова до,значения Р|/. 1, далее происходит опять его .обнуление и т.д. до тех пор, пока на вход 64 счетчика 34 не поступает импульс сброса счетчика 34 в начальное состояние. Этот импульс установит в О счетчик 59 адреса через элемент- ИЛИ 62 и триггер 66 через элемент И 65. Значения Р-ых разрядов выхода счетчика 59 адреса поступают на выход 61 счетчика 34, а значение прямого выхода триггера 66 (Pi.) на выход 68 счетчика 3. Счетчик 34 (фиг.8) блока 8 работает следующим образом. В начальном состоянии счетчик 59 адреса установлен в нулевое состояние, а триггер 66 - в единичное. В таком режиме счетчик 59 адреса вырабатьшает адрес , записи. Когда значение старшего Р-го разряда достигает значения P 1, то по этому импульсу триггер 66 устанавливается в нулевое состояние. ;0дновременно с обнулением триггера 66 происходит и обнуление счетчика 59 адреса по импульсу сброса, поступающему на первый вход 63 счетчика 34. Счетчик начинает заново считать, вырабатьшая адрес считывания до тех пор, пока на вход 64 счетчика 34 не поступит импульс установки его в начальное состояние. Предлагаемое устройство вычисляет полный спектр сигнала, который распределен по оси частот неравномерно с большим сгущением в центре частотного диапазона. Такое сгущение сп ектра устраняет неопределенность оценки спектра из-за размытия спектра, связанную с несовпадением частот составляющих сигнала с частотой весовых функций преобразования. Переход к повышению частотного измерения сигналов в известном устройстве неэффективен и связан с усложнением устройства и резким увеличением объема оперативной памяти.

ФЫ

46 0-

3if

55

1

fr 4(7

f

4ft 0 38

HSU;

Ъ

55

Фи&.3

-%-й-Й % Iz %

Фи1.5

41

7 055

55

Kj arcM$t

К

W

5/

7 W 0

J 5Z

-05 57

Ф(/г.б

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления коэффициентов фурье | 1975 |

|

SU537349A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Евтеев Ю.И | |||

| и др | |||

| Аппаратурная реализация дискретного преобразования Фурье | |||

| М., Энергия, 1978, с | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

Авторы

Даты

1985-01-23—Публикация

1983-09-08—Подача