Изобретение относится к вычислительной технике и может быть использо-вано при построении устройств цифровой вычислительной техники и дискретной автоматики на потенциальных логических элементах неизбыточных базисов, реализуемых преимущественно в виде БИС, например, счетчиков.

Целью изобретения является упрощение устройства.

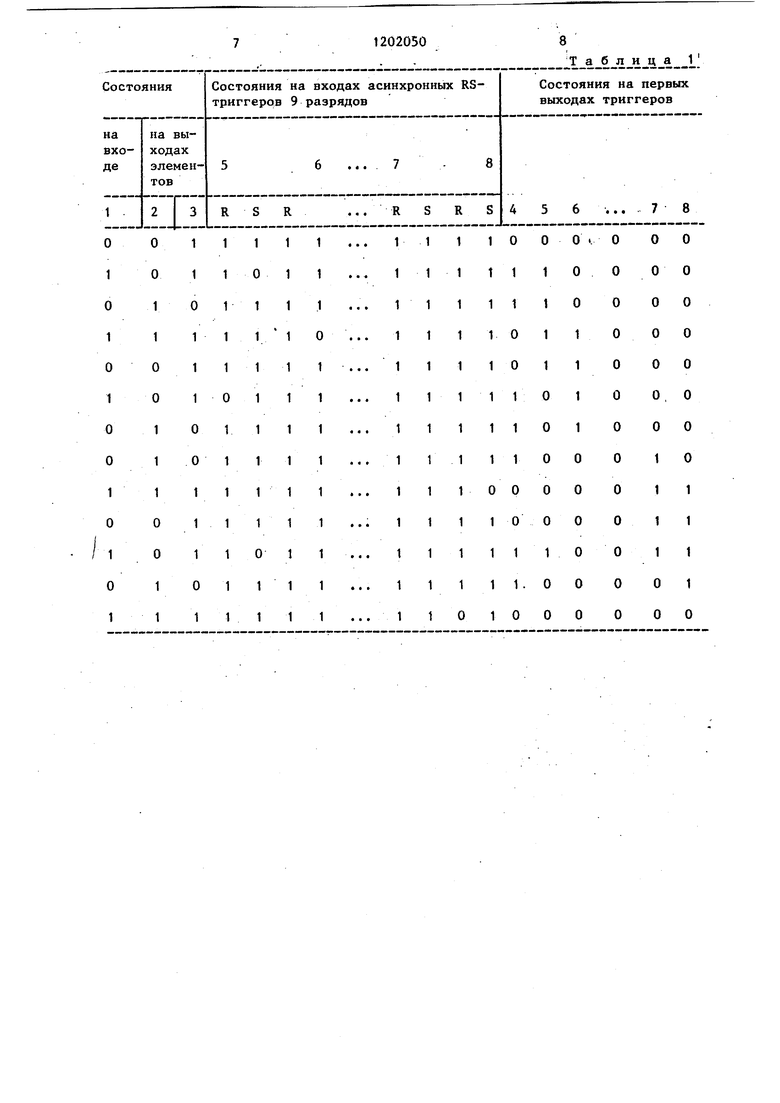

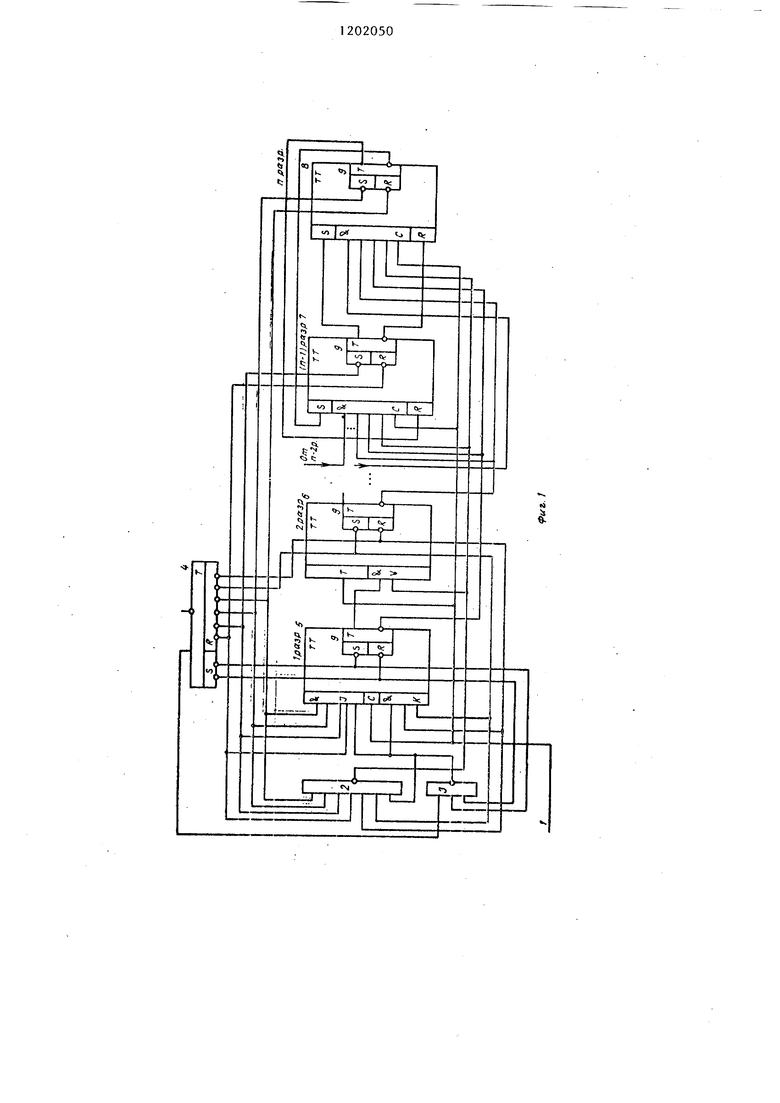

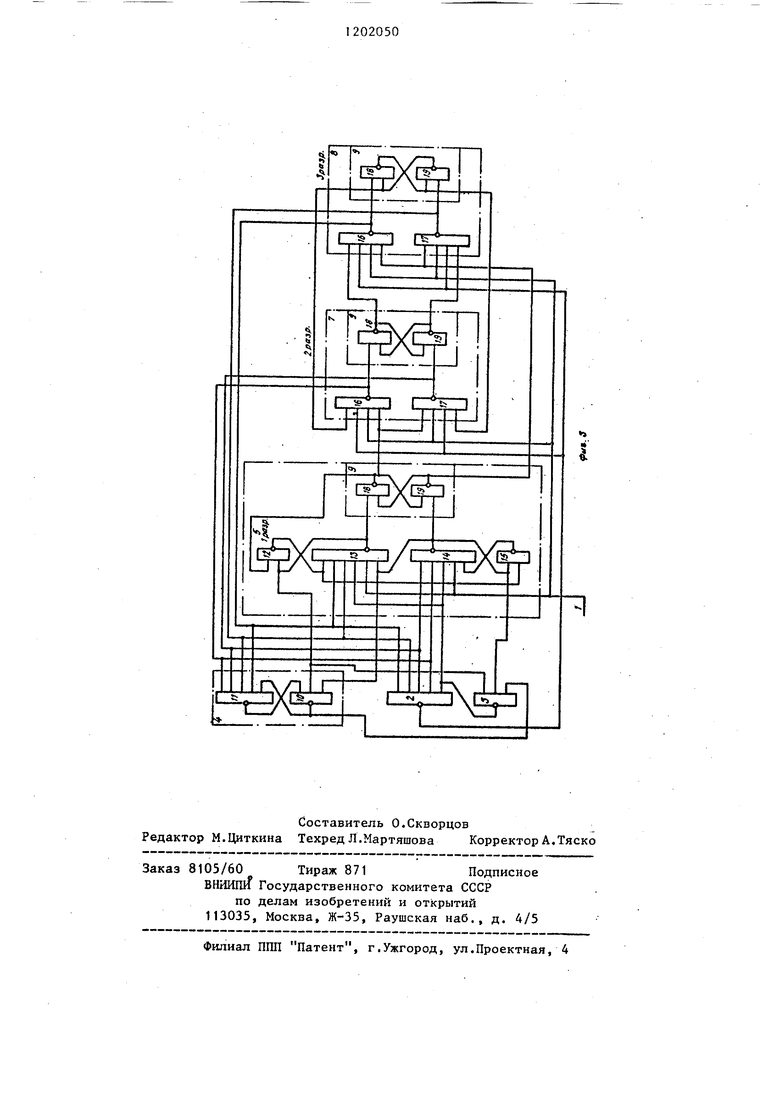

На фиг. 1 изображен п-разрядный счетчик в коде Грея; на фиг. 2 четырехразрядный предлагаемый счетчик} на фиг. 3 - трехразрядный предлагаемый счетчик.

Счетчик в коде Грея (фиг. 1) содержит счетный вход 1, первый 2 и .второй 3 логические элементы, RSтриггер 4, 1К-триггер 5, TV-триггер второго разряда 6,..., в (п-1)-м и п-м разрядах синхронные RS-триггеры 7 и 8. Триггеры 5, б,. . . , 7, 8 содержат по асинхронному RS-триггеру 9, выходы которого являются выходами этого триггера и данного разряда, счетньШ вход 1 соединен с синхровходами 1К-триггера 5, синхронных RS-триггеррв 7 и 8 и Т-входами TVтриггеров 6. Первый выход каждого разряда 5, 6,..., кроме (n-l)-ro 7 и п-го 8, соединен с входом последующего разряда 6,..., второй выход каждого разряда 5, 6,..., кроме (пг1)-го 7 и п-го 8 разрядов, соединен с входами всех старших разрядов ..., 7, 8, кроме последующего 6. Первый выход RS-триггера 4 соединен с первым входом второго элемента 3, выход которого соединен с первым входом первого элемента 2, выход ко- торого соединен с вторыми сипхровходами RS-триггеров 7 и 8 (п-1)-го и п-го разрядов и V-входами TV-триггеров 6Первый и второй выходы

п-го разряда 8 соединены соответственно с R- и S-входами синхронного RS-триггера 7 (п-1)-разряда, первый и второй выходы Сп-1)-го разряда 7 соединены соответственно с S- и R-входами синхронного RS-триггера 8 п-го разряда, S и R-входы асинхронно го RS-триггера 9 первого разряда 5 соединены попарно с двумя З-входами RS-триггера 4 и вторым и третьим входами второго элемента 3, S- и Rвходы RS-триггера 9 второго разряда соединены попарно с первым и вторым

020502

R-входами RS-триггера 4 и вторым и третьим входами первого элемент 2, S и R-входы асинхронных RS-триггеров 9 всех разрядов, начиная с третьего, соединены попарно с третьего по (2п-2)-й R-входами RS-триггера 4, с четвертого по (2п-1)-й входами элемента 2 и с второго по (2п-3)-й Iвходами 1К-триггера первого разряда

10 5, первый I- и третий К-входы которого соединены с выходом второго элемента 3.

Функционирование счетчика (фиг. 1) с инверсными входами асинхронных RS-триггеров 9 и логическими элементагди И-НЕ поясняется таблицей состояний (табл. 1), в строках которой состояния на входах и выхо- дах триггеров и элементов указаны 20 после окончания переходных процессов, вызванных предшествующим изг еиением сигнала на входе 1 в состояние, указанное в данной строке. Код Грея формируется на первых выходах разряд25 Ь1х триггеров 5, 6,...,7, 8. Разрядные асинхронные RS-TpHrrepN 9 разрядов 5, 6,..., 7. 8 и RS-триггеры переключаются по фронту импульсов на счетном входе 1 после переключения 20 в логический нуль одного из сигналов на R-или 8-входах ,RS-триггеров 9. При переключениях первого разряда 5 сигнал логической 1 на вькоде второго элемента 3 поддерживается сигналом логического О на одном из R- или S-входов асинхронного RS-триггера 9 первого разряда 5. При переключении одного из старших разрядов 6,..., 7, 8 параллельно переключа тся второй элемент 3 в логическую 1 (после переключения RS-триггера 4 в логический О) и 1К-триггер 5 удерживается в старом состояниисигналом логического нуля па I- или К-входе,соединенном с R- или S-входом RSтриггера 9 одного из старших разрядов 6,. .., 7, 8. .

Четырехразрядный счетчик, выполненный на логических элементах И-НЕ (фиг. 2), содержит счетный вход 1, первый и второй логические элементы 2 и 3, RS-триггер 4, в первом разряде - 1К-триггер 5, в четвертом и третьем разрядах - синхронные RSтриггеры 7 и 8, во втором разряде 55 xv-триггер 6. При этом триггеры 5-8 содержат по асинхронному RS-триггеру 9, выходы которого соединены попарно с выходами этого триггера и данного разряда. Кроме того, счетный вход 1 соединен с синхровходами 1К-трнггера 5, синхронных RS-триггеров 7 н 8 и Т-входом TV-триггера 6. Первый выход каждого из разрядов 5 и 6 соединей со входом носледующего разряда, а второй выход казкдого из разрядов 5 и 6 соединен с входами всех старших разрядов 6, 7, 8, кроме последу ющего, первый выход RS-триггера 4 со единен с первым входом второго элемента 3, выход которого соединен с пер-вым входом первого элемента 2, выход которого соединен с другими синхровходами RS-триггеров 7 и 8 третьего и четвертого разрядов и V-входом TV-триггера 6. Первый и вто рой выходы четвертого разряда 8 соединены попарно соответственно с Rи S-входами синхронного RS-триггера третьего разряда 7, первый и второй выходы третьего разряда соединены по парно соответственно с S- ш R-BXOдами синхронного RS-триггера четвер того разряда 8, S- и R-входы асинхронного RS-триггера 9 первого разряда 5 соединены попарно с двумя Sвходами RS-триггера 4, вторым и тре тьим входами второго элемента 3, Sи R-входы RS-триггера 9 второго раз .ряда 6 соединены попарно с первым и вторым К-входами 1К-триггера первого разряда 5, первьм и вторым R-BXOдами RS-триггера 4, вторым и третьим входами первого элемента 2. S- и Rвходы RS-TpnrrepoD 9 третьего и четвертого разрядов 7 и 8 соединены попарно с третьего по шестой R-BXOдами RS-триггера 4,.с четвертого по седьмой входами первого элемента 2 и с второго по пятьш 1-входами ГК-триггера первого разряда 5, первый L- и третий К-входы которого соединены с выходом вт.орого элемента 3, RS-триггер 4 выполнен на элементах 10 и 11, IK- триггер 5 и TVтриггер 6 выполнены каждый на элемен тах 12,..., 15 и RS-триггера 9. RSтриггер 9 построен на элементах 18 и 19, Синхронные RS-триггеры 7 и 8 построены на элементах 16, ..., 19. Функционирование счетчика, выполненного на элементах И-НЕ (фиг, 2), поясняется таблицей состояний (табл. 2), в калсдой строке которой указаны состояния на выходах логических элементов после окончания переходных процессов, вызванных предшествующим переключением сигнала на входе 1. Трехразрядньй счетчик, выполненHbul на логических элементах И-НЕ (фиг. 3), содержит счетньш вход 1, первый и второй элементы 2 и 3, RSтриггер 4, 1К-триггер первого разряда 5 и синхронные RS-триггеры второго и третьего разрядов 7 и 8. Триггеры разрядов 5, 7 и 8 содержат каждый до асинхронному RS-триггеру 9, выходы которого соединены попарно с выходами этого триггера и данного разряда. Счетный вход 1 соединен с синхровходами триггеров 5, 7 и 8. Первый выход триггера 5 соединен с входом триггера 7. Второй выход триггера 5 соединен с входом триггера 8. Выход RS-триггера 4 соединен с первым входом второго элемента 3, выход которого соединин с первым входом первого элемента 2, выход которого соединен с другими синхровходамн RS-триггеров 7 и 8. Первый и второй выходы третьего разряда 8 соединены попарно соответственно с Rи S-входами синхронного RS-триггера второго разряда 7. Первый и второй выходы второго разряда 4 соединены попарно соответстве шо с S- и Rвходами синхронного RS-триггера третьего разряда 8. S- и R-входы RSтриггера 9 первого разряда 5 соединены попарно с двумя S-входами RSтриггера 4 и вторым и третьим входами второго элемента 3, S- и R-входы RS-триггера 9 второго разряда 7 соединены попарно с первым и вторым КБходами 1К-триггера первого разряда 5, первым и вторым R-входами RSтриггера 4, вторым и третьим входами первого элемента 2, S- и R-входы RSтриггера 9 третьего разряда 8 соединены попарно с третьим и четвертым R-входами RS-триггера 4, с четвертым и пятым входами первого элемента 2, с вторым и третьим 1-иходами IKтриггера первого разряда 5, первый I- и третий К-входы которого соединены с выходом второго элемента 3. RSтриггер 4 выполнен на элементах 10 и 11. IK-триггер первого разряда 5 выполнен на элементах 12,..., 15 п RS- триггера 9. Синхро1П1ые RS-трнггеры 7 и 8 построены каждый на элементах 16 и 17 и RS-триггера 9. RS-триггер 9 выполнен на элементах 18 и 19. Выходы элементов 13 и 14 соединены попарно соответственно с S- и R-входа

ми RS-триггера 9 первого разряда 5, а выходы элементов 16 и 17 соединены попарно соответственно с S- и R-BXOдами RS-триггера 9 второго разряда 7 и третьего разряда 8.

Последовательность состояний счетчика (фиг. 3), постраенного на логических элементах И-НЕ, приведена в табл. 3, в каждой строке которой указаны состояния на выходах логических элементов после окончания переходных процессов, вызванных предшествующим переключением сигнала на входе 1 .

Функционирование счетчиков, построенных на логических элементах ИЛИ-ИЕ, происходит аналогично.

Формулаиз обретения

1. Счетчик в коде Грея, содержащий счетный вход, первый и второй логические элементы, RS-триггер, 1К-триггер первого разряда, синхронные RSтриггеры {п-1)-го и п-го разрядов, TV-триггеры в остальных разрядах, при этом IK-, TV-триггеры и синхронные RS-триггеры содержат каждый по асинхронному RS-триггеру, выходы которого являются выходами соответственно IK-, TV- или синхронного RS-триггеров и данного разряда, кроме того, .счетный вход соединен с синхровходами 1К-триггера, синхронных RS-триггеров (п-1)-го и п-го разрядов и с Т-входами TV-триггеров остальных разрядов, первый выход каждого разряда, кроме (п-1)-го и п-го, соединен с входом последующего разряда, а второй выход каждого разряда, кроме (п-1)-го и п-го, соединен с входами старших разрядов, кроме последующего, первый выход RS-триггера соединен

с первым входом второго логичс элемента, выход которого соединен с первым входом первого логического элемента, выход которого соединен с другими синхровходами синхронных RS-триггеров (п-1)-го и п-го разрядов и V-входами TV-триггеров остальных разрядов, отл и чающий с я тем, что, с целью упрощения, первый и второй выходы п-го разряда соединены попарно соответственно с R- и S-входами синхронного RS-триггера (n-l)-ro разряда,первый и второй выходы (n-l)-ro разряда соединены попарно соответственно с S- и R-BXOдами синхронного RS-триггера п-го разряда, S- и R-входы асинхронного RS-триггера первого разряда соединены попарно с двумя S-входами RSтриггера, вторым и третьим входами второго логического элемента, S- и R-входы асинхронного RS-триггера второго разряда соединены попарно с первым и вторым К-входами 1К-триггера первого разряда, первым и вторым R-входами RS-триггера, вторым и третьим входами первого логического элемента, первый 1-й третий К-входы 1К-триггера соединены с выходом второго логического элемента, S-, Rвходы асинхронных RS-триггеров всех разрядов, начиная с третьего разряда, соединены попарно с третьего по (2п-2)-й R-входами RS-триггера, с четвертого по (2п-1)-й входами первого логического элемента, с второго, по (2п-3)-й 1-входами 1К-триггера

2.Счетчик по п. 1, отличающийся тем, что выполнен на логических элементах И-НЕ.

3.Счетчик по п. 2,о т л ич аю щ и и с я тем, что выполнен на логических элементах ИЛИ-НЕ.

Таблица 1 о о Ъ о ооо о о о «- - о linlo - «-.« -ОО о - AI 1- «.. -о ., . . V. I %О I v- .«« т- о iftio о - - о о - о- - - - - «|л|--о ---- - о ы|«- «-О о. о« «-«- - - о о

„ о 9

о

о

о - о о о о о о о о о о - о «- о

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик в коде грея | 1984 |

|

SU1225011A1 |

| Счетное устройство | 1980 |

|

SU953741A1 |

| Устройство для дискретной регулировки фазы | 1978 |

|

SU779904A1 |

| Счетное устройство | 1982 |

|

SU1080250A1 |

| Синхронный счетчик | 1985 |

|

SU1257838A1 |

| Синхронный счетчик | 1987 |

|

SU1437994A1 |

| Генератор случайной последовательности | 1983 |

|

SU1275434A1 |

| Синхронный счетчик | 1987 |

|

SU1451851A1 |

| Счетный разряд | 1990 |

|

SU1725387A1 |

| Преобразователь угла поворота валаВ КОд | 1979 |

|

SU842898A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении устройств цифровой техники и дискретной автоматики на потенциальных логических элементах неизбыточных базисов, реализуемых преимущественно в виде больших интегральных схем, например, счетчиков. Целью изобретения является упрощение устройства. Данный счетчик в коде Грея выполнен на 1К-и TV-триггерах, а также на синхронных и асинхронных RS-триггерах и логических элементах, в первом варианте на логических элементах И-НЕ, во втором варианте - ИЛИ-НЕ. Функционирование счетчика в первом и втором варис € антах выполнения поясняется структурными схемами ti таблицами в описании сл с: изобретения. 2Л. п. ф-лы, 3 ил., 3 табл. to о ю о сл

i о

о о - -

,- - р - - о

«о

о - - р о - -

О

о и

«- о о о

S

. о

- - о

. о - . о о - «- о о « «-i

о «- о - о

«ч ti

| Гуртовцев А.Л | |||

| и др | |||

| Логическое проектирование устройств автоматики | |||

| Рига: Зинатие, 1978 | |||

| Проектирование микроэлектронных цифровых устройств | |||

| М.: Сов | |||

| радио, 1977. |

Авторы

Даты

1985-12-30—Публикация

1984-01-13—Подача