1

Изобретение относится к построению устройств цифровой вычислительной техники и дискретной автоматики, преимущественно на потенциальных логических элементах неизбыточньгх базисов.

Цель изобретения - упрощение устройства.

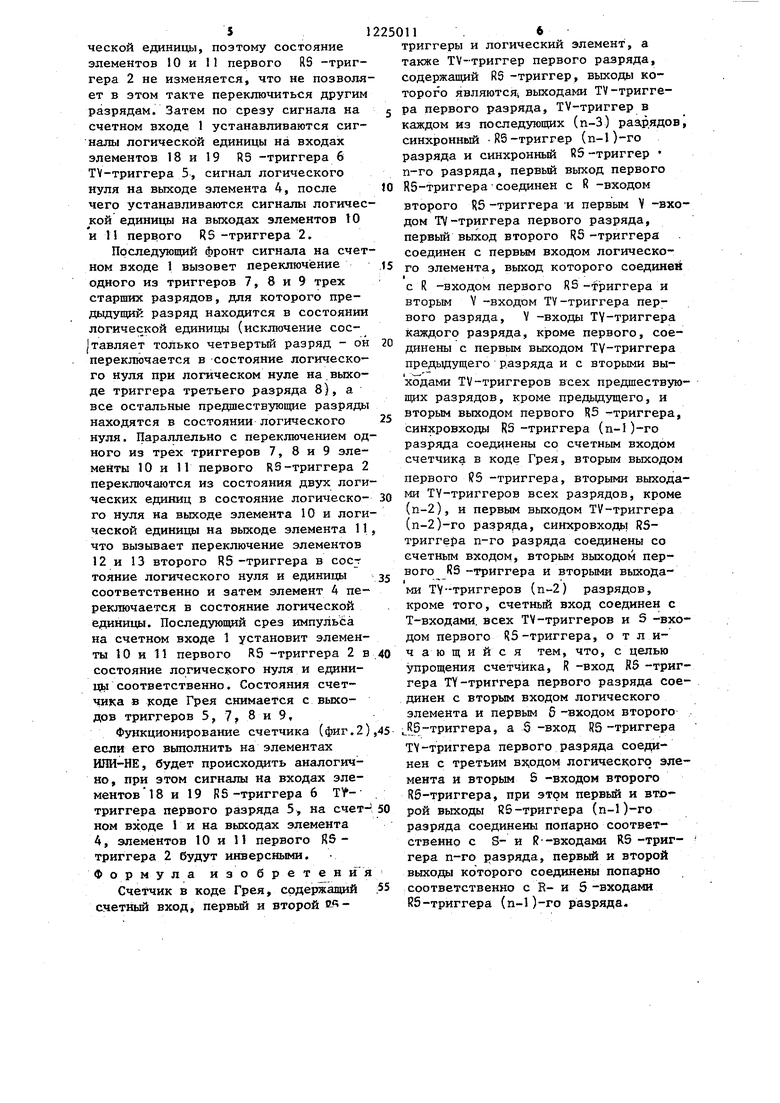

Счетчик в коде Грея может быть реализован на элементной базе в виде логических элементов И-НЕ или ИЛИ-НЕ . На фкг. 1 изображена структурная схема и -разрядного счетчика Грея; на фиг. 2 - структурная схема четырехразрядного счетчика Грея, вьшол- ненного на логических элементах И-НЕ

Счетчик в коде Грея (фиг. 1) содержит счетный вход 1, первый и второй R 5-триггеры 2 и 3 и логический элемент 4, TV-триггер 5 первого разряда, содержащий R5-тpиггep 6, выходы которого являются выходами TV-три гера 5, TV-триггер 7 второго разряда синхронные R5-триггера 8 и 9 в (n-l)-OM и п-ом разряде. Лервый выход первого R5 -триггера 2 соединен с R -входом второго RS -триггера 3 и первым V -входом TV-триггера 5 первого разряда, первьй вьгход второго R5-триггера 3 соединен с первым входом логического элемента 4, вьгход которого соединен с R -входом первого R5 -триггера 2 и вторым V -входом TV-триггера 5 первого разряда, V - входы каждого TV -триггера каждого разряда, кроме первого, соединены с первым выходом TV -триггера предыдущего разряда, со вторыми выходами TV -триггеров всех предшествующих разрядов, кроме предыдущего, и вторым выходом первого R5-триггера 2, синхровходы fiS-триггера 8 ()-го разряда соединены соответственно со счетным входом 1, вторым выходом первого RS -триггера 2, вторыми выходами TV -триггеров 5 и 7, всех разря-- дов, кроме (п-2)-го, первым выходом TV-триггера (п-2)-го разряда Счётный вход соединен также с Т-вхо- дами всех TV-триггеров 5, 7,... и 5-входом первого R5 -триггера 2, R-вход R5-триггера 6 TV-триггера 5 первого разряда соединен со вторым входом логического элемента 4 и первым 5 -входом второго R5-триггера 3 5-вход R5 -триггера 6 TV-триггера 5 первого разряда соединен с третьим входом логического элемента 4 и

112

вторым 5 -входом второго RS -триггера 3. Первый и второй выходы RS- триггера 8 (n-l)-ro разряда соединены соответственно с 5- и R -входами R5 -триггера 9 п-го разряда, первый и второй выходы которого соединены попарно соответственно с R- и 5 -входами R5 -триггера В (п-1)- го разряда. Последовательность полных состояний триггеров описьгоает .функционирование счетчика, ТУ-триг- гера которого переключаются по фронту импульса на Т-входе (реализация на логических элементах И-НЕ).

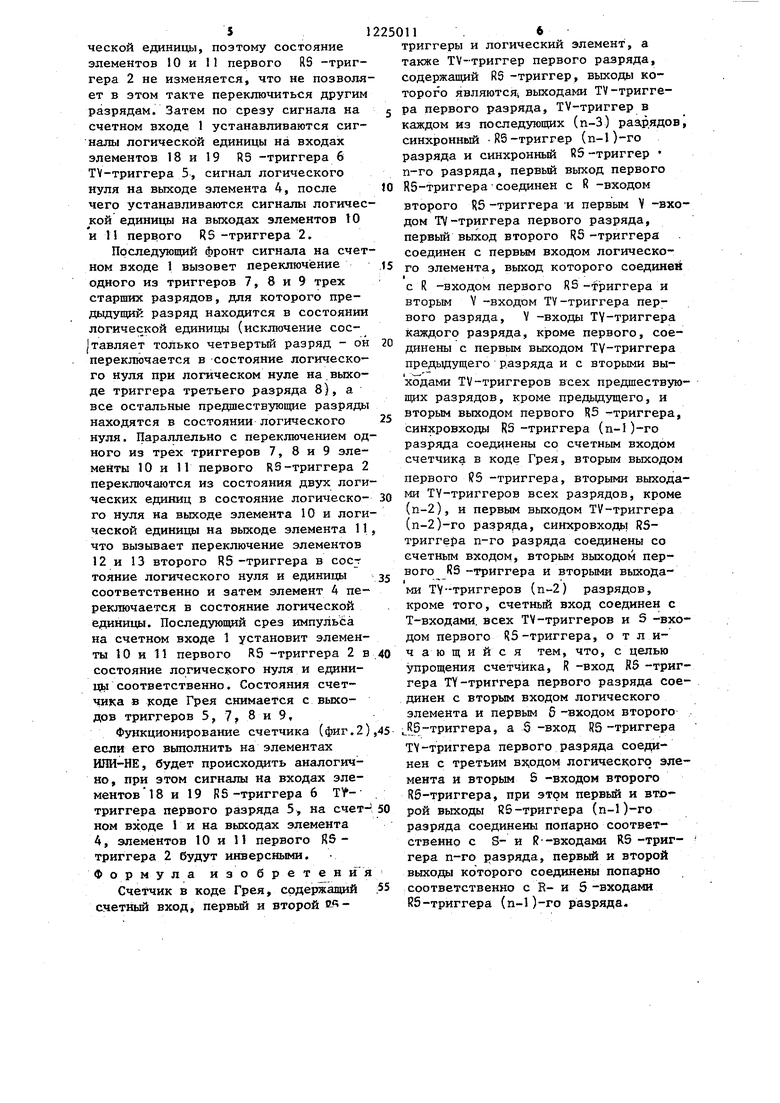

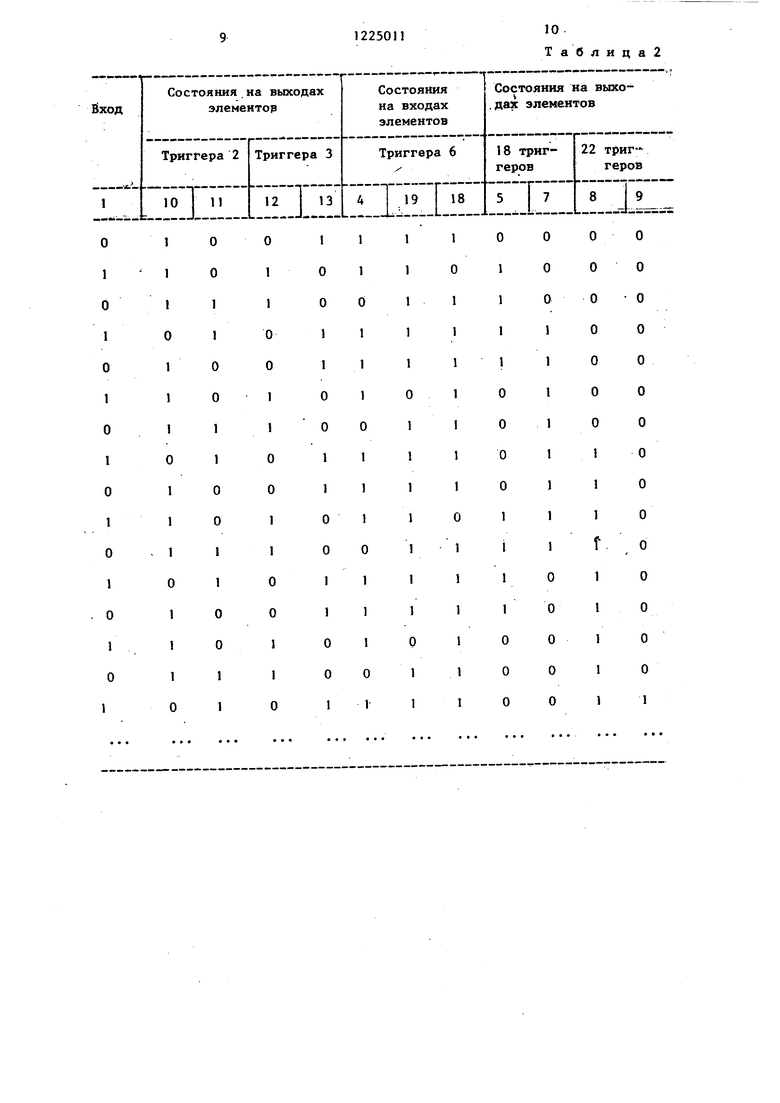

Состояния на всех выходах триггеров и элемента 4 указаны в табл. I после окончания переходных процессов , вызванных последним переключением сигнала на счетном входе 1.

Переключения TV-триггера 5 первого разряда происходит при сигналах логической единицы на первом выходе R6 -триггера 2, на выходе логического элемента 4 по фронту сигнала на счетном входе 1. При этом первым переключается в состояние логического нуля сигнал на 5 - или на R -входе RS -триггера 6 ТУ-триггера 5, после него параллельно переключается RS -триггер 6 TV-триггера 5 и R5 -триггер 3 устанавливается в состояние логической единицы. На выходе элемента 4 сохраняется сигнал логической единицы, поэтому состоя-

ние первого R5 -триггера 2 не изменяется, что не позволяет в этом такте переключаться другим разрядам. Затем по срезу сигнала на входе 1 устанавливается сигнал логической

единицы на R- и 5 -входе RS -триг- гера 6 TV -триггера 5 и сигнал логического нуля на выходе элемента 4, после него устанавливается сигнал логической единицы на двух выходах

первого R5 -триггера 2. Последующий фронт импульса на счетном входе 1 вызывает переключение того разряда из старших (п-1) разрядов, для которого предьщущий

разряд находится в состоянии логической единицы, а все остальные - в состоянии логического нуля (исключение составляет только п-ный разряд R5-триггера 9, который переключается в состояние логического нуля при условии, что предшествующие разряды находятся в состоянии логического нуля Параллельно с переключе3

нием одного из старших (п-1) разрядо первый R6-триггер 2 переключается из состояния двух логических единиц по первому и второму выходам в состояние логического нуля по первому выходу и логической единицы по второму, что вызывает переключение второго RS -триггера 3 в состояние логического нуля и затем переключение элемента 4 в состояние логической единицы. Последующий срез импульса на счетном входе 1 установит первый RS-триггер 2 в состояние логического нуля. Состояние счетчика в коде Грея формируется на первых выходах триггеров 5,7,...,8,9.

Функционирование счетчика, TVr-три гера которого переключаются по срезу импульса на .Т-входе, например по построении TV-триггеров на логических элементах ИЛИ-НЕ, происходит аналогично, при этом сигналы на выходах первого R5-триггера 2, элемента 4 нулевого разряда, на счетном входе

1и на R- и 5-входах R5 -триггера 6 TY-триггера 5 первого разряда будут инверсными.

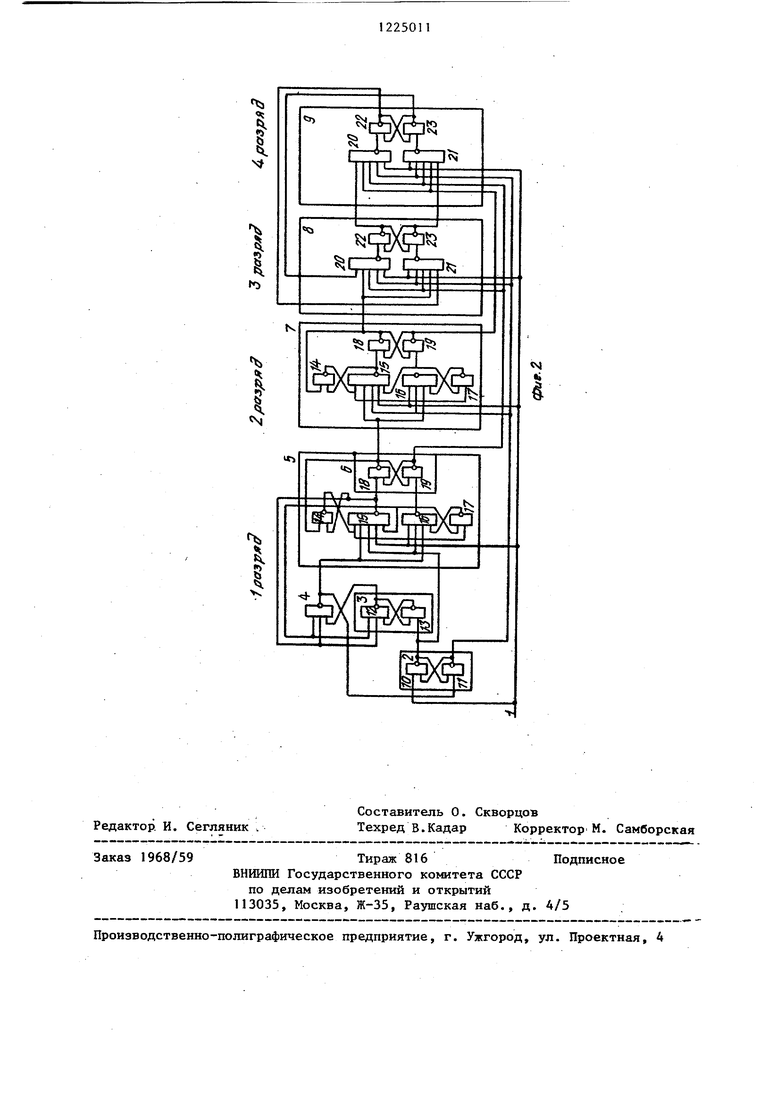

На фиг. 2 представлен четырехразрядный счетчик в коде Грея, построенный на логических элементах И-НЕ. Он содержит счетный вход 1, первый

2и второй 3 RS -триггеры и логический элемент 4, TV-триггер 5 первого разряда, содержащий, в свою очередь, RS-триггер 6, выходы которого являются выходами TV-триггера 5 первого разряда, TV-триггер 7 иа втором разряде, синхронный R5-триггер 8 третьего разряда и синхронный Яб-триггер 9 четвертого разряда, причем первый выход первого RS -триггера 2 соединен с R -входом вторичного RS -триггера 3 и первым V - входом Т -триггера 5 первого разряда первый выход второго R5 -триггера

3соединен с первым входом логического элемента 4, выход которого соединен c. R -входом первого RS -триггера 2 и вторым V -входом ту-триггера

5 первого разряда, V -входы ТУ-триггеры 7 второго разряда соединены попарно с первым выходом ТУ-триггера 5 первого разряда и вторым выходом первого RS -триггера 2. Синхровходы RS-триггера третьего разряда 8 соединены попарно со счетным входом 1, вторым выходом первого RS -триггера 2, вторым выходом TV-триггера 5 пер25011

вого разряда и первым выходом TV- триггера 7 второго разряда. Синхровходы R5 -триггера 9 четвертого .разряда соединены соответственно со 5 счетным входом, вторыми выходом первого R5 -триггера 2 и вторым выходами TV-триггеров третьего и четвертого разрядов 8 и 9. Кроме того, счетный вход соединен с 5 -входом

0 первого R5 -триггера 2 и Т-входами TV-триггеров 5 и 7, а R -вход RS - триггера 6 ТУ-триггера 5 первого разряда соединен со вторым входом элемента 4 и первым 5 -входом вто)5 рого R5-триггера 3,5-вход R5-триггера 6 Ту-триггера 5 первого разряда соединен с третьим входом элемента 4 и вторым 5 -входом второго R5 - триггера 3. Первый и второй выходы

0 КЗ-триггера третьего разряда соединены соответственно с S- и R - входами RS -триггера 9 четвертого разряда, первый и второй выходы которого соединены соответственно с

5 S- и R -входами R5 -триггера 8

третьего разряда. Первый RS-триггер 2 построен на элементах 10 и II, а второй R5 -триггер 3 - на элементах 12 и 13. ту-триггеры первого и

Q второго разрядов 5 и 7 выполнены

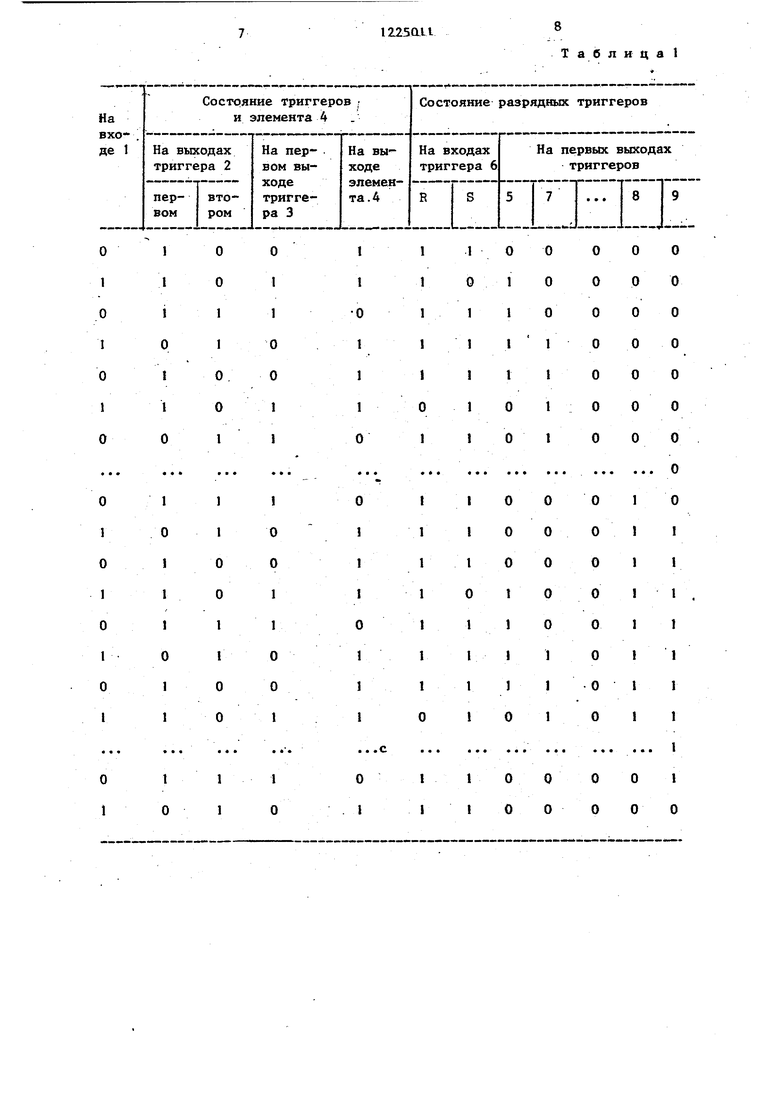

на элементах 14-19, причем RS -триггер 6 ТУ-триггера 5 первого разряда построен на элементах 18 и 19. RS-триггеры третьего и четвертого разрядов 8 и 9 построены на элементах 20-23. Функционирование счетчика (фиг. 2), построенного на логических элементах И-НЕ, поясняется последовательностью полных состояQ НИИ, представленн,ьгх э табл. 2, где указаны состояния .нтов после окончания переходных процессов, вызванных последним переключением сигнала на счетном входе 1.

5 Переключения элемента 18 TV-триггера первого разряда 5 происходят при сигналах логической единицы на выходах элементов 4 и 10 по фронту сигнала на счетном входе 1. При

0 этом первым переключается в логический нуль сигнал на входе элемента 18 или 19 R5 -триггера 6 TV-триггера 5 первого разряда, после чего параллельно переключаются элементы 18

5 и 19 и элемент 12 в состояние логической единиЩ), а элемент 13 - в состояние логического нуля, на выходе элемента 4 сохраняется сигнал логи5

ческой единицы, поэтому состояние элементов 10 и 11 первого R6 -триггера 2 не изменяется, что не позволяет в этом такте переключиться другим разрядам. Затем по срезу сигнала на счетном входе 1 устанавливаются сигналы логической единицы на входах элементов 18 и 19 RS -триггера 6 TV-триггера 5, сигнал логического нуля на выходе элемента 4, после чего устанавливаются сигналы логичес- кой единицы на вьтходах элементов 10 и 11 первого RS -триггера 2.

Последующий фронт сигнала на счетном входе 1 вызовет переключение одного из триггеров 7, 8 и 9 трех старших разрядов, для которого пре- дьщущий разряд находится в состоянии логической единицы (исключение сос- |тавляет только четвертый разряд - он переключается в состояние логического нуля при логическом нуле на выходе триггера третьего разряда 8), а все остальные предшествующие разряды находятся в состоянии логического нуля. Параллельно с переключением одного из трех триггеров 7, 8 и 9 элементы 10 и 11 первого RS-триггера 2 переключаются из состояния двух логитриггеры и логический элемент, а также TV-триггер первого разряда, содержащий R5 -триггер, выходы которого являются1 выходами TV-тригге- 5 ра первого разряда, TV-триггер в каждом из последующих (п-3) разрядов, синхронный -RS-триггер (п-1)-го разряда и синхронный R5 -триггер п-го разряда, первый выход первого to Н5-триггера соединен с R -входом

второго 1 5-триггера И первым V -входом TV-триггера первого разряда, первый выход второго RS -триггера соединен с первым входом логического элемента, выход которого соединей

I . . с R -входом первого RS-триггера и вторым V -входом ТУ-триггера первого разряда, V -входы ТУ-триггера Каждого разряда, кроме первого, соединены с первым выходом ТУ-триггера предьщущего разряда и с вторыми выходами TV-триггеров всех предшествующих разрядов, кроме предьщущего, и 25 вторым выходом первого R5 -триггера, синхровходы R5 -триггера (п-1)-го разряда соединены со счетным входом счетчика в коде Грея, вторым выходом

первого (5 -триггера, вторыми выхода,15

20

-ческих единиц в состояние логическо- 30 TY-триггеров всех разрядов, кроме

(п-2), и первым выходом TV-триггера (п-2)-го разряда, синхровхода RS- триггера п-го разряда соединены со счетным входом, вторьм выходом пер- , вого RS -триггера и вторыми выхоДаJ3 ,

ми ту Триггеров (п-2) разрядов, кроме того, счетный вход соединен с Т-входами, всех TV-триггеров и 5 -входом первого RS-триггера, о т л и- 40 чающийся тем, что, с целью упрощения счетчика, R -вход Кб -триггера ТУ-триггера первого разряда соединен с вторым входом логического элемента и первым б -входом второго

го нуля на выходе элемента 10 и логической единицы на выходе элемента 11, что вызывает переключение элементов 12 и 13 второго R5 -триггера в сосг тояние логического нуля и единицы соответственно и затем элемент 4 переключается в состояние логической единицы. Последующий срез импульса на счетном входе 1 установит элементы 10 и 11 первого R5 -триггера 2 в состояние логического нуля и единицы соответственно. Состояния чика в коде Грея снимается с дов триггеров 5, 7, В и 9,

счет- выхоФункционирование счетчика (фиг.2),45 ,R5-триггера, а б -вход R5-триггера

если его выполнить на элементах ИЛИ-НЕ, будет происходить аналогично, при этом сигналы на входах элементов 18 и 19 R 5-триггера 6 ТУ- триггера первого разряда 5, на счетЧ ном входе 1 и на выходах элемента 4, элементов 10 и 11 первого R6 - триггера 2 будут инверсными. Формула изобретения

Счетчик в коде Грея, содержащий сяетный вход, первьй и второй

225011 . 6

триггеры и логический элемент, а также TV-триггер первого разряда, содержащий R5 -триггер, выходы которого являются1 выходами TV-тригге- 5 ра первого разряда, TV-триггер в каждом из последующих (п-3) разрядов, синхронный -RS-триггер (п-1)-го разряда и синхронный R5 -триггер п-го разряда, первый выход первого to Н5-триггера соединен с R -входом

второго 1 5-триггера И первым V -входом TV-триггера первого разряда, первый выход второго RS -триггера соединен с первым входом логического элемента, выход которого соединей

I . . с R -входом первого RS-триггера и вторым V -входом ТУ-триггера первого разряда, V -входы ТУ-триггера Каждого разряда, кроме первого, соединены с первым выходом ТУ-триггера предьщущего разряда и с вторыми выходами TV-триггеров всех предшествующих разрядов, кроме предьщущего, и 25 вторым выходом первого R5 -триггера, синхровходы R5 -триггера (п-1)-го разряда соединены со счетным входом счетчика в коде Грея, вторым выходом

первого (5 -триггера, вторыми выхода,15

20

ТУ-триггера первого разряда соединен с третьим вх,одом логического элемента и вторым S -входом второго Кб-триггера, при этом первый и BTJO- рой выходы К6-триггера (n-l)-ro разряда соединены попарно соответственно с S- и R--входами R5 -триг- гера п-го разряда, первый и второй выходы которого соединены попарно соответственно с R- и 5 -входами Кб-триггера (n-l)-ro разряда.

Таблица 1

1 1 1 О 1 1 1 О

1 1 1 о 1 1 1 о

о о 1 1

о о 1 1 о о 1 1

о о 1 1

о 1 1 о о 1 1

о о 1 1 о о 1 1 о

1

о о 1 1 о о 1 1

о о 1 1 о о 1

1225011

10 Таблица2

1 1 1 1 1 о 1 1 1 1 1 1 1

о

1 1

1

о 1 1 1 1 1 1 1

о 1 1 1

1 1

о 1 1 1 1 о о о о 1 1 1 1 о о о

о о о 1 1 1 1 1 1 1 1 о о о о о

о о о о о о о 1 1 1

f

1

1 1 1 1

о о о о о о о о о о о о о о о 1

5. f

W

-Ч

«sj

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик в коде Грея | 1984 |

|

SU1202050A1 |

| Счетное устройство | 1982 |

|

SU1080250A1 |

| Синхронный счетчик | 1985 |

|

SU1257838A1 |

| 2К-разрядный счетчик в коде Грея | 1990 |

|

SU1707761A1 |

| Синхронный счетчик | 1984 |

|

SU1190520A1 |

| ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1993 |

|

RU2047939C1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Делитель частоты с регулируемым коэффициентом деления | 1982 |

|

SU1051732A1 |

| Электронное временное устройство с обнаружением отказов | 1983 |

|

SU1167574A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

Изобретение относится к области построения устройств цифровой вычислительной техники и дискретной автоматики, преимущественно на потенциальных логических элементах неизбыточных базисов; Цель изобретения - упрощение устройства. Достигается она за счет введения новых функциональных связей между схемными элементами. Счетчик кода Грея может быть реализован на элементной базе в виде логических элементов (ЛЭ) И-НЕ или ИЛИ-НЕ. Счетчик содержит счетный вход 1, RS-триггеры 2 и 3, ЛЭ 4, TV -триггер 5 первого разряда, содержащий RS-триггер, TV -триггер 7 второго разряда, синхронные RS - триггеры 8 и 9 в (п-1)-м и iп-м разрядах. В описании изобретения приводится вариант реализации устройства на ЛЭ И-НЕ. Работа поясняется по приведенным в описании таблицам. 2 табл. 2 ил. (Л Ipaap/iS 52pa { fS S {fr-t}-pff3f Aff em(.frtr3p. ft-fej/f ND IC 01

Редактор. И. Сегляник

Заказ 1968/59

Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Составитель О. Скворцов

Техред В.Кадар Корректор М. Самборская

Авторы

Даты

1986-04-15—Публикация

1984-10-08—Подача