Изобретение относится к цифровой вычислительной технике и дискретной автоматике и может быть использовано при построении счетных устройств на потенциальных логических элементах.

Цель изобретения - повышение достоверности функционирования.

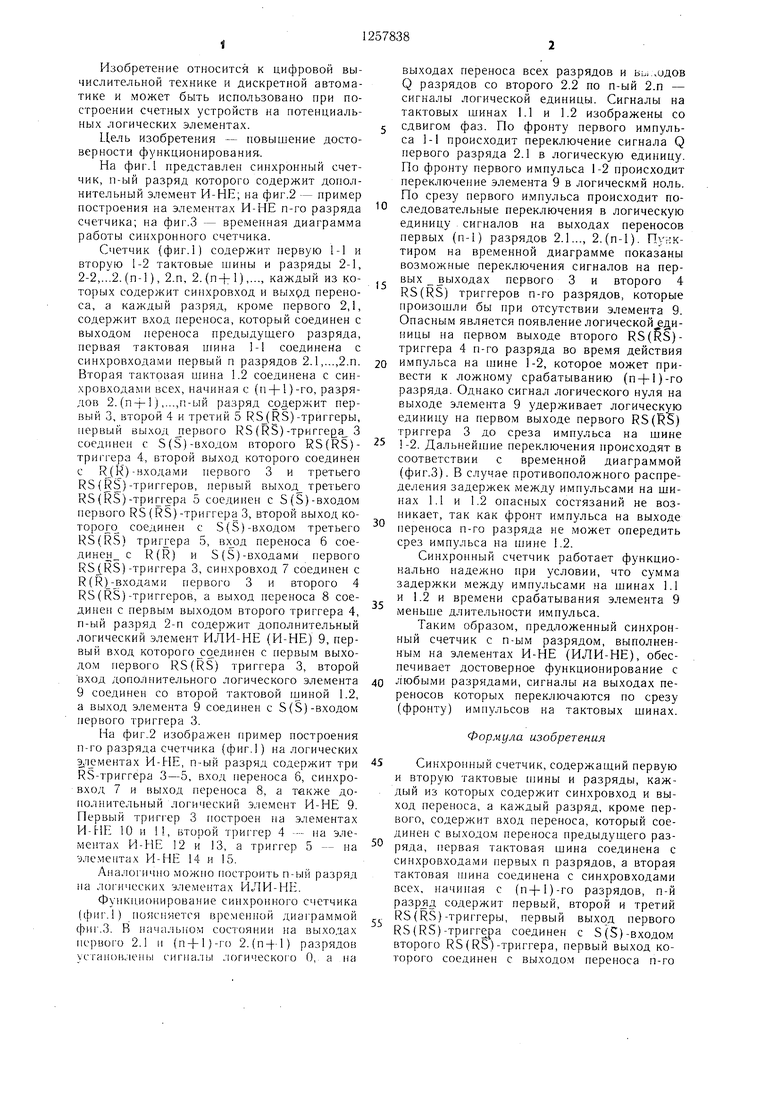

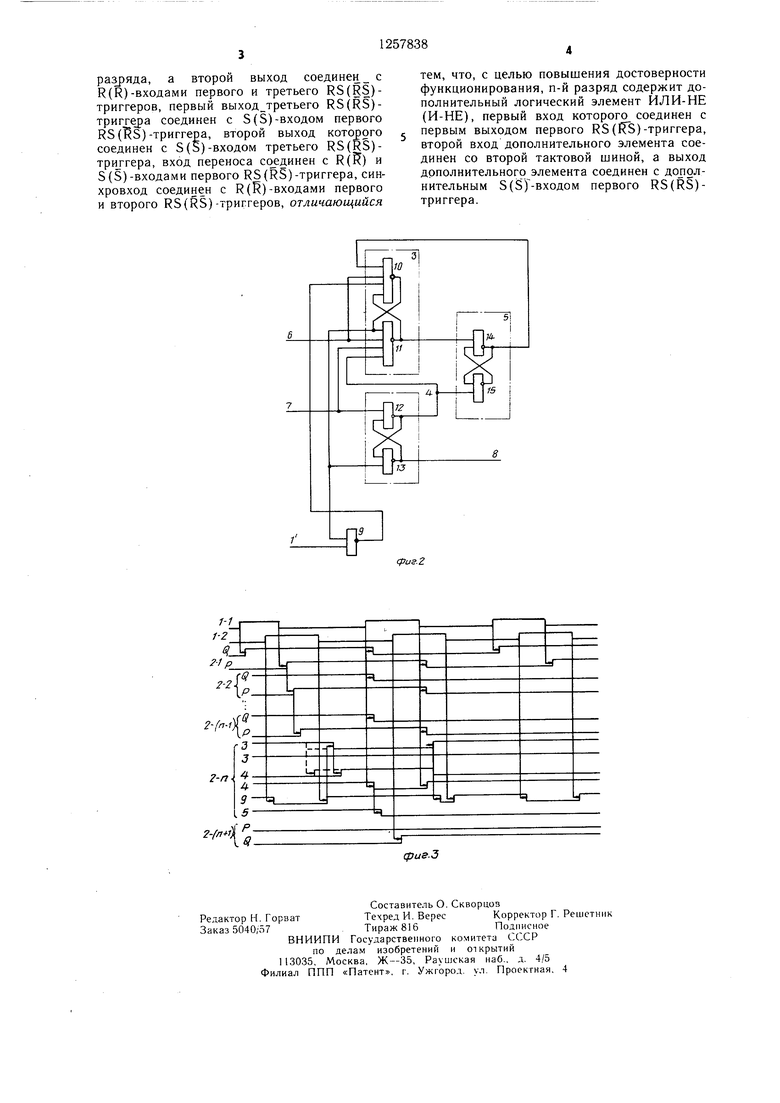

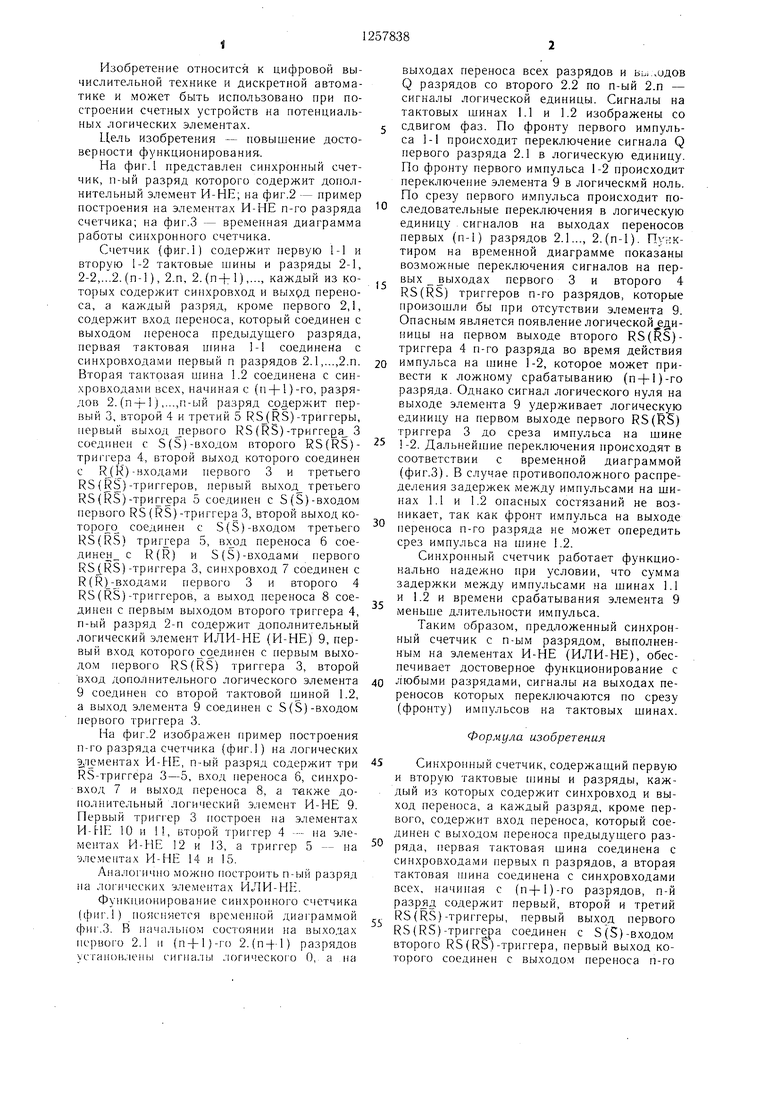

На фиг.1 представлен синхронный счетчик, п-ый разряд которого содержит дополнительный элемент И-НЕ; на фиг.2 - пример построения на элементах И-НЕ п-го разряда счетчика; на фиг.З - временная диаграмма работы синхронного счетчика.

Счетчик {фиг.1) содержит первую 1-1 и вторую 1-2 тактовые пшны и разряды 2-1, 2-2,.. 2.(п-1), 2.П, 2.(п-Ь1),.--, каждый из которых содержит синхровход и выход переноса, а каждый разряд, кроме первого 2,1, содержит вход переноса, который соединен с выходом переноса предыдущего разряда, первая тактовая нгина 1-1 соединена с синхровходами первый п разрядов 2.1,...,2.п. Вторая тактовая шина 1.2 соединена с синхровходами всех, начиная с (п-|-1)-го, разрядов 2.(n-f-i) ..п-ый разряд содержит первый 3, второй 4 и третий 5 RSJRS)-триггеры, первый выход первого RS(RS)-Tpnrrega 3 соединен с S(S)-входом второго RS{RS)- три1тера 4, второй выход которого соединен с RjR)-входами первого 3 и третьего RS (RS)-триггеров, первый выход третьего RS (RSi-Tpnr repa 5 соединен с S(S)-входом первого RS (RS)-триггера 3, второй выход ко- торого соединен с S(S)-входом третьего RS(RS) триггера 5, переноса 6 сое- динен с R(R) и S(S)-входами первого RS|RS)-триггера 3, синхровход 7 соединен с R(R)- вxoдaми первого 3 и второго 4 RS(RS)-триггеров, а выход переноса 8 сое- динеп с первым выходом второго триггера 4, п-ый разряд 2-п содержит дополнительный логический элемент ИЛИ-НЕ (И-НЕ) 9, первый вход которогоJcgeдинeн с первым выходом первого RS(RS) триггера 3, второй вход дополнительного логического элемента 9 соединен со второй тактовой шиной 1.2, а выход элемента 9 соединен с S(S)-входом первого триггера 3.

На фиг.2 изображен пример построения п-го разряда счетчика {фиг.1) на логических Э; юментах И-НЕ, п-ый разряд содержит три RS-триггера 3-5, вход переноса б, синхровход 7 и выход переноса 8, а тйкже дополнительный логический э;1емент И-НЕ 9. Первый триггер 3 построен на элементах И-НГ: 10 и 1, второй триггер 4 - на элементах И-НЕ 12 и 13, а триггер 5 - на эл с м е 11та X И-НЕ 14 и 15.

Аналогично можно построить п-ый разряд на л()-ических элементах ИЛИ-НЕ.

Функционирование синхронного счетчика (фиг.1) поясняется временной диаграммой фиг.З. В начальном состоянии на выходах первого 2.1 и {n-fl)-r() 2.{п-)--1) разрядов vcranoBjieiibi сигналы . югического О, а на

0

5

выходах переноса всех разрядов и ы.;.одов Q разрядов со второго 2.2 по п-ый 2.п - сигналы логической единицы. Сигналы на тактовых шинах 1.1 и 1.2 изображены со сдвигом фаз. По фронту первого импульса 1-1 происходит переключение сигнала Q первого разряда 2.1 в логическую единицу. По фронту первого импульса 1-2 происходит переключение элемента 9 в логическмй ноль. По срезу первого импульса происходит последовательные переключения в логическую единицу . сигналов на выходах переносов первых (п-1) разрядов 2.1..., 2.(п-1). Пунктиром на временной диаграмме показаны возможные переключения сигналов на первых выходах первого 3 и второго 4 RS(RS) триггеров п-го разрядов, которые произошли бы при отсутствии элемента 9. Опасным является появление логической ницы на первом выходе второго RS(S)- триггера 4 п-го разряда во время действия

0 импульса на шине 1-2, которое может привести к ложному срабатыванию (п + О-го разряда. Однако сигнал логического нуля на выходе элемента 9 удерживает логическую единицу на первом выходе первого RS(RS) триггера 3 до среза импульса на шине

5 1-2. Дальнейшие переключения происходят в соответствии с временной диаграммой (фиг.З). В случае противоположного распределения задержек между импульсами на шинах 1.1 и 1.2 опасных состязаний не возникает, так как фронт импульса на выходе переноса п-го разряда не может опередить срез импульса на 1.2.

Синхронный счетчик работает функционально надежно при условии, что сумма задержки .между импульсами на шинах 1.1 и 1.2 и времени срабатывания элемента 9 меньше длительности импульса.

Таким образом, предложенный синхронный счетчик с п-ым разрядом, выполненным на элементах И-НЕ (ИЛИ-НЕ), обеспечивает достоверное функционирование с любыми разрядами, сигналы на выходах переносов которых переключаются по срезу (фронту) импульсов на тактовых шинах.

Формула изобретения

5 Синхронный счетчик, содержап ий первую и вторую тактовые и разряды, каж- из которых содержит синхровход и выход переноса, а каждый разряд, кроме первого, содержит вход переноса, который соединен с выходом переноса предыдущего разряда, первая тактовая шина соединена с синхровходами первых п разрядов, а вторая тактовая 1пина соединена с синхровходами всех, начиная с (п+1)-го разрядов, п-й разряд содержит первый, второй и третий

RS(RS)-триггеры, первый выход первого RS(RS)-триггера соединен с S(S)-входом второго RS (RS)-триггера, первый выход которого соединен с выходом переноса п-го

0

5

0

0

разряда, а второй выход соединен с R(R)-входами первого и третьего RS(RS)- триггеров, первый выход третьего RS(RS)- тригге а соединен с S(S)-входом первого RS ()-триггера, второй выход соединен с S(S)-входом третьего RS(RS)- три ггера, вход переноса соединен с R(K) и S(S)-входами первого RS(RS)-триггера, син- хровход соединен с R(R)-входами первого и второго RS(RS)-триггеров, отличающийся

тем, что, с целью повышения достоверности функционирования, п-й разряд содержит дополнительный логический элемент ИЛИ-НЕ (И-НЕ), первый вход которого соединен с первым выходом первого RS (ITS)-триггера, второй вход дополнительного элемента соединен со второй тактовой шиной, а выход дополнительного элемента соединен с дополнительным 5(5У-входом первого RS(RS)- триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик в коде Грея | 1984 |

|

SU1202050A1 |

| Счетное устройство | 1982 |

|

SU1080250A1 |

| Устройство для контроля цифровых узлов | 1987 |

|

SU1571593A1 |

| Устройство для подавления дребезга контактов @ выключателей | 1988 |

|

SU1621155A1 |

| Быстродействующий селективный измеритель амплитуды ВЧ-сигнала | 1990 |

|

SU1780029A1 |

| Разряд синхронного счетчика | 1986 |

|

SU1370780A1 |

| Счетное устройство | 1980 |

|

SU953741A1 |

| ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1993 |

|

RU2047939C1 |

| Счетчик в коде грея | 1984 |

|

SU1225011A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

Изобретение относится к цифровой вычислительной технике и дискретной автоматике. Может быть использовано при построении счетных устройств на потенциальных логических элементах. Цель изобретения - повышение достоверности функционирования. В устройстве, содержащем 1-1 и 1-2 тактовые шины, разряды 2-1, 2 (п-1), 2п, 2(п + 1), каждый из которых содержит син- хровход и выход переноса, а каждый разряд, кроме 2-1, содержит вход переноса, п-й разряд содержит RS (RS) триггеры 3.4,5, для достижения цели в п-й разряд введен дополнительный логический элемент ИЛИ-НЕ (И-НЕ) 9. В описании изобретения приведен вариант построения п-го разряда счетчика на логических элементах И-НЕ. Устройство работает надежно при условии, что суммы задержки между импульсами на шинах 1-1 и 1-2 времени срабатывания элемента 9 меньше длительности импульса. Устройство обеспечивает достоверное функционирование с любыми разрядами, сигналы на выходах переносов которых переключаются по срезу (фронту) импульсов на тактовых шинах. 3 ил. (О (Л 2-1 2-2 /-/ 1-2 2-/7 2 -fn l to ел sj 00 00 00

| Счетное устройство | 1980 |

|

SU892737A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Филиппов А | |||

| Г., Белкин О | |||

| С | |||

| Проектирование логических узлов ЭВМ | |||

| М.: Советское радио, 1974. | |||

Авторы

Даты

1986-09-15—Публикация

1985-04-16—Подача