(5k) УСТРОЙСТВО ВРЕМЕННОЙ ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реле времени | 1984 |

|

SU1211871A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1697265A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРИОДИЧЕСКОГО СИГНАЛА В ЧАСТОТУ И ПЕРИОД | 2012 |

|

RU2520409C2 |

| Преобразователь напряжения в частоту | 1988 |

|

SU1522407A1 |

| УСТРОЙСТВО ВЫБОРКИ И ХРАНЕНИЯ | 2007 |

|

RU2389070C2 |

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Аналоговый перемножитель | 1984 |

|

SU1166143A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388987A1 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматического управления в качестве реле времени.

Известны устройства, содержащие накопительный конденсатор, зарядную цепь, пиковый распределитель, катодный повторитель, ключ и дискриминатор. Принцип работы устройства основан на заряде и разряде накопительного конденсатора через резисторы с разным значением сопротивлений 1 .

Недостатком данного устройства является то, что точность его работы в значительной степени определяется линейностью функции преобразования в области малых времен, т.е. на начальном участке кривой заряда накопительного конденсатора.

Наиболее близким к предлагаемому является устройство, содержащее со- единенные последовательно времяза

дающую цепь, повторитель, блок dpa нения, источник опорного напряжения формирователь ,2J.

Недостатком известного устройства является то, что точность его работы зависит от стабильности источника опорного напряжения и, кроме того, диапазон временной задержки ограничен величиной постоянной времени врёмязадающей цепочки.

10

Цель изобретения - повышение точности и расширение диапазона временной задержки.

Поставленная цель достигается тем, что в устройстве временной за15держки, содержащем интегратор и последовательно соединенные источник опорного напряжения, блок сравнения и формирователь, причем выход интегратора соединен с другим входом

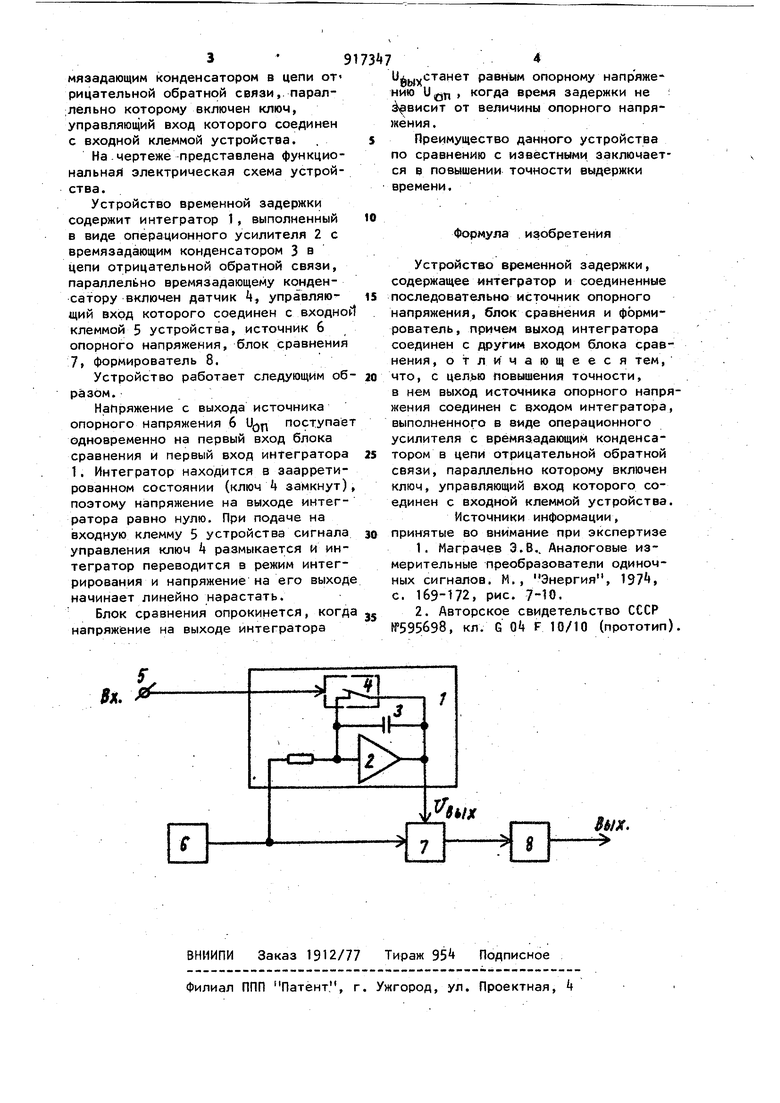

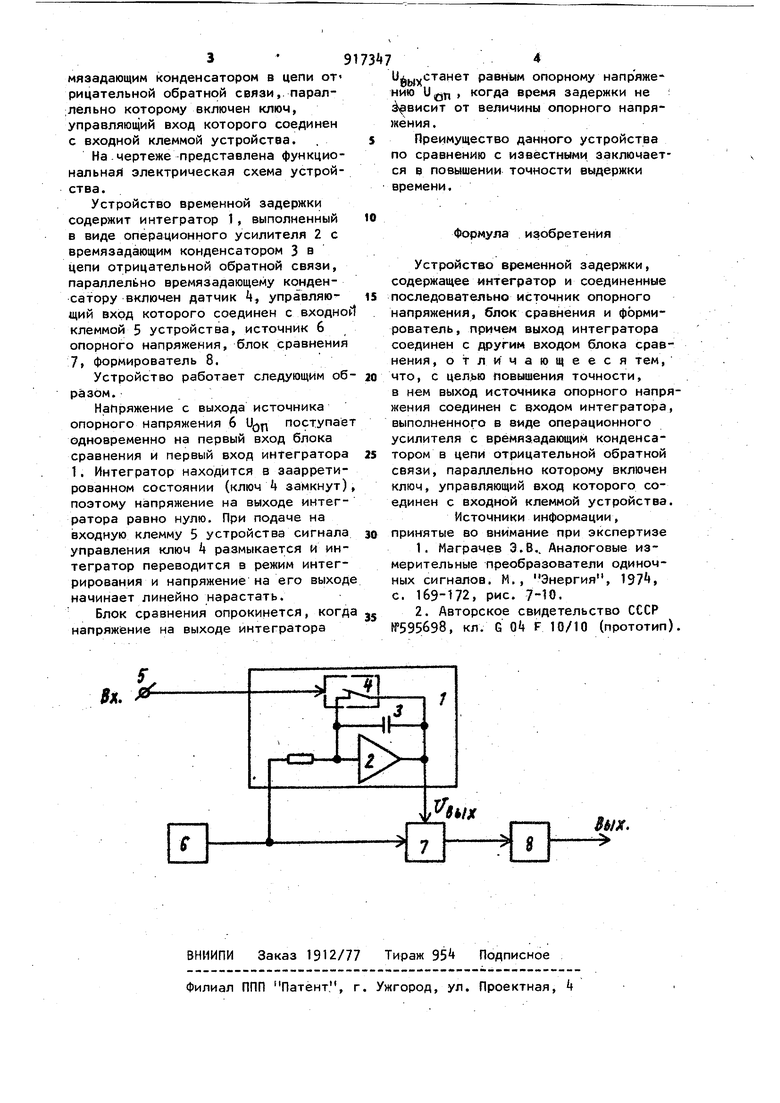

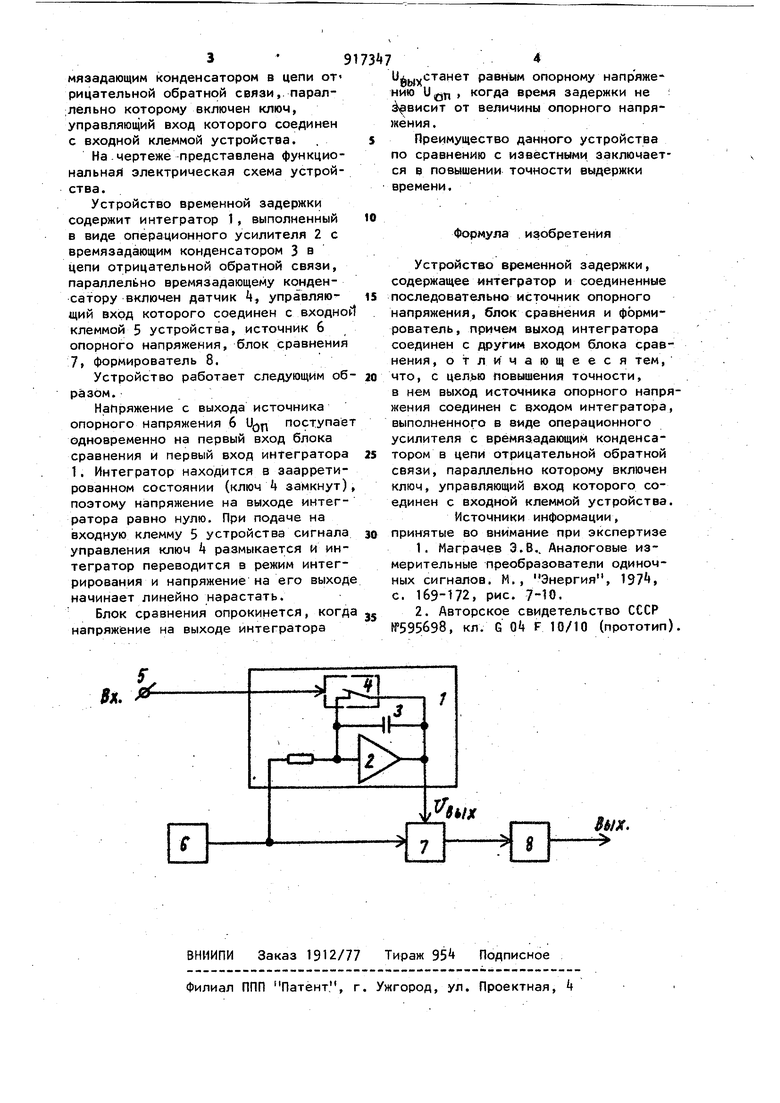

20 блока сравнения, выход источника опорного напряжения соединен с входом интегратора, выполненного в виде операционного у.силителя с вре3мяэадающим конденсатором в цепи оТ рицательной обратной связи,, парал;лельно которому включен ключ, управляющий вход которого соединен с входной клеммой устройства. На.чертеже представлена функциональнай электрическая схема устройства. Устройство временной задержки содержит интегратор 1, выполненный в виде операционного усилителя 2 с времязадающим конденсатором 3 в цепи отрицательной обратной связи, параллельно времязадающему конденсатору включен датчик 4 управляющий вход которого соединен с вxoднo клеммой 5 устройства, источник 6 опорного напряжения, блок сравнения 7, формирователь 8, Устройство работает следующим об разом. Напряжение с выхода источника опорного напряжения 6 поступае одновременно на первый вход блока сравнения и первый вход интегратора 1. Интегратор находится в заарретированном состоянии (ключ t замкнут) поэтому напряжение на выходе интегратора равно нулю. При подаче на входную клемму 5 устройства сигнала управления ключ k размыкается и интегратор переводится в режим интегрирования и напряжение на его выход начинает линейно нарастать. Блок сравнения опрокинется, когд напряжение на выходе интегратора 4 и уустанет равным опорному напряжению U|Q , когда время задержки не : висит от величины опорного напряжения . Преимущество данного устройства по сравнению с известными заключается в повышении точности выдержки времени. Формула изобретения Устройство временной задержки, содержащее интегратор и соединенные последовательно источник опорного напряжения, блок сравнения и формирователь, причем выход интегратора соединен с другим входом блока сравнения ,отличающееся тем, что, с целью Повышения точности, в нем выход источника опорного напряжения соединен с входом интегратора, выполненного в виде операционного усилителя с врёмязадающиМ конденсатором в цепи отрицательной обратной связи, параллельно которому включен ключ, управляющий вход которого соединен с входной клеммой устройства. Источники информации, принятые во внимание при экспертизе 1.Маграчев Э.В.. Аналоговые измерительные преобразователи одиночных сигналов. Н,, Энергия, 197, с. 169-172, рис. 7-10. 2.Авторское свидетельство СССР №595698, кл. G О F 10/10 (прототип).

Авторы

Даты

1982-03-30—Публикация

1979-09-06—Подача