1

Изобретение относится к импульсной технике и может быть использовано в синтезаторах частот, требующих поиышенного быстродействия.

Цель изобретения - повьпиение быстродействия и надежности функционирования за счет обеспечения синхронного режима р.аботы.

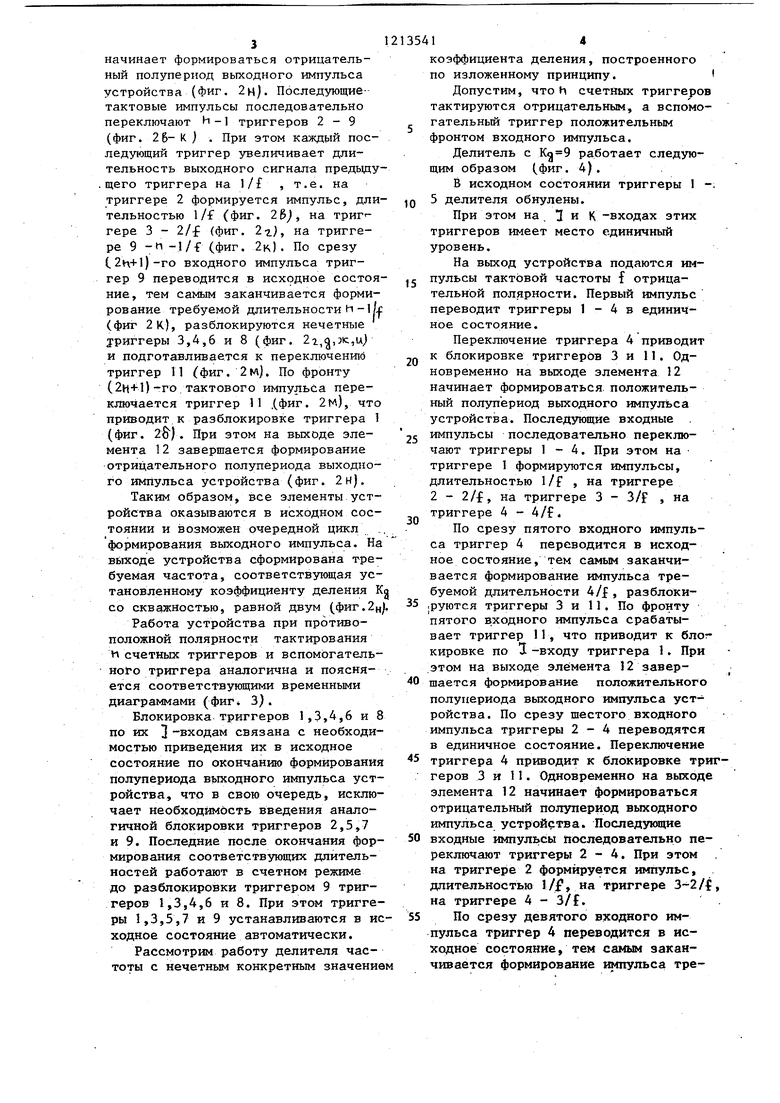

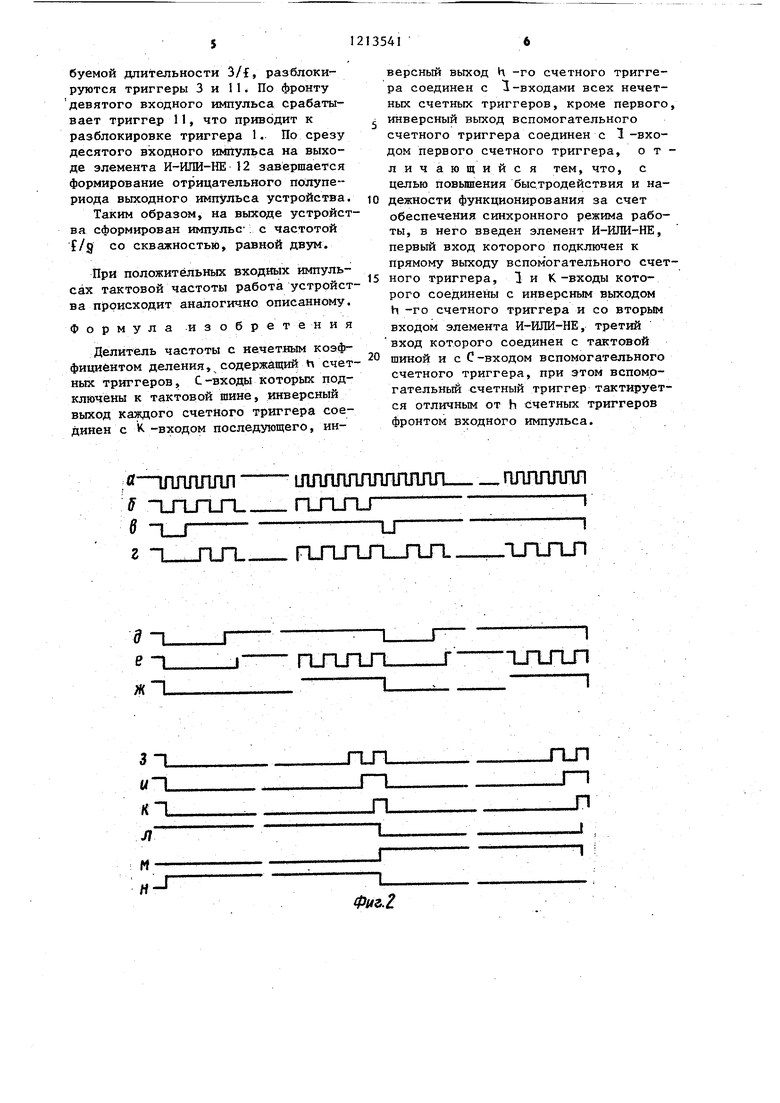

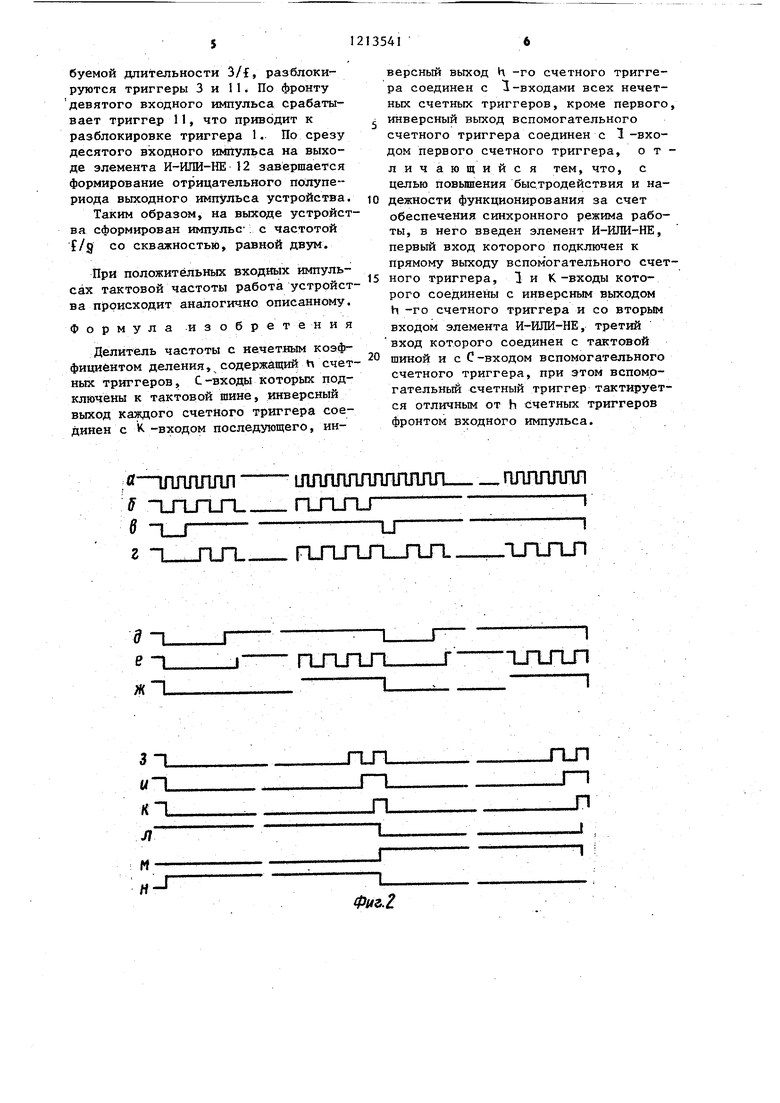

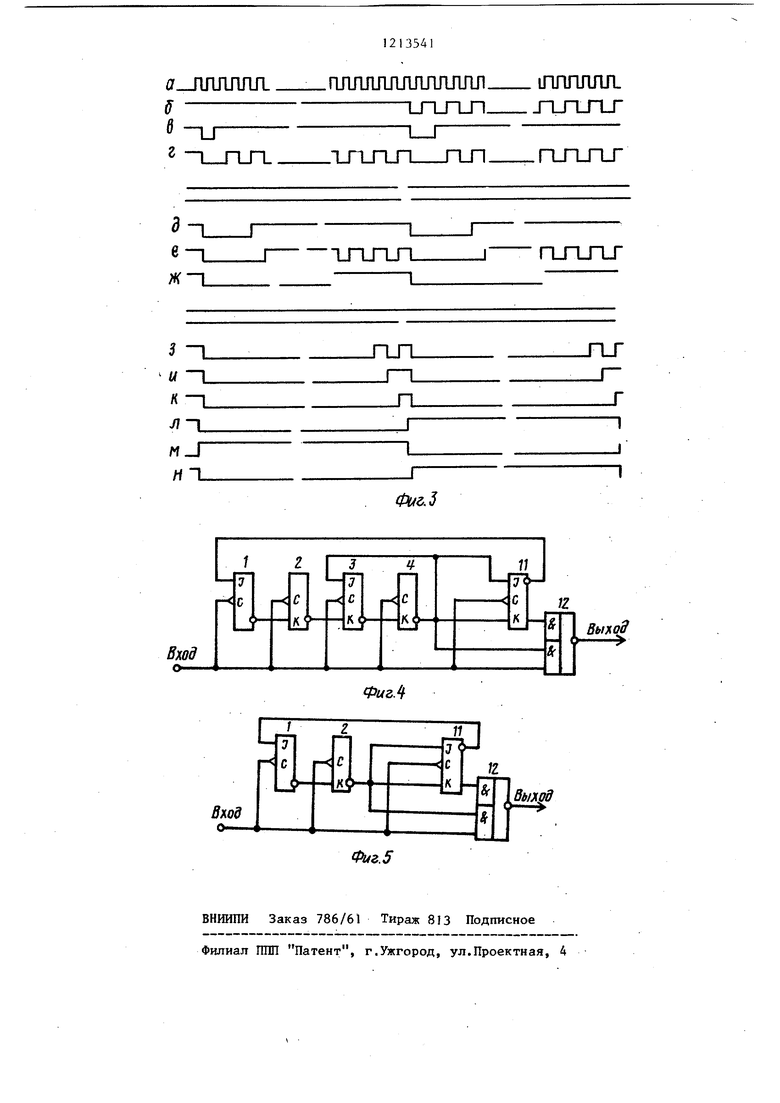

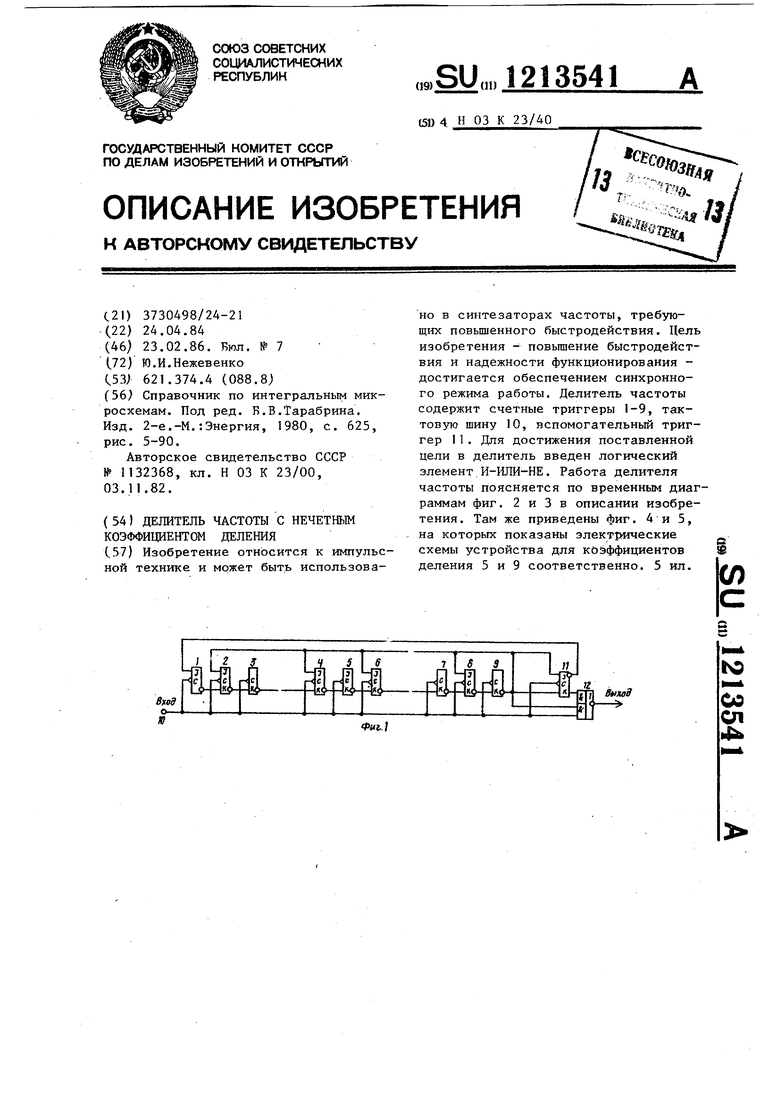

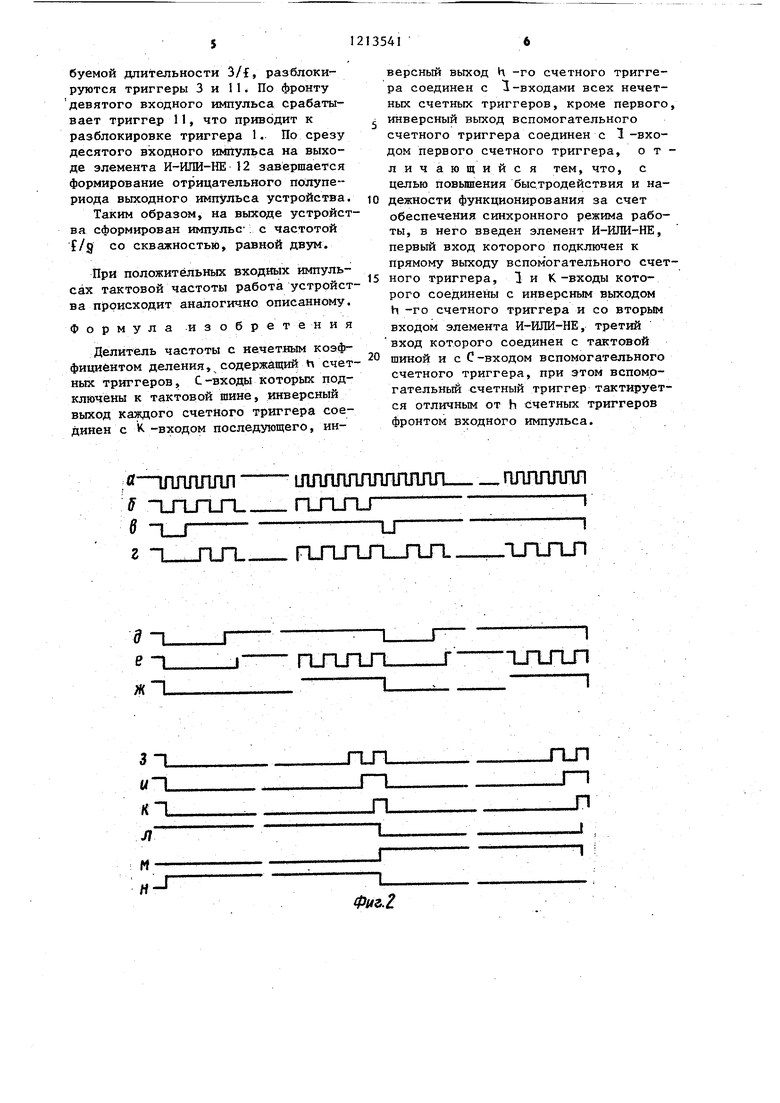

На фиг. 1 приведена электрическа функциональная схема делителя частоты с нечетным коэффициентом деления -на фиг. 2 и 3 -временные диаграммьг, поясняющие работу делителя при различных полярностях входных импульсов; на фиг. 4 и 5 - электрические схемы устройства с конкретным значением коэффициента деления: девять и пять соответственно.

Делитель частоты с нечгтным коэффициентом деления содержит h счетных триггеров I - 9, С -входы которых подключены к тактовой шине 10, инверсный выход каждого счетного тргера 1 - 9 соединен с К -входом последующего, инверсный выход вспомогательного триггера 11 соединен с 1-входом первого счетного триггера 1, первый вход элемента И-ИЛИ- НЕ 12 подключен к прямому выходу вспомогательного триггера II, 1- и К -входы вспомогательного триггера II соединены с инверсным выходом h -го счетного триггера 9 и с вторым входом элемента И-Щ1И-НЕ 12, третий вход которого соединен с . актовой шиной 10 и с С-входом вспомогательного триггера 11, инверсный выход h-го счетного триггера 9 соединен с 1 -входами нечетных счетных триггеров 3,4,6,8, кроме первого триггера 1.

Реализация устройства с коэффициентом деления Кд требует п счет. Х-А-1

ных триггеров, где h -j- тактируемых отрицательным (.положительным) фронтом входного импульса, вспомогательный триггер, тактируемый положительным (отрицательным) фронтом входного импульса и элемент И-ИЛИ-НЕ.

Рассмотрим работу устройства с коэффициентом деления К/ч, 4м+ 1, где ,1,2 ...

Допустим, h триггеров 1-9 тактируются отрицательным, а вспомогательный триггер 11 положительными фронтами входного (с шины 10) им- .пульса (фиг. 2а).

5412

В исходном состоянии триггеры устройства обнулены. При этом на 1-входах триггеров 1,3,4,6,8 (фиг. 2 SjT.-j , ж; ,м) имеет место едипичный уровень за счет перекрестных связей с инверсных выходов триггеров 11 и 9. Таким образом,И триггеров 1 - 9 и вспомогательный триггер 11 подготовлены к переклю0 чению по их С-входам.

На вход устройства (шину 10) подаются импульсы тактовой частоты f отрицательной полярности ( фиг. 2а). Первый тактовый импульс переводит

5 линейку из н триггера 9 (фиг. 2чЬ-к5 в единичное . состояние, взводит триггер 1 (фиг. 26). Переключение триггера 9 (фиг. 2 к) приводит к блокировке нечетных триггеров 3,4, 6

0 и 8 по их 4-входам (фиг. 2гЛ,ж,и) . Одновременно на выходе элемента 12 начинает формироваться положительный полупериод выходного импульса устройства (фиг. 2н). Последующие

5 входные импульсы последовательно переключают триггеры 1 - 9. При этом каждьй последующий триггер увеличивает длительность выходного сигнала предьщущего триггера на 1/f , т.е.

Q на триггере 1 формируется импульс, длительностью 1/f (фиг. 2S } , на триггере 2 - 2/f(фиг. , на триггере 3 - 3/-f (фиг. 2г), и так далее, на триггере 9 -h/f (фиг. 2к).

По срезу (h+l) -го входного импульса триггер 9 переводится в исходное состояние (фиг. 2 Ц,), тем самым заканчивается формирование требуемой длительности h/f (фиг. 2к), разблокируются нечётные триггеры 3,4,6 и 8 (фиг. 2 2,,3c,u) и подготавливается к переключению триггер 11 (фиг. 2cu).

По фронту (h-ь 1)-го тактового им- пульса срабатьтает триггер 11 СФиг. 2м), что приводит к блокировке по Д-входу триггера 1 (фиг. 26). . При этом завершается формирование положительного полупериода выходно- го импульса устройства (фиг. 2м).

По срезу (h+2)-го входного импульса линейка из h-1 триггеров 2-9 (фиг. 2 - к) переводится в единичное состояние. Переключение 5 триггера 9 (фиг. 2 к) приводит к блокировке нечетных триггеров 3,4,6 и 8, по их 3 -входам (фиг, 2г,о,ж,и). Одновременно на выходе элемента 12

ачинает формироваться отрицательый полупериод выходного импульса стройства (фиг. 2н). Последующие- тактовые импульсы последовательно ереключают h-1 триггеров 2-9 (фиг. 26- К) . При этом каждый поседующий триггер увеличивает длительность выходного сигнала предыду- щего триггера на 1/f , т.е. на триггере 2 формируется импульс, длительностью 1/f (фиг. 2&), на триг-- гере 3 - 2/f (фиг. 2i), на триггере 9 -п -1/f (фиг. 2к). По срезу (,)-го входного импульса триггер 9 переводится в исходное состояние, тем самым заканчивается формирование требуемой длительности h-1/ (фиг 2 к), разблокируются нечетные триггеры 3,4,6 и 8 (фиг. 21,,ж,ц) и подготавливается к переключеник) триггер 11 (фиг. 2м). По фронту (2н+1)-го.тактового импульса переключается триггер 11 .(фиг. 2м), что приводит к разблокировке триггера 1 (фиг. 28). При этом на выходе элемента 12 завершается формирование отрицательного полупериода выходного импульса устройства (фиг. 2н).

Таким образом, все элементы устройства оказываются в исходном состоянии и возможен очередной цикл , формирования выходного импульса. На выходе устройства сформирована требуемая частота, соответствующая установленному коэффициенту деления Kg со скважностью, равной двум (фиг.2н).

Работа устройства при противоположной полярности тактирования и счетных триггеров и вспомогательного триггера аналогична и поясняется соответствующими временными диаграммами (фиг 3).

Блокировка триггеров 1,3,4,6 и 8 по их 3-входам связана с необходимостью приведения их в исходное состояние по окончанию формирования полупериода вьжодного импульса устройства, что в свою очередь, исключает необходимость введения аналогичной блокировки триггеров 2,5,7 и 9. Последние после окончания формирования соответствующих длительностей работают в счетном режиме до разблокировки триггером 9 триггеров 1,3,4,6 и 8. При этом триггеры 1,3,5,7 и 9 устанавливаются в исходное состояние автоматически.

Рассмотрим работу делителя частоты с нечетным конкретным значением

5

0

5

0

5

0

5

0

5

коэффициента деления, построенного по изложенному принципу.

Допустим, что h счетных триггеров тактируются отрицательным, а вспомогательный триггер положительным фронтом входного импульса.

Делитель с работает следующим образом (фиг. 4).

В исходном состоянии триггеры 1 -. 5 делителя обнулены.

При этом на , tl и К -входах этих триггеров имеет место единичный уровень.

На выход устройства подаются импульсы тактовой частоты f отрицательной полярности. Первый импульс переводит триггеры 1 - 4 в единичное состояние.

Переключение триггера 4 приводит к блокировке триггеров 3 и 11. Одновременно на выходе элемента 12 начинает формироваться положительный полупериод выходного импульса устройства. Последующие входные . импульсы последовательно переключают триггеры 1 - 4. При этом на триггере 1 формируются импульсы, длительностью 1/f , на триггере 2 - 2/f, на триггере 3 - 3/f , на триггере 4 - 4/f.

По срезу пятого входного импульса триггер 4 переводится в исходное состояние, тем самым заканчивается формирование импульса требуемой длительности 4/f, разблоки- .руются триггеры 3 и 11. По фронту пятого входного импульса срабатывает триггер 11 , что приводит к блот- кировке по 1 -входу триггера 1. При этом на выходе элемента 12 завершается формирование положительного полупериода выходного импульса устройства. По срезу шестого входного импульса триггеры 2-4 переводятся в единичное состояние. Переключение триггера 4 приводит к блокировке триггеров 3 и 11. Одновременно на выходе элемента 12 начииает формироваться отрицательный полупериод выходного импульса устройства. Последующие входные импульсы йоследовательно переключают триггеры 2 - 4. При этом на триггере 2 формируется импульс, длительностью 1/, иа триггере 3-2/{, иа триггере 4 - 3/..

По срезу девятого входного импульса триггер 4 переводится в исходное состояние, тем самым заканчивается формирование импульса требуемой длительности 3/f, разблокируются триггеры 3 и 11. По фронту девятого входного импульса срабатывает триггер 11, что приводит к разблокировке триггера 1. По срезу десятого входного импульса на выходе элемента И-ИЛИ-НЕ 12 завершается формирование отрицательного полупериода выходного импульса устройства.

Таким образом, на выходе устройства сформирован импульс- с частотой f/g со скважностью, равной двум.

При положительных входных импульсах тактовой частоты работа устройства происходит аналогично описанному.

Формула .изобретения

Делитель частоты с нечетным коэффициентом деления, содержа щий h счетных триггеров, С-входы которьк подключены к тактовой шине, инверсный выход каждого счетного триггера соединен с К. -входом последующего, ин

шлллллллгшлл

плти

LJ

г .

rUTJlJT-JTri

Р П.

П-ЛЛЛ.

версный выход h -го счетного триггера соединен с 1-входами всех нечетных счетных триггеров, кроме первого, инверсный выход вспомогательного счетного триггера соединен с 1 -входом первого счетного триггера, о т - л и ч а ю щ и и с я тем, что, с целью повышения быстродействия и на-

дежности функционирования за счет обеспечения синхронного режима работы, в него введен элемент И-ИЛИ-НЕ, первый вход которого подключен к прямому выходу вспомогательного счетного триггера, 1 и К -входы которого соединены с инверсным выходом h -го счетного триггера и со вторым входом элемента И-ИЛИ-НЕ, третий вход которого соединен с тактовой

шиной и с С-входом вспомогательного счетного триггера, при этом вспомогательный счетный триггер тактируется отличным от h счетных триггеров фронтом входного импульса.

гшшлпл

.итлл

гллл

шишлллялшшл.

LTLTLn.

.

.innrmjuL

-гииаг

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с нечетным коэффициентом деления | 1984 |

|

SU1213540A1 |

| Делитель частоты с нечетным коэффициентом деления (его варианты) | 1982 |

|

SU1132368A1 |

| Управляемый делитель частоты | 1985 |

|

SU1277389A1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Делитель частоты следования импульсов | 1987 |

|

SU1598165A1 |

| Умножитель частоты | 1984 |

|

SU1179334A1 |

| Делитель частоты следования импульсов | 1983 |

|

SU1128390A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1661981A1 |

| Адаптивный эхокомпенсатор | 1989 |

|

SU1665520A1 |

Изобретение относится к импульсной технике и может быть использовано в синтезаторах частоты, требующих повышенного быстродействия. Цель изобретения - повышение быстродействия и надежности функционирования - достигается обеспечением синхронного режима работы. Делитель частоты содержит счетные триггеры 1-9, тактовую шину 10, вспомогательный триггер 11. Для достижения поставленной цели в делитель введен логический элемент.И-ИЛИ-НЕ. Работа делителя частоты поясняется по временным диаграммам фиг. 2 и 3 в описании изобретения. Там же приведены фиг. 4 и 5, на которых показаны электрические схемы устройства для коэффициентов деления 5 и 9 соответственно. 5 ил. О) 8иявЗ Фиг..} КС со О1 J

д

е ж

иитл.

rUTLTLT

пл

гъг

Фиг.З

ФигЛ

Выход

ВНИИПИ Заказ 786/61 Тираж 813 Подписное Филиал ШШ Патент, г.Ужгород, ул.Проектная, 4

Фиг. 5

| Справочник по интегральным микросхемам | |||

| Под ред | |||

| Б.В.Тарабрина | |||

| Изд | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ТАНК-ПАРОВОЗ | 1923 |

|

SU625A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Делитель частоты с нечетным коэффициентом деления (его варианты) | 1982 |

|

SU1132368A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-02-23—Публикация

1984-04-24—Подача