Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики, вычислительной техники и связи, в частности при построении цифровых синтезаторов частоты импульсных сигналов.

Известны управляемые делители частоты следования импульсов, содержащие счетчик, триггеры и логические элементы совпадения. Работа этих устройств основана на сравнении выходного кода счетчика с заданным коэффициентом деления и формировании в моменты их равенства выходных импульсов (Смирнов Ю.В. Управляемый делитель частоты импульсов. Авторское свидетельство СССР N 1403365, кл. H 03 K 23/66, опубл. 15.06.88 г., бюллетень N 22; Климов В.В. Управляемый делитель частоты. Авторское свидетельство СССР N 1262726, кл. H 03 K 23/66, опубл. 07.10.86 г., бюллетень N 37; Мельников А.А., Рыжевский А. Г., Трифонов Е.Ф. Обработка частотных и временных импульсных сигналов. - М.: Энергия, 1976 г. - с. 18-28, рис. 6-17).

К недостаткам известных устройств относится зависимость паузы между выходными импульсами от коэффициента деления, при повышении которого увеличивается скважность формируемых импульсов.

Наиболее близким по технической сущности (прототипом) является управляемый делитель частоты следования импульсов, содержащий входную шину, шину управления и шину кода коэффициента деления, два элемента совпадения, первый вход одного из которых соединен с первым разрядом шины кода коэффициента деления, вычитающий счетчик, информационные входы которого подключены к второму и последующим разрядам шины кода коэффициента деления, а его счетный вход соединен с входной шиной, и два триггера, выход второго из которых является выходом устройства (Бантюков Е.Н. Управляемый делитель частоты следования импульсов. Авторское свидетельство СССР N 1338066, кл. H 03 K 23/68, опубл. 15.09.87 г., бюллетень N 34).

В этом устройстве на выходе формируются короткие импульсы, длительность которых определяется периодом входного сигнала, поэтому при изменении коэффициента деления изменяется расстояние (пауза) между импульсами. Это приводит к изменению скважности формируемых импульсов и, как следствие, к изменению действующего значения выходного сигнала. При использовании известных устройств в системах автоматического регулирования скорости электродвигателей понижение скважности импульсов при большом коэффициенте деления частоты приводит к уменьшению выходной мощности, а при построении цифровых синтезаторов частоты - к уменьшению амплитуды или мощности формируемых сигналов.

Технической задачей изобретения является формирование выходных импульсов заданной частоты со скважностью, равной двум, независимо от коэффициента деления частоты.

Для решения поставленной задачи в устройство, содержащее входную шину, шину управления и шину кода коэффициента деления, два элемента совпадения, первый вход одного из которых соединен с первым разрядом шины кода коэффициента деления, вычитающий счетчик, информационные входы которого подключены к второму и последующим разрядам шины кода коэффициента деления, а счетный вход вычитающего счетчика соединен с входной шиной, и два триггера, выход второго из которых является выходом устройства, дополнительно введены мажоритарный элемент и элемент "Исключающее ИЛИ". Первый вход элемента "Исключающее ИЛИ" подключен к входной шине устройства, второй вход - к выходу первого элемента совпадения, а выход элемента "Исключающее ИЛИ" соединен с входом запуска первого триггера и первым входом мажоритарного элемента. Второй вход мажоритарного элемента подключен к выходу заема вычитающего счетчика, а третий вход объединен с выходом мажоритарного элемента и подключен к первому входу второго элемента совпадения, второй вход которого соединен с шиной управления и входом сброса (R-входом) второго триггера, а его выход подключен к входу предварительной установки вычитающего счетчика и входу запуска второго триггера. Выход второго триггера соединен с D-входом первого триггера, к выходу которого подключен второй вход первого элемента совпадения.

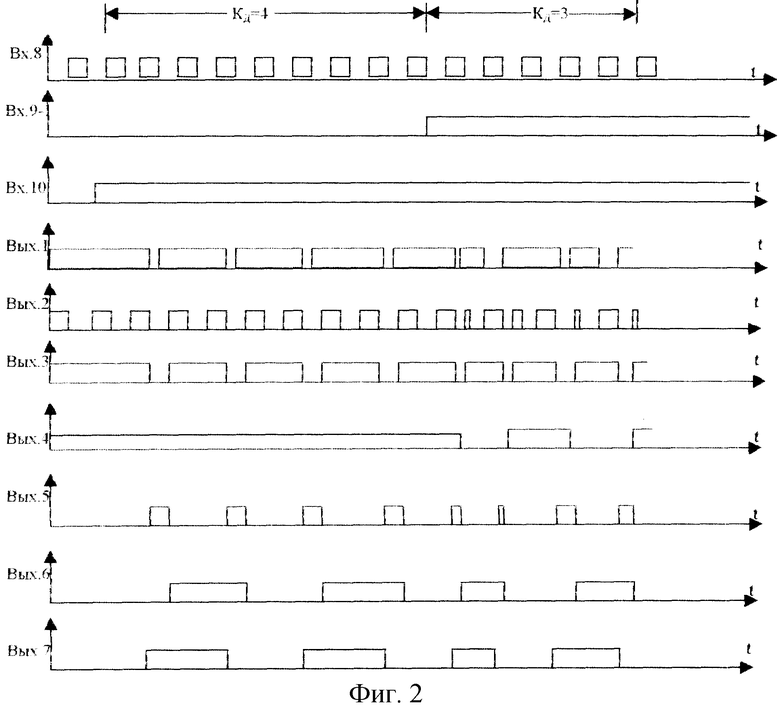

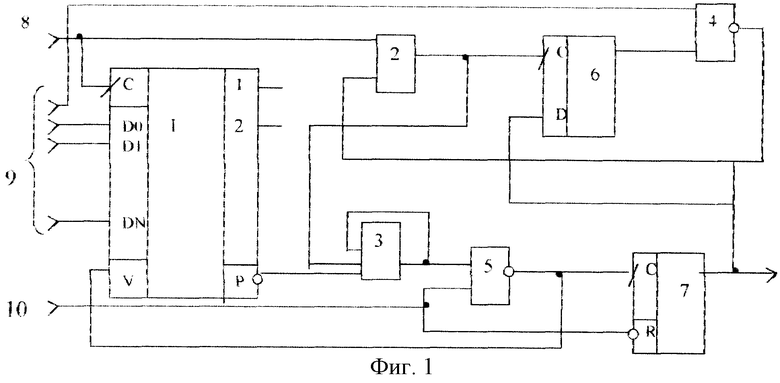

На фиг. 1 приведена электрическая функциональная схема управляемого делителя частоты импульсов, а на фиг. 2 показаны временные диаграммы, поясняющие работу устройства.

Устройство содержит вычитающий счетчик 1, элемент "Исключающее ИЛИ" 2, мажоритарный элемент 3, первый 4 и второй 5 элементы совпадения, первый 6 и второй 7 триггеры.

Входная шина 8 подключена к счетному входу вычитающего счетчика 1 и первому входу элемента "Исключающее ИЛИ" 2, выход которого соединен с тактовым входом запуска триггера 6 и первым входом мажоритарного элемента 3, второй вход которого подключен к инверсному выходу заема счетчика 1, а третий вход и выход мажоритарного элемента 3 объединены и соединены с первым входом элемента совпадения 5, инверсный выход которого подключен к входу предварительной установки вычитающего счетчика 1 и входу запуска триггера 7. Выход триггера 7 соединен с выходом всего устройства и подключен к D-входу триггера 6, выход которого соединен с вторым входом первого элемента совпадения 4. Первый вход элемента совпадения 4 соединен с первым (младшим) разрядом шины 9 кода установки коэффициента деления, остальные разряды которой, начиная со второго, подключены к информационным входам вычитающего счетчика 1. Кроме того, второй вход элемента совпадения 5 подключен к шине управления 10 и соединен с инверсным R-входом сброса триггера 7.

Управляемый делитель частоты импульсов работает следующим образом.

В исходном положении на шину 8 поступают входные импульсы высокой частоты fВХ, а на шине 9 в двоичном коде установлен заданный коэффициент деления частоты KД. На шину 10 поступает запрещающий сигнал нулевого уровня, поэтому элемент совпадения 5 установлен в единичное состояние и при его выходном сигнале высокого уровня счетчик 1 находится в состоянии предварительной установки, т. е. режиме записи данных, поступающих на его информационные входы от шины 9 кода коэффициента деления. Триггер 7 находится в нулевом состоянии, так как на его R-вход подан сигнал "0" по шине 10. Работа схемы разрешается подачей сигнала единичного уровня по шине управления 10. При этом дальнейший режим работы устройства зависит от четного или нечетного значения коэффициента деления частоты на шине 9.

Если коэффициент деления четный, то в первом (младшем) разряде шины 9 двоичного кода коэффициента деления будет сигнал нулевого уровня. При этом элемент совпадения 4 находится в единичном состоянии, и на его выходе формируется сигнал логической "1", который поступает на вход элемента 2 "Исключающее ИЛИ". Особенность работы элемента "Исключающее ИЛИ" состоит в том, что при одном входном сигнале нулевого уровня этот элемент выполняет функцию повторителя, т.е. просто передает на выход второй входной сигнал, а при первом сигнале единичного уровня элемент "Исключающее ИЛИ" выполняет функцию логического инвертора - передает на выход второй входной сигнал с инверсией уровня (при входном уровне логической "1" на выходе формируется сигнал логического "0" и наоборот). Поэтому при четном коэффициенте деления на выходе элемента 2 "Исключающее ИЛИ" формируется сигнал, инверсный по отношению к сигналу на шине 8, или при скважности входного сигнала Q = 2 на выходе элемента 2 формируются аналогичные импульсы, сдвинутые на фазовый угол 180o. При работе вычитающего счетчика 1 по переднему фронту входного импульса на шине 8 выполняется операция вычитания единицы из записанного значения кода деления. Например, при значении коэффициента деления KД = 4 на шине 9 установлен двоичный код "100". Так как информационные входы D0...DN счетчика 1 подключены к второму и последующим разрядам шины кода коэффициента деления, то на его входах D0...DN будет код "10", соответствующий цифре KД/2 = 2. Вследствие этого при появлении первого импульса на счетном входе вычитающего счетчика его выходной код становится на единицу меньше, а при появлении второго счетного импульса на шине 8 счетчик 1 устанавливается в нулевое состояние, и на его выходе заема появляется нулевой уровень сигнала, который поступает на второй вход мажоритарного элемента 3.

Мажоритарный элемент обычно выполняет логическую функцию выбора двух сигналов из трех входных, т.е. если на два или три его входа приходят сигналы логического "0" - на выходе появляется "0", а при единичном уровне двух или трех входных сигналов на выходе мажоритарного элемента появляется логическая "1". При объединении одного из входов мажоритарного элемента с его выходом реализуется функция элемента памяти: если мажоритарный элемент ранее находился в единичном состоянии, то для его переключения в нулевое состояние необходимо подать на первый и второй входы сигналы логического "0", а при исходном нулевом состоянии для переключения мажоритарного элемента в состояние логической "1" необходимо подать на первый и второй входы сигналы высокого уровня.

Вследствие этого когда по переднему фронту второго импульса на шине 8 счетчик 1 обнуляется и на выходе заема появляется сигнал логического нуля, то он совпадает во времени с нулевым сигналом на выходе элемента 2 "Исключающее ИЛИ". При этом на выходе мажоритарного элемента 3 возникает перепад сигнала "1"--->"0", который проходит через второй элемент совпадения 5, и на его выходе формируется перепад сигнала "0"--->"1". Фронтом этого сигнала переключается в противоположное состояние триггер 7 и одновременно выполняется предварительная установка счетчика 1, в который опять записывается код "0". Сигнал на выходе заема после записи кода с шины 9 изменяется из состояния "0" в "1", однако мажоритарный элемент остается в нулевом состоянии до тех пор, пока не окончится импульс на входной шине 8, и на выходе элемента 2 "Исключающее ИЛИ" не появится уровень логической "1".

Вследствие этого импульсы на выходе заема счетчика 1 появляются (при коэффициенте деления KД = 4) после каждых двух импульсов входной частоты fВХ. Триггер 7 работает в счетном режиме и делит частоту импульсов на два, поэтому на выходе формируются импульсы частоты fВЫХ = fВХ/KД со скважностью Q = 2.

Если на шине 9 установлен двоичный код нечетного коэффициента деления, то в младшем разряде этого кода будет уровень логической "1", которым разрешается работа первого элемента совпадения 4. Для получения нечетного коэффициента деления, например KД = 3, на шину 9 подается двоичный код "11", поэтому при предварительной установке счетчика 1 в него записывается код "0" и сигнал на выходе заема счетчика переходит из состояния "1" в "0" после первого импульса на входной шине 8, т.е. через интервал времени, равный одному периоду входной частоты fВХ. Первый триггер 6, срабатывающий с задержкой на половину периода входного сигнала после триггера 7, находится в состоянии логической "1", и на инверсном выходе элемента совпадения 4 формируется сигнал нулевого уровня. Этим сигналом элемент 2 "Исключающее ИЛИ" переводится в режим логического повторителя, и на его выходе остается высокий логический уровень до окончания входного импульса на входе 8. Поэтому мажоритарный элемент 3 срабатывает с задержкой на половину периода входного сигнала после появления логического "0" на выходе заема вычитающего счетчика, причем нулевой уровень сигнала на его выходе остается до появления следующего импульса на шине 8. При сигнале логического "0" на выходе мажоритарного элемента 3 элемент совпадения 5 формирует сигнал логической "1" переводящий счетчик в состояние предварительной установки, а сигнал нулевого уровня на выходе элемента 5 появляется после прихода следующего импульса на счетный вход вычитающего счетчика. Поэтому счетчик 1 не вычитает этот импульс из установленного на входах D0...DN кода и срабатывает только после появления переднего фронта второго импульса. Таким образом реализуется задержка счетчика на один период входной частоты, т.е. при входном коде, соответствующем коэффициенту деления KД = 3, триггер 7 переключается через каждые полтора периода входного сигнала, и на его выходе формируются импульсы частоты fВЫХ = fВХ/KД = fВХ/3 со скважностью Q = 2.

В данном устройстве при нулевом уровне сигнала в младшем разряде шины 9 кода коэффициента деления или при нулевом состоянии триггера 6 на выходе заема счетчика 1 формируются импульсы с частотой fВЫХ = 2fВХ/KД, а при переключении триггера 6 в единичное состояние с помощью элементов 2 и 3 обеспечивается задержка срабатывания выходного триггера 7 на половину периода входного сигнала. Этим обеспечивается формирование частоты выходных импульсов со скважностью, равной двум? как при четных, так и при нечетных значениях кода коэффициента деления на шине 9.

Достоинством устройства является надежность работы при высокой частоте входного сигнала, которая может достигать максимальной частоты переключения применяемых элементов, так как длительность тактовых импульсов на входе запуска триггера 7 всегда соответствует половине периода сигнала входной частоты.

Устройство может быть сравнительно просто реализовано на современных микросхемах. Вычитающий счетчик можно собрать на микросхемах типа К561ИЕ11 или К561ИЕ14, элемент "Исключающее ИЛИ" - на микросхеме К561ЛП2, мажоритарный элемент - на микросхеме К561ЛП13, элементы совпадения 4, 5 - на микросхеме К561ЛА7, а триггеры - на микросхеме К561ТМ2.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЧАСТОТЫ | 1998 |

|

RU2138829C1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| ГЕНЕРАТОР СИНУСОИДАЛЬНОГО СИГНАЛА К ЭЛЕКТРОМАГНИТНОМУ МНОГОЧАСТОТНОМУ СТРУКТУРОСКОПУ | 1999 |

|

RU2178945C2 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ ДЕВИАЦИИ ЧАСТОТЫ | 1997 |

|

RU2126587C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЕВИАЦИИ ЧАСТОТЫ | 1998 |

|

RU2138828C1 |

| ИНФОРМАЦИОННО-ПОИСКОВАЯ СИСТЕМА | 2001 |

|

RU2199778C1 |

| ГЕНЕРАТОР СИНУСОИДАЛЬНОГО СИГНАЛА | 1999 |

|

RU2156027C1 |

| УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2146064C1 |

| МОДУЛЬ СИСТЕМЫ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2145434C1 |

| ПАРАЛЛЕЛЬНАЯ СИСТЕМА ИНФОРМАЦИОННОГО ПОИСКА | 2001 |

|

RU2195015C1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики, вычислительной техники и связи, в частности при построении цифровых синтезаторов частоты импульсных сигналов. Технический результат - формирование выходных импульсов заданной частоты со скважностью, равной двум, независимо от коэффициента деления частоты. Устройство содержит вычитающий счетчик, элемент Исключающее ИЛИ, мажоритарный элемент, первый и второй элементы совпадения, первый и второй триггеры. В устройстве за счет элемента Исключающее ИЛИ и мажоритарного элемента с положительной обратной связью обеспечивается независимость выходных импульсов от коэффициента деления частоты. 2 ил.

Управляемый делитель частоты импульсов, содержащий входную шину, шину управления и шину кода коэффициента деления, два элемента совпадения, первый вход первого из которых соединен с первым разрядом шины кода коэффициента деления, вычитающий счетчик, информационные входы которого подключены к второму и последующим разрядам шины кода коэффициента деления, а его счетный вход - к входной шине, два триггера, выход второго из которых является выходом устройства, отличающийся тем, что в него введены мажоритарный элемент и элемент Исключающее ИЛИ, первый вход которого подключен к входной шине, второй вход - к выходу первого элемента совпадения, а выход элемента Исключающее ИЛИ соединен с входом запуска первого триггера и первым входом мажоритарного элемента, второй вход которого подключен к выходу заема вычитающего счетчика, а третий вход и выход мажоритарного элемента объединены и подключены к первому входу второго элемента совпадения, второй вход которого соединен с шиной управления и входом сброса второго триггера, а выход подключен к входу предварительной установки вычитающего счетчика и входу запуска второго триггера, выход которого соединен с D-входом первого триггера, к выходу которого подключен второй вход первого элемента совпадения.

| Управляемый делитель частоты следования импульсов | 1986 |

|

SU1338066A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1992 |

|

RU2028728C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2037958C1 |

| Управляемый делитель частоты импульсов | 1986 |

|

SU1403365A1 |

| Управляемый делитель частоты | 1985 |

|

SU1262726A1 |

| УСТРОЙСТВО ДЛЯ НЕПРЕРЫВНОЙ ЖИДКОСТНОЙ ОБРАБОТКИ ДЛИННОМЕРНОГО МАТЕРИАЛА | 1995 |

|

RU2078166C1 |

| СПОСОБ ПОЛУЧЕНИЯ ЧЕТВЕРТИЧНОЙ АММОНИЕВОЙ СОЛИ, ОБЛАДАЮЩЕЙ ПРОТИВООПУХОЛЕВЫМ ДЕЙСТВИЕМ | 2020 |

|

RU2749722C1 |

Авторы

Даты

2001-10-20—Публикация

2000-10-16—Подача