1

Изобретение относится к импульс- ной технике и предназначено для управления входными и выходными буферными регистрами блоков цифровой телевизионной памяти.

Целью изобретения является расширение функциональных возможностей распределителя импульсов путем организации двух режимов работы.

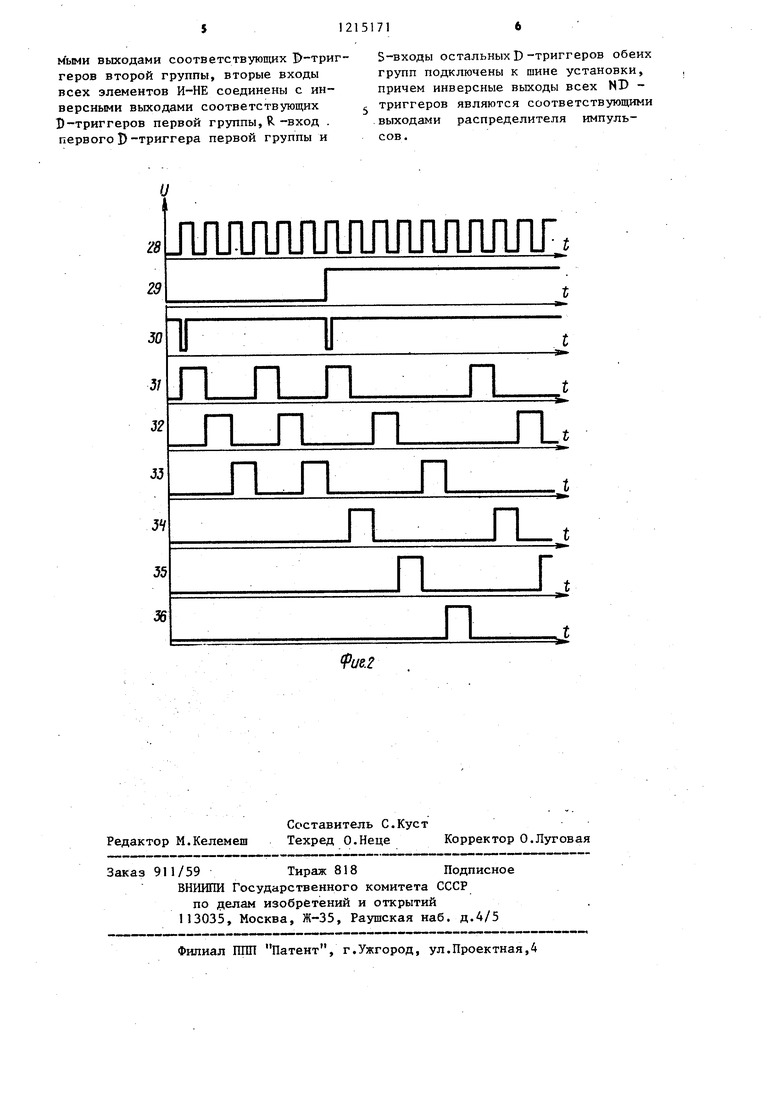

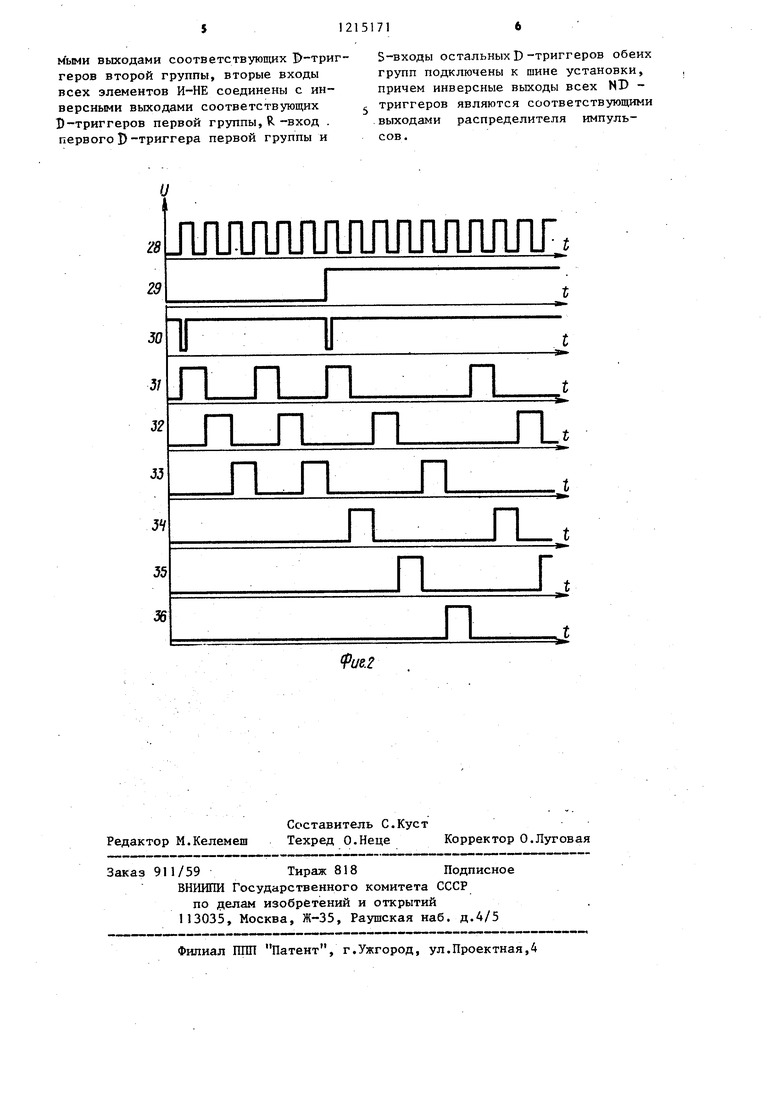

На фиг. 1 представлена функциональная схема устройства (); на фиг.2 - диаграммы, иллюстрирующие его работу.

Распределитель импульсов содержит первый 1, второй 2, третий 3 D-триггеры первой группы и первый 4, второй 5 и третий 6 D-триггеры второй группы, С-входы которых соединены с входной шиной 7, а также первый 8, второй 9 и третий 10 элементы 2И-ИЛИ и первый 11, второй 12 и третий 13 элементы И-НЕ, при этом выход каждого элемента 2И-ИЛИ 8, 9 и 10 соединен с D-входом соответствующего J)-триггера 1 , 2 и 3 первой труппы, выход каждого элемента И-НЕ i1, 12 и 13 соединен с D-входом соответствующего D-триггера 4, 5 и 6 второй группы, первые входы первых элементов И 1А, 15 и 16 элементов 2И-ИЛИ 8,9 и 10 и первые входы всех элементов И-НЕ 11, 12 и 13 соединены с шиной 17 управления, первый вход второго элемента И 18 элемента 2И-ИЛИ 8 соединен с прямым выходом последнего D-триггера 3 первой группы, вторые входы первого и второго элементов И 14, 18 первого элемента 2И-ШШ 8 соединены с прямым выходом последнего D-триггера 6 второй группы, первые входы вторых элементов И 19, 20 элементов 2И-ИЛИ 9, 10 соединены с прямыми выходами соответствующих D-триггеров 1, 2 первой группы, вторые входы первого и второго элементов И 19, 20 элементов 2И-ИЛИ 9,10 соединены с прямыми выходами соответствующих D-триггеров 4,5 второй группы, вторые входы с первого по третий элементов И-НЕ 11 - 13 соединены с инверсными выходами соответствующих D-триггеров 1,2 и 3 первой группы, R-вход первого D-триггера 1 первой группы и S-входы остальных D-триггеров 2-6 подключены к шине 21 установки, вы- ,ходш4и 22-27 распределителя явля151712

ются соответствующие инверсные выходы D-триггеров 1-6.

На фиг.2 показаны: импульсы 28 на входной шине 7, сигнал 29 на шине 17 5 управления, импульсы 30 на шине 21 установки, импульсы 31 - 36 на соответствующих выходах 22 - 27 распределителя импульсов.

Устройство работает следующим разом.

Первому режиму работы соответствует нулевое состояние сигнала 29 шины 17 управления. При поступлении по шине 21 установки короткого отри15 цательного импульса 30 первый D-триг- гер 1 устанавливается в нуль, остальные D-триггеры 2 - 6 - в единицу. На выходах всех элементов И-НЕ 11, 12 и 13 устанавливается уровень

20 логической 1 и D-триггеры 4-6 второй группы, уже находящиеся в единичном состоянии, не будут перебрасываться при поступлении тактовых импульсов 28 с входной шины 7.

25 На инверсных выходах D-триггеров 4 - 6 будет зафиксировано состояние импульсов 34 - 36 логического О. На первые входы первых элементов И 14-16 элементов 2И-ШШ 8 - 10 с

30 шины 17 управления поступает уро- вень логического О, на вторые входы элементов И 14, 18, 15, 19, 16, 20 элементов 2И-ИЛИ 8, 9 и 10 с прямых выходов соответствующих D-тригJ геров б, 4 и 5 второй группы поступает уровень логической 1. Тогда на D-входе второго D-триггера 2 первой группы будет состояние логического О, а на D-входах первого и

Q третьего D-триггеров 1, 3 будет состояние логической I. С приходом первого (после импульса 30 установки} тактового импульса с входной шины 7 D-триггер 2 установится в ну5 левое, а D-триггер 1 - в единичное состояние. При этом на D-входе третьего D-триггера 3 установится логический О, а на D-входе второго D-триггера 2 - логическая 1. С приходом

0 очередного тактового импульса 28 третий D-триггер 3 перебросится в нулевое, а второй D-триггер 2 - в единичное состояние. После этого уровень логического О появится на D-входе

JJ первого D-триггера 1, который с

приходом следующего тактов ого импульса перебросится в нулевое состояние. D-триггер 3, на D-входе которого бы-

3

ла логическая 1, перебросится в единичное состояние. Далее весь цикл работы повторится.

Второй режим работы соответствует единичному состоянию шины 17 управления. При этом на первые входы всех элементов И 14, 15 и 16 элементов 2И-ИЛИ 8, 9, 10 и первые вхо- Ды всех элементов И-НЕ 11, 12 и 13 поступает уровень логической 1. С приходом импульса 30 предварительной установки по шине 21 установки первый D-триггер 1 установится в нулевое, а остальные D-триггеры 2 - 6 - в единичное состояние. На вторые входы элементов И 14, 18 элемента 2И-И1Ш 8 поступает логическая 1 с прямого выхода шестого D-триг- гера 6, а на вторые входы элементов И 15, 19, 16, 20 элементов 2И-ИЛИ 9, 10 поступает уровень логической .1 с прямых выходов соответствующих D-триггеров 4 и 5 второй группы. Тогда на D-вхрде D-триггера 4 .будет присутствовать уровень логического О, а на D-входах остальных D-триггеров 1 - 3, 5 и 6 - уровень логической I. С приходом первого (после импульса 30 установки) тактового импульса с входной шины 7 первый D-триггер 4 второй группы перебросится в нулевое состояние, а первый D-триггер 1 первой группы - в единичное состояние. После этого уровень логического О установится на В- входе второго D-триггера 2, в то время как на D-входах остальных D-триггеров обеих rpjrnn будет состояние логической 1. С приходом следующего тактового импульса второй D-триггер 2 первой группы перебросится в нулевое состояние, а первый D-триггер 4 второй группы - в единичное состояние. После этого уровень логического О установится на D-входе D-триггера 5, на D-входах остальных D-триггеррв 1 - 4, 6 будет уровень логической 1. С приходом тактового синхроимпульса D-триггер 5 перебросится в нулевое а D-триггер 2 - в единичное состояние. Состояние логического О появися на D-входе третьего D-триггера 3, на D-входах остальных D-триггеров 1,2,4-6 будет состояние логической 1. С приходом тактового импулса D-триггер 3 установится в нулевое, а D-триггер 5-й единичное состояние. На D-входв D-триггера 6

71

установится нулевое состояние, на D-входах остальных D-триггеров 1 - 5 будет состояние логической 1. Очередным тактовым импульсом D-триггер 6 установится в нулевое, а D-триггер 3 - в единичное состояние. Состояние логического О появится на D-входе первого D-триггера 1, на D-входы остальных D-триггеров 2-6

поступает логическая 1. Тактовым импульсом D-триггер 1 установится в нулевое, а D-триггер 6 - в единичное состояние. Снова на D-входе D-триггера 4, появится логический

О. Далее весь цикл работы повторится. При необходимости получения отрицательных импульсов выходами распределителя могут являться прямые выходы D-триггеров 1-6,

Технический эффект от использования предложенного распределителя импульсов заключается в расширении функциональных возможностей за счет реализации двух режимов работы в зависимости от сигнала на шине 17 управления .

Формула изобретения

Распределитель импульсов, содержащий две группы по ND -триггеров в каждой, С-входы которых соединены с входной шиной, отличающий- с я тем, что, с целью расширения функциональных возможностей, в него введены N элементов 2И-ИЛИ и N эле- ментов ИГ-НЕ, при этом выход каждого элемента 2И-ШЮ соединен с Р -входом соответствующего D-триггера первой группы, выход каждсхго элемента И-НЕ соединен с Т) -входом соответствующего) -триггера второй группы, лервые входы первых элемеитов И всех элементов 2И-ИЛИ и первые входы всех элементов И-НЕ соединены с шиной управления, первый вход второго элемента И первого элемента 2И-ИЛИ соединен с прямым выходом последнего )-триггера первой группы, вторые входы первого и второго элементов

и первого элемента 2И-ИЛИ соединены с прямьм выходом последиегоЗ) -триггера второй группы, первые входы вторых элементов И остальных элементов 2И-ИЛИ соединены с прямыми

выходами соответствующих D-триггеров первой группы, вторые входы первого и второго элементов И остальных элементов 2И-ИПИ соединены с пря

Мыми выходами соответствующих 1)-триг- геров второй группы, вторые входы всех элементов И-НЕ соединены с инверсными выходами соответствующих D-триггеров первой группы,R -вход . первогоD-триггера первой группы и

1В 29

30

S1 32

33 34

Редактор М.Келемеш

Составитель С.Куст

Техред О.НецеКорректор О.Луговая

Заказ 911/59 Тираж 818 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб. д.4/5

Филиал ППП Патент, г.Ужгород, ул.Проектная,4

S-входы остальныхD-триггеров обеих групп подключены к шине установки, причем инверсные выходы всех ND - триггеров являются соответствующими .выходами распределителя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехканальный реверсивный распределитель уровней | 1984 |

|

SU1226648A1 |

| Устройство для выделения одиночного импульса | 1985 |

|

SU1274135A1 |

| Реверсивный распределитель уровней | 1976 |

|

SU663109A1 |

| Электронный музыкальный звонок | 1988 |

|

SU1748176A1 |

| Двухрежимный распределитель импульсов для управления трехфазным шаговым двигателем | 1981 |

|

SU1019571A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Трехканальный трехрежимный распределитель импульсов для управления шаговым двигателем | 1984 |

|

SU1275734A1 |

| Трехканальный двухрежимный распределитель импульсов для управления шаговым двигателем | 1980 |

|

SU907753A1 |

| Двенадцатитактный реверсивный распределитель импульсов | 1981 |

|

SU980287A1 |

| Кольцевой реверсивный распределитель уровней с нечетным числом каналов | 1987 |

|

SU1450104A1 |

Изобретение относится к импульсной технике и предназначено для управления входными и выходными буферными регистрами блоков цифровой телевизионной памяти. Цель изобрете22 Ч 21 ния - расширение функциональных возможностей распределителя путем орга низации двух режимов работы. Устройство содержит В-триггеры I, 2 и 3 первой группы, D -триггеры- 4,5 и 6 второй группы, входную шину 7, логические элементы (ЛЭ) 2И-ИЛИ 8,9 и 10, ЛЭ И-НЕ 12 и 13, ЛЭ И 14, 15 и 16, шину 17 управления, ЛЭ И 18, входящий в состав ЛЭ 2И-ИЛИ 8, ЛЭ И 19 и 20, входящие в состав ЛЭ 2И-ИЛИ 9 и 10, шину 21 уставки, выходы 22-27. Первому режиму соответствует нулевое состояние сигнала пш- ны 17, второму режиму - единичное состояние сигнала. Работа устройства поясняется временными диаграммами в описании изобретения. 2 ил. (О 24 25 26 27 Фиг.}

| Букреев И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| М.: Советсткое радио, 1975, с | |||

| Нож для надрезывания подошвы рантовой обуви | 1917 |

|

SU269A1 |

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

| Распределитель импульсов | 1982 |

|

SU1050114A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-02-28—Публикация

1984-07-06—Подача