Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель несимметричности сигналов | 1990 |

|

SU1725179A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| Устройство для считывания и отображения графической информации | 1986 |

|

SU1506459A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Цифровой генератор | 1986 |

|

SU1347164A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1984 |

|

SU1292029A1 |

Изобретение относится к импульснрй технике. Целью изобретения является расширение функциональных возможностей за счет повышения информативности измерений. Поставленная цель в цифровом измерителе центра тяжести достигается тем, что в него введены аналоговый ключ 1, аналого- цифровой преобразователь 2, генератор 4 управляющих сигналов, блок 5 формирования отсчетов, блок 6 выбора адресов, блок 7 вычисления функции, блок 8 хранения информации, блок 9 синхронизации. Кроме того, измеритель содержит пороговый элемент 3. 7 з.п.ф-лы, 16 ил.

Изобретение относится к измерительной технике, преимущественно для анализа формы сигналов и отображения ее характеристик на графических индикаторах.

Известен формирователь 1 центра тяжести группы видеосигналов произвольной формы, содержащий интегратор, линию задержки, формирователь строба, компаратор и триггер.

Недостатками известного устройства являются ограниченные функциональные возможности и ограниченный диапазон измерения длительностей входных сигналов.

Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому решению является устройство 2 для определения центра тяжести повторяющихся импульсов, содержащее преобразователь напряжения в частоту, пороговый элемент, два элемента И, три счетчика, два

регистра памяти, два блока .сравнения, элемент ИЛИ, формирователь импульсов, элемент задержки, генератор импульсов, накапливающий сумматор, блок согласования, включающий элемент И, триггер и два одновибратора, и выходное устройство.

Однако данное устройство выдает информацию только о положении центра тяжести видеоимпульса, имеет ограниченный диапазон измерения длительностей входного сигнала.

Цель изобретения - расширение функциональных возможностей устройства.

Указанная цель достигается тем, что в цифровой измеритель центра тяжести видеосигналов, содержащий пороговый элемент, включающий компаратор, элемент НЕ, первый и второй формирователи коротких импульсов, причем первый вход компаратора соединен через первый вход

V4

ГО

ы ел ся ю

порогового элемента с шиной Вход измерителя, второй вход компаратора через второй вход порогового элемента соединен с шиной Uon, выход компаратора соединен с входом элемента НЕ, входом второго формирователя коротких импульсов и четвертым выходом порогового элемента, выход элемента НЕ соединен с входом первого формирователя коротких импульсов и первым выходом порогового элемента, выход первого формирователя коротких импульсов соединен с вторым выходом порогового элемента, выход второго формирователя коротких импульсов соединен с третьим выходом порогового элемента, введены аналоговый ключ, аналого-цифровой преобразователь, генератор управляющих сигналов, блок формиросания отсчетов, блок выбора адресов, блок вычисления функции, блок хранения информации и блок синхронизации.

При этом первый вход аналогового ключа соединен с шиной Вход, первый выход порогового элемента соединен с вторым входом аналогового ключа, с первым входом генератора управляющих сигналов и четвертым входом блока формирования отсчетов, Второй выход порогового элемента соединен с вторым входом генератора управляющих сигналов, с третьим входом блока вычисления функции, с одиннадцатым входом блока формирования отсчетов, с третьим входом блока хранения информации, с вторыми входами блока выбора адресов и блока синхронизации. Выход порогового элемента соединен с двенадцатым входом блока формирования отсчетов и первым входом блока выбора адресов, выход аналогового ключа соединен с входом UBX аналого-цифрового преобразователя, выход аналого-цифрового преобразователя соединен с первым входом блока формирования отсчетов. Первый выход генератора управляющих сигналов сое- дине н с входом ти аналого-цифрового преобразователя, второй выход генератора управляющих сигналов соединен с тринад- цатым входом блока формирования отсчетов, третий выход генератора управляющих сигналов соединен с третьим входом блока формирования отсчетов, четвертый выход генератора управляющих сигналов соединен с вторым входом блока формирования отсчетов. Первый выход блока формирования отсчетов соединен с первым входом блока вычисления функции, второй выход блока формирования отсчетов соединен с третьими входами блока выбора адресов и блока синхронизации, третий выход блока

формирования отсчетов соединен с шиной Выход 1. Первый выход блока выбора адресов соединен с пятыми входами блоков формирования отсчетов и хранения информации, второй выход блока выбора адресов соединен с вторым входом блока вычисления функции, третий, четвертый, пятый и седьмой выходы блока выбора адресов соединены соответственно с четвертым, пятым,

0 шестым и седьмым входами блока вычисления функции, шестой и девятый выходы блока выбора адресов соединены соответственно с вторым и первым входами блока хранения информации, восьмой выход бло5 ка выбора адресов соединен с первым входом блока синхронизации, десятый, одиннадцатый, двенадцатый и тринадцатый выходы блока выбора адресов соединены соответственно с шестым, девятым, седь0 мым и десятым входами блока формирования отсчётов. Выход блока вычисления функции соединен с четвертым входом блока хранения информации, первый выход блока хранения информации соединен с ши5 ной Выход 2, второй выход блока хранения информации соединен с шиной Выход 3, третий выход блока хранения информации соединен с шиной Выход 4, Первый выход блока синхронизации соединен с

0 седьмым входом блока хранения информации, второй выход блока синхронизации соединен с четырнадцатым входом блока формирования отсчетов и шиной Синхронизация, третий выход блока синхрониза5 ции соединен с шестым входом блока

хранения информации, четвертый выход

блока синхронизации соединен с восьмым

входом блока формирования отсчетов.

Генератор управляющих сигналов со0 держит генератор тактовых импульсов, К D- триггеров, RS-триггер, регистр памяти, два дешифратора, линию задержки, элемент ИЛИ, умножитель/сумматор и элемент НЕ, причем первый вход генератора управляю5 щих сигналов соединен с входом генератора тактовых импульсов, второй вход генератора управляющих сигналов соединен с вторым входом элемента ИЛИ, выход генератора тактовых импульсов соединен с

0 входом С первого D-триггера и К-входэми первого и второго дешифраторов, Q-выходы каждого из К D-триггеров соединены с D- входами регистра памяти и 1,2,,..,(К-1)-м входами первого и второго дешифраторов,

5 Q-выход каждого 1,2(К-1)-го D-триггера

соединен с D-входом этого же триггера и входом С следующего D-триггера, 5-выход К-го D-триггера соединен с его D-входом, выход первого дешифратора соединен с R- входом RS-триггера и четвертым выходом

генератора управляющих сигналов, выход второго дешифратора соединен с входами элемента НЕ и линии задержки, первый выход линии задержки соединен с первым входом элемента ИЛИ, второй выход линии задержки соединен с вторым выходом генератора управляющих сигналов, выход элемента ИЛИ соединен с R-входамй каждого из К D-триггеров, регистра памяти и S-вхо- дом RS-триггера, 6-выход RS-триггера-Сое- динен с первым выходом генератора управляющих сигналов, выход элемента НЕ соединен с входом С регистра памяти, Q-вы- ходы регистра памяти соединены с Х-входа- ми умножителя/сумматора, на Y-входах умножителя/сумматора монтажным путем установлен двоичный код периода тактовых импульсов, на входах К и М монтажным путем задан двоичный код равный 0...0, выход умножителя/сумматора соединен с третьим выходом генератора управляющих сигналов.

Блок формирования отсчетов содержит первый и второй регистры памяти, умножитель/сумматор, формирователь коротких импульсов, оперативное запоминающее устройство, элемент ИЛИ, группу элементов 3-ЗИ-ЗИЛИ и двоичный счетчик, причем первый вход блока формирования отсчетов соединен с D-входами первого регистра памяти, второй вход блока формирования отсчетов соединен с входом формирователя коротких импульсов, третий вход блока формирования отсчетов соединен с Y-входом умножителя/сумматора, пятый вход блока формирования отсчетов соединен с четвертым и седьмым входами элемента 3-ЗИ- ЗИЛИ, четвертый, шестой, седьмой, девятый и десятый входы блока формирования отсчетов соединены соответственно с первым, пятым, шестым, восьмым и девятым входами элемента 3-ЗИ-ЗИЛИ, одиннадцатый вход блока формирования отсчетов соединен с R-входами первого и второго регистров памяти и вторым R-вхо- дом двоичного счетчика, двенадцатый вход блока формирования отсчетов соединён с входом С второго регистра памяти, тринадцатый вх/эд блока формирования отсчетов соединен с первым и вторым W-входами оперативного запоминающего устройства, четырнадцатый вход блока формирования отсчетов соединен с первым R-входом двоичного счетчика, Q-выходы первого регистра памяти соединены с Х-входом умножителя/сумматора и вторым D-входом оперативного запоминающего устройства, на К и М входах умножителя/сумматора монтажным путем установлен двоичный код D...O, выход умножителя/сумматора соединен с первым D-входом оперативного запоминающего устройства, выход элемента 3- ЗИ-ЗИЛИ соединен с первыми А-входами оперативного запоминающего устройства; 5 выход формирователя коротких импульсов соединен с входом С первого регистра памяти и первым входом элемента ИЛИ, выход элемента ИЛИ соединен с входом С двоичного счетчика, Q-выходы двоичного счетчи0 ка соединены с D-входами второго регистра памяти, с вторыми А-входами оперативного запоминающего устройства и вторым входом ,элемента 3-ЗИ-ЗИЛИ, первый выход оперативного запоминающего устройства

5 соединен с первым выходом блока-формирования отсчетов, второй выход оперативного запоминающего устройства соединен с третьим выходом блока формирования отсчетов, Q-выходы второго регистра памяти

0 соединены с вторым выходом блока формирования отсчетов.

Блок выбора адресов содержит первый...пятый элементы ИЛИ, первый...четвертый RS-триггеры, генератор тактовых

5 импульсов, распределитель импульсов, элемент 3-2И-НЕ, элемент 2-2И, первый и второй двоичные реверсивные счетчики, двоичный счетчик, первую...третью схемы сравнения, элемент 2-ЗИ, элемент 2-2И0 НЕ, первый...третий формирователи коротких импульсов, элемент 2-2И-2ИЛИ и ..элемент 4И-НЕ, причем первый вход блока выбора адресов соединен с S-входом перво- го RS-триггера и первым входом второго

5 элемента ИЛИ, второй вход блока выбора адресов соединен с первыми входами первого, третьего, четвертого и пятого элементов ИЛИ, R-входамй распределителя импульсов, первого и второго двоичных ре0 версивных счетчиков и двоичного счетчика, третий вход блока адресов соединен с В- входами второй и третьей схем сравнения, выход первого элемента ИЛИ соединен с R-входом первого RS-триггера, выход второ5 го элемента ИЛИ соединен с S-входом второго RS-триггера. выход третьего элемента ИЛИ соединен с R-входом второго RS-триггера, выход четвертого элемента ИЛИ соединен с R-входом третьего RS-триггера,

0 выход пятого элемента ИЛИ соединен с R- входом четвертого RS-триггера, выход элемента 4И-НЕ соединен с S-входом четвертого RS-триггера, Q-выход первого RS-триггера соединен с первым выходом

5 блока выбора адресов и входом генератора тактовых импульсов, Q-выход второго RS- триггера соединен с первым, третьим и пятым входами элемента 3-2И-НЕ, Q-выход второго RS-триггера соединен с первым входом элемента 4И-НЕ, Q-выход третьего

RS-триггера соединен с первым входом элемента 2-2И, вторым входом элемента 2-2И-2ИЛИ, третьим входом первого формирователя коротких.импульсов и десятым выходом блока выбора адресов, 5-выход третьего RS-триггера соединен с вторым входом элемента 4И-НЕ, первым и пятым входами элемента 2-ЗИ, Q-пыход четвертого RS-триггера соединен с третьим входом элемента 2-2И, четвертым входом элемента 2-2И-2ИЛ И, одиннадцатым выходом блока выбора адресов и третьим входом второго формирователя коротких импульсов, Q-вы- ход четвертого RS-триггера соединен с четвертым входом элемента 4И-НЕ и третьим и шестым входами элемента 2-ЗИ, выход генератора тактовых импульсов соединен с входом С распределителя импульсов, второй, третий и четвертый выходы распределителя импульсов соединены соответственно с вторым, четвертым и шестым входами элемента 3-2И-НЕ, пятый выход распределителя импульсов соединен с вторым и четвертым входами элемента 2-2И, шестой выход распределителя импульсов соединен с первым входом первого формирователя коротких импульсов, седьмой выход распределителя импульсов соединен с первым и третьим входами элемента 2-2И- 2ИЛИ, восьмой выход распределителя импульсов соединен с вторым выходом блока выбора адресов, девятый выход распределителя импульсов соединен с четвертым входом второго элемента 2-ЗИ, десятый выход распределителя импульсов соединен с первым входом элемента 2-2И-НЕ, одиннадцатый выход распределителя импульсов соединен с вторым входом элемента 2-ЗИ и третьим входом элемента 2-2И-НЕ, двенадцатый выход распределителя импульсов соединен с третьим входом элемента 4И-НЕ, первый выход элемента 3-2И-НЕ соединен с входом С двоичного счетчика, второй выход элемента 3-2И-НЕ соединен с входами С первого и второго реверсивных двоичных счетчиков, третий выход элемента 3-2И-НЕ соединен с вторым входом третьего элемента ИЛИ и S-входом третьего RS-триггера, первый выход элемента 2-2И соединен с входом -1 первого двоичного реверсивного счетчика, второй выход элемента 2-2И соединен с входом -И второго двоичного реверсивного счетчика, Q-выходы первого реверсивного двоичного счетчика соединены с А-входами первой схемы сравнения и двенадцатым выходом блока выбора адресов, Q-выходы второго двоичного реверсивного счетчика соединены с А-входами второй схемы сравнения и тринадцатым выходом блока выбора адресов, Q-выходы двоичного счетчика соединены с D-входа ми первого и второго двоичных реверсивных счетчиков, А-входами третьей схемы сравнения и девятым выходом блока выбора адресов, на В-вход первой схемы сравнения монтажным путем подан двоичный код O...Q, выход А - В первой схемы сравнения соединен с вторым входом первого формирооате- ля коротких импульсов, .выход первого

0 формирователя коротких импульсов соединен с вторым входом четвертого элемента ИЛИ, выход А В второй схемы сравнения соединен с вторым входом оторого формирователя коротких импульсоо и вторым и

5 четвертым входами элемента 2-2И-НЕ, выход второго формирователя коротких импульсов соединен с вторыми входами второго и пятого элементов ИЛИ, а первый вход формирователя коротких импульсов

0 соединен с одиннадцатым выходом распре. делителя импульсов, выход А В третьей схемы сравнения соединен с вторым входом третьего формирователя коротких импульсов, первый вход формирователя коротких

5 импульсов соединен с третьим выходом распределителя импульсов, выход третьего формирователя коротких импульсов соединен с вторым входом первого элемента ИЛИ и восьмым выходом блока выбора адресов,

0 выход элемента 2-2И-2ИЛИ соединен $ третьим выходом блока выбора адресов,, первый и второй выходы элемента 2-ЗИ CQr единены соответственно с четвертым и пяг тым выходами блока выбора адресов,

5 первый и второй выходы элемента 2-2И-Н Е соединены соответственно с шестым и седьмым выходами блока выбора адресов.

Блок вычисления функции содержит умножитель/сумматор, накапливающий сум0 матор, арифметическо-логическое устройство, группу элементов 2И, группу элементов 2И-НЕ, группу элементов ИЛИ, элемент ИЛИ, двоичный счетчик, регистр пймяти и элемент НЕ, причем первый вход блока со5 единен с входами X умножителя/сумматора, второй вход блока соединен с входом С накапливающего сумматора, третий вход блока соединен с входом элемента НЕ, четвертый вход блока соединен с входом С дво0 ичного счетчика, пятый вход блока соединен с вторым входом элемента ИЛИ, шестой вход блока соединен с входом С регистра памяти, седьмой вход блока соединен с вторым R-входом регистра памяти, входы К и М

5 умножителя/сумматора монтажным путем соединены с потенциалом логического нуля, входы So,- Si, 82, 5з, М арифметическо-логи- ческого устройства соединены монтажным путем на операцию вычитания, выход умножителя/сумматора соединен с входом А накапливающего сумматора, выход накапливающего сумматора соединен с входами А арифметическо-логического устройства и D- триггера памяти, выход элемента НЕ соединен с первым входом элемента ИЛИ, первым входом R накапливающего сумматора и первым R-входом регистра памяти, выход элемента ИЛИ соединен с R-входом двоичного счетчика и вторым R-входом накапливающего сумматора, выход регистра памяти соединен с входами В арифметическо-логического устройства, выход С4 арифметическо-логического устройства соединен с входом Сп арифметическо-логического устройства и первыми входами групп элементов 2И и 2И-НЕ, выход F арифметическо-логического устройства соединен с вторыми входами групп элементов 2И и 2И- НЕ, выходы группы элементов 2И соединены с первыми входами группы элементов ИЛИ, выходы группы элементов 2И-НЕ соединены с вторыми входами группы элементов ИЛИ, выходы группы элементов ИЛИ соединены с шиной выхода блока вычисления функции.

Блок хранения информации, содержит первый и второй регистры памяти, схему сравнения, группу элементов 2-2И-2ИЛИ, оперативное запоминающее устройство и элемент И, причем первый вход блока соединен с D-входами первого регистра памяти и первыми входами группы элементов 2- 2И-2ИЛИ, второй вход блока соединен с первым входом элемента И и W-входом оперативного запоминающего устройства, третий вход блока соединен с Ro-входом первого регистра памяти и Rg-входом второго регистра памяти, четвертый вход блока соединен с D-входами второго регистра памяти и оперативного запоминающего устройства и входом А схемы сравнения, пятый вход блока соединен с вторыми входами группы элементов 2-2И-2ИЛИ, шестой вход блока соединен с третьими входами группы элементов 2-2И-2ИЛИ, седьмой вход блока соединен с четвертыми входами группы элементов 2-2И-2ИЛИ, выход элемента И соединен с входами С первого и второго регистров памяти, выход первого регистра памяти соединен с первым выходом блока хранения информации, выход второго регистра памяти соединен с В-вхо- дом схемы сравнения и вторым выходом блока, выход А В схемы сравнения соединен с вторым входом элемента И, выход элемента 2-2И-2ИЛИ соединен с входом А оперативного запоминающего устройства, выход оперативного запоминающего устройства соединен с третьим выходом блока хранения информации.

Блок синхронизации содержит RS-триг- гер, генератор тактовых импульсов, элемент ИЛИ-НЕ, двоичный счетчик, схему сравнения, формирователь коротких импульсов и 5 элемент ИЛИ, причем первый вход блока синхронизации соединен с S-входом RS- триггера и первым входом элемента ИЛИ, второй вход блока синхронизации соединен с R-входом .RS-триггера и первым входом

0 элемента ИЛИ-НЕ, третий вход блока синхронизации соединен с входом В схемы сравнения, Q-выход RS-триггёра соединен с входом генератора тактовых импульсов и третьим выходом блока синхронизации, вы5 ход генератора тактовых импульсов соединен с входом С двоичного счетчика и четвертым выходом блока синхронизации, выход двоичного счетчика соединен с. входом А схемы сравнения и первым выходом

0 блока синхронизации, выход А. В схемы сравнения соединен с входом формирователя коротких импульсов, выход формирователя коротких импульсов соединен с вторыми входами элементов ИЛИ и ИЛИ5 НЕ, выход элемента ИЛИ-НЕ соединен с R-входом двоичного счетчика, выход элемента ИЛИ соединен с вторым выходом блока синхронизации.

Заявляемое устройство по сравнению с

0 прототипом (а.с. 1013905) отличается наличием новых элементов: аналогового ключа, аналого-цифрового преобразователя, генератора управляющих сигналов, блока формирования отсчетов, блока выбора адресов,

5 блока вычисления функции, блока хранения информации, блока синхронизации и связей между ними.

Сравнение заявляемого решения с другими техническими решениями показывает,

0 что элементы, отличающие заявляемое решение от прототипа, широко известны. Однако при их введении в указанной связи с остальными элементами схемы в заявляемый цифровой измеритель центра тяжести

5 видеосигналов указанные элементы проявляют новые свойства.

В новой совокупности признаков предлагаемое устройство обеспечивает выполнение новых функций измерительного

0 процесса. Введение новых элементов обеспечивает преобразование сигналов в дискретные цифровые отсчеты, вычисление функции различия моментов, определение минимального значения функции различия,

5 выдачу их на индикаторы.

Таким образом, предложенное устройство обладает новыми по сравнению с прототипом признаками. Следовательно, заявляемое техническое решение обладает новизной. Наличие указанных новых дополнительных свойств, обеспечивающих достижение положительного эффекта, позволяет признать предложенное техническое решение соответствующим критерию существенные отличия.

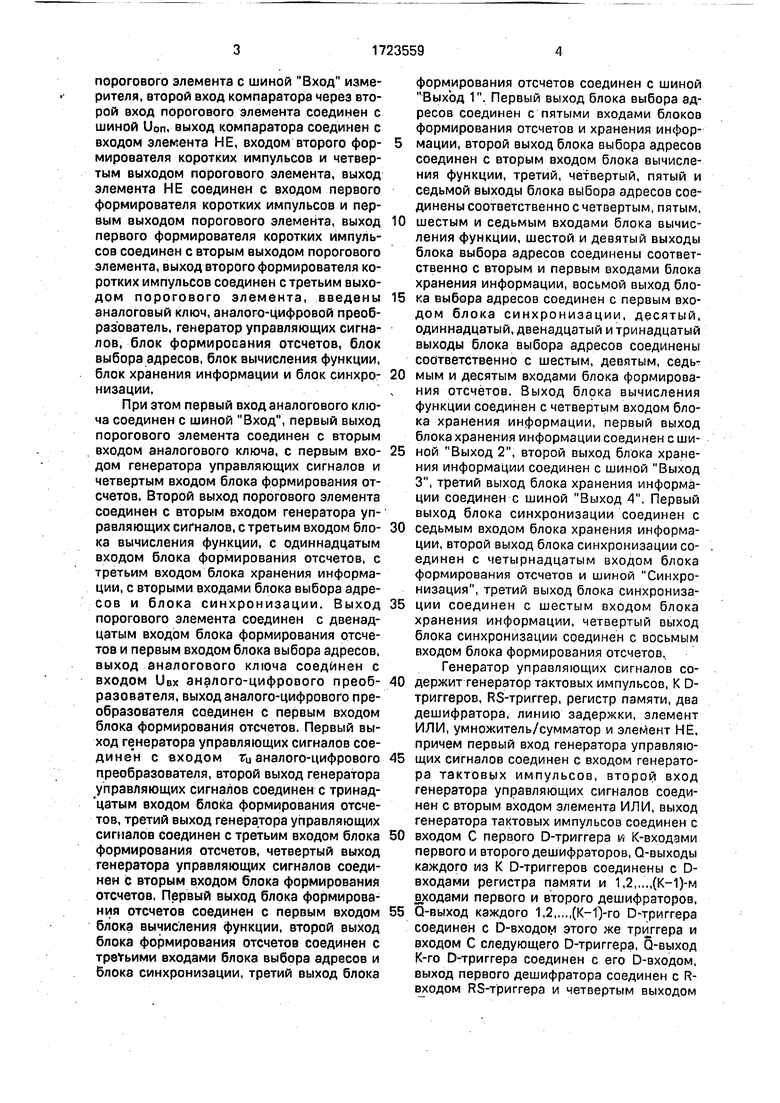

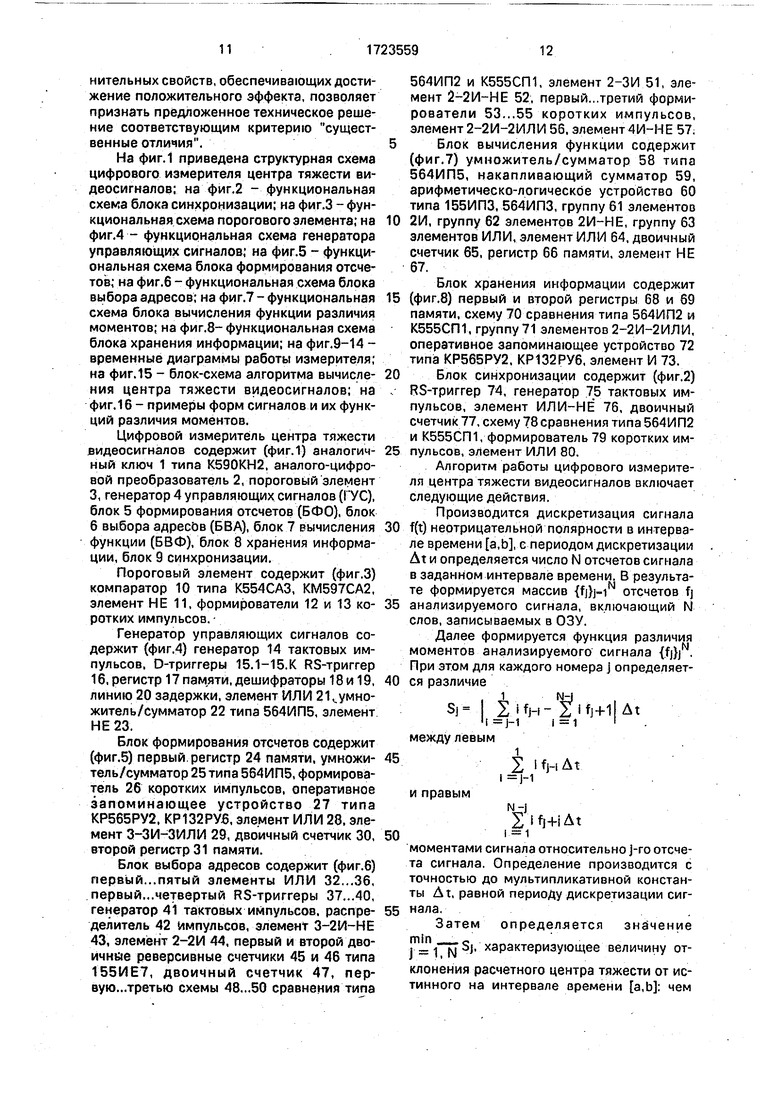

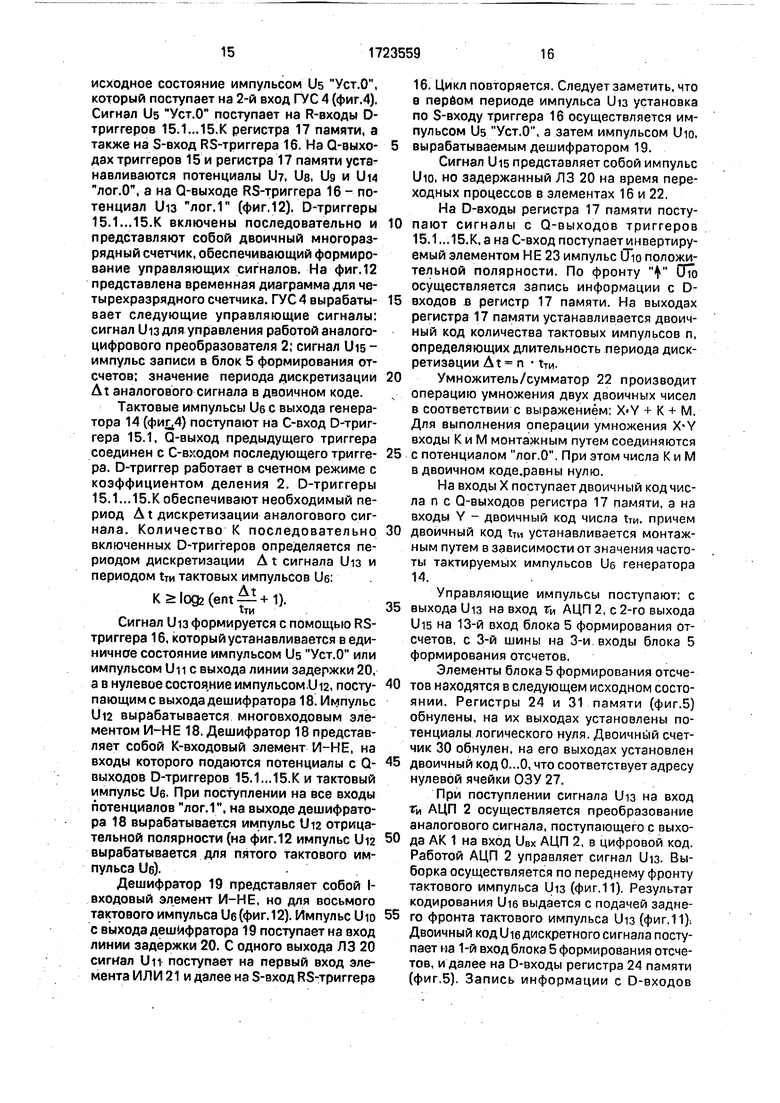

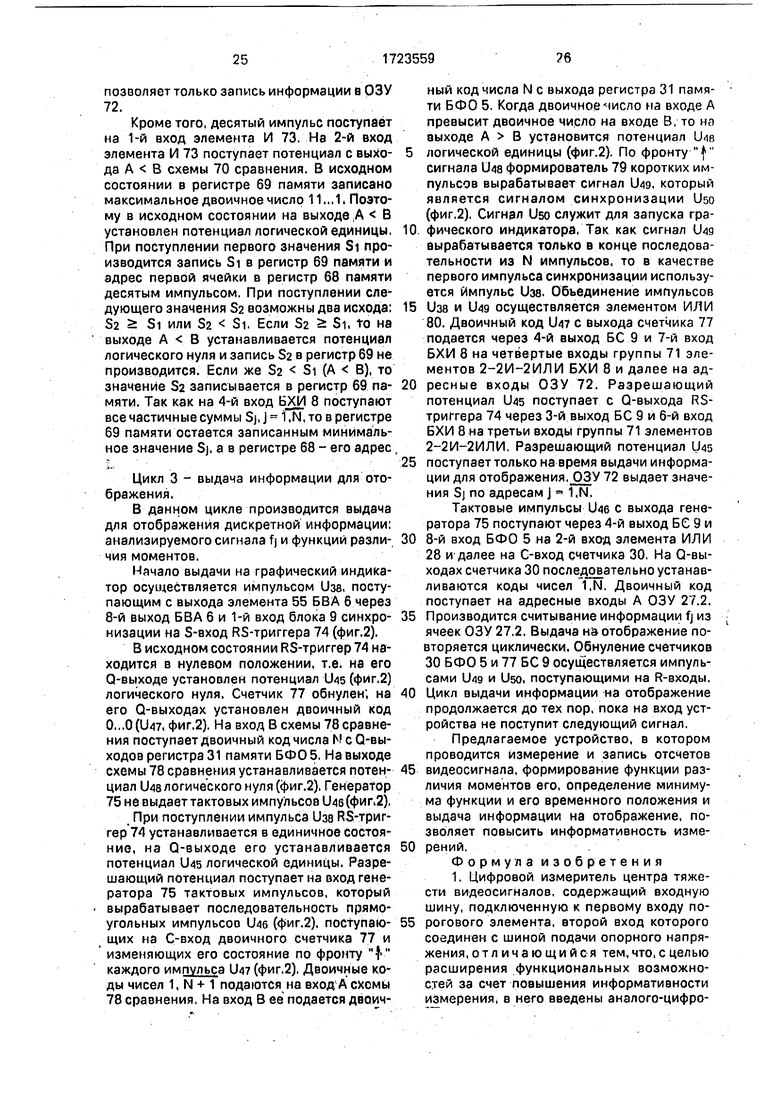

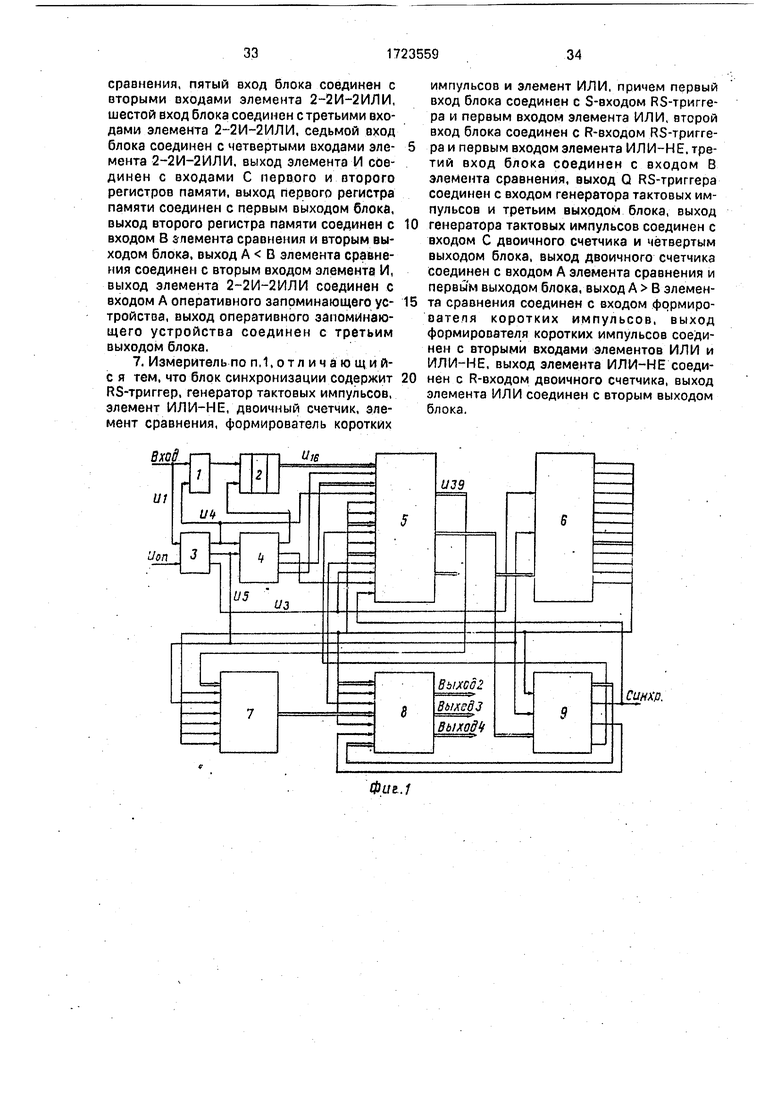

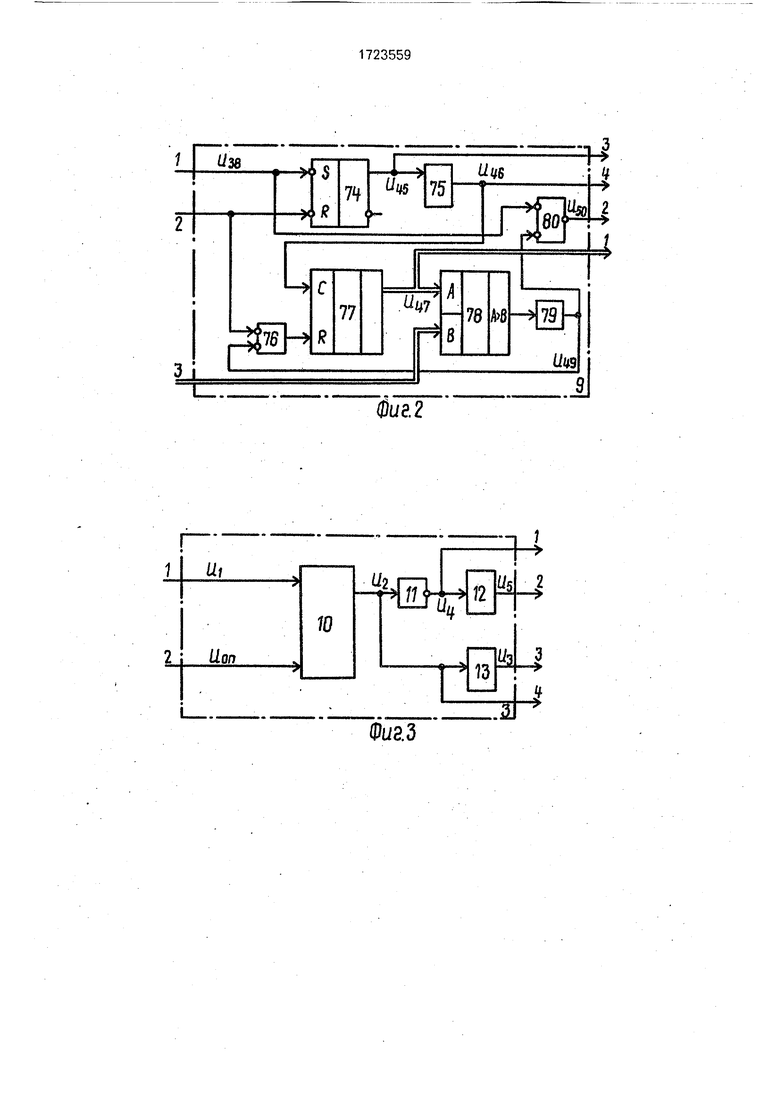

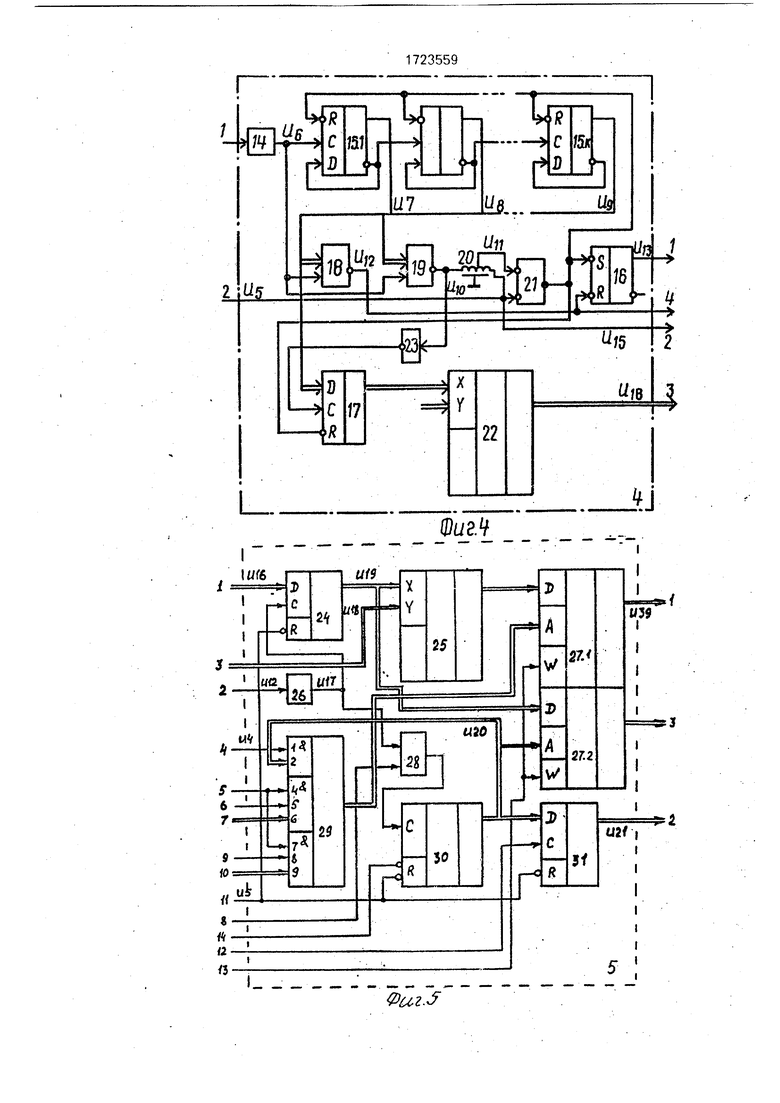

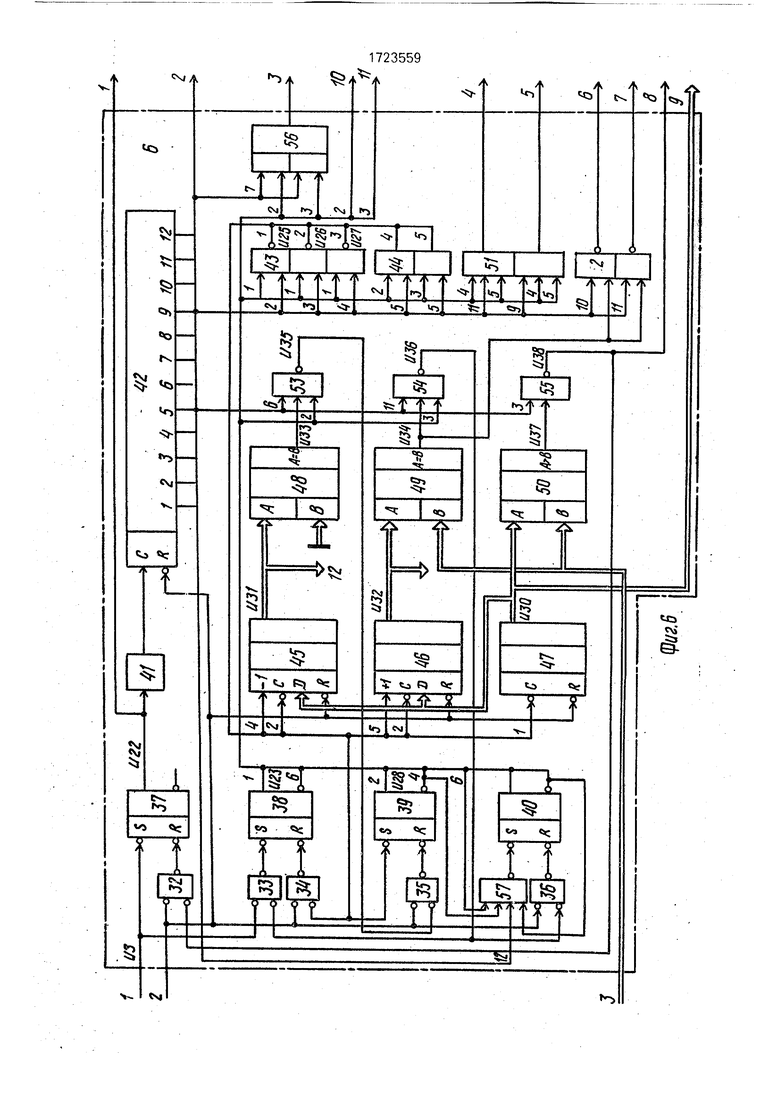

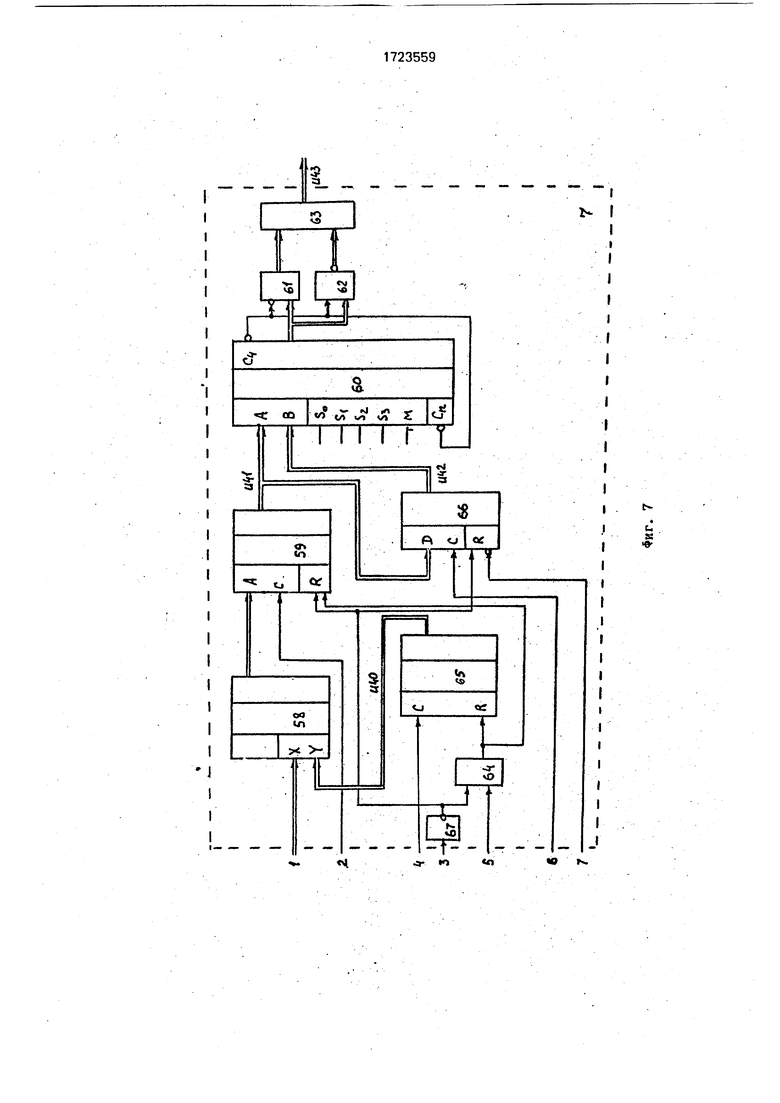

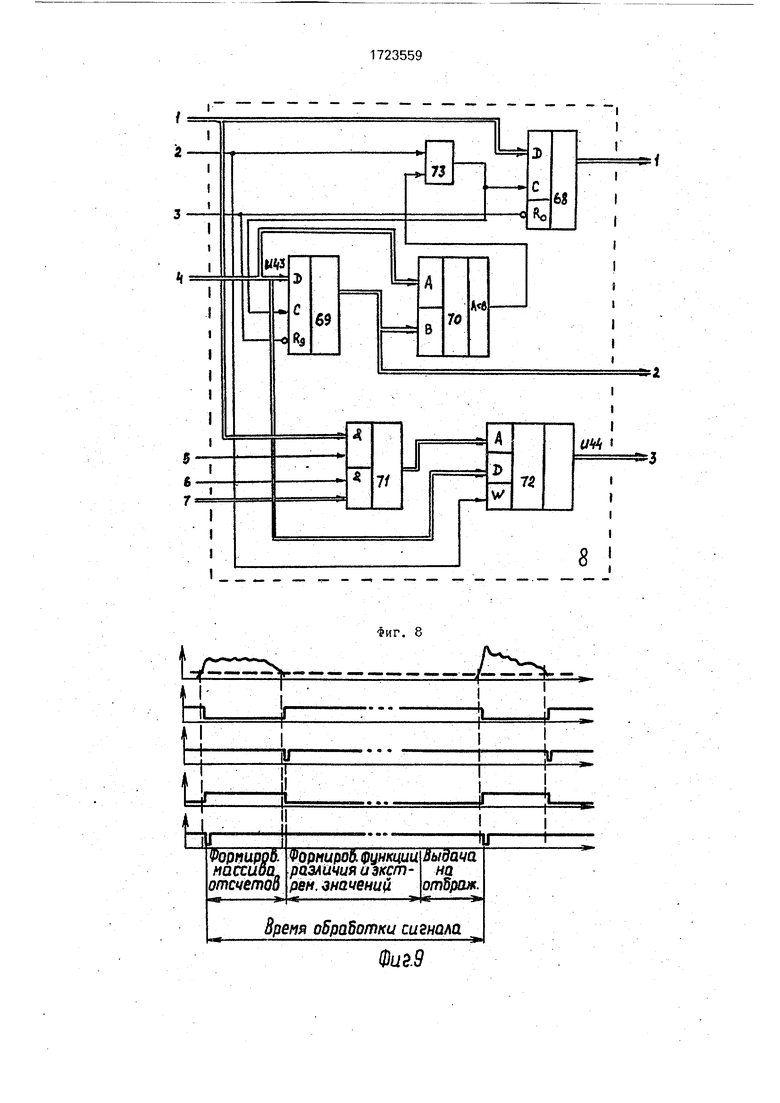

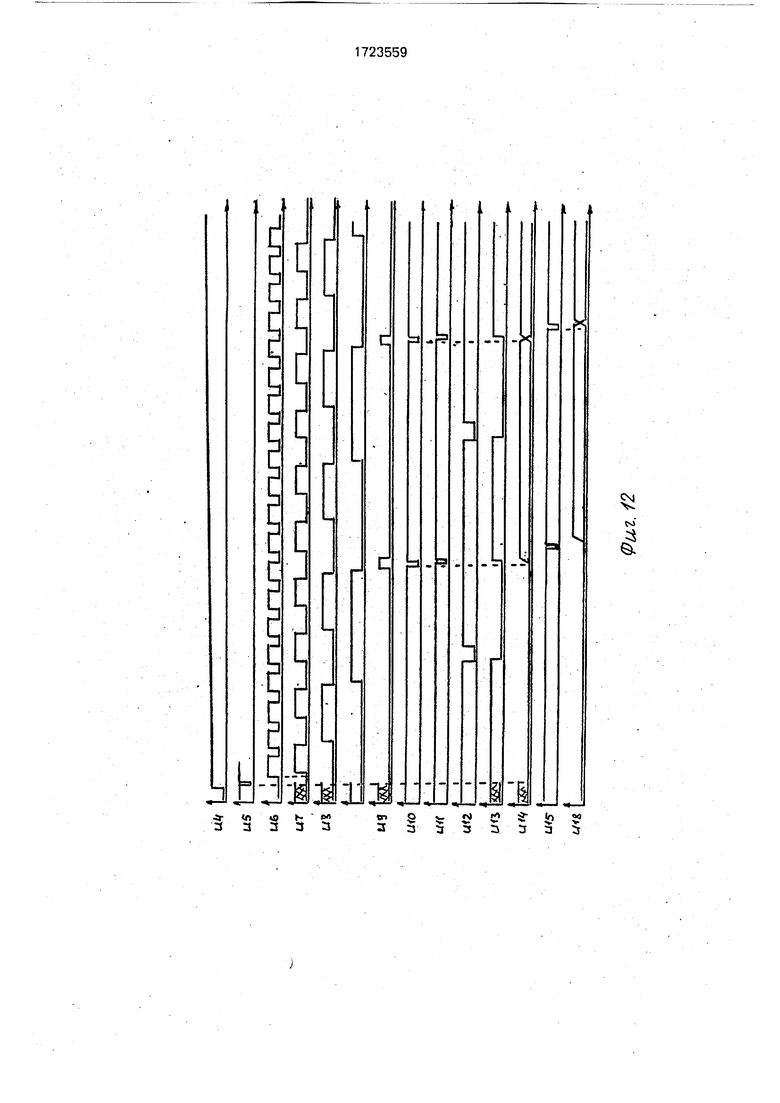

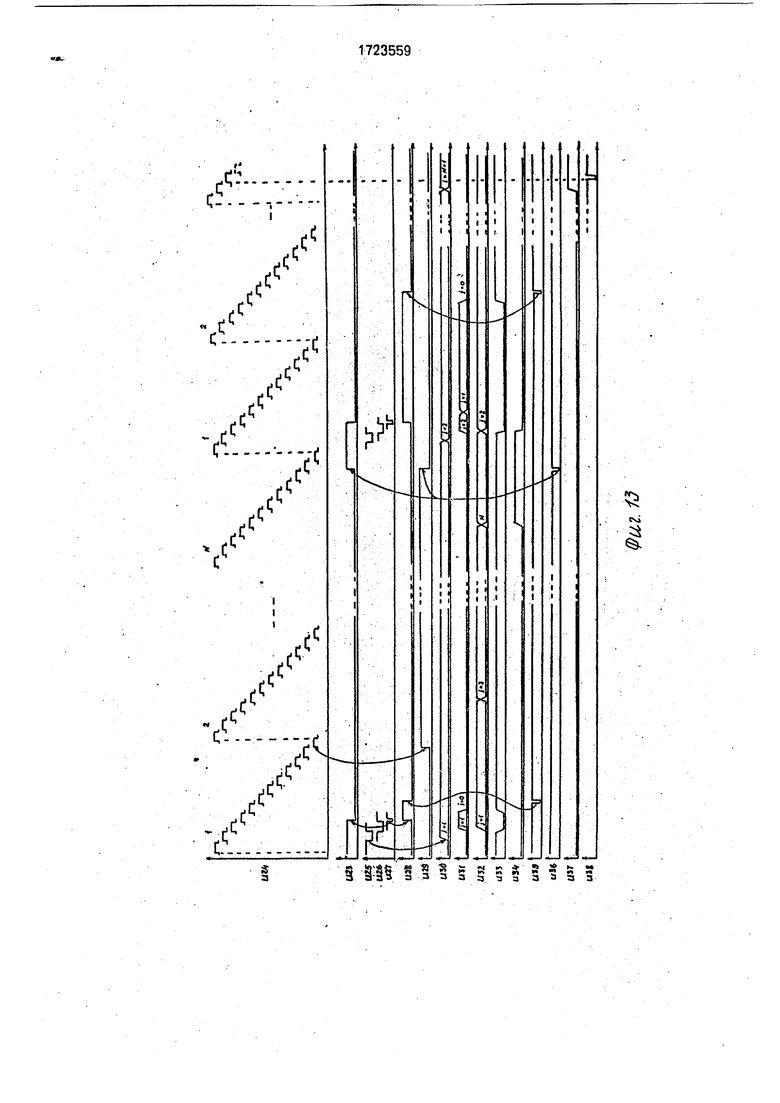

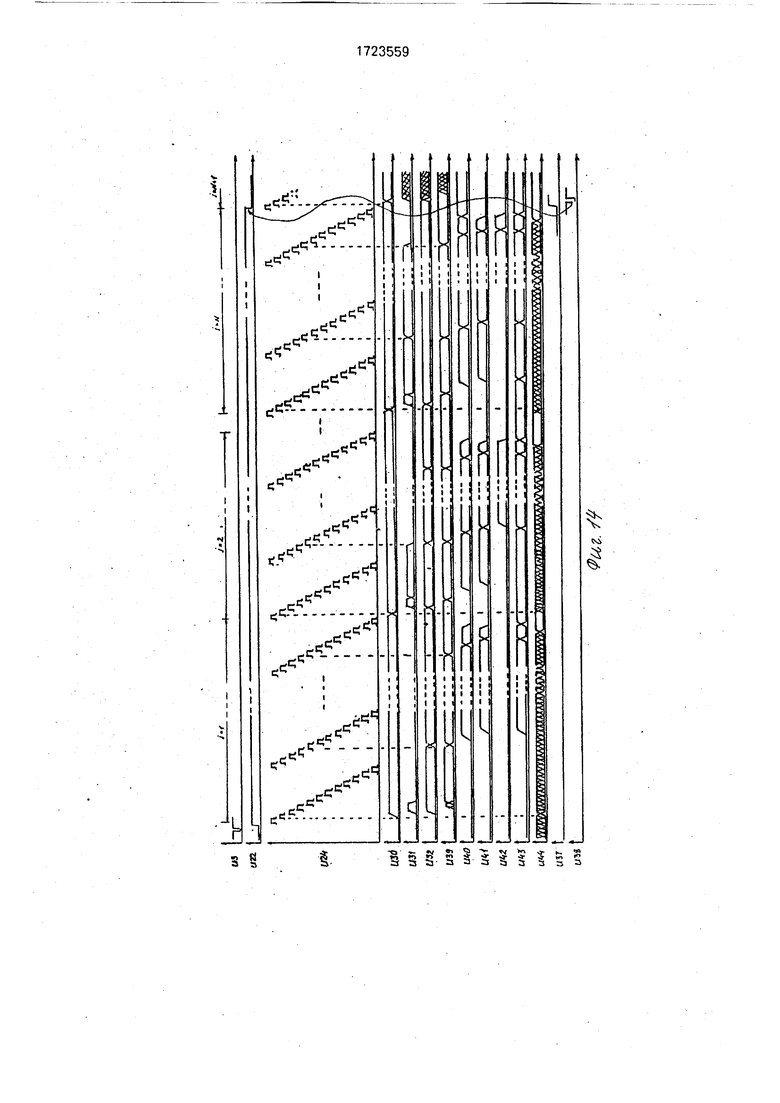

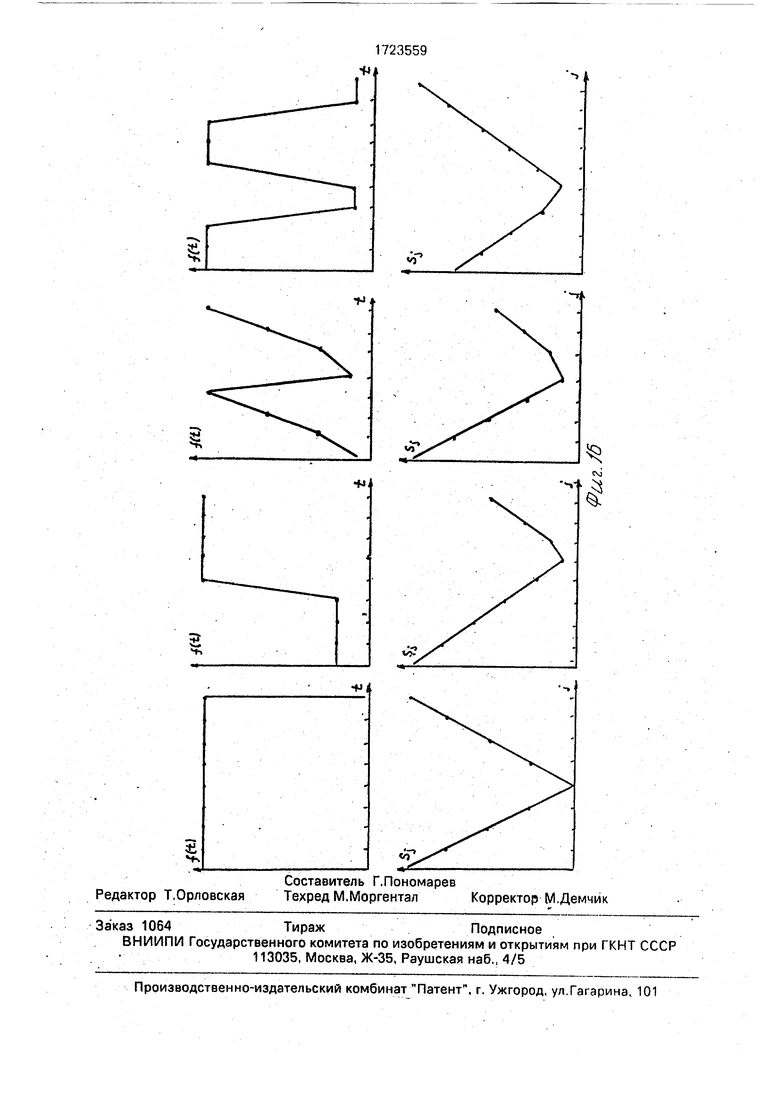

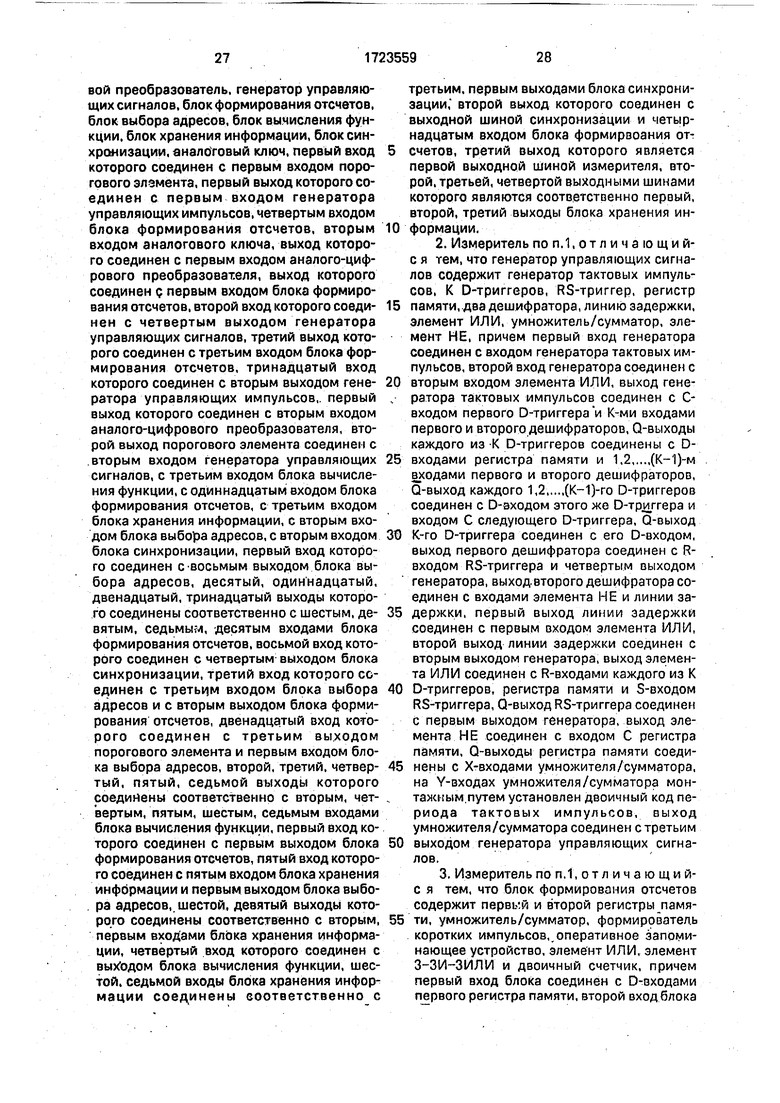

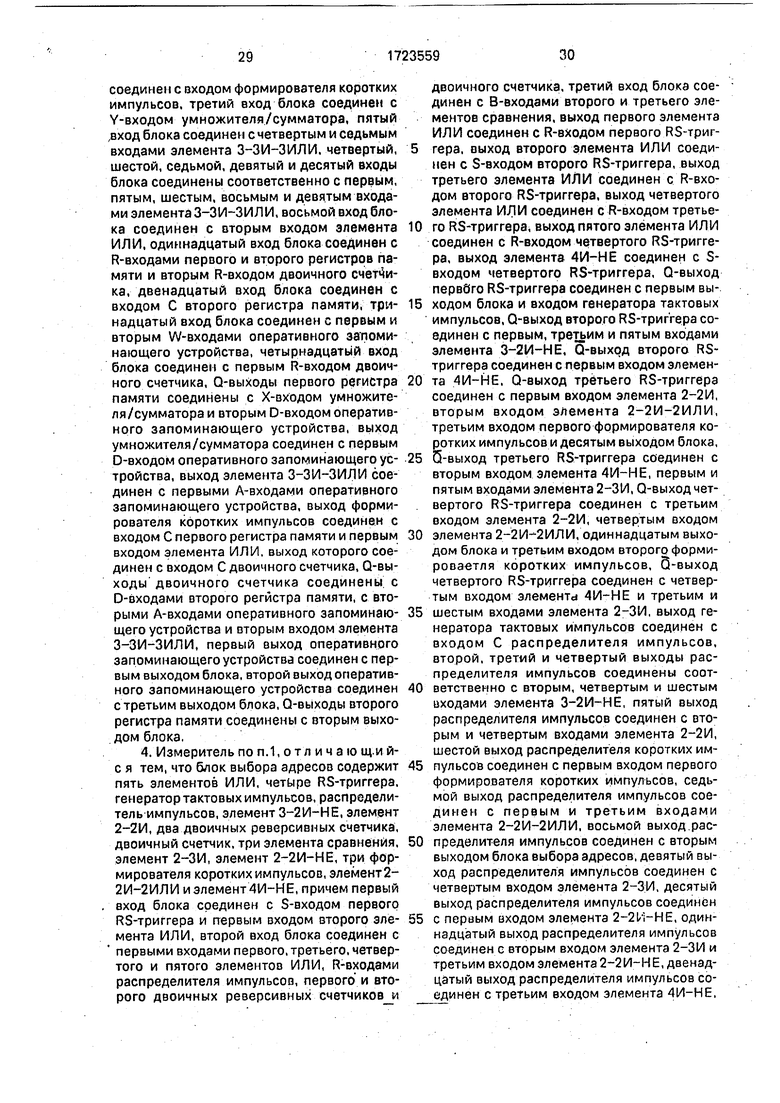

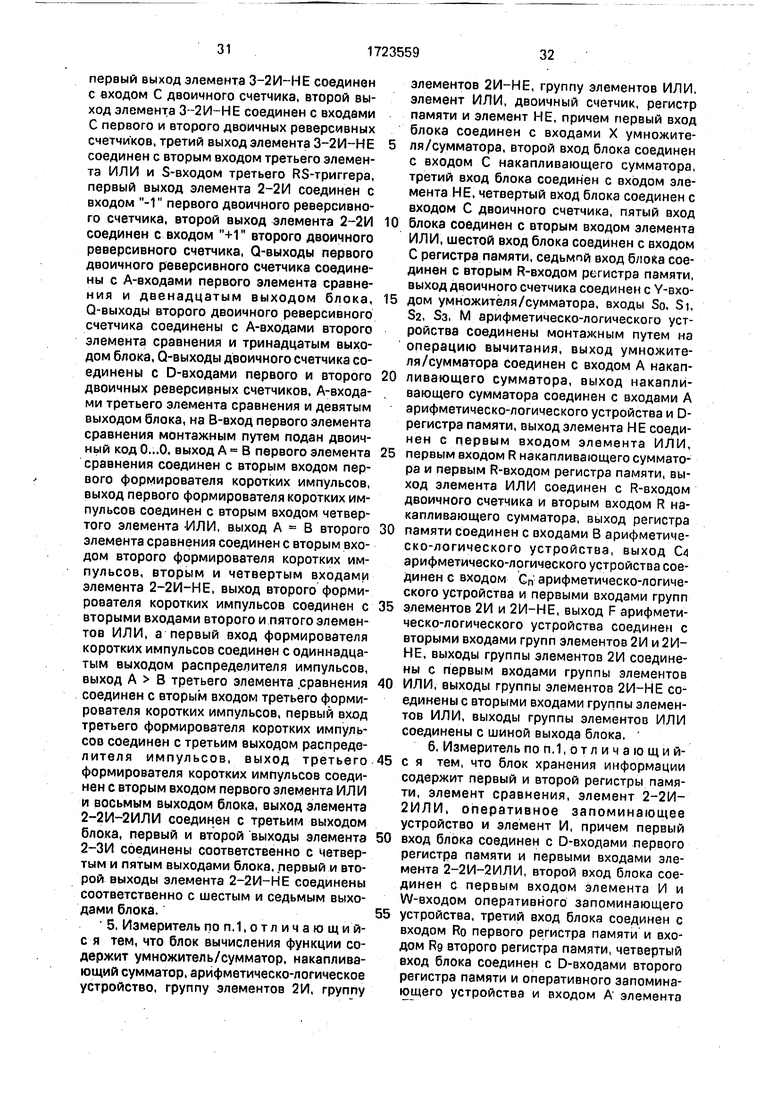

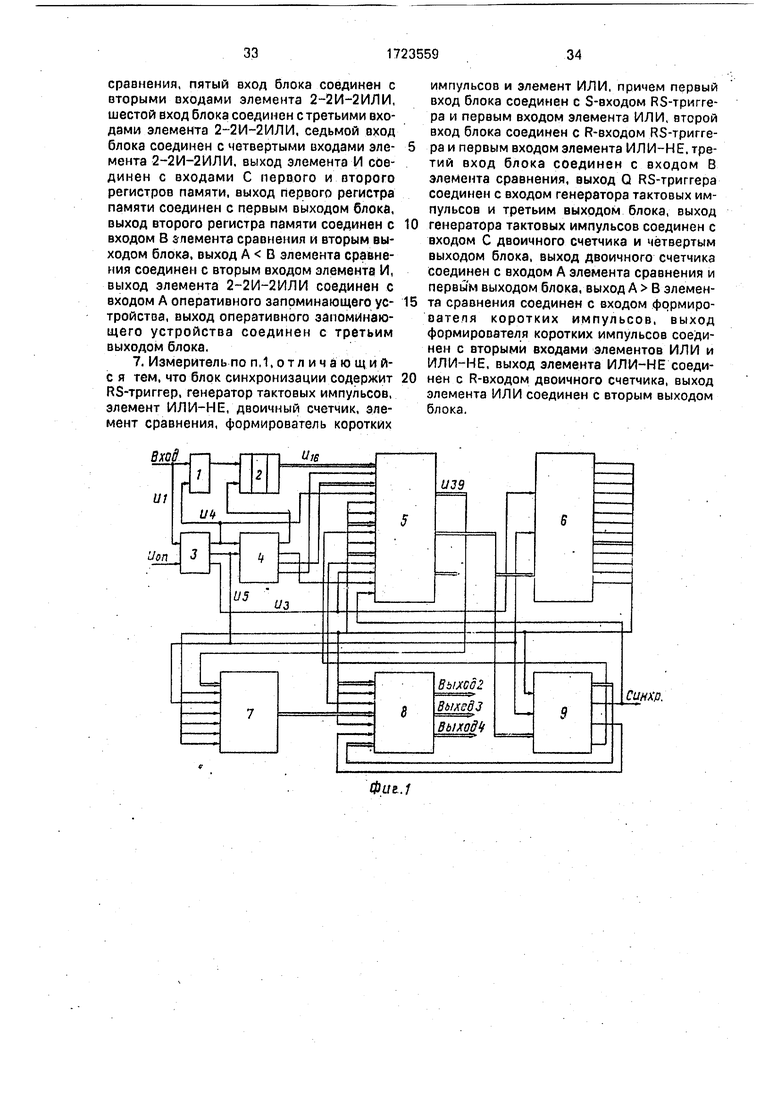

На фиг.1 приведена структурная схема цифрового измерителя центра тяжести видеосигналов; на фиг.2 - функциональная схема блока синхронизации; на фиг.З - функциональная схема порогового элемента; на фиг.4 - функциональная схема генератора управляющих сигналов; на фиг.5 - функциональная схема блока формирования отсчетов; на фиг.6 - функциональная схема блока выбора адресов; на фиг.7 - функциональная схема блока вычисления функции различия моментов; на фиг.8- функциональная схема блока хранения информации; на фиг.9-14 - временные диаграммы работы измерителя; на фиг. 15 - блок-схема алгоритма вычисления центра тяжести видеосигналов; на фиг.1б - примеры форм сигналов и их функций различия моментов.

Цифровой измеритель центра тяжести видеосигналов содержит (фиг.1) аналогичный ключ 1 типа К590КН2, аналого-цифровой преобразователь 2, пороговый элемент 3, генератор 4 управляющих сигналов (ГУС), блок 5 формирования отсчетов (БФО), блок 6 выбора адресов (БВА), блок вычисления функции (БВФ), блок 8 хранения информации, блок 9 синхронизации.

Пороговый элемент содержит (фиг.З) компаратор 10 типа К554САЗ, Ш597СА2, элемент НЕ 11, формирователи 12 и 13 коротких импульсов.

Генератор управляющих сигналов содержит (фиг.4) генератор 14 тактовых импульсов. D-триггеры 15.1-15.К RS-триггер 16, регистр 17 памяти, дешифраторы 18 и 19, линию 20 задержки, элемент ИЛИ 2 умножитель/сумматор 22 типа 564ИП5, элемент: НЕ 23.

Блок формирования отсчетов содержит (фиг.5) первый, регистр 24 памяти, умножитель/сумматор 25 типа 564ИП5, формирователь 26 коротких импульсов, оперативное запоминающее устройство 27 типа КР565РУ2, КР132РУ6, элемент ИЛИ 28, элемент 3-ЗИ-ЗИЛИ 29, двоичный счетчик 30, второй регистр 31 памяти.

Блок выбора адресов содержит (фиг.б) первый...пятый элементы ИЛИ 32...36, первый...четвертый RS-триггеры 37...40, генератор 41 тактовых импульсов, распределитель 42 Импульсов, элемент 3-2И-НЕ 43, элемент 2-2И 44, первый и второй двоичные реверсивные счетчики 45 и 46 типа 155ИЕ7, двоичный счетчик 47, первую...третью схемы 48...50 сравнения типа

564ИП2 и К555СП1, элемент 2-ЗИ.51, элемент 2-2И-НЕ 52, первый...третий формирователи 53...55 коротких импульсов, элемент 2-2И-2ИЛИ 56. элемент4И-НЕ 57;

Блок вычисления функции содержит

(фиг.7) умножитель/сумматор 58 типа 564ИП5, накапливающий сумматор 59, арифметическо-лргическбе устройство 60 типа 155ИПЗ, 564ИПЗ, группу 6.1 элементов

2И, группу 62 элементов 2И-НЕ, группу 63 элементов ИЛИ, элемент ИЛИ 64, двоичный счетчик 65, регистр 66 памяти, элемент НЕ 67.

Блок хранения информации содержит

(фиг.8) первый и второй регистры 68 и 69 памяти, схему 70 сравнения типа 564ИЛ2 и К555СЛ1, группу 71 элементов 2-2И-2ИЛИ, оперативное запоминающее устройство 72 типа КР565РУ2. КР132РУ6, элемент И 73.

Блок синхронизации содержит (фиг.2)

RS-триггер 74, генератор 75 тактовых импульсов, элемент ИЛИ-НЁ 76, двоичный счетчик 77, схему 78 сравнения типа 564ИП2 и К555СП1, формирователь 79 коротких импульсов, элемент ИЛИ 80.

Алгоритм работы цифрового измерителя центра тяжести видеосигналов включает следующие действия.

Производится дискретизация сигнала

f(t) неотрицательной полярности в интервале времени а,Ь, с периодом дискретизации At и определяется число N отсчетов сигнала в заданном интервале времени. В результате формируется массив {fj}j-iN отсчетов fj

анализируемого сигнала, включающий N слов, записываемых в ОЗУ.

Далее формируется функция различия моментов анализируемого сигнала {.fj}jN. При этом для каждого номера j определяется различие

.1N-I.

S ЁИН- 2 ifj+1 At

между левым

45

I, Ifj-iAt H

и правым

N-j

Я

fj+iAt

моментами сигнала относительно j-ro отсчета сигнала. Определение производится с точностью до мультипликативной константы At, равной периоду дискретизации сиг- нала..

Затем определяется значение

I характеризующее величину отклонения расчетного центра тяжести от истинного на интервале времени а, чем

ближе к нулю это значение, тем меньше расчетный центр тяжести отличается от истинного для анализируемого дискретного сигнала {fj}j-i .

Номер j отсчета, на котором достигаетm n- fi является расчетным центром

ся

.N

тяжести сигнала. Положение расчетного центра тяжести на оси времени определяется началом интервала времени а, периодом дискретизации сигнала Ахи номером j отсчета из выражения а + А Т (j-1).

Функция различия моментов сигнала выдается для отображения на графический индикатор, а минимальное ее значение и его временное положение - на цифровые индикаторы.

Устройство имеет три цикла работы: цикл 1 - формирование и запись массива отсчетов анализируемого сигнала, цикл 2 - формирование функции различия моментов сигнала и определение ее минимального значения, отыскание его положения в массиве значений функции, цикл 3 - выдача информации для отображения формы анализируемого сигнала, его функции различия моментов, ее минимального значения и положения последнего на оси времени.

Временная диаграмма последовательности выполнения этих циклов представлена на фиг,9. Суммарная длительность выполнения циклов определяет минимальный Период повторения входных видеосигналов.

Цикл 1 - формирование и запись массива отсчетов сигнала.

В данном цикле устройство преобразует аналоговый сигнал f(t) в цифровой KOA fj с периодом дискретизации At и выполняет операцию умножения Aj fj -At.

Устройство работает следующим образом.

На шину Вход поступает анализируемый сигнал И1 (фиг.1) и далее на первые входы аналогового ключа (АК) 1 и порогового элемента (ПЭ) 3. ПЭ 3 вырабатывает управляющие сигналы. В исходном состоянии на вход 2 компаратора 10 (фиг.З) подано опорное напряжение Uon. на вход 1 компаратора не поступает анализируемый сигнал. На выходе компаратора установлен потенциал логической единицы. На вход 1 ПЭ (фиг.З) поступает анализируемый сигнал Ui (фиг. 10). На вход 2 поступает опорное напряжение Uon. Когда амплитуда входного сигнала Ui превысит величину опорного напряжения Don (точка ц на фиг.10). то на выходе компаратора 10 появляется выходное напряжение LJ2, уровень кото рога соответствует лог.О (фиг.10). Сигнал Ua

поступает на вход элемента НЕ 11, инвертируется. На выходе элемента 11 вырабатывается сигнал U4, который поступает на вход формирователя 12 коротких импульсов 5 (ФКИ). ФКИ 12 вырабатывает по фронту V сигнала LM короткий сигнал Us отрицательной полярности (фиг.10),

Когда амплитуда входного сигнала Ui станет меньше величины опорного напря0 жения Uon (точка ta), на выходе компаратора 10 появится выходное напряжение U2, уровень которого соответствует лог. 1 (фиг. 10). По заднему фронту сигнала U2 вырабатывается короткий отрицательный сигнал

5 Ua (фиг. 10) формирователем 13 коротких импульсов.

Таким образом, ПЭ 3 вырабатывает три управляющих сигнала: сигнал И4 на выходе 1 положительной полярности, по длительно0 сти равный длительности анализируемого сигнала (ti-t2); сигнал И5 на выходе 2 отрицательной полярности, временное положение которого соответствует началу анализируемого сигнала tt; сигнал ИЗ на

5 выходе 3 отрицательной полярности, временное положение которого соответствует окончанию анализируемого сигнала t2.

Сигнал с 2-го выхода используется в качестве сигнала Уст.О, который поступает

0 на установочные входы блоков и приводит . устройство в исходное состояние.

Сигнал с 3-го выхода фиксирует момент

окончания формирования массива отсчетов.

Сигнал с 1-го выхода поступает на 1-й

5 вход генератора 4 управляющих сигналов (ГУС), на 2-й вход аналогового ключа 1 и на 4-й вход блока 5 формирования отсчетов.

Элементы ГУС 4 находятся в следующем исходном состоянии: генератор 14

0 тактовых сигналов не вырабатывает последовательности импульсов, D-триггеры 15 обнулены, на их выходах установлен потенциал логического нуля, RS-триггер 16 находится в единичном состоянии, на его

5 Q-выходе установлен потенциал логический единицы, на входе умножителя /сумматора 22 установлен потенциал логического нуля, на входе У установлен двоичный код периода тактовых импульсов.

0 ГУС 4 (фиг.4) работает следующим образом. На 1-й вход ГУС 4 поступает управляющий сигнал UA лог.1 с 1-го выхода формирователя 3 управляющих сигналов (фиг.12) и далее на вход генератора 14 так5 товых импульсов, Генератор 14 вырабатывает последовательность тактовых импульсов Uo. Причем временное положение переднего фронта пер вого тактового импульса Ue задержано относительно переднего фронта ммпульса U4 и Us. ГУС 4 устанавливается в

исходное состояние импульсом Us Уст.О, который поступает на 2-й вход ГУС 4 (фиг.4), Сигнал Us Уст.О поступает на R-входы D- триггеров 15.1...15 К регистра 17 памяти, а также на S-вход RS-триггера 16. На Q-выхо- дах триггеров 15 и регистра 17 памяти устанавливаются потенциалы U, UB, Ug и Ui4 лог.О, а на Q-выходе RS-триггера 16 - потенциал Ui3 лог.1 (фиг.12). D-триггеры 15.1...15.К включены последовательно и представляют собой двоичный многоразрядный счетчик, обеспечивающий формирование управляющих сигналов. На фиг.12 представлена временная диаграмма для четырехразрядного счетчика. ГУС 4 вырабатывает следующие управляющие сигналы: сигнал U13 для управления работой аналого- цифрового преобразователя 2; сигнал Uis- импульс записи в блок 5 формирования отсчетов; значение периода дискретизации At аналогового сигнала в двоичном коде.

Тактовые импульсы Ue с выхода генератора 14 (фиг) поступают на С-вход D-триг- гера 15.1, Q-выход предыдущего триггера соединен с С-входом последующего триггера. D-триггер работает в счетном режиме с коэффициентом деления 2. D-триггеры 15.1...15.К обеспечивают необходимый период A t дискретизации аналогового сигнала. Количество К последовательно включенных D-триггеров определяется периодом дискретизации A t сигнала ичз и периодом t™ тактовых импульсов Ue:

(ent - +1).

tlM

Сигнал U.13 формируется с помощью RS- триггера 16, который устанавливается в единичное состояние импульсом Us Уст.О или импульсом Un с выхода линии задержки 20, а в нулевое состояние им пульсом.012, поступающим с выхода дешифратора 18. Импульс U12 вырабатывается многовходовым элементом И-НЕ 18. Дешифратор 18 представляет собой К-входовый элемент И-НЕ, на входы которого подаются потенциалы с Q- выходов D-триггеров 15.1...15.К и тактовый импульс Ue. При поступлении на все входы потенциалов лог.1, на выходе дешифратора 18 вырабатывается импульс Ui2 отрицательной полярности (на фиг.12 импульс Ui2 вырабатывается для пятого тактового импульса Ue).

Дешифратор 19 представляет собой I- входовый элемент И-НЕ, но для восьмого тактового импульса иб(фиг.12). Импульс Uio с выхода дешифратора 19 поступает на вход линии задержки 20. С одного выхода ЛЗ 20 сигнал Un поступает на первый вход элемента ИЛИ 21 и далее на S-вход RS-триггера

вырабатываемым дешифратором 19.

Сигнал Uis представляет собой импульс Uio, но задержанный ЛЗ 20 на время переходных процессов в элементах 16 и 22. На D-входы регистра 17 памяти поступают сигналы с Q-выходов триггеров 15.1...15.К, а на С-вход поступает инвертируемый элементом НЕ 23 импульс положительной полярности. По фронту V Uio осуществляется запись информации с Dвходов в регистр 17 памяти. На выходах регистра 17 памяти устанавливается двоичный код количества тактовых импульсов п, определяющих длительность периода дискретизации At п t™.

Умножитель/сумматор 22 производит операцию умножения двух двоичных чисел в соответствии с выражением: X«Y + К + М. Для выполнения операции умножения входы К и М монтажным путем соединяются

с потенциалом лог.О. При этом числа К и М в двоичном коде.равны нулю.

На входы X поступает двоичный код числа п с Q-выходов регистра 17 памяти, а на входы Y - двоичный код числа t™, причем

двоичный код Тти устанавливается монтажным путем в зависимости от значения частоты тактируемых импульсов UG генератора 14.

Управляющие импульсы поступают: с

выхода Uis на вход ги АЦП 2, с 2-го выхода Uis на 13-й вход блока 5 формирования отсчетов, с 3-й шины на 3-й входы блока 5 формирования отсчетов.

Элементы блока 5 формирования отсчетов находятся в следующем исходном состоянии. Регистры 24 и 31 памяти (фиг.5) обнулены, на их выходах установлены потенциалы логического нуля. Двоичный счетчик 30 обнулен, на его выходах установлен

двоичный код 0...0, что соответствует адресу нулевой ячейки ОЗУ 27.

При поступлении сигнала Uia на вход Ги АЦП 2 осуществляется преобразование аналогового сигнала, поступающего с выхода АК 1 на вход UBx АЦП 2, в цифровой код. Работой АЦП 2 управляет сигнал Ui3. Выборка осуществляется по переднему фронту тактового импульса Uis (фиг.11). Результат кодирования Uie выдается с подачей заднего фронта тактового импульса 1Нз (фиг.11); Двоичный код U 1в дискретного сигнала поступает на 1-й вход блока 5 формирования отсчетов, и далее на D-входы регистра 24 памяти (фиг,5). Запись информации с D-входов

на выход регистра 24 памяти осуществляется импульсом Ui (фиг.11), который формируется по положительному импульсу Ui2 (фиг. 12). Временное положение импульса Ui таково, что переходные процессы в АЦП 2 окончились и на выходе его информация достоверна. С выходов регистра 24 памяти двоичный код поступает на Х-вход умножителя/сумматора 25, На его Y-входы поступает двоичный код DIB значения периода дискретизаций Ate 3-го выхода ГУ С 4. Входы К и М умножителя /сумматора 25 монтажным путем соединены с логическим нулем. Таким образом, умножитель/сумматор 25 выполняет только операцию умножения X-Y+K + M X-Y. Результат умножения Х- Y fj -At записывается в ОЗУ 27.1, а дискретное значение входного сигнала fj - в ОЗУ 27.2. С выходов умножителя/сумматора 25 двоичный код поступает на D-входы РЗУ 27.1, а на D-входы ОЗУ 27.2 - значение fj. Адрем ячеек ОЗУ 27.1, в которые необходимо записать результат умножения, задается двоичным счетчиком 30. На счетный вход С счетчика 30 поступают положительные импульсы Ui через элемент 28 ИЛИ, по переднему их фронту изменяется состояние счетчика 30 (IJ20, фиг.11). С Q-выходов счетчика 30 двоичный код поступает на 2-е входы группы 29 элементов 3-ЗИ-ЗИЛИ и далее на адресные входы ОЗУ 27.1. Импульс записи U15 формируется генератором 4 управляющих сигналов (фиг. 12), который по.- ступаетна 1-3-й вход блока 5 формирования отсчетов и далее на W-входы ОЗУ 27. Импульс записи U15 поступает на W-вход ОЗУ 27 тогда, когда на D- и А-входах окончились переходные процессы. Время задержки выбирается с помощью линии задержки 20 генератора управляющих сигналов.

Количество отсчетов N определяется длительностью сигнала Ui, величиной выбранного порога Don и периодом дискретизации At.

Окончание цикла формирования и записи массива отсчетов фиксируется по заднему отрицательному фронту импульса Ш. когда амплитуда входного сигнала Ui станет меньше величины опорного напряжения Ооп (фиг.11). На 1-м выходе генератора управляющих сигналов прекращается выдача разрешающего потенциала . В этом случае прекращается генерация тактовых импульсов генератором 14 и не вырабатываются управляющие сигналы ГУС4, запрещается выбор адресов ОЗУ 27.

Сформированный пороговым элементом 3 отрицательный импульс Us (.фиг.11) поступает на 12-й вход блока 5 формирования отсчетов и далее на С-входы регистра 31 памяти. По фронту | импульса из осуще ствляется запись двоичного кода числа отсчетов N с Q-выходов двоичного счетчика 30 5 в регистр 31 памяти (U21. фиг. 11).

Таким образом, по окончании цикла в ячейках ОЗУ 27.1 записано в двоичном коде значение произведения амплитуды сигнала на период дискретизации: Aj fj At, а в

0 ОЗУ 27.2 - значение fj. В регистре 31 памяти записано в двоичном коде число N отсчетов анализируемого сигнала.

Цикл 2 - формирование функции различия м оментов сигнала, определение ее ми5 нимального значения и отыскание его положения в массиве отсчетов.

В данном цикле работают блоки 5-8. В исходном состоянии в блоке 6 RS- триггеры 37...40 установлены в нулевое со0 стояние. На Q-выходах RS-триггеров установлены потенциалы логического нуля. Счетчики 45...47 обнулены. На генератор 41 поступает потенциал запрещения, и на его выходе отсутствуют прямоугольные импуль5 сы. На выходе А В схемы 48 сравнения установлен потенциал логической единицы. На выходах А В и А В схем 49 и 50 сравнения установлены потенциалы логического нуля.

0В блоке 7 (фиг.7) счетчик 65, накапливающий сумматор 59 и регистр 66 памяти находятся в исходном состоянии. На Q-выходах их установлены потенциалы логического нуля.

5 В блоке 8 (фиг.8) регистры 68 и 69 памяти установлены соответственно в нулевое и единичное состояние. На Q-выходах регистра 68 памяти установлены потенциалы логического нуля, а на Q-выходах регистра 69 0 потенциалы логической единицы. На выходе А В установлен потенциал логического нуля.

В данном цикле устройство вычисляет . значение функции различия моментов сиг5 нала в соответствии с выражением:

sj I i 1АН-1(н)А,|.

Ч j-1 -1 + 1

Технически алгоритм реализуется следую- 0 щим образом.

По окончании входного сигнала Ui ПЭ 3 вырабатывает отрицательный прямоугольный импульс Us (фиг.Ю. 13). Импульс Уз с 3-го выхода ПЭ 3 поступает на 1-й вход блое ка 5 выбора адресов, элементы которого (фиг.6) находятся в исходном состоянии: RS- триггеры 37...40 - в нулевом состоянии, на Q-выходах RS-триггеров 37...40 установлен нулевой потенциал, распределитель 42 импульсов не вырабатывает управляющих имульсов, счетчики 45...47 находятся в исходом состоянии, т.е. на Q-выходах счетчиков становлен двоичный код 0...0. На выходе В схемы 48 сравнения установлен потенциал логической единицы, на выходе А В 5 хемы 49 сравнения - потенциал логического нуля, на выходе А В схемы 50 сравнения - потенциал логического нуля.

С 1-го входа блока 6 выбора адресов импульс 1)з (фиг.10,13) поступает на S-вход 10 триггера 37 и на 1-й вход элемента 33 ИЛИ,, и далее на S-вход триггера 38. По фронту | импульса Us RS-триггеры 37 и 38 устанавливаются в единичное состояние. На Q-выходах RS-триггеров 37 и 38 устанавли- 15 ваются соответственно потенциалы логической единицы U22 и U23 (фиг. 13).

С 6-выхода RS-триггера 37 потенциал логической единицы 1)22 поступает на вход генератора 41 тактовых импульсов. С выхо- 20 да генератора 41 тактовые импульсы поступают на С-вход распределителя 42 импульсов/который на выходах 1...12 выдает серию импульсов прямоугольной формы U24, сдвинутых друг относительно друга, а 25 длительность их равна периоду повторения тактовых импульсов. Распределитель 42 импульсов вырабатывает циклически пачки по двенадцать импульсов до тех пор, пока на- ходится в единичном состоянии RS-триггер 30 37, т.е. пока не будет определена функция различия моментов сигнала для всех отсчетов.

Потенциал (J23 (фиг. 13) логической единицы с Q-выхода RS-триггера 38 поступает 35 на 1-й, 3-й и 5-й входы элемента 43 3-2И- НЕ. На 2-й, 4-й и 6-й входы этого элемента поступают соответственно второй, третий и четвертый импульсы положительной полярности U24 с 2-го, 3-го и 4-го выходов распре- 40 делителя 42 импульсов. На 1-м, 2-м, и 3-м выходах элемента 3-2И-НЕ 43 формируются прямоугольные отрицательные импульсы U25, U26 и 1)27. Временное положение импульсов U25, U26 и U27 соответствует второ- 45 му, третьему и четвертому импульсам U24. Импульс U25 поступает на С-вход счетчика 47 и по фронту Ч U25 изменяет состояние счетчика 47 (изо, фиг. 13). На счетчике 47 устанавливается текущее значение номера 50 j-ro отсчета (на фиг. 13, J 1 и J - 2), относительно которого осуществляется перебор адресов ячеек ОЗУ 27.1, расположенных слева и справа от J.

Импульс U26 поступает на С-входы счет- 55 чиков 45 и 46, по фронту f производит перезапист информации по D-входам с Q- выходов счетчика 47 на выходы счетчиков 45 и 46. На Q-выходах счетчиков 45 и 46 устанавливается двоичный код Usi и U32 соответственно текущему двоичному коду счетчика 47.

Импульс 1)27 поступает на 2-й вход элемента ИЛ И 34 и далее на R-вход триггера 38, который устанавливается в нулевое (исходное) состояние. На Q-выходе триггера 38 устанавливается потенциал логического нуля U23 и запрещает прохождение в дальнейшем второму, третьему и четвертому импульсам 1/24 (фиг. 13).

Кроме того, импульс U27 поступает на S-вход триггера 39 и устанавливает его в единичное состояние 1/28. Разрешающий потенциал U28 поступает на 1-й вход элемента 2-2И 44. На 2-й вход этого элемента поступает прямоугольный положительный импульс с 5-го выхода распределителя 42 импульсов. С 1-го выхода элемента 44 импульс поступает на вход -1 счетчика 45 и изменяет его состояние USL Счетчик 45 работает в режиме вычитания, поэтому при каждом поступлении импульса на вход -1 осуществляется вычитание единицы из содержимого счетчика 45 (вычитание единицы начинается с текущего значения J, установленного на счетчике 47). Уменьшение содержимого счетчика 45 осуществляется до тех пор, пока на Q-выходах его не появится двоичный код 0...0. Этот момент фиксируется схемой 48 сравнения. На А-входы схемы 48 поступает двоичный код с Q-выходов счетчика 45 Uai, а на В-входы - двоичный код 0...0, причем двоичный код 0...0 на В-входах схемы 48 сравнения устанавливается монтажным путем. При равенстве кодов на А- и В-входах схемы 48 сравнения на ее входе А В устанавливается потенциал логической единицы 11зз(фиг.13), который поступает на 2-й вход формирователя 53 коротких импульсов. На 3-й вход этого формирователя поступает потенциал U28 логической единицы с триггера 39, а на 1-й вход - импульс с 6-го выхода распределителя 42 импульсов. На выходе ФКИ 53 вырабатывается импульс Uss отрицательной полярности, который поступает на 2-й вход элемента ИЛИ 35 и далее на R-вход триггера 39 и устанавливает его в исходное состояние U20 (фиг.13). На выходе триггера 39 устанавливается потенциал логического нуля U28 (фиг.13) по фронту f импульсов Uss и U28 и запрещает прохождение пятого импульса на вход -1 счетчика 45. Таким образом, на Q-выходах счетчика 45 последовательно устанавливается двоичный код чисел J-1, J-2О, т.е.

осуществляется перебор адресов ячеек памяти 27.1 от J-1 до 0. После установки на счетчике 45 числа 0 начинается перебор адресов справа. Выбор адресов справа от текущего значения номера отсчета j

производится следующим Образом, На 1-й вход элемента 4И-НЕ 57 поступает потенциал лог. Г с U-выхода триггера 39, на 3-й вход потенциал лог., Г с Q-выхода триггера 40, а на 2-й вход двенадцатый импульс U24 с 2-го выхода распределителя 42 импульсов. На выходе элемента 4И-Н Е 57 формируется импульс отрицательной полярности, который поступает на S-вход триггера 40 и устанавливает его в единичное состояние (фиг. 13). На Q-выходе триггера 40 устанавливается потенциал U29 логической единицы (фиг.13), который поступает на 3-й вход элемента 2-2И 44. На 4-й вход этого же элемента поступает прямоугольный положительный импульс с 5-го выхода распределителя 42 импульсов. С 2-го выхода элемента 2-2И 44 импульс положительной полярности поступает на вход +1 счетчика 46. По фронту . изменяется состояние счетчика 46 U32. Счетчик 46 работает в режиме сложения, поэтому при каждом поступлении импульса на вход +1 содержимое счетчика 46 увеличивается на единицу (добавление единицы начинается с текущего значения номера j, установленного на счетчике 47). Увеличение содержимого счетчика 46 производится до тех пор, пока на Q-вы- ходах счетчика 46 не установится двоичный код, соответствующий числу N. Этот момент фиксируется схемой 49 сравнения. На А: входы схемы 49 сравнения подается двоичный код 1)з2 с Q-выходов счетчика 46, а на В-входы - двоичный код Uia числа N отсчетов с Q-выходов регистра 31 памяти блока 5. При равенстве двоичных кодов на входах А и В схемы 49 сравнения на выходе А В схемы устанавливается потенциал 1Ы логической единицы (фиг.13). Этот потенциал подается на 2-й вход формирователя 54 коротких импульсов. На 3-й вход ФКИ 54 подается потенциал с Q-выхода триггера 40. На 1-й вход ФКИ 54 подается одиннадцатый импульс с выхода распределителя 42 импульсов. По фронту f одиннадцатого импульса 1)24 формируется ФКИ 54 отрицательный импульс Узе, который поступает на 2-е входы элементов ИЛИ 36 и 33. С выхода элемента ИЛИ 36 импульс поступает на R- вход триггера 40 и устанавливает его в исходное (нулевое) состояние. На Q-выходе триггера 40 устанавливается потенциал U29 логического нуля и запрещает прохождение пятого импульса на вход +1 счетчика 46 (фиг. 13).

Таким образом, на Q-выходах счетчика 46 последовательно устанавливается двоичный код чисел j + 1, j + 2N, т.е. осуществляется перебор адресов ячеек памяти 27 от j + 1 до N.

Следует заметить, что на фиг. 13 изображены временные диаграммы для состояния счетчика 47 при номере J 1 отсчета и частично - при j 2, причем перебор адресов

5 справа и слева от j осуществляется только после установления текущего значения номера j-ro отсчета на счетчике 47. Перебор всех значений номеров J с помощью счетчика 47 производится до тех пор, пока на Q0 выходах его не установится двоичный код числа N + 1, Этот момент фиксируется схемой 50 сравнения. На А-входы схемы 50 сравнения подается двоичный код с Q-выходов счетчика 47, а на В-входы - двоичный

5 код числа N с Q-выходов регистра 31 БФО 5. Кактолько двоичный код на входе-А будет равен числу N + 1, на выходе А В установится потенциал логической единицы Уз (фиг. 13), который поступает на 2-й вход фор0 мирователя 55 коротких импульсов. На 1-й вход поступает третий импульс 1124 с распределителя 42 импульсов. ФКИ 55 вырабатывает импульс отрицательной полярности 1)зв, который поступает на 2-й вход элемента

5 ИЛИ 32 и далее на вход R триггера 37, На Q-выходе триггера 37 устанавливается потенциал U22 логического нуля (фиг. 13), который поступает на вход генератора 4.1 тактовых импульсов. Генератор 41 и распре0 делитель 42 импульсов прекращают вырабатывать управляющие сигналы. На этом прекращается перебор адресов ячеек памяти 27.1.

Операции умножения I AJ-I , суммирова5

ния 5) i Aj-1 и вычитания

iiA -vJ+vj)Ai

)

Q осуществляются блоком 7.

Двоичный код числа AJ-I с 1-го выхода БФО 5 поступает на 1-й вход БВФ 7. Значение AJ-I считывается из ячеек ОЗУ 27.1 БФО 5, расположенных (условно) слева от j-й

5 ячейки, а затем - справа от нее. Адреса ячеек задаются счетчиками 45 и 46 БВА 6 (фиг, 14), С Q-выходов счетчиков 45 и 46 двоичные коды 11з1 и Кз2 через 12-й и 13-й выходы подаются на 7-й и 10-й входы БФО 5 и

Q далее через 6-й и 9-й входы элемента 3-ЗИ- ЗИЛИ 29 на адресные входы А ОЗУ 27, С 1-го выхода БВА 6 через 5-й вход БФО 5 на 4-й и -7-й входы элемента 29 подается разрешающий потенциал U22 с Q-выхода RS-триггера

5 РазРешаюи ий потенциал подается только на время вычисления функции различия моментов. С Q-выходов RS-триггеров 39 и 40 подаются разрешающие потенциалы U28 и U29 через 10-й и 11-й выходы БВА 6, 6-й и 9-й входы БФО 5 на 5-й и 8-й входы элемента

3-ЗИ-ЗИЛИ 29. Эти разрешающие потенциалы осуществляют селекцию двоичных кодов IJ31 и Уза, поступающих одновременно на элемент 29 со счетчиков 45 и 46 БВА 6. Выбранное значение AJ-I 1)29 поступает на 1-й вход БВФ 7 и далее на вход X умножителя/сумматора 58 (фиг.6 и 14). На вход Y поступает двоичный код Uio с Q-выходов двоичного счетчика 65 текущего значения j-l. Состояние счетчика 65 БВФ 7 (U40, фиг. 14) изменяется с приходом каждого импульса с выхода элемента 2-2И-2ИЛИ 56 БВА 6. Временное положение этого импульса соответствует седьмому импульсу с выхода распределителя 42 БВА 6. Селекция этого импульса производится разрешающими потенциалами LJ28 и 1)29 с выходов RS- триггеров 39 и 40 БВА 6.

Умножитель/сумматор 58 осуществляет операцию умножения в соответствии с выражением в прямом коде X Y + К + М X Y. Входы К и М монтажным путем соединены с потенциалом логического нуля, Результат умножения с Q-выходов подается

. на А-входы накапливающего сумматора 59. Восьмой импульс, поступающий с 8-го выхода распределителя 42 через 2-й выход БВА 6 и 2-й вход.БВФ 7, подается на вход С. По фронту f восьмого импульса производится

суммирование текущего значения произведения I AJ-I с содержимым сумматора в прямом коде U41 (фиг.14), Операция суммирования значений i AJ-I по адресам, расположенным слева от J, осуществляется до тех пор. пока на счетчике 45 не установится двоичный код числа нуль. Этот момент фиксируется элементом 2-ЗИ 51.2 БВА 6. На его 5-й и б-й входы подаются разрешающие потенциалы с Q-выходов RS-триггеров 39 и 40, а на вход Y - девятый импульс с выхода распределителя 42. Положительный импульс с выхода элемента 51.2 через 5-й выход БВА 6 и 6-й вход БВФ 7 поступает на С-вход регистра 66 памяти. По фронту | осуществляется запись частичной суммы

I --Aj-i в регистр 66 памяти U42 (фиг.14).

Элементом 2-ЗИ 51.1 БВА 6 вырабатывается импульс установки в исходное состояние накапливающего сумматора 59 и счетчика 65. На 1-й и 3-й входы элемента 511 подаются разрешающие потенциалы с б-выходов RS-триггеров 39 и 40, а на 2-й вход поступает одиннадцатый импульс с выхода распределителя 42, С выхода элемента 51.1 импульс через 4-й выход 5ВА 6 и 5-й вход БВср 7 поступает на 2-й вход элемента ИЛИ 64 и далее на R-входы счетчика 65 и накапливающего сумматора 59, устанавливаемых

в исходное состояние U40 и U41 (фиг, 14). Затем осуществляется формирование частичной суммы

Я

7+1

(i-J) AI из ячеек.

расположенных справа от текущего значения J. Операции умножения (l-j)Ai и суммированияN

Zi (Н) AI производится аналогично рас- i 7+1

смотренным ранее,

Частичная сумма 2) AJ-I, записанная

в регистре 66 памяти, подается на вход В арифметическо-логического устройства 60,

На вход А подается частичная сумма У

i 7+1

(H)A| (U41, фиг.14). Входы S и М соединены на операцию вычитания, Результат вычита

i i -А)

гДг1)А1

может быть как положительным, так и отрицательным числом, АЛУ 60 представляет собой сумматор обратного кода, для чего выход старшего разряда переноса С4 соединен с младшим разрядом переноса Сп.

Если в старшем разряде переноса С4

присутствует потенциал логической единицы, то результат в АЛУ представлен в обратном коде. Для его преобразования имеется

группа 62 элементов 2И-НЕ, инвертирующая двоичный обратный код в двоичный прямой код. Если результат в АЛУ 60 получен в прямом коде, то преобразование кода не призводится, а двоичный код передается

через группу 61 элементов 2И на входы труппы ИЛИ 63. Результат вычитания записывается в ячейку памяти ОЗУ 72 импульсом с выхода элемента 2-2И-НЕ 52.1. На 2-й вход поступает разрешающий потенциал

1Ы с выхода А В схемы 49 сравнения, а на 1-й вход десятый импульс с выхода распределителя 42. С выхода элемента 2-2И-НЕ 52.1 импульс через 6-й выход БВА 6 и 2-й вход БХИ 8 поступает на W-вход ОЗУ 72, На

D-вход ОЗУ 72 с выхода группы 63 элементов ИЛИ через выход БВФ 7 и 4-й вход БХИ 8 поступает результат Sj вычитания. Адрес ячейки ОЗУ 72 задается с выхода счетчика 47 БВА 6. Двоичный код с выхода счетчика

47 через 9-й выход БВА 6 и 1-й вход БХИ 8 поступает на 1-е входы группы 71 элементов 2-2И-2ИЛИ. На 2-е входы группы 71 подается разрешающий потенциал U22 с выхода RS-триггера 37, который поступает на время вычисления функции различия моментов и

позволяет только запись информации в ОЗУ 72.

Кроме того, десятый импульс поступает на 1-й вход элемента И 73. На 2-й вход элемента И 73 поступает потенциал с выхода А В схемы 70 сравнения. В исходном состоянии в регистре 69 памяти записано максимальное двоичное число 11...1, Поэтому в исходном состоянии на выходе А В установлен потенциал логической единицы, При поступлении первого значения Si производится запись Si в регистр 69 памяти и адрес первой ячейки в регистр 68 памяти десятым импульсом. При поступлении следующего значения S. возможны два исхода: S2 Si или S2 Si. Если S2 3: Si, to на выходе А В устанавливается потенциал логического нуля и запись S2 в регистр 69 не производится. Если же S2 Si (А В), то значение Зз записывается в регистр 69 памяти. Так как на 4-й вход БХИ 8 поступают все частичные суммы Sj, j 1 ,N, то в регистре 69 памяти остается записанным минимальное значение Sj, а в регистре 68 - его адрес,

Цикл 3 - выдача информации для отображения.

В данном цикле производится выдача для отображения дискретной информации: анализируемого сигнала fj и функций различия моментов.

Начало выдачи на графический индикатор осуществляется импульсом 1)зв, поступающим с выхода элемента 55 БВА 6 через 8-й выход БВА 6 и 1-й вход блока 9 синхронизации на S-вход RS-триггера 74 (фиг.2).

В исходном состоянии RS-триггер 74 находится в нулевом положении, т.е. на его Q-выходе установлен потенциал IMs (фиг.2) логического нуля. Счетчик 77 обнулен; на его Q-вы ходах установлен двоичный код 0...0 (IJ47, фиг.2). На вход В схемы 78 сравнения поступает двоичный код числа N с 0-вы- ходов регистра 31 памяти БФО 5, На выходе схемы 78 сравнения устанавливается потенциал U48 логического нуля (фиг.2). Генератор 75 не выдает тактовых импульсов 1}4в(фип2).

При поступлении импульса Уза RS-триггер 74 устанавливается в единичное состояние, на Q-выходе его устанавливается потенциал 1)45 логической единицы. Разрешающий потенциал поступает на вход генератора 75 тактовых импульсов, который вырабатывает последовательность прямоугольных импульсов U46 (фиг.2), поступающих на С-вход двоичного счетчика 77 и изменяющих его состояние по фронту Ч каждого импульса Щ (фиг.2). Двоичные коды чисел 1, N + 1 подаются на вход А схемы 78 сравнения, На вход В ее подается двоичный код числа N с выхода регистра 31 памяти БФО 5. Когда двоичное мисло на входе А превысит двоичное число на входе В, то на выходе А В установится потенциал 1Мв 5 логической единицы (фиг.2). По фронту f сигнала IJ48 формирователь 79 коротких импульсов вырабатывает сигнал 1)49, который является сигналом синхронизации USD (фиг,2). Сигнал Uso служит для запуска гра0. фического индикатора, Так как сигнал U49 вырабатывается только в конце последовательности из N импульсов, то в качестве первого импульса синхронизации используется импульс Uза. Объединение импульсов

5 U38 и U49 осуществляется элементом ИЛИ 80. Двоичный код U47 с выхода счетчика 77 подается через 4-й выход БС 9 и 7-й вход БХИ 8 на четвертые входы группы 71 элементов 2-2И-2ИЛИ БХИ 8 и далее на ад0 ресные входы ОЗУ 72. Разрешающий потенциал U45 поступает с Q-выхода RS- триггера 74 через 3-й выход БС 9 и 6-й вход БХИ 8 на третьи входы группы 71 элементов 2-2И-2ИЛИ. Разрешающий потенциал U45

5 поступает только на время выдачи информации для отображения.ОЗУ 72 выдает значения Sj по адресам J 1,14.

Тактовые импульсы IJ46 с выхода генератора 75 поступают через 4-й выход БС 9 и

0 8-й вход БФО 5 на 2-й вход элемента ИЛИ 28 и далее на С-вход счетчика 30, На 0-вы- ходах счетчика 30 последовательно устанавливаются коды чисел 1.N. Двоичный код поступает на адресные входы А ОЗУ 27.2.

5 Производится считывание информации fj из ячеек ОЗУ 27.2. Выдача на отображение повторяется циклически. Обнуление счетчиков 30 БФО 5 и 77 БС 9 осуществляется импульсами U49 и UBO, поступающими на R-входы.

0 Цикл выдачи информации на отображение продолжается до тех пор, пока на вход устройства не поступит следующий сигнал.

Предлагаемое устройство, в котором проводится измерение и запись отсчетов

5 видеосигнала, формирование функции различия моментов его, определение минимума функции и его временного положения и выдача информации на отображение, позволяет повысить информативность изме0 рений..

Формул а изобретения 1. Цифровой измеритель центра тяжести видеосигналов, содержащий входную шину, подключенную к первому входу по5 рогового элемента, второй вход которого соединен с шиной подачи опорного напряжения, от л ича ющийся тем,что, с целью расширения функциональных возможностей за счет повышения информативности измерения, в него введены аналого-цифровой преобразователь, генератор управляющих сигналов, блок формирования отсчетов, блок выбора адресов, блок вычисления функции, блок хранения информации, блок синхронизации, аналоговый ключ, первый вход которого соединен с первым входом порогового элемента, первый выход которого соединен с первым входом генератора управляющих импульсов, четвертым входом блока формирования отсчетов, вторым входом аналогового ключа, выход которого соединен с первым входом аналого-цифрового преобразователя, выход которого соединен Q первым входом блока формирования отсчетов, второй вход которого соединен с четвертым выходом генератора управляющих сигналов, третий выход которого соединен с третьим входом блока формирования отсчетов, тринадцатый вход которого соединен с вторым выходом генератора управляющих импульсов,, первый выход которого соединен с вторым входом аналого-цифрового преобразователя, второй выход порогового элемента соединен с .вторым входом генератора управляющих сигналов, с третьим входом блока вычисления функции, с одиннадцатым входом блока формирования отсчетов, с третьим входом блока хранения информации, с вторым входом блока выбора адресов, с вторым входом блока синхронизации, первый вход которого соединен с восьмым выходом блока выбора адресов, десятый, одиннадцатый, двенадцатый, тринадцатый выходы которого соединены соответственно с шестым, девятым, седьмым, десятым входами блока формирования отсчетов, восьмой вход которого соединен с четвертым1 выходом блока синхронизации, третий вход которого соединен с третьим входом блока выбора адресов и с вторым выходом блока формирования отсчетов, двенадцатый вход которого соединен с третьим выходом порогового элемента и первым входом блока выбора адресов, второй, третий, четвертый, пятый, седьмой выходы которого соединены соответственно с вторым, четвертым, пятым, шестым, седьмым входами блока вычисления функции, первый вход которого соединен с первым выходом блока формирования отсчетов, пятый вход которого соединен с пятым входом блока хранения информации и первым выходом блока выбора адресов, шестой, девятый выходы которого соединены соответственно с вторым, первым входами блока хранения информации, четвертый вход которого соединен с выхЪдом блока вычисления функции, шестой, седьмой входы блока хранения информации соединены соответственно с

третьим, первым выходами блока синхронизации, второй выход которого соединен с выходной шиной синхронизации и четырнадцатым входом блока формирования отсчетов, третий выход которого является первой выходной шиной измерителя, второй, третьей, четвертой выходными шинами которого являются соответственно первый, второй, третий выходы блока хранения ин0 формации.

5 памяти, два дешифратора, линию задержки, элемент ИЛИ, умножитель/сумматор, элемент НЕ, причем первый вход генератора соединен с входом генератора тактовых импульсов, второй вход генератора соединен с

0 вторым входом элемента ИЛИ, выход генератора тактовых импульсов соединен с С- входом первого D-триггера и К-ми входами первого и второго дешифраторов, Q-выходы каждого из -К D-триггеров соединены с D5 входами регистра памяти и 1.2(К-1)м

входами первого и второго дешифраторов, Q-выход каждого 1,2,...,(К-1)-го D-триггеров соединен с D-аходом этого же D-триггера и входом С следующего D-триггера, Q-выход

0 К-го D-триггера соединен с его D-входом, выход первого дешифратора соединен с R- входом RS-триггера и четвертым выходом генератора, выход-второго дешифратора соединен с входами элемента НЕ и линии за5 держки, первый выход линии задержки соединен с первым входом элемента ИЛИ, второй выход линии задержки соединен с вторым выходом генератора, выход элемента ИЛИ соединен с R-входами каждого из К

0 D-триггеров, регистра памяти и S-входом RS-триггера, Q-выход RS-триггера соединен с первым выходом генератора, выход элемента НЕ соединен с входом С регистра памяти, Q-выходы регистра памяти соеди5 нены с Х-входами умножителя/сумматора, на Y-входах умножителя/сумматора монтажным.путем установлен двоичный код периода тактовых импульсов, выход умножителя/сумматора соединен с третьим

0 выходом генератора управляющих сигналов.

соединен с входом формирователя коротких импульсов, третий вход блока соединен с Y-входом умножителя/сумматора, пятый ,вход блока соединен с четвертым и седьмым входами элемента 3-ЗИ-ЗИЛИ, четвертый, шестой, седьмой, девятый и десятый входы блока соединены соответственно с первым, пятым, шестым, восьмым и девятым входами элемента 3-ЗИ-ЗИЛИ, восьмой вход блока соединен с вторым входом элемента ИЛИ, одиннадцатый вход блока соединен с R-входами первого и второго регистров памяти и вторым R-входом двоичного счетчика, двенадцатый вход блока соединен с входом С второго регистра памяти, тринадцатый вход блока соединен с первым и вторым W-входами оперативного запоминающего устройства, четырнадцатый вход блока соединен с первым R-входом двоичного счетчика, Q-выходы первого регистра памяти соединены с Х-входом умножителя/сумматора и вторым D-входом оперативного запоминающего устройства, выход умножителя/сумматора соединен с первым D-входом оперативного запоминающего устройства, выход элемента 3-ЗИ-ЗИЛИ соединен с первыми А-входами оперативного запоминающего устройства, выход формирователя коротких импульсов соединен с входом С первого регистра памяти и первым входом элемента ИЛИ, выход которого соединен с входом С двоичного счетчика, Q-выходы двоичного счетчика соединены с D-входами второго регистра памяти, с вторыми А-входами оперативного запоминающего устройства и вторым входом элемента 3-ЗИ-ЗИЛИ, первый выход оперативного запоминающего устройства соединен с первым выходом блока, второй выход оперативного запоминающего устройства соединен с третьим выходом блока, Q-выходы второго регистра памяти соединены с вторым выходом блока,

двоичного счетчика, третий вход блока соединен с В-входами второго и третьего элементов сравнения, выход первого элемента ИЛИ соединен с R-входом первого RS-триг- 5 гера, выход второго элемента ИЛИ соединен с S-входом второго RS-триггера, выход третьего элемента ИЛИ соединен с R-входом второго RS-триггера, выход четвертого элемента ИЛИ соединен с R-входом третье0 го RS-триггера, выход пятого элемента ИЛИ соединен с R-входом четвертого RS-триггера, выход элемента 4И-НЕ соединен с S- входом четвертого RS-триггера, Q-выход первЭго RS-триггера соединен с первым вы-.

5 ходом блока и входом генератора тактовых импульсов, Q-выход второго RS-трипгера соединен с первым, третьим и пятым входами элемента 3-2И-НЁ, Q-выход второго RS- триггера соединен с первым входом элемен0 та 4И-НЕ, Q-выход третьего RS-триггера соединен с первым входом элемента 2-2И, вторым входом элемента 2-2И-2ИЛИ, третьим входом первого формирователя коротких импульсов и десятым выходом блока,

5 б-выход третьего RS-триггера соединен с вторым входом элемента 4И-НЕ, первым и пятым входами элемента 2-ЗИ, Q-выход четвертого RS-триггера соединен с третьим входом элемента 2-2И, четвертым входом

0 элемента 2-2И-2ИЛИ, одиннадцатым выходом блока и третьим входом второго форми- роваетля коротких импульсов, Q-выход четвертого RS-триггера соединен с четвертым входом элемента 4И-НЕ и третьим и

5 шестым входами элемента 2-ЗИ, выход генератора тактовых импульсов соединен с входом С распределителя импульсов, второй, третий и четвертый выходы распределителя импульсов соединены соот0 ветственно с вторым, четвертым и шестым иходами элемента 3-2И-НЕ, пятый выход распределителя импульсов соединен с вторым и четвертым входами элемента 2-2И, шестой выход распределителя коротких им5 пульсов соединен с первым входом первого формирователя коротких импульсов, седьмой выход распределителя импульсов соединен с первым и третьим входами элемента 2-2И-2ИЛИ, восьмой выход.рас0 пределителя импульсов соединен с вторым выходом блока выбора адресов, девятый выход распределителя импульсов соединен с четвертым входом элемента 2-ЗИ, десятый выход распределителя импульсов соединен

5 с первым входом элемента 2-2И-НЕ, одиннадцатый выход распределителя импульсов соединен с вторым входом элемента 2-ЗИ и третьим входом элемента 2-2И-НЕ, двенадцатый выход распределителя импульсов соединен с третьим входом элемента 4И-НЕ,

первый выход элемента 3-2И-НЕ соединен с входом С двоичного счетчика, второй выход элемента 3--2И-НЕ соединен с входами С первого и второго двоичных реверсивных счетчиков, третий выход элемента 3-2И-НЕ соединен с вторым входом третьего элемента ИЛИ и S-входом третьего RS-триггера, первый выход элемента 2-2И соединен с входом -1 первого двоичного реверсивного счетчика, второй выход элемента 2-2И соединен с входом +1 второго двоичного реверсивного счетчика, Q-выходы первого двоичного реверсивного счетчика соединены с А-входами первого элемента сравнения и двенадцатым выходом блока, Q-выходы второго двоичного реверсивного счетчика соединены с А-входами второго элемента сравнения и тринадцатым выходом блока, Q-выходы двоичного счетчика соединены с D-входами первого и второго двоичных реверсивных счетчиков, А-входами третьего элемента сравнения и девятым выходом блока, на В-вход первого элемента сравнения монтажным путем подан двоичный кодО...О, выход А В первого элемента сравнения соединен с вторым входом первого формирователя коротких импульсов, выход первого формирователя коротких импульсов соединен с вторым входом четвертого элемента -ИЛИ, выход А В второго элемента сравнения соединен с вторым входом второго формирователя коротких импульсов, вторым и четвертым входами элемента 2-2И-НЕ, выход второго формирователя коротких импульсов соединен с вторыми входами второго и пятого элементов ИЛИ, а первый вход формирователя коротких импульсов соединен с одиннадцатым выходом распределителя импульсов, выход А В третьего элемента сравнения соединен с вторым входом третьего формирователя коротких импульсов, первый вход третьего формирователя коротких импульсов соединен с третьим выходом распреде- лителя импульсов, выход третьего формирователя коротких импульсов соединен с вторым входом первого элемента ИЛ И и восьмым выходом блока, выход элемента 2-2И-2ИЛИ соединен с третьим выходом блока, первый и второй выходы элемента 2-ЗИ соединены соответственно с четвертым и пятым выходами блока, .первый и второй выходы элемента 2-2И-НЕ соединены соответственно с шестым и седьмым выходами блока.

элементов 2И-НЕ, группу элементов ИЛИ, элемент ИЛИ, двоичный счетчик, регистр памяти и элемент НЕ, причем первый вход блока соединен с входами X умножителя/сумматора, второй вход блока соединен с входом С накапливающего сумматора, третий вход блока соединен с входом элемента НЕ, четвертый вход блока соединен с входом С двоичного счетчика, пятый вход

0 блока соединен с вторым входом элемента ИЛИ, шестой вход блока соединен с входом С регистра памяти, седьмой вход блока соединен с вторым R-входом регистра памяти, выход двоичного счетчика соединен с Y-вхо5 дом умножителя/сумматора, входы So, Si, 82, Зз, М арифметическо-логического устройства соединены монтажным путем на операцию вычитания, выход умножителя/сумматора соединен с входом А накап0 ливающего сумматора, выход накапливающего сумматора соединен с входами А арифметическо-логического устройства и D- регистра памяти, выход элемента НЕ соединен с первым входом элемента ИЛИ,

5 первым входом R накапливающего сумматора и первым R-входом регистра памяти, выход элемента ИЛИ соединен с R-входом двоичного счетчика и вторым входом R накапливающего сумматора, выход регистра

0 памяти соединен с входами В арифметическо-логического устройства, выход С4 арифметическо-логического устройства соединен с входом Сп арифметическо-логического устройства и первыми входами групп

5 элементов 2И и 2И-НЕ, выход F арифметическо-логического устройства соединен с вторыми входами групп элементов 2И и 2И- НЕ, выходы группы элементов 2И соединены с первым входами группы элементов

0 ИЛИ, выходы группы элементов 2И-НЕ соединены с вторыми входами группы элементов ИЛИ, выходы группы элементов ИЛИ соединены с шиной выхода блока.

0 вход блока соединен с D-входами первого регистра памяти и первыми входами элемента 2-2И-2ИЛИ, второй вход блока соединен с первым входом элемента И и W-входом оперативного запоминающего

5 устройства, третий вход блока соединен с входом RO первого регистра памяти и входом Rg второго регистра памяти, четвертый вход блока соединен с D-входами второго регистра памяти и оперативного запоминающего устройства и входом А элемента

сравнения, пятый вход блока соединен с вторыми входами элемента 2-2И-2ИЛИ, шестой вход блока соединен с третьими входами элемента 2-2И-2ИЛИ, седьмой вход блока соединен с четвертыми входами эле- мента 2-2И-2ИЛИ. выход элемента И соединен с входами С первого и второго регистров памяти, выход первого регистра памяти соединен с первым выходом блока, выход второго регистра памяти соединен с входом В элемента сравнения и вторым выходом блока, выход А В элемента сравнения соединен с вторым входом элемента И, выход элемента 2-2И-2ИЛИ соединен с входом А оперативного запоминающего ус- тройства, выход оперативного запоминающего устройства соединен с третьим выходом блока.

импульсов и элемент ИЛИ, причем первый вход блока соединен с S-входом RS-тригге- ра и первым входом элемента ИЛИ, второй вход блока соединен с R-входом RS-тригге- ра и первым входом элемента ИЛИ-НЕ. третий вход блока соединен с входом В элемента сравнения, выход Q RS-триггера соединен с входом генератора тактовых импульсов и третьим выходом блока, выход генератора тактовых импульсов соединен с входом С двоичного счетчика и четвертым выходом блока, выход двоичного счетчика соединен с входом А элемента сравнения и первым выходом блока, выход А В элемента сравнения соединен с входом формирователя коротких импульсов, выход формирователя коротких импульсов соединен с вторыми входами элементов ИЛИ и ИЛИ-НЕ, выход элемента ИЛИ-НЕ соединен с R-входом двоичного счетчика, выход элемента ИЛИ соединен с вторым выходом блока.

Фиг.1

г

D

Uff

7 1fi

- 4lЈr|

un

D

R

l

П

U7

|

as...

US

Un

ЙЕУ

«

йяр

1

Ж

22

J

Шаг

z.J

О

ю

1Л СО

«Ч

a- to«о

{

г

Фиг. 8

Фиг.9

Фиг. И

а

t «ft 0 Ь 33 3 3 3

3 3 3 . 3 П. 3 3 3

$

§Ш 111

Ј

esj

g

Й 3

к. и

и 5 5

з а зз

3 3

,{4J}j.1,M/

I

a ioi{sjYw,$mi«,jmiii /

:№ue.1S

±

z«0,/«/-/

r Z +iA-j i

,

&r fi-jJAi

Jy.-ir-I l J J+1SmlflsSj,JffiiftsJ

±

| Формирователь центра тяжести импульсов | 1983 |

|

SU1129581A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Устройство для определения центра тяжести повторяющихся импульсов | 1981 |

|

SU1013905A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-03-30—Публикация

1990-01-23—Подача