Изобретение относится к радиотехнике и может быть использовано в радиоприемных и радиопередающих устройствах для формирования сетки частот.

Цель изобретения - уменьшение паразитной фазовой модуляции выходного сигнала.

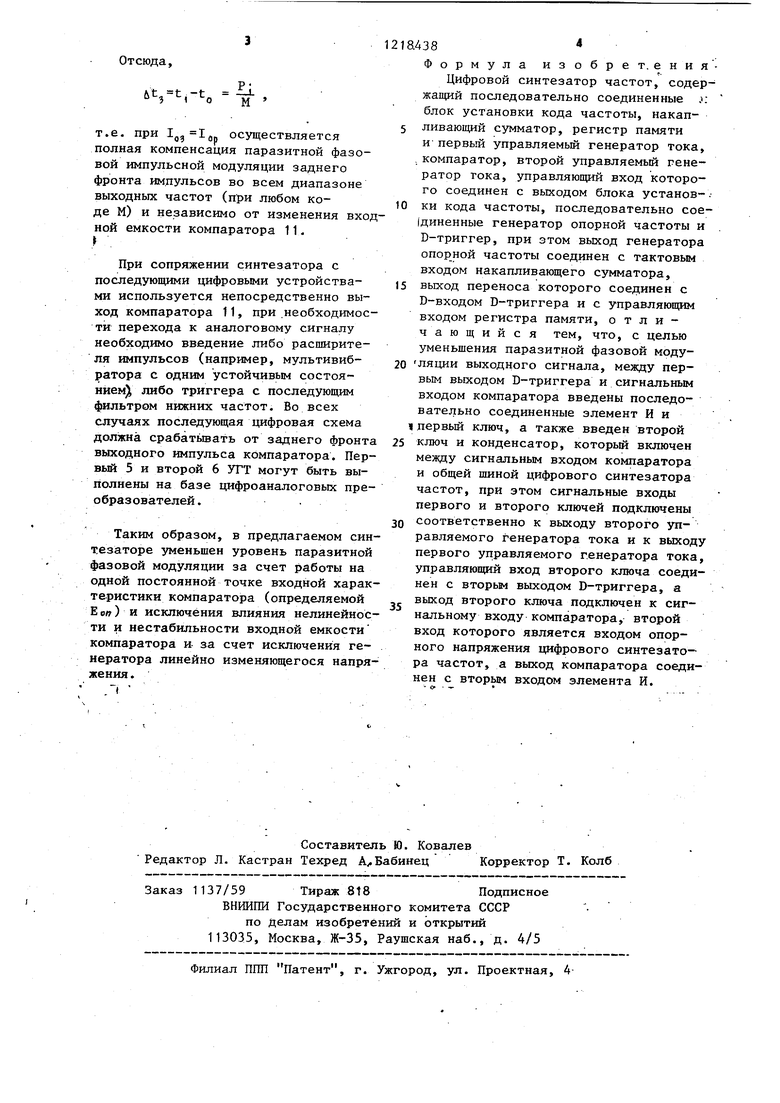

На чертеже представлена структурная электрическая схема цифрового синтезатора частот.

Цифровой синтезатор частот содержит генер4тор 1 опорной частоты (ГОЧ блок 2 установки кода частоты, накапливающий сумматор 3, регистр 4 памяти, первьй 5 и второй 6 управляге мые генераторы тока (УГТ), D-триг- гер 7, первый ключ 8, второй ключ 9, конденсатор 10, компаратор 11 и элемент И 12.

Цифровой синтезатор частот работает следующим образом.

Код требуемой выходной частоты М с выхода блока 2 установки кода частоты поступает на накапливакнций сумматор 3, имеющий емкость N, и

на входы второго УГТ 6. .1. .

С частотой следования импульсов на выходе ГОЧ 1 в накапливающем сумматоре 3 осуществляется сложение накопленного числа с числом М. Через К периодов ГОЧ 1 происходит переполнение накапливающего сумматора 3, на его выходе переполнения появляется импульс, который поступает на управляющий вход регистра 4 памяти и на D-вход D-триггёра 7, В регистр памяти 4 переписывается код числа PI , оставшегося в накап- ливакщем сумматоре 3 после его переполнения . После прихода следующего импульса с вькода ГОЧ 1 исчезает сигнал переполнения на выходе накапливающего сумматор 3, а на выходе D-триггера 7 возникает импульс, длительность которого равна периоду 1 следования импульсов на. выходе ГОЧ 1 Этот импульс открывает второй ключ 9 и в течение времени Т осуществляется заряд конденсатора 10 током первого УГТ 5, определяемого кодом на выходе регистра 4 памяти, т.е. числом р. . На выходе компаратора 11 начинается импульс, поступающий на второй вход элемента И 12. В момент появления второго импульса с выхода ГОЧ 1 заканчивается импульс на выходе D-триггера 7 и запирается

25

218438

второй ключ 9. Заряд конденсатора 10 прекращается. Одновременно на первом входе элемента И 12 возникает логическая 1, передающаяся на выход. 5 элемента И 12 и открьшающая первый ключ 8. Начинается разряд конденсатора 10 током второго УГТ 6, величина которого определяется числом М. Как только напряжение на конденса- 10 торе 10 достигает величины опорного напряжения Е, заканчивается импульс на выходе компаратора 11 и через элемент И 12 закрывается первый ключ 8. Разряд конденсатора 10 15 прекращается.

При следующем переполнении накапливающего сумматора 3 весь цикл повторяется. Различие заключается в другом токе заряда первого УГТ 5, 20 определяемом новым числом .

Число Р; определяет величину паразитной фазовой модуляции импульсов uCf| на выходе D-триггера 7

йср;

21( ii- К Т

вмх

которая приводит к временному сдвигу (в сторону опережения отнрситель- но гипотетической равномерной последовательности той же частоты) каждо- го выходного импульса на величину

it.

L .,. т i- т 27 i ebix М «

где Т..,., - период следования выходVO Д

ньпс импульсов.

Задержка At, окончания импульса на выходе компаратора 11 определяется из условия равенства напряжений при заряде

р. т .т

7Т Р О ди

и разряде конденсатора tO

Л7Т - М Ipf At

1 с

емкость конденсатора 10j токи генераторов первого 5 и второго 6 УГТ соответственно, при минимальных управляющих кодах (логическая единица только в младшем разряде).

Отсюда,

lf

т.е. при 1д 1

-op

осуществляется

полная компенсация паразитной фазовой импульсной модуляции заднего фронта импульсов во всем диапазоне выходных частот (при любом коде М) и независимо от изменения входной емкости компаратора 11. .

При сопряжении синтезатора с последующими цифровыми устройствами используется непосредственно выход компаратора 11, при необходимости перехода к аналоговому сигналу необходимо введение либо расширителя импульсов (например, мультивибратора с одним устойчивым состоянием либо триггера с последующим фильтром нижних частот. Во всех случаях последующая цифровая схема должна срабатьшать от заднего фронта выходного импульса компаратора. Первый 5 и второй 6 5ТТ могут быть выполнены на базе цифроаналоговых преобразователей.

Таким образом, в предлагаемом синтезаторе уменьшен уровень паразитной фазовой модуляции за счет работы на одной постоянной точке входной характеристики компаратора (определяемой Е Off) и исключения влияния нелинейности и нестабильности входной емкости компаратора и за счет исключения генератора линейно изменяющегося напряжения.

Составитель Ю. Ковалев Редактор Л. Кастран Техред А Бабинец Корректор Т. Колб

Заказ 1137/59 Тираж 818Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ПШТ Патент, г. Ужгород, ул. Проектная, 410

15

218.438

Формула изобрет. ения - Цифровой синтезатор частот, содержащий последовательно соединенные .; блок установки кода частоты, накап- 5 ливающий сумматор, регистр памяти

и первый управляемый генератор тока, . компаратор, второй управляемый генератор тока, управляющий вход которого соединен с выходом блока установ-. ки кода частоты, последовательно сое- (диненные генератор опорной частоты и D-триггер, при этом выход генератора опорной частоты соединен с тактовым входом накапливающего сумматора, выход переноса которого соединен с D-входом D-триггера и с управляющим входом регистра памяти, отличающийся тем, что, с целью уменьшения паразитной фазовой моду- ляции выходного сигнала, между пер- Bbw выходом D-триггера и сигнальным входом компаратора введены последовательно соединенные элемент И и I первый ключ, а также введен второй 25 ключ и конденсатор, который включен между сигнальным входом компаратора и общей шиной цифрового синтезатора частот, при этом сигнальные входы первого и второго ключей подключены соответственно к выходу второго управляемого генератора тока и к выходу первого управляемого генератора тока, управляющий вход второго ключа соединен с вторьм выходом D-триггера, а выход второго ключа подключен к сигнальному входу компаратора, второй вход которого является входом опорного напряжения цифрового синтезатора частот, а выход компаратора соединен с вторым входом элемента И.

20

30

35

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частот | 1985 |

|

SU1337989A1 |

| Цифровой синтезатор частот | 1987 |

|

SU1515336A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1990 |

|

RU2030829C1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1714784A1 |

| Цифровой синтезатор частоты прямого действия | 1989 |

|

SU1621170A2 |

| Цифровой синтезатор частот | 1989 |

|

SU1704265A1 |

| Цифровой синтезатор частот | 1986 |

|

SU1363426A1 |

| Цифровой синтезатор частот | 1981 |

|

SU978314A1 |

| Синтезатор частот | 1982 |

|

SU1061235A1 |

Изобретение относится к радиотехнике. Уменьшается паразитная фазовая модуляция выходного сигнала. Код требуемой выходной частоты М с блока 2 установки кода частоты посту- пает на накапливающий сумматор (НС) 3 и на второй управляемый генератор тока (УГГ) 6. По импульсам с генератора 1 опорной частоты происходит сложение накопленного в НС 3 числа с числом М. По импульсу переполнения с НС 3 код числа PJ, оставшегося в НС 3, переписывается в регистр памяти 4. С регистра памяти 4 число Р/, определяющее величину паразитной фазовой модуляции импульсов, поступает на первьй УГТ 5. После прекращения импульса переполнения D-триггер 7 формирует импульс , по которому открывается второй ключ 9. Через открытый ключ 9 током первого УГТ 5, оп- ределяемьм числом Pj , заряжается конденсатор 10. С выхода компаратора 11, подключенного к конденсатору 10, импульс поступает на выход и на элемент И 12. После запирания ключа 9 импульс с D-триггера 7 поступает на элемент И 12. Логическая 1 с его выхода сткрьшает ключ 8 и конденсатор 10 разряжается током второго УГТ 6, величина которого определяет- . ся числом М. При достижении напряжения на конденсаторе 10 величины опорного напряжения импульс компаратора 11 закончится и через элемент И 12 закроет ключ 8. 1 ил. - -

| Патент США № 3882403, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| Цифровой синтезатор частот | 1981 |

|

SU978314A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-03-15—Публикация

1984-12-17—Подача