Изобретение относится к радиотехнике и может быть использовано для синтеза частот в радиопередающих и радиоприемных устройствах, а также в измерительной технике.

Цель изобретения - снижение побочных составляющих в спектре выходного сигнала синтезатора частот.

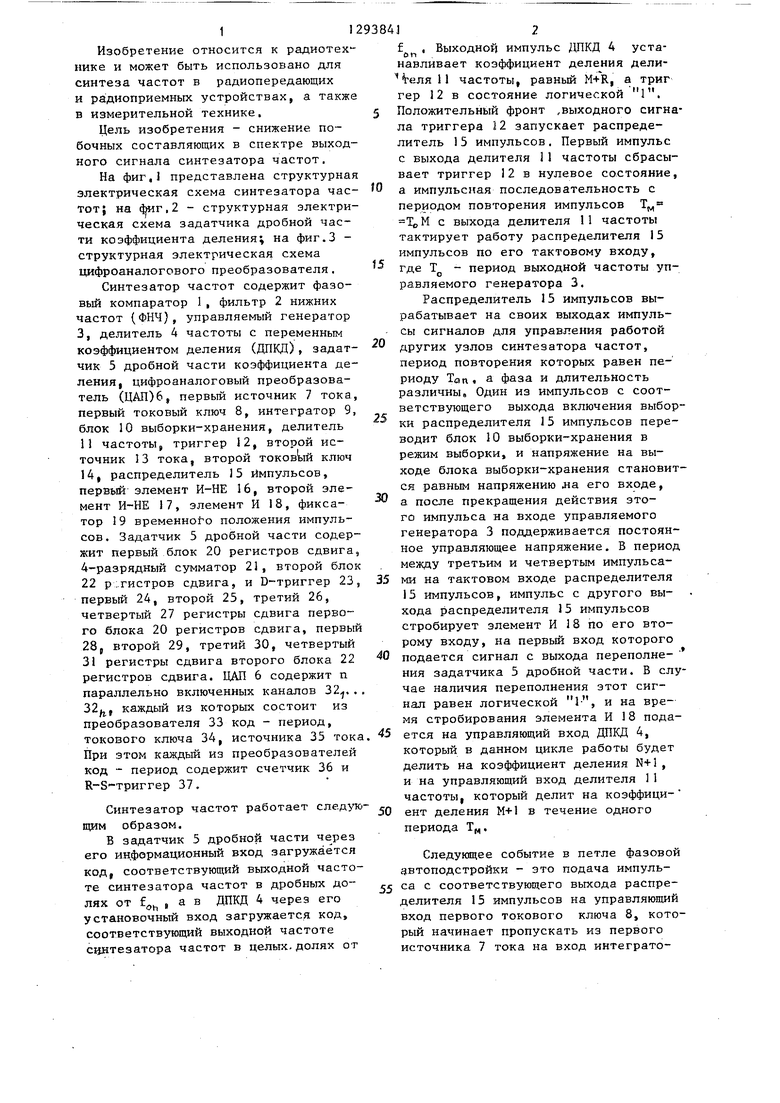

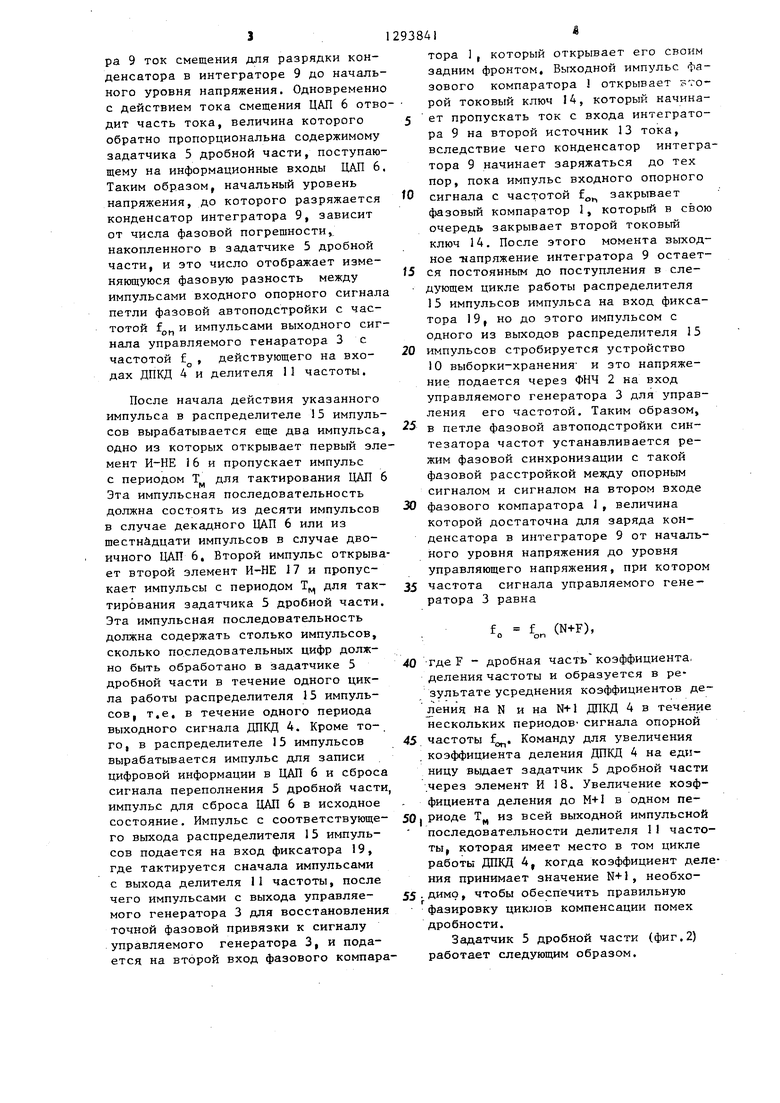

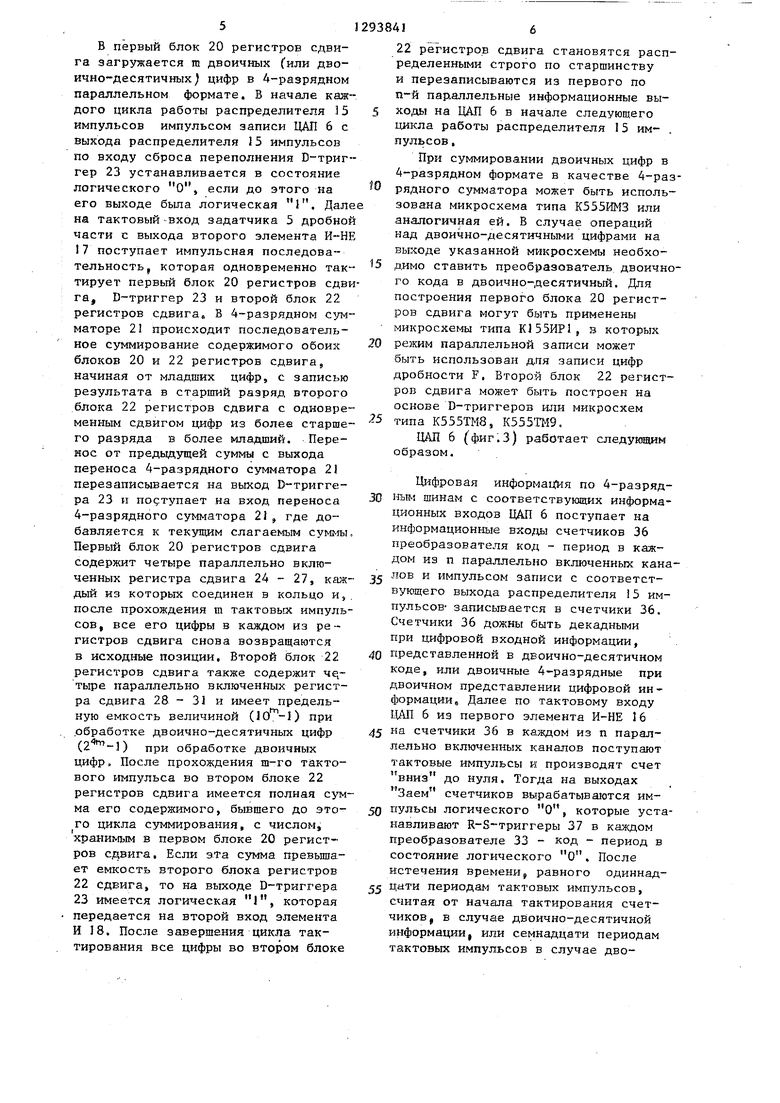

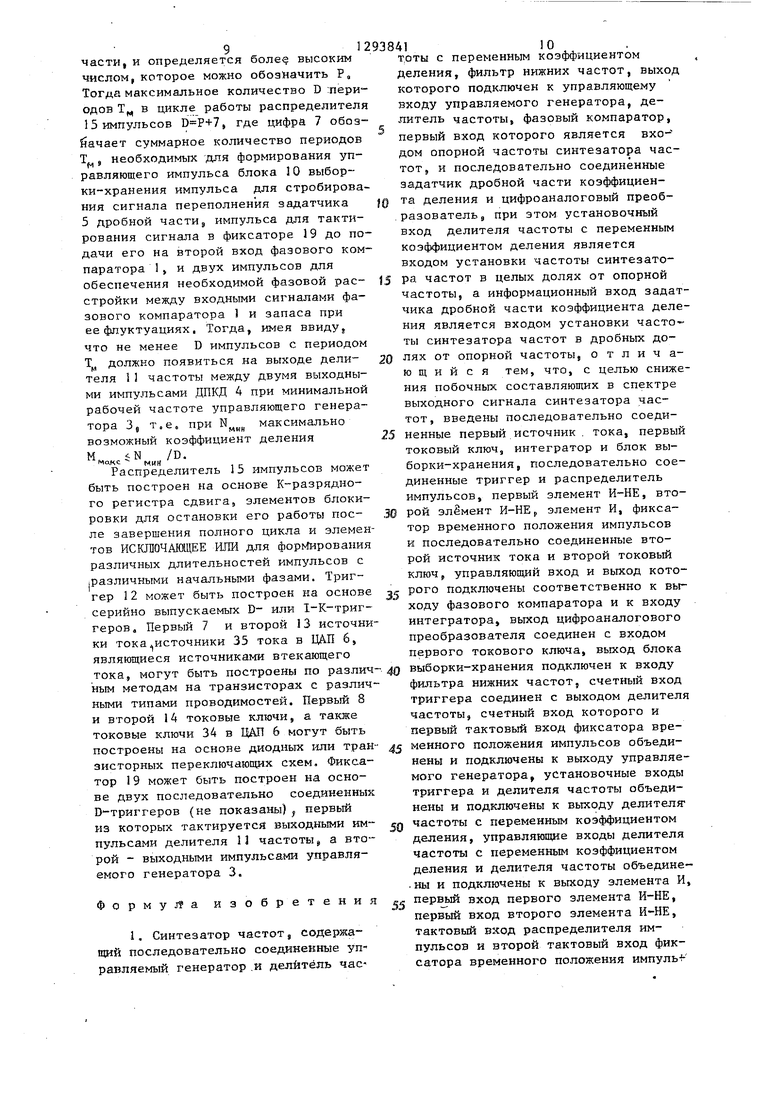

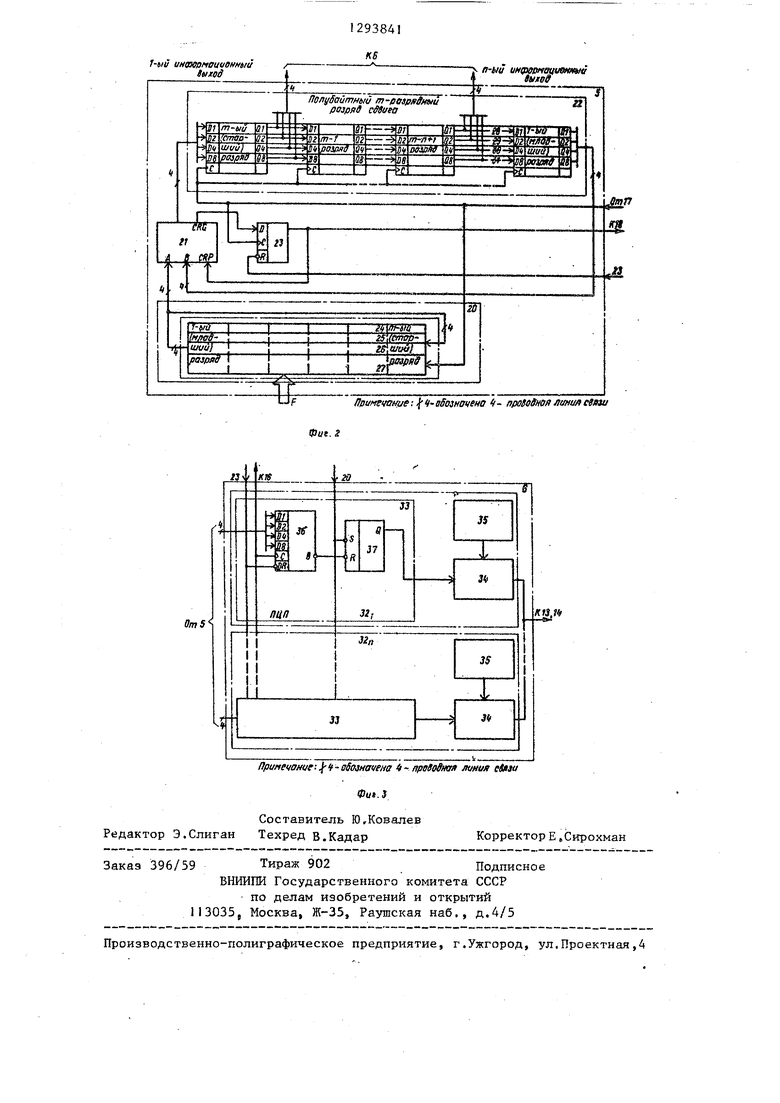

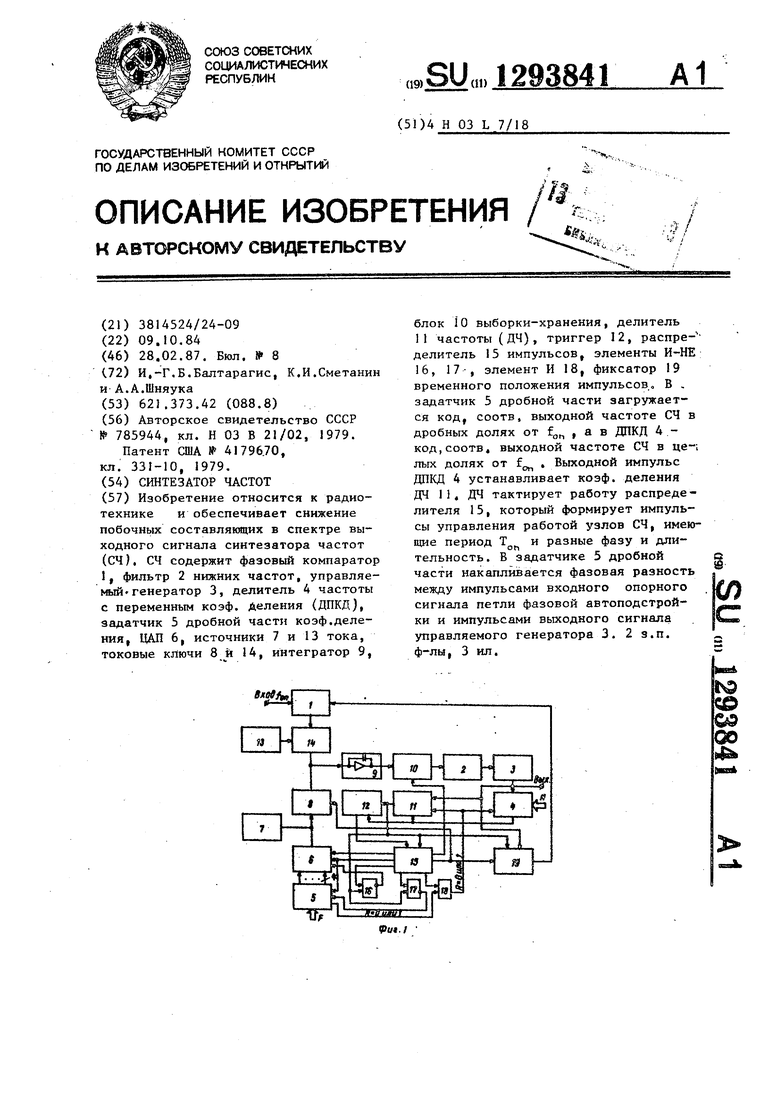

На фиг,1 представлена структурная электрическая схема синтезатора частот; на фиг,2 - структурная электрическая схема задатчика дробной части коэффициента деления на фиг.З - структурная электрическая схема цифроаналогового преобразователя.

Синтезатор частот содержит фазовый компаратор 1, фильтр 2 нижних частот (ФНЧ), управляемый генератор 3, делитель 4 частоты с переменным коэффициентом деления (ДПКД), задат- чик 5 дробной части коэффициента деления, цифроаналоговый преобразователь (ЦА11)6, первый источник 7 тока, первый токовый ключ 8, интегратор 9, блок 10 выборки-хранения, делитель П частоты, триггер J2, второй источник 13 тока, второй ТОКОВ1ЫЙ ключ 14, распределитель 15 импульсов, первый элемент И-НЕ 16, второй элемент И-НЕ 17, элемент И 18, фиксатор 19 временного положения импульсов. Задатчик 5 дробной части содержит первый блок 20 регистров сдвига, 4-разрядный сумматор 21, второй блок 22 р :.гистров сдвига, и D-триггер 23, первый 24, второй 25, третий 26, четвертый 27 регистры сдвига первого блока 20 регистров сдвига, первый 28( второй 29, третий 30, четвертый 31 регистры сдвига второго блока 22 регистров сдвига. ЦАП 6 содержит п параллельно включенных каналов 32, . 32, каждый из которых состоит из преобразователя 33 код - период, токового ключа 34, источника 35 тока При этом каждый из преобразователей код - период содержит счетчик 36 и R-S -триггер 37.

Синтезатор частот работает следующим образом.

В задатчик 5 дробной части его информационный вход загружается код, соответствующий выходной частоте синтезатора частот в дробных долях от f , а в ДПКД 4 через его установочный вход загружается код, соответствующий выходной частоте синтезатора частот в целых.долях от

5

0

5

f, . Выходной импульс ДПКД 4 устанавливает коэффициент деления дели- еляП частоты, равный , а триг гер 12 в состояние логической 1. Положительный фронт ,выходного сигнала триггера 12 запускает распределитель 15 импульсов. Первый импульс с выхода делителя 11 частоты сбрасывает триггер 12 в нулевое состояние, а импульсная последовательность с периодом повторения импульсов ТоМ с выхода делителя 11 частоты тактирует работу распределителя 15 импульсов по его тактовому входу, где Т - период выходной частоты управляемого генератора 3.

Распределитель 15 импульсов вырабатывает на своих выходах импульсы сигналов для управления работой других узлов синтезатора частот, период повторения которых равен периоду Теп. а фаза и длительность различны. Один из импульсов с соответствующего выхода включения выборки распределителя 15 импульсов переводит блок 10 выборки-хранения в режим выборки, и напряжение на выходе блока выборки-хранения становится равным напряжению ла его входе, а после прекращения действия этого импульса на входе управляемого генератора 3 поддерживается постоянное управляющее напряжение. В период между третьим и четвертым импульсами на тактовом входе распределителя 15 импульсов, импульс с другого выхода распределителя 15 импульсов стробирует элемент И 18 по его второму входу, на первый вход которого

0 подается сигнал с выхода переполнения задатчика 5 дробной части. В случае наличия переполнения этот сигнал равен логической , и на время стробирования элемента И 18 пода5 ется на управляющий вход ДПКД 4,

который в данном цикле работы будет делить на коэффициент деления N-fl , и на управляющий вход делителя 11 частоты, который делит на коэффици- ент деления М+1 в течение одного периода Т„.

0

5

0

Следующее событие в петле фазовой автоподстройки - это подача импуль- 55 са с соответствующего выхода распределителя 15 ж мпульсов на управляющий вход первого токового ключа 8, который начинает пропускать из первого источника 7 тока на вход интеграто3

pa 9 ток смещения для разрядки конденсатора в интеграторе 9 до начального уровня напряжения. Одновременн с действием тока смещения ЦАП 6 отвдит часть тока, величина которого обратно пропорциональна содержимому задатчика 5 дробной части, поступающему на информационные входы ЦАП 6 Таким образом, начальный уровень напряжения, до которого разряжается конденсатор интегратора 9, зависит от числа фазовой погрешности,, накопленного в задатчике 5 дробной части, и это число отображает изменяющуюся фазовую разность между импульсами входного опорного сигнал петли фазовой автоподстройки с частотой fj, и импульсами выходного сигнала управляемого генаратора 3 с

частотой f

действующего на входах ДПКД 4 и делителя 11 частоты.

После начала действия указанного импульса в распределителе 15 импульсов вырабатывается еще два импульса, одно из которых открывает первый элемент И-НЕ 16 и пропускает импульс с периодом Т| для тактирования ЦАП 6 Эта импульсная последовательность должна состоять из десяти импульсов в случае декадного ЦАП 6 или из шестнадцати импульсов в случае двоичного ЦАП 6, Второй импульс открывает второй элемент И-НЕ 17 и пропускает импульсы с периодом Т для тактирования задатчика 5 дробной части. Эта импульсная последовательность должна содержать столько импульсов, сколько последовательных цифр должно быть обработано в задатчике 5 дробной части в течение одного цикла работы распределителя 15 импульсов, т.е. в течение одного периода выходного сигнала ДПКД 4. Кроме то-, го, в распределителе 15 импульсов вырабатывается импульс для записи цифровой информации в ЦАП 6 и сброса сигнала переполнения 5 дробной части импульс для сброса ЦАП 6 в исходное состояние. Импульс с соответствующего выхода распределителя 15 импульсов подается на вход фиксатора 19, где тактируется сначала импульсами с выхода делителя 11 частоты, после чего импульсами с выхода управляемого генератора 3 для восстановления точной фазовой привязки к сигналу управляемого генератора 3, и подается на второй вход фазового компараO

тора 1 , который открывает его своим задним фронтом. Выходной импульс Фазового компаратора открывает второй токовый ключ 14, который начинает пропускать ток с входа интегратора 9 на второй источник 13 тока, вследствие чего конденсатор интегратора 9 начинает заряжаться до тех пор, пока импульс входного опорного сигнала с частотой f закрывает

5

фазовый компаратор 1, который в свою очередь закрывает второй токовьтй ключ 14. После этого момента выходное напряжение интегратора 9 остается постоянньм до поступления в сле- дующем цикле работы распределителя 15 импульсов импульса на вход фиксатора 19, но до этого импульсом с одного из выходов распределителя 15

0 импульсов стробируется устройство 10 выборки-хранения- и это напряжение подается через ФНЧ 2 на вход управляемого генератора 3 для управления его частотой. Таким образом,

в петле фазовой автоподстройки синтезатора частот устанавливается режим фазовой синхронизации с такой фазовой расстройкой между опорным сигналом и сигналом на втором входе

0 фазового компаратора 1, величина которой достаточна для заряда конденсатора в интеграторе 9 от начального уровня напряжения до уровня управляющего напряжения, при котором

5 частота сигнала управляемого генератора 3 равна

fo

fon ()

где F - дробная часть коэффициента, деления частоты и образуется в результате усреднения коэффициентов деления на N и на N+1 ДПКД 4 в течение нескольких периодов сигнала опорной

частоты f. Команду для увеличения коэффициента деления ДПКД 4 на единицу выдает задатчик 5 дробной части .через элемент И 18. Увеличение коэффициента деления до М+1 в одном периоде Т из всей выходной импульсной последовательности делителя 11 частоты, которая имеет место в том цикле работы ДПКД 4, когда коэффициент деления принимает значение N+1, необхоДимо, чтобы обеспечить правильную фазировку циклов компенсации помех дробности.

Задатчик 5 дробной части (фиг.2) работает следующим образом.

в первый блок 20 регистров сдвиа загружается m двоичных (или двочно-десятичных) цифр в 4-разрядном араллельном формате, В начале кажого цикла работы распределителя 15 мпульсов импульсом записи ЦАП 6 с ыхода распределителя 15 импульсов о входу сброса переполнения D-триг- гер 23 устанавливается в состояние огического О, если до этого на его выходе была логическая }, Далее на тактовый вход задатчика 5 дробной асти с выхода второго элемента I7 поступает импульсная последовательность которая одновременно тактирует первый блок 20 регистров сдвига, В триггер 23 и второй блок 22 регистров сдвигав В 4-разрядном сумматоре 21 происходит последовательное суммирование содержимого обоих блоков 20 и 22 регистров сдвига, начиная от младших цифр, с записью результата в старший разряд второго блока 22 регистров сдвига с одновременным сдвигом цифр из более старшего разряда в более младший. Перенос от предыдущей суммы с выхода переноса 4-разрядного сумматора 2 перезаписывается на выход D-тригге- ра 23 и поступает на вход переноса 4-разрядного сумматора 21, где добавляется к текущим слагаемь м суммы. Первый блок 20 регистров сдвига содержит четыре параллельно включенных регистра сдвига 24 - 27, каждый из которых соединен в кольцо и,. после прохождения m тактовых импульсов, все его цифры в каждом из регистров сдвига снова возвращаются в исходные позиции. Второй блок 22 регистров сдвига также содержит тыре параллельно включенных регистра сдвига 28-3 и имеет предельную емкость величиной (10.-I) при обработке двоично-десятичных цифр () при обработке двоичных цифр, После прохождения ш-го тактового импульса во втором блоке 22 регистров сдвига имеется полная сумма его содержимого, бьшщего до этого цикла сз мирования, с числом, хранимым в первом блоке 20 регистров сдвига. Если э.та сумма превьшга- ет емкость второго блока регистров

22сдвига, то на выходе D-триггера

23имеется логическая J, которая передается на второй вход элемента

И 18. После завершения цикла тактирования все цифры во втором блоке

10

938416

22 регистров сдвига становятся распределенными строго по старшинству и перезаписываются из первого по п-й параллельные информационные вы- 5 ходы на ЦАП 6 в начале следующего цикла работы распределителя 15 им- . пульсов,

При суммировании двоичных цифр в 4-разрядном формате в качестве 4-разрядного сумматора может быть использована микросхема типа К555ИМЗ или ан.злогичная ей. В случае операций над двоично-десятичными цифрами на выходе указанной микросхемы необходимо ставить преобразователь двоичного кода в двоично-десятичный. Для построения первого блока 20 регистров сдвига могут быть применены микросхемы типа К155ИР1, з которых режим параллельной записи может быть использован д,гтя записи цифр дробности F, Второй блок 22 регистров сдвига может быть построен на основе D-триггеров или микросхем типа К555ТМ8, К555та9.

ЦАП 6 (фиг.З) работает следуюи№1м образом.

15

20

25

Цифровая информагХМя по 4-разрядШ1м шинам с соответствующих информационных входов ЩШ 6 поступает на информационные вкода счетчиков 36 преобразователя код - период в каждом из п пара,плельно включенных каналов и импульсом записи с соответствующего выхода распределителя 15 импульсов- записывается в счетчики 36. Счетчики 36 дожны быть декадными при цифровой входной информации,

представленной в двоично-десятичном коде, или двоичные 4-разрядные при двоичном представлении цифровой информации. Далее по тактовому входу ЦАП 6 из первого элемента И-НЕ 16

на счетчики 36 в каждом из п параллельно включенных каналов поступают тактовые импульсы и производят счет вниз до нуля. Тогда на выходах Заем счетчиков вырабатываются импульсы логического О, которые устанавливают R-S-триггеры 37 в каждом преобразователе 33 - код - период в состояние логического О. После истечения времени, равного одиннадцати периодам тактовых импульсов, считая от начгша тактирования счетчиков, в случае двоично-десятичной информации, или семнадцати периодам тактовых импульсов в случае двоичной информации, распределитель 15 импульсов на одном из своих выходов Вырабатывает импульс логического О, который по входу сброса ЦАП 6 .устанавливает R-S-триггары 37 во преобразователях 33 код - период соответственно в состояние логическая. Таким образом на выходах R-S-триггеров 37 вырабатываются импульсы, длительность которых обратно пропорциональна величине чисел, записанных на информационных входах ЦАП 6 Например,в случае записи в двоично- десятичной форме цифры 7 длитель ность выходного импульса R-S-тригге- ра 37 будет равна трем периодам входных тактовых импульсов, при цифре 1 - девяти периодам входных тактовых импульсов и т.п. На время действия этих выходных импульсов открываются токовый ключ 34 и источник 35 тока в каждом из параллельных каналов и отводят таким образом широтно-импульсно-модулиррванный ток от первого источника 7 и тем самым компенсируют фазовую погрешность с выхода фазового компаратора 1, Для обеспечения правильных весовых значений разрядов ЦАП 6 токи источника 35 тока в каждом из параллельно включенных каналов должны

соответствовать зависимости 1-

fj-tl

I. 10 для двоично-десятичной

входной цифровой информации или Ij 2 для двоичной А-разряд- ной входной информации каждого информационного входа ЦА.П 6, где j - номер любого 4-раэрядного входа (от 1 по п), Количество п входов в общем случае может быть равно числу цифр m в задатчике 5 дробной части. При большом количестве ш число п зависит от -требуемого уровня компенсации помех дробности и от точности и стабильности источников 35 тока, но обычно не превышает 5.

Численное соотношение величии токов второго источника 13 тока первого источника 7 и источников тока 35 в каждом из параллельно включенных каналов ЦДЛ 6 определяется по следующим соображениям. Врем, мя действия импульса смещения должно превышать максимальное время действия выходных токов ЦАП 6 из-за конечной длительности фронтов импульсов, но не менее два периода Т„ тактирующих импульсов распределителя 15 импульсов (один период Тц до вклю

чения токов ЦАП 6 и один период Т после выключения токов ЦАП 6). Если принять фазовую расстройку между входными сигналами фазового компаратора 1 на уровне одного периода Т| , то в установившемся режиме работы петли фазовой автоподстройки при отсутствии коррекции тока смещения со стороны ЦАП 6 .должно выполняться следующее условие:

I Т

В)

в

где I

В

-величина тока второго источника J3 тока;

-величина тока первого источника 7 тока;

-количество периодов Т в интервале действия .

Тогда 1о„ . Максимальная фазовая флуктуация выходного сигнала фазового компаратора равна периоду TO выходного сигнала управляемого генератора 3 в те моменты, когда коэффициент деления ДПКД 4 равен N+I, Для компенсации помеховой составляющей I -Т необходимо эквивао W о

лентное действие компенсирукяцего то-. ка н выходе ЦАП 6 в течение максимального периода действия этого тока, что можно выразить следующими равенетами: 1„ 1,Т,(;М-10 - для десятичного ЦАП; 1 Т I, T -M-ie- для двоичного ЦАП, где Т , 10 число периодов Т в течение максимального интервала, времени протекания компенсирукяцего тока для десятичного ЦАП; 16 - число периодов Т| в течение максимального интервала времени протекания компенсирующего тока для двоичного ЦАП. Отсюда

связь величины тока 1 и тока 1 i ч

.1, -о.

1д„,/10-М - для десятичного ЦАП; I /16-М - для двоичного ЦАП. Величина коэффициента деления М делителя частоты должна выбираться такой, чтобы количество импульсов на тактовом входе распределителя 15 импульсов в течение од,ного периода выходного импульса ДПКД 4 было дос- ;таточно для обеспечения требуемой длительности цикла работы распределителя J5 импульсов. Количество периодов Т в 191кле работы распределите-, ля 15 импульсов зависит от того, двоичные или двоично-десятичные цифры поступают на ЦАП 6„ также от числа m цифр в регистрах задатчика 5 дробной

TM теля

части, и определяется боле высоким числом, которое можно обоз-начить Ра Тогда максимальное количество D периодов Т„ в цикле работы распределителя 15 импульсов , где цифра 7 обоэ- йачает суммарное количество периодов Т. J необходимых для формирования управляющего импульса блока IО выборки-хранения импульса для стробирова- ния сигнала переполнения задатчика 5 дробной частиJ импульса для тактирования сигнала в фиксаторе 19 до подачи его на второй вход фазового компаратора 1, и двух импульсов для обеспечения необходимой фазовой расстройки между входными сигналами фазового компаратора 1 и запаса при ее флуктуациях. Тогда, имея ввиду, что не менее D импульсов с периодом должно появиться на выходе дели11 частоты между двумя выходными импульсами ДПКД 4 при минимальной рабочей частоте управляющего генератора 3| т.е. при N, максимально возможный коэффициент деления

М $N /D. - мик

Распределитель 1Ь импульсов может быть построен на основ е К-разрядно- го регистра сдвига, элементов блокировки для остановки его работы после завершения полного цикла и элементов ИСКЛЮЧАЩЕЕ ИЛИ для формирования различных длительностей импульсов с различными начальными фазами. Триггер 12 может быть построен на основе серийно выпускаемых D- или 1-К-триг- геров. Первый 7 и второй 13 источники тока источники 35 тока в ЦАП 6, являющиеся источниками втекающего тока, могут быть построены по различ ным методам на транзисторах с различными типами проводимостей. Первь Й 8 и второй 14 токовые ключи, а также токовые ключи 34 в ЦДЛ 6 могут быть

построены на основе диодных или тран- менного положения импульсов объедизисторных переключающих схем. Фиксатор 19 может быть построен на основе двух последовательно соединенных D-триггеров (не показаны), первый из которых тактируется выходными импульсами делителя П частотыj а второй - выходными импульсами управляемого генератора 3,

Ф о р м у J а

иены и подключены к выходу управляемого генератора, установочные входы триггера и делителя частоты объединены и подключены к выходу делителя J частоты с переменным коэффициентом деления, управляющие входы делителя частоты с переменным коэффициентом деления и делителя частоты объедине- .ны и подключены к выходу элемента И,

зобретения первый вход первого элемента И-НЕ,

первый вход второго элемента И-НЕ, тактовый вход распределителя импульсов и второй тактовый вход фиксатора временного положения импуль-f1, Синтезатор частот, содержащий последовательно соединенные уп равляемый генератор .и делитель час

29384 10

трты с переменным коэффициентом

деления, фильтр нижних частот, выход которого подключен к управляющему входу управляемого генератора, делитель частоты, фазовый компаратор, первый вход которого является вхо- дом опорной частоты синтезатора часзадатчик дробной части коэффициента деления и цифроаналоговый преоб- разователЬд при этом установочный вход делителя частоты с переменным коэффициентом деления является входом установки частоты синтезатора частот в целых долях от опорной частоты, а информационный вход задатчика дробной части коэффициента деления является входом установки частоты синтезатора частот в дробных долях от опорной частоты, отличающийся тем, что, с целью снижения побочных составляющих в спектре выходного сигнала синтезатора частот, введены последовательно соединенные первый источник . тока, первый токовый ключ, интегратор и блок выборки-хранения, последовательно соединенные триггер и распределитель импульсов, первый элемент И-НЕ, второй элемент И-НЕ р элемент И, фиксатор временного положения импульсов и последовательно соединенные второй источник тока и второй токовый ключ, управляюпц1й вход и выход которого подключены соответственно к выходу фазового компаратора и к входу интегратора, выход цифроаналогового преобразователя соединен с входом первого токового ключа, выход блока

выборки-хранения подключен к входу фильтра нижних частот, счетный вход триггера соединен с выходом делителя частоты, счетный вход которого и первый тактовый вход фиксатора вре

111

сов объединены и подключены к выходу делителя частоты, выход фиксатора временного положения импульсов соединён с сигнальным входом фазового компаратора, вход сброса переполнения задатчика дробной части коэф- фициента деления объединен с входом записи цифроаналогового преобразова т еля, тактовый вход и выход переполнения задатчика дробной части коэффициента деления подключены соответственно к выходу второго элемента И-НЕ и - к первому входу элемента И, выход, первого элемента И-НЕ соединен с тактовым входом цифроаналогового преобразователя, управляющий вход первого токового ключа объединен с сигнальным входом фиксатора временного положения импульсов, при этом входы сброса и записи цифроаналогового преобразователя, вторые входы первого и второго элементов И-НЕ, второй вход элемента И, управляющий вход первого токового ключа и управляю- щий вход блока -выборки-хранения подключены к соответствующим выходам распределителя импульсов.

2. Синтезатор поп.1, отличающийся тем, что задатчик дроб- ной части коэффициента деления содержит последовательно соединенные первый блок регистров сдвига, четырехразрядный сумматор и второй блок регистра сдвига, и D-триггер, D-вход которого соединен с выходом переноса четырехразрядного сумматора, тактовые входы D-триггера, первого и второго блоков регистров сдвига объединены и являются тактовым входом за- датчика дробной части коэффициента деления, выход D-триггера объединен с входом переноса черырехразрядного сумматора и является выходом переполнения задатчика дробной части коэффициента деления, R-вход ,D-триггера является входом сброса переполнения задатчика дробной части коэффициента деления, при этом каждый из блоков регистров сдвига вьтолнен в виде четырех параллельно включен

A1

2

ных регистров сдвига, выход младшего разряда каждого из четырех регистров сдвига первого блока регистров сдвига соединен с входом старшего разряда соответствующего из четырех регистров сдвига первого блока регистров сдвига, информационные входы первого блока регистров сдвига являются входами установки частоты синтезатора частот в дробных долях от опорной частоты, выход ()-го младщего разряда каждого из четырех регистров сдвига второго блока регистров сдвига соединен с соответствующим входом второй группы информационных входов четырехразрядного сумматора, а информационные выходы

0

5

0 5 0 5 0

с первого по п-и старщих разрядов каждого из четырех регистров сдвига второго блока регист1)ов сдвига являются информационными выходами

задатчика дробной части коэффициента деления,

3, Синтезатор по п.1, о т л и ч а- ю щ и и с я тем, что цифроаналого- вый преобразователь состоит из п параллельных включенных каналов каждый из которых состоит из последовательно соединенных преобразователя код - период, токового ключа и источника тока, выход которого соединен с информационным входом токового ключа, выходы токовых ключей каждого из п каналов объединены и являются выходом цифроаналогового преобразователя, кодовые входы преобразователей код - период каждого из п каналов являются информационными входами цифг роаналогового преобразователя, при этом тактовые входы преобразователя код - период каждого из п каналов объединены и являются тактовым входом цифроаналогового преобразователя, входы записи преобразователей код - период каждого из п каналов объединены и являются входом записи цифроаналогового преобразователя, а входы сброса преобразователей код период каждого из п каналов объединены и являются входом сброса цифро- аналогового преобразователя.

Притчате-}(- 1$оаначена npeSoSm линия flSus.J

Составитель Ю.Ковалев Редактор Э.Слиган Техред В.Кадар

Заказ 396/59 Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор Е .Сирохман

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1986 |

|

SU1394434A1 |

| Цифровой синтезатор частот | 1985 |

|

SU1252940A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Синтезатор частот | 1988 |

|

SU1656680A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

| Цифровой синтезатор частот | 1987 |

|

SU1515336A1 |

| Синтезатор частот | 1982 |

|

SU1084992A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1376221A1 |

Изобретение относится к радиотехнике и обеспечивает снижение побочных составляющих в спектре выходного сигнала синтезатора частот (СЧ), СЧ содержит фазовый компаратор 1, фильтр 2 нижних частот, управляе- Nfttfi генератор 3, делитель 4 частоты с переменным коэф. Деления (ДПКД), задатчик 5 дробной части коэф.деления, ЦАП 6, источники 7 и 13 тока, токовые ключи 8 jk 14, интегратор 9, блок 10 выборки-хранения, делитель 11 частоты (ДЧ), триггер 12, распре- делитель 15 импульсов, элементы И-НЕ 6, 17-, элемент И 18, фиксатор 19 временного положения импульсов., В , задатчик 5 дробной части загружается код, соотв. выходной частоте СЧ в дробньгх долях от fg , а в ДПКД 4.- код,соотв« выходной частоте СЧ в лых долях от fp . Выходной импульс ДПКД 4 устанавливает коэф. деления ДЧ 11, ДЧ тактирует работу распределителя 15, который формирует импульсы управления работой узлов СЧ, имеющие период Т и разные фазу и длительность. В задатчике 5 дробной части накаплй зается фазовая разность между импульсами входного опорного сигнала петли фазовой автоподстройки и импульсами выходного сигнала управляемого генератора 3. 2 з.п. ф-лы, 3 ил. (Л «

| Цифровой синтезатор частот | 1979 |

|

SU785944A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для центрального соединения между собой листов рессоры | 1933 |

|

SU41796A1 |

| Накладной висячий замок | 1922 |

|

SU331A1 |

Авторы

Даты

1987-02-28—Публикация

1984-10-09—Подача