(5) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частот | 1989 |

|

SU1714784A1 |

| Цифровой синтезатор частот | 1984 |

|

SU1197043A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1704265A1 |

| Цифровой синтезатор частот | 1987 |

|

SU1515336A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Синтезатор частот | 1986 |

|

SU1376242A1 |

| Цифровой синтезатор частот | 1984 |

|

SU1218438A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| Синтезатор частот | 1980 |

|

SU868973A1 |

| ИЗМЕРИТЕЛЬНЫЙ ГЕНЕРАТОР ПАРНЫХ ИМПУЛЬСОВ | 2022 |

|

RU2788980C1 |

1

Изобретение относится к радиотехнике и может использоваться при построении измерительных генераторов с малым уровнем побочных коле аний, а также в радиопередающих устройствах в качестве возбудителя или частотного манипулятора.

Известен синтезатор частот, содержащий последовательно соединенные генератор опорной частоты, D-триггер, генератор линейно изменяющегося напряжения, компаратор, триггер и фильтр нижних частот, а также последовательно соединенные блок установки кода частоты, накапливающий сумматор, регистр памяти и блок умножения-деления, а также первый цифроаналоговый преобразователь, поразрядные входы которого соединены с соответствующими поразрядными выходами блока установки кода частоты, и второй цифро-аналоговый преобразователь, выход которого соединен с другим входом компаратора, при этом

ВЫХОД генератора опорной частоты соединен с сигнальным входом накапливающего сумматора, дополнительный выход которого соединен с другим входом D-триггера и с управляющим входом регистра памяти 1.

Недостатком известного устройства является сложность устройства, поскольку блок умножения-деления представляет собой арифметическое

to устройство, выполняющее операции деления кода переполнения на число, соответствующее коду установленной частоты и умножение полученного частного на соответствующий коэффициент.

15 По объему оборудования блок умножения-деления наиболее сложный в синтезаторе.

Цель изобретения - упрощение синтезатора.

20

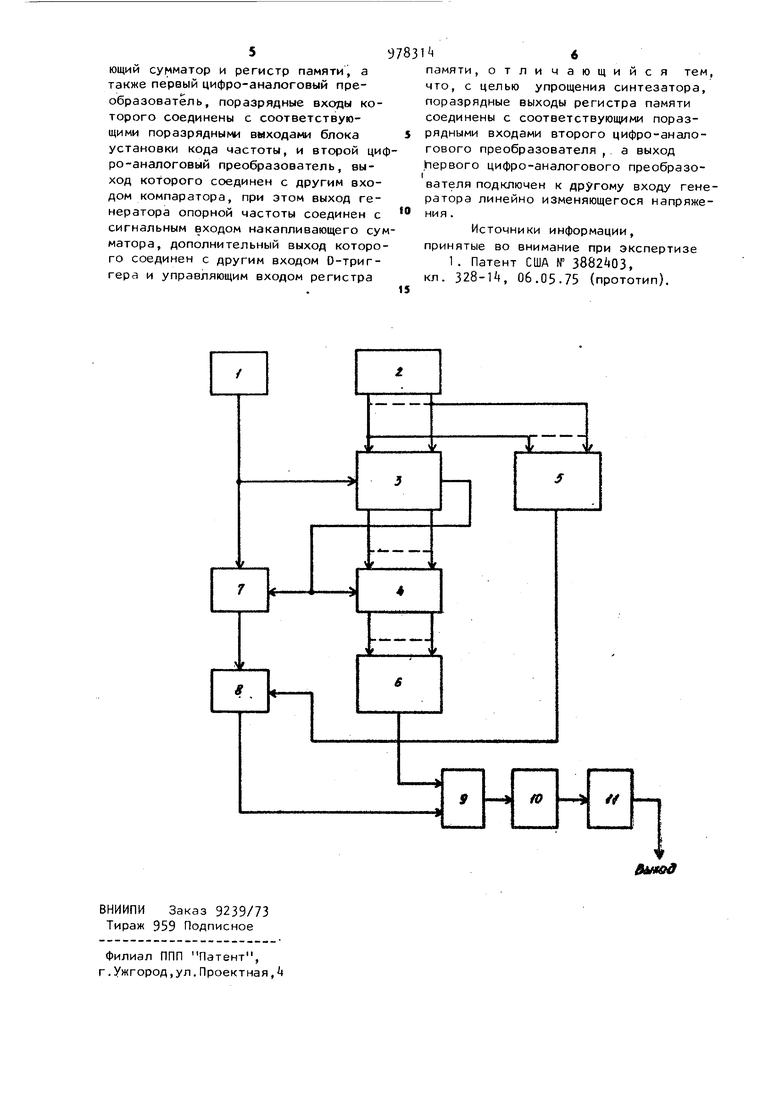

Поставленная цель достигается тем, что в цифровом синтезаторе уастот, содержащем последовательно соединенные генератор опорной частоты. iD-триггвр, генератор линейно изменяющегося напряжения, компаратор, триг гер и фильтр нижних частот, а также последовательно соединенные блок установки кода частоты, накапливающий сумматор и регистр памяти, а также первый цифро-аналоговый преобразователь, поразрядные входы которого со единены с соответствующими поразрядными выходами блока установки кода частоты, и второй цифро-аналоговый преобразователь, выход которого соединен с -другим входом компаратора, при этом выход генератора опор(Ной частоты соединен с сигнальным входом накапливающего сумматора, дополнительный выход которого соединен с другим входом D-триггера и с управляющим входом регистра памяти, поразрядные выходы регистра памяти соединены с соответствующими поразрядными входами второго цифро-аналогового преобразователя, а выход первого цифро-аналогового преобразователя подключен к другому входу генератора линейно изменяющегося напряжения. На чертеже изображена структурная электрическая схема предлагаемого цифрового синтезатора частот. Синтезатор содержит генератор 1 -опорной частоты, блок 2 установки кода частоты, накапливающий сумматор 3, регистр k памяти, первый цифро-аналоговый преобразователь (ЦАП) 5, второй ЦАП 6, D-триггер 7 генератор 8 линейно изменяющегося .напряжения (ГЛИН), компаратор 9, триггер 10 и фильтр 11 Нижних часто Устройство работает следующим об разом. Код требуемой выходной частоты с выходов блока 2 установки кода час тоты поступает на накапливающий сум матор 3, имеющий емкость N, и на входы первого ЦАП $ Напряжение с его выхода поступает на ГЛИН 8 в ка стве напряжения питания схемы. С частотой следования импульса в хода генератора 1 в накапливающем сумматоре 3.осуществляется сложение накопленного числа с числом М, соот ветствующим коду на выходе блока 2. Через К периодов импульсов генератора 1 происходит переполнение накапливающего сумматора 3, на его выходе переполнения появляется импульс, который поступает на управ™ ляющий вход регистра k памяти и на 9 D-вход О-т-риггера 7- В регистре 4 памяти фиксируется код числа Р, оставшегося в накапливающем сумматоре 3 после его переполнения . Второй ЦАП 6 преобразует код этого числа в напряжение, поступающее на первый вход компаратора 9. На второй вход компаратора 9 поступают импульсы пилообразной формы с выхода ГЛИН 8, длительность которых равна периоду следования импульсов опорной частоты, а положение определяется импульсами с выхода D-триггера 7, задержанными по отношению к импульсам переполнения также на период опорной частоты.. При совпадении уровней напряжений на обоих входах компаратор 5 вырабатывает импульсы, длительность которых изменяется в процессе работы синтезатора. Триггер 10 работает в счетном режиме, необходимом для получения на входе фильтра 11 симметричных импульсов. Для того, чтобы исключить зависимость результата сравнения от значений числа М, соответствующего установленной частоте выходного сигнала, напряжение на выходе ГЛИН 8 с изменением М должно изменяться по размаху, поэтому в качестве питающего напряжения ГЛИН 8 используется выходное напряжение первого ЦАП 5, величина которого пропорциональна числу М. Предлагаемое устройство позволяет также увеличить максимальную частоту сигнала на выхопе компаратора. При применении предлагаемого устройства в качестве датчика мелкой сетки частот или в качестве частотного манипулятора значение числа М в процессе работы изменяется незначительно. При этом размах пилообразного напряжения на втором входе компаратора 9 изменяется незначительно, что приводит к уменьшению уровня побочмых спектральных составляющих выходного сигнала. Формула изобретения Цифровой синтезатор частот, содержащий последовательно соединенные генератор опорной частоты, D-триггер, генератор линейно изменяющегося напряжения, компаратор, триггер и фильтр нижних частот, а также последовательно соединенные блок установки кода частоты, накаплива

Авторы

Даты

1982-11-30—Публикация

1981-01-12—Подача