f

Изобретение относится к радиотехнике и может быть использовано в системах цифровой обработки сигналов

Цель изобретения - повышение надежности.

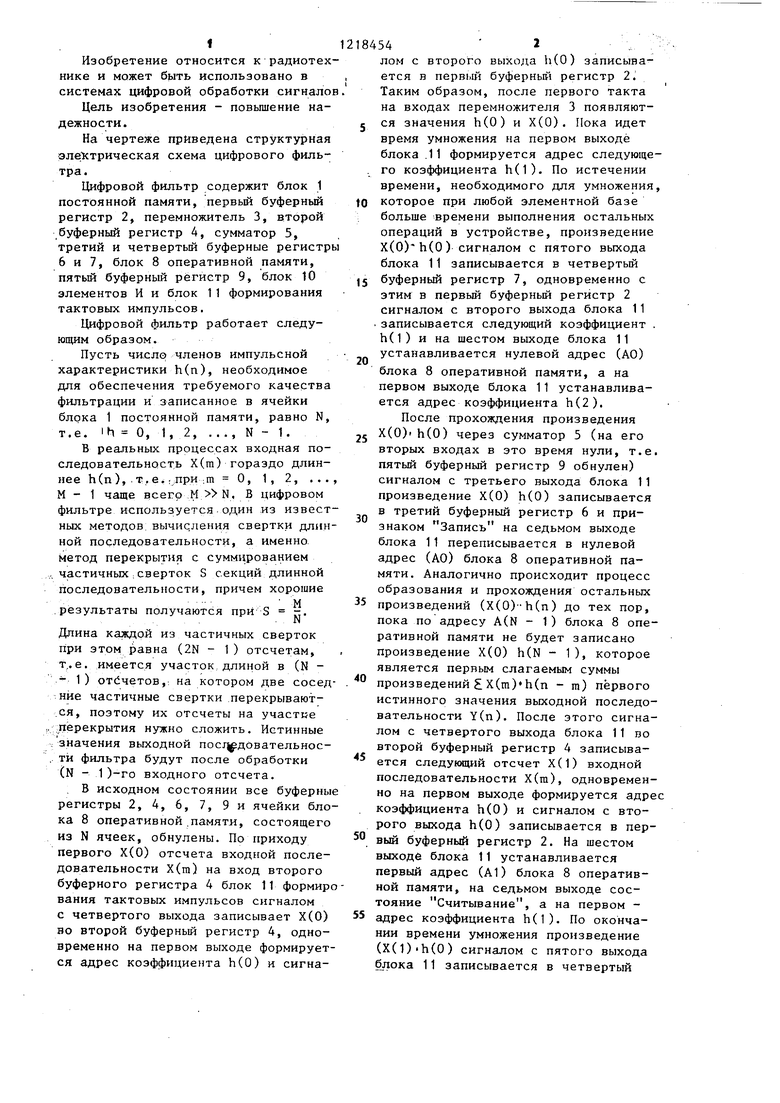

На чертеже приведена структурная электрическая схема цифрового фильтра.

Цифровой фильтр содержит блок 1 постоянной памяти, первый буферный регистр 2, перемножитель 3, второй буферный регистр 4, сумматор 5, третий и четвертый буферные регистр 6 и 7, блок 8 оперативной памяти, пятый буферный регистр 9, блок 10 элементов И и блок 11 формирования тактовых импульсов.

Цифровой фильтр работает следующим образом.

Пусть число членов импульсной характеристики h(n), необходимое для обеспечения требуемого качества фильтрации и записанное в ячейки блока 1 постоянной памяти, равно N, т.е. ih О, 1, 2, ..., N - 1.

В реальных процессах входная последовательность Х(га) гораздо длиннее h(n),.т.е.г при.т 0, 1, 2, ... М - 1 чаще всего , В цифровом фильтре используется один из известных методов: вычисления свертки длинной последовательности, а именно Метод перекрытия с суммированием . частичных.сверток S секций длинной последовательности, причем хорошие

М

.результаты получаются при S -.

N

Длина каждой из частичных сверток при этом равна (2N - 1 ) отсчетам, т,.е. имеется участок длиной в (N - 1) отсчетов, на котором две сосед нйе частичные свертки перекрывают- .ся, поэтому их отсчеты на участке ;;Перекрытия нужно сложить. Истинные значения выходной посх довательнос- , тй фильтра будут после обработки (N - 1 )-го входного отсчета.

. В исходном состоянии все буферны регистры 2, 4, 6, 7, 9 и ячейки блока 8 оперативной .памяти, состоящего из N ячеек, обнулены. По приходу первого Х(0) отсчета входной последовательности Х(т) на вход второго буферного регистра 4 блок 11 формирвания тактовых импульсов сигналом с четвертого выхода записывает Х(0) но второй буферный регистр 4, одновременно на первом выходе формируется адрес коэффициента h(0) и сигна

54 2 , . : лом с второго выхода Ь(0) записывается в первый буферный регистр 2. Таким образом, после первого такта на входах перемножителя 3 появляются значения h(0) и Х(0). Пока идет время умножения на первом выходе блока. 11 формируется адрес следующе- го коэффициента h(1). По истечении времени, необходимого для умножения,

которое при любой элементной базе больше времени выполнения остальных операций в устройстве, произведение Х(0) h(0) сигналом с пятого выхода блока 11 записывается в четвертый

буферный регистр 7, одновременно с этим в первый буферный регистр 2 сигналом с второго выхода блока 11 .записывается следующий коэффициент . h(1) и на шестом выходе блока 11 устанавливается нулевой адрес (АО)

блока 8 оперативной памяти, а на первом выходе блока 11 устанавливается адрес коэффициента h(2).

После прохождения произведения

Х(0) h(0) через сумматор 5 (на его вторых входах в это время нули, т.е. пятый буферный регистр 9 обнулен) сигналом с третьего выхода блока 11 произведение Х(0) h(0) записывается в третий буферный регистр 6 и признаком Запись на седьмом выходе блока 11 переписывается в нулевой адрес (АО) блока 8 оперативной памяти. Аналогично происходит процесс образования и прохождения остальных

произведений (X(0)h(n) до тех пор, пока по адресу A(N - 1 ) блока 8 оперативной памяти не будет записано произведение Х(0) h(N - 1), которое является первым слагаемым суммы

произведений X(ra)h(n - m) первого истинного значения выходной последовательности Y(n). После этого сигналом с четвертого выхода блока 11 во второй буферный регистр 4 записывается следующий отсчет Х(1) входной последовательности Х(т), одновременно на первом выходе формируется адрес коэффициента h(0) и сигналом с второго выхода h(0) записывается в первый буферный регистр 2. На шестом выходе блока 11 устанавливается первый адрес (А1) блока 8 оперативной памяти, на седьмом выходе состояние Считывание, а на первом адрес коэффициента h(1). По окончании времени умножения произведение (X(l) h(O) сигналом с пятого выхода блока 11 записывается в четвертый

3

буфернЕ 1й регистр 7, одновременно сигналом с восьмого выхода в пятый буферный регистр 9 записывается содержимое первого адреса (Л1) блока 8 оперативной памяти и сигналом с второго выхода в первый бу- ферный регистр 2 записывается коэффициент h(1). Пока на перемножителе 3 вычисляется произведение X(1) «h(1 а на сумматоре 5 сумма X(1)-h(0) + + А1 X(1) h(Q) + X(0)-h(1), на шестом выходе блока 11 устанавливается значение нулевого адреса блока 8 оперативной памяти. По окончании времени сложения в третий буферньй регистр 6 сигналом с третьего выход блока 11 записывается сумма X(1) h(0 + X(0) h(1 ), сразу после этого на шестом выходе блока 11 устанавливается значение адреса А2 блока 8 оперативной памяти и одновременно на седьмом выходе состояние Запись меняется на Считывание, а на первом выходе блока 11 устанавливается адрес коэффициента h(2). По окончании времени умножения произведени X(1) h(1) сигналом с пятого выхода блока 11 записывается в четвертый буферный регистр 7. Одновременно сигналом с восьмого выхода в пятый Ьуферный регистр У записывается содержимое второго адреса (А2) блока 8 оперативной памяти и сигналом с второго выхода в первый буферный регистр 2 записывается коэффициент h(2). Пока вычисляется очередное произведение и сумма, на шестом выходе блока 11 устанавливается значение адреса АО блока 8 оперативной памяти, после чего установкой на седьмом выходе состояния Запись сумма X(1) h(05 + X(0) h(1) записывается по адресу АО. В общем случае обработку отсчета Х(1) входной послдовательности Х(т) условно можно представить в следующем виде: Х(1)х X h(n) + А(п + 1), где н 0, 1, 2, ..., N - 1, ...- содержимое адреса; знак обозначает операцию записи. По окончании обработки отсчета Х(1) по адресу A(N - 2) будет записана частичная сумма (двух слагаемых) первого истинного значения выходной последовательности Y(n), а по адресу A(N - т 1) будет записано произведение X(1)h(N - 1), так как адреса AN в блоке 8 оперативной памяти нет и имеется в виду при 0.

18454

Это произведение X(1) h(N - 1) является первым слагаемым суммы, определяющей первый член перекрывающего участка частичной свертки ну5 левой секции входной последовательности Х(т), где m О, 1, ) N - - 1 с первой секцией Х(т), m N, N + 1, ..., 2N - 1. Все последующие отсчеты нулевой секции входной по10 следо-вательности обрабатываются так - же как и Х(1). После обработки последнего отсчета X(N - 1) нулевой секции входной последовательности по нулевому адресу будет записано

15 первое истинное значение Y(0) выходной последовательности Y(n), в адресах А(1), А(2), ..., A(N - 1) - все значения частичной свертки перекрывающегося участка нулевой сек20 цйи с первой секцией. Поэтому перед считыванием первого отсчета X(N) первой секции блок 11 по шестому выходу устанавливает нулевой адрес, по седьмому - признак Считывание,

25 по восьмому записывает АО в пятый буферный регистр 9 и по девятому выходу выдает разрешение на вторые входы блока 10 элементов И для прохождения на выход значения Y(0).

30 После этого во второй буферный регистр 4 записывается значение X(N) и обрабатывается аналогично X(N - 1 ) с выдачей после обработки на выход второго отсчета Y О ходной последовательности и т.д. до обработки последнего отсчета Х(М - 1) входной последовательности , f

I .

Статические регистры, в качестве

буферных, обеспечивают конвейерную обработку входной последовательности отсчетов, когда все .операции обработки совмещены по времени с операцией умножения, что отличает йред- лагаемый цифровой фильтр от известных быстродействием, простотой и экономичностью. Для получения в фильтре низкой частоты частотной характеристики с полосой пропускания

50 0-45 Гц, переходной полосой 45-150 Гц и частотой следования входной последовательности 10000 Гц необходимо было использовать N 263 коэффициента импульсной характеристики. В

55 прототипе это потребовало применения 2N 526 сдвиговых регистров, что на два порядка больше, чем в предлага- емом устройстве.

35

Формула изобретения

Цифровой фильтр, содержащий последовательно соединенные блок посто янной памяти, первый буферный регист и перемножитель, между вторым входом которого и входом цифрового фильтра включен второй буферный . регистр, последовательно соединенные сумматор и третий буферньй регистр, а также блок оперативной памяти, блок элементов И,, выход которого является выходом цифрового фильтра, и блок формирования тактовых импуль- сов, первьй, второй, третий и четвертый выходы которого подключены к входу считывания блока постоянной памяти, входу записи первого буферного регистра, входу записи третье- го буферного регистра и входу записи второго буферного регистра соответРедактор М.Дылын

Составитель А.Осипович

Техред О.Неде Корректор М.Демчик

1138/60 Тираж 818Подписное

ВНИНПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул.Проектная, 4

ственно, отличающийся тем, что, с целью повышения надежности, в него введены четвер тый буферный регистр, включеннньй между выходом перемножителя и первым входом сумматора, и пятый буферный регистр, включенный между выходом - блока оперативной памяти и первым входом блока элементов И, объединенным с вторым входом сумматора, причем вход блока оперативной памяти подключен к выходу третьего буферного регистра, а вход записи четвертого буферного регистра, входы записи и считывания блока оперативной памяти, вход записи пятого буферного регистра и второй вход блока элементов И соединены с пятым, шестым, седьмым, восьмым и девятым выходами блока форшрования тактовых импульсо соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления свертки | 1985 |

|

SU1297073A1 |

| Цифровой перестраиваемый полосовой фильтр | 1982 |

|

SU1166274A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1211748A1 |

| Цифровой фильтр | 1986 |

|

SU1387015A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Низкоскоростной дельта-модулятор | 1984 |

|

SU1203706A1 |

| Устройство для вычисления преобразования Фурье-Галуа и свертки | 1985 |

|

SU1295415A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

Изобретение относится к радиотехнике и может использоваться при цифровой обработке сигналов. Цепь изобретения - повышение надежности. В блоке I постоянной памяти записаны N козф. h.Отсчет входной последовательности Х(0) поступает во второй буферный регистр (БР) 4 и далее на перемножитель 3. На другой вход перемножителя 3 с блока 1 постоянной памяти через первый БР 2 поступают значения коэффициентов h. Результат перемножения через четвертый БР 7 поступает на сумматор 5. Вычисленное значение через третий БР 6 записывается по соответствующему адресу в блок 8 оперативной памяти (БОП). После перемножения отсчета на все N коэф. h и обработки этих значений по адресу (N - 1) БОП 8 запишется первое слагаемое первого истинного.значения выходной последовательности Y(n ). Затем во второй БР 4 заносится следующий отсчет и осуществляется аналогичная обработка. По окончании обработки Х(1) , отсчета по адресу (N - 2) БОП 8 записывается сумма двух слагаемых первого истинного значения выходной последовательности, поступающего через пятый БР 9 на другой вход сумматора 5. По окончании обработки последнего отсчета X(N - 1 ) по нулевому адресу БОП 8 запишется первое истинное значение выходной последовательности, поступакицее через пятый БР 9 и блок 10 элементов И на выход. 1 ил. 5 5 00 4 О1 4;

| Нерекурсивный цифровой фильтр нижних частот | 1982 |

|

SU1037417A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой фильтр | 1982 |

|

SU1059670A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ТИИЭР, т | |||

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

Авторы

Даты

1986-03-15—Публикация

1984-10-18—Подача