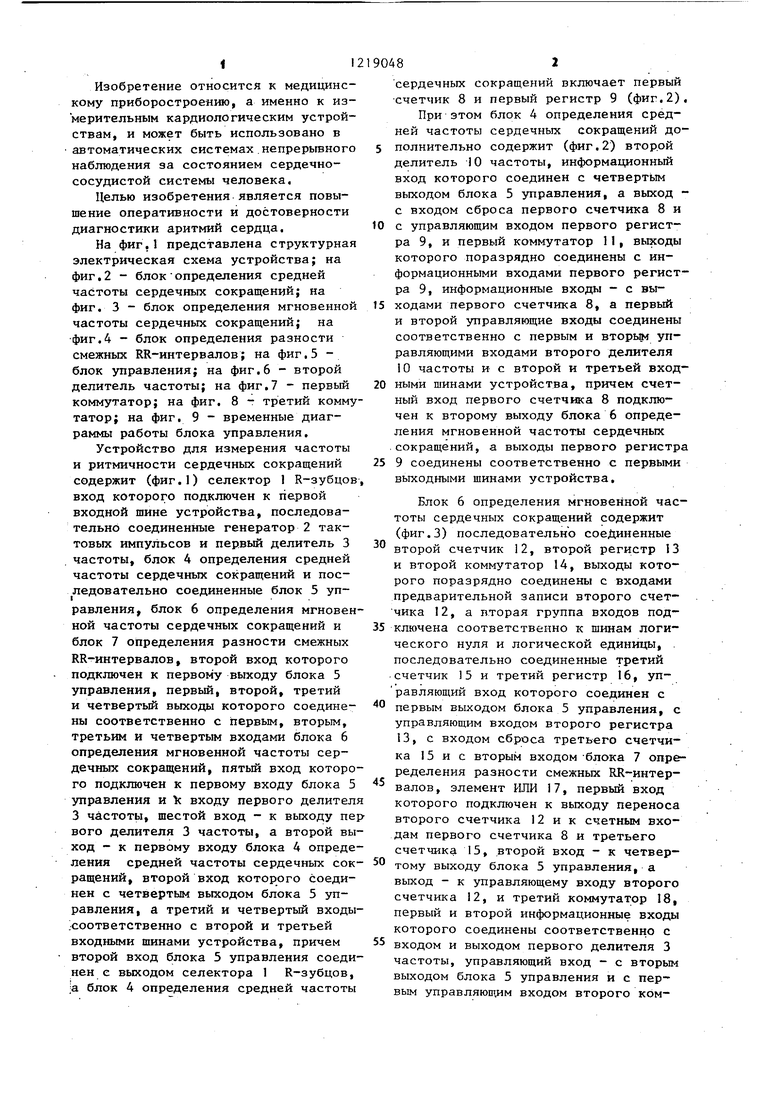

2.Устройство по п,1 о т л и - чающееся тем, что в нем блок определения средней частоты сердечных сокращений дополнительно содержит второй делитель частоты, информационный вход которого соединен с четвертью выходом блока управления, а выход - с входом сброса первого счетчика и с управляющим входом первого регистра, и первый коммутатор, выходы которого поразрядно соединены с информационными входами первого регистра, инфо1)мационные входы с выходами первого счетчика, а первы и второй управляющие входы соединены соответственно с первым и вторым управляющими входдми второго делителя частоты и с второй и третьей входными шинами устройства, причем счетный вход первого счетчика подключен

к второму выходу блока определения мгновенной частоты сердечных сокращений,

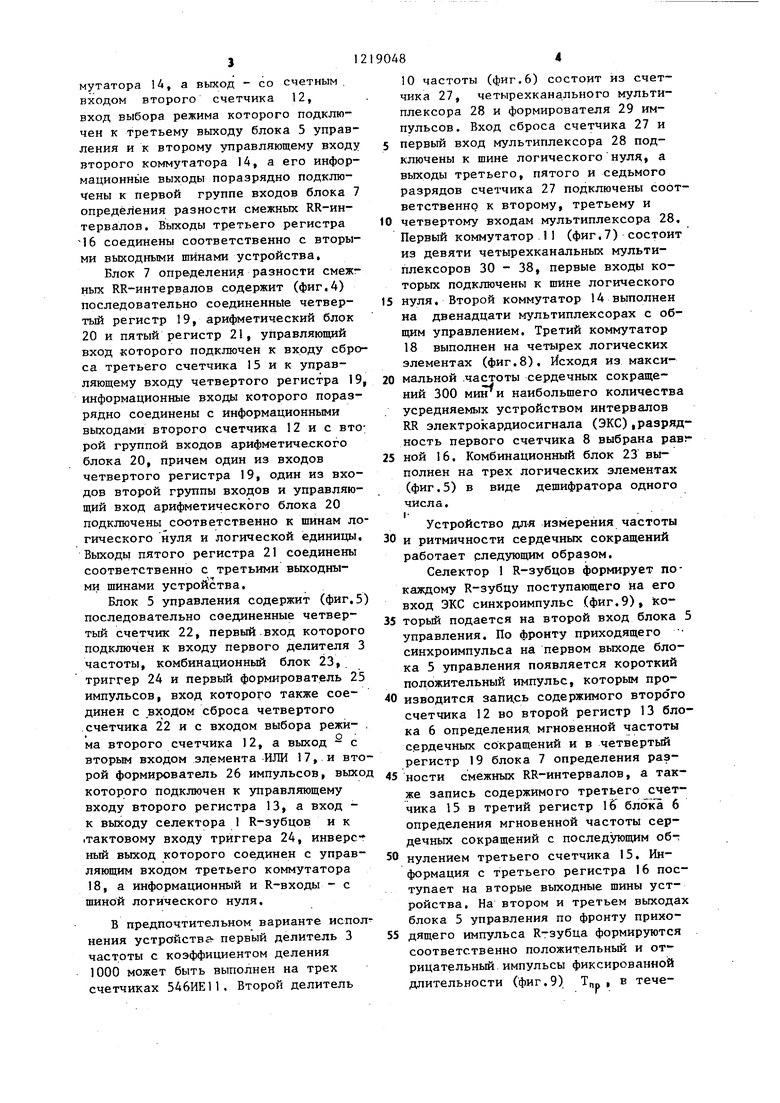

3.Устройство по п. 1, о т л и ч а ю щ е е с я тем, что в нем блок определения мгновенной частоты сердечных со1 ращений содержит последовательно соединенные второй сч етчик, второй регистр и второй коммутатор, входы которого поразрядно соединены

с входами предварительной записи второго счетчика, а вторая группа входов подключена соответственно к шинам логического нуля и логической единицы, последовательно соединенные третий счетчик и третий регистр, управляющий вход которого соединен с первым выходом блока управления, с управляющим входом второго регистра, с входом сброса третьего счетчика и с вторым входом блока определения разности смежньк RR-интервалов, элемент ИЛИ, первый вход которого подключен к выходу переноса второго счетчика и к счетным входам первого и третьего счетчиков, второй вход четвёртому выходу блока управления, а выход - к управляющему входу второго счетчика, и третий коммутатор, первый и второй информационные входы которого соединены соответственно с входом и выходом первого делителя

048

частоты, управляющий вход - с вторым выходом блока управления и с первым управляющим входом второго коммутатора, а выход - со счетным входом второго счетчика, вход выбора режима которого подключен к третьему выходу блока управления и к второму управляг ющему входу второго коммутатора, а его информационные выходы поразрядно подключены к первой группе входов блока определения разности смежных RR-интервалов,

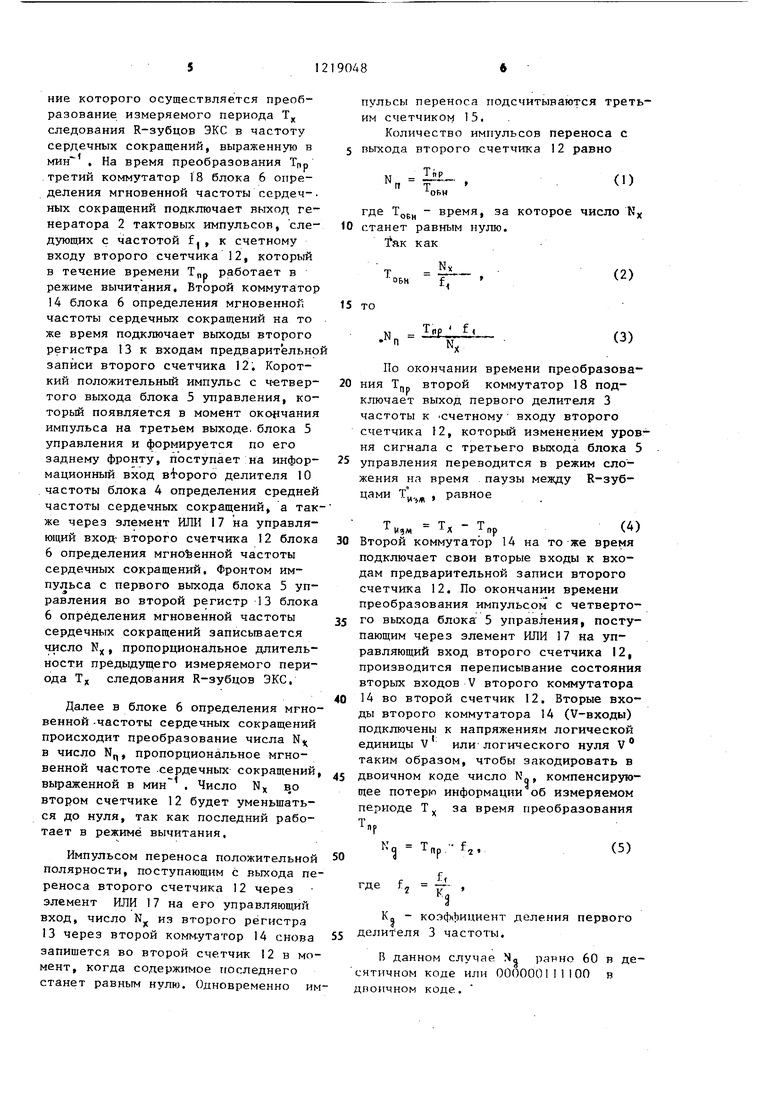

4,Устройство ПОП.1, отличающееся тем, что в нем блок определения разности смежных RR-интервалов содержит последовательно соединенные четвертый регистр, арифметический блок и пятый регистр, управляющий вход которого подключен к входу сброса третьего счетчика и к управляющему входу четвертого регистра, информационные входы которого поразрядно соединены с информационными выходами второго счетчика и с второй группой входов арифметического блока, причем один из входов четвертого ре.гистра, один из входов второй группы входов и управляющий вход арифметического блока подключены соответственно к шинам логического нуля и логической единицы,

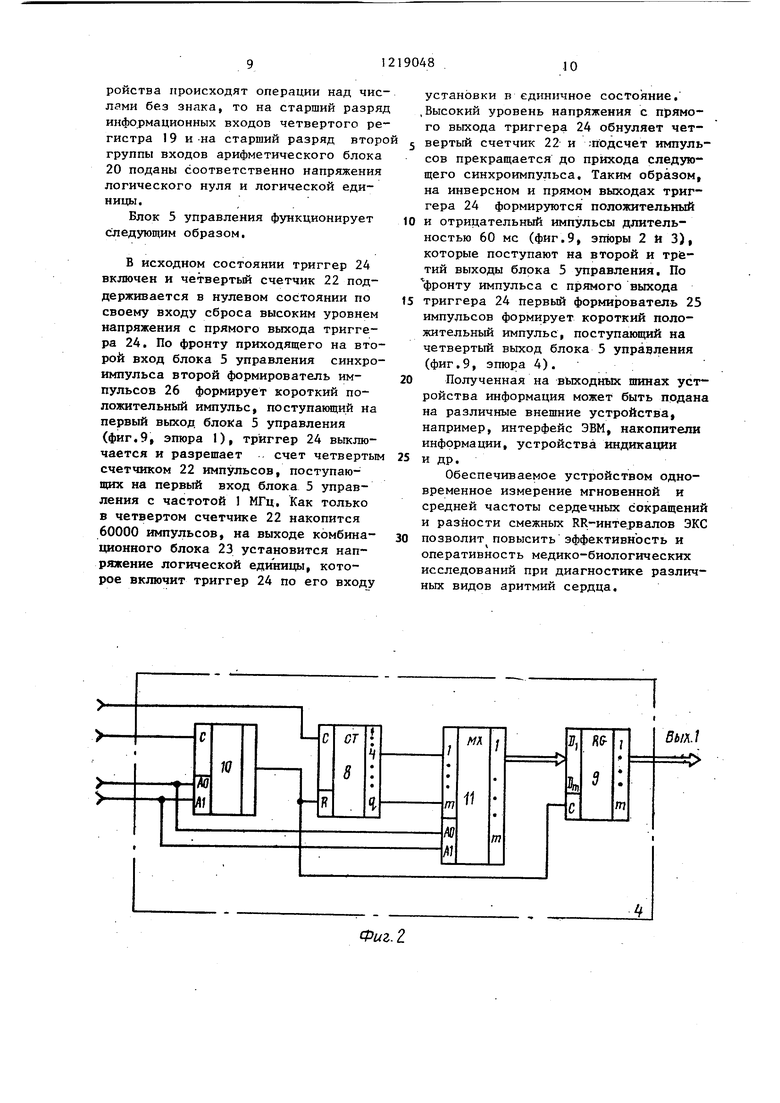

5.Устройство по п,1, о т л и т чающееся тем, что в нем блок управления содержит последовательно соединенные четвертый счетчик, первых вход которого подключен к входу первого делителя частоты, комбинационный блок, триггер и первый формирователь импульсов, вход которого также соединен с входом сброса четвертого счетчика и с входом выбора режима второго счетчика, а выход с вторым входом элемента ИЛИ, и второй формирователь импульсов, выход которого пoдкJшчeн к управляющему входу второго регистра, а вход - к выходу селектора R-зубцов и к тактовому входу триггера, инверсный , выход которого соединен с управляющим входом третьего коммутатора, а информационный и R-входы - с щиной логического нуля.

112

Изобретение относится к медицинскому приборостроению, а именно к измерительным кардиологическим устройствам, и может быть использовано в автоматических системах.непрерывного наблюдения за состоянием сердечнососудистой системы человека.

Целью изобретения является повышение оперативности и достоверности диагностики аритмий сердца.

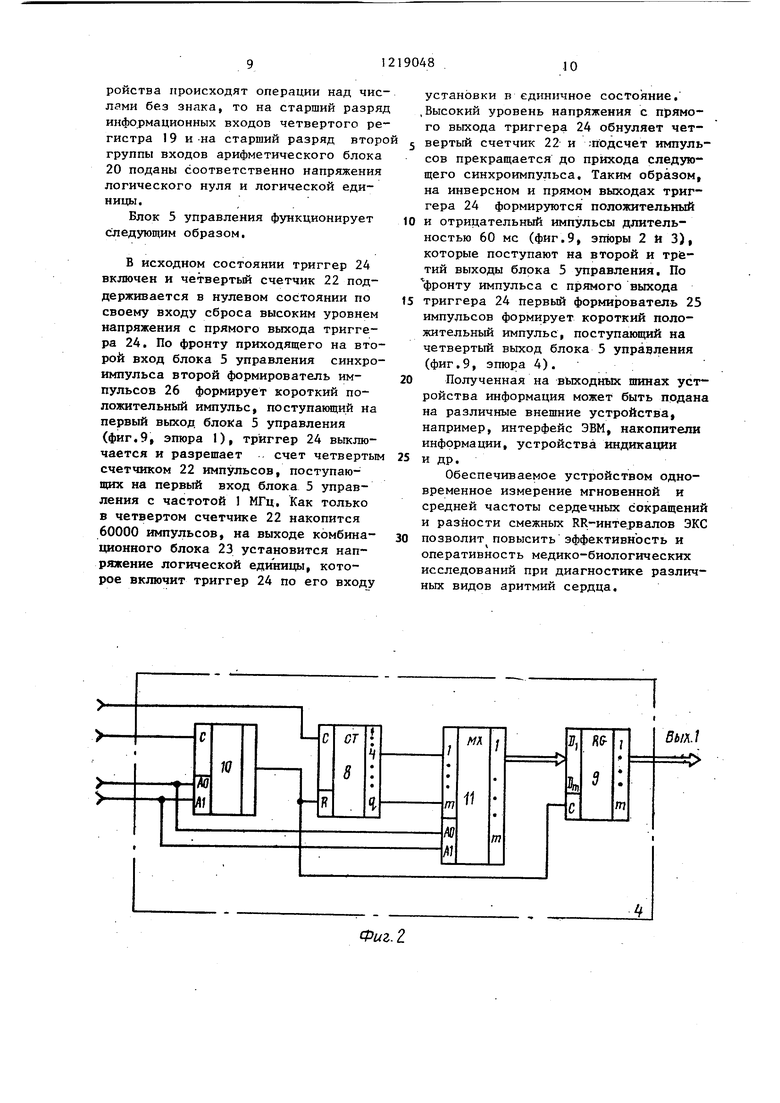

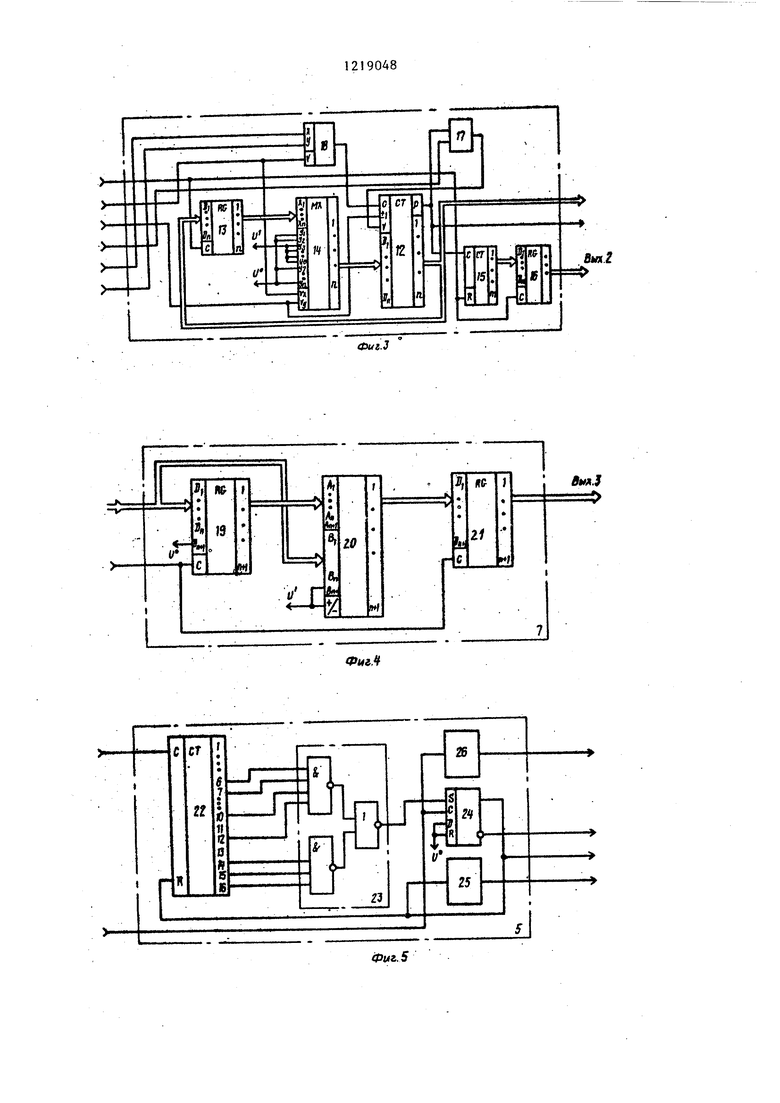

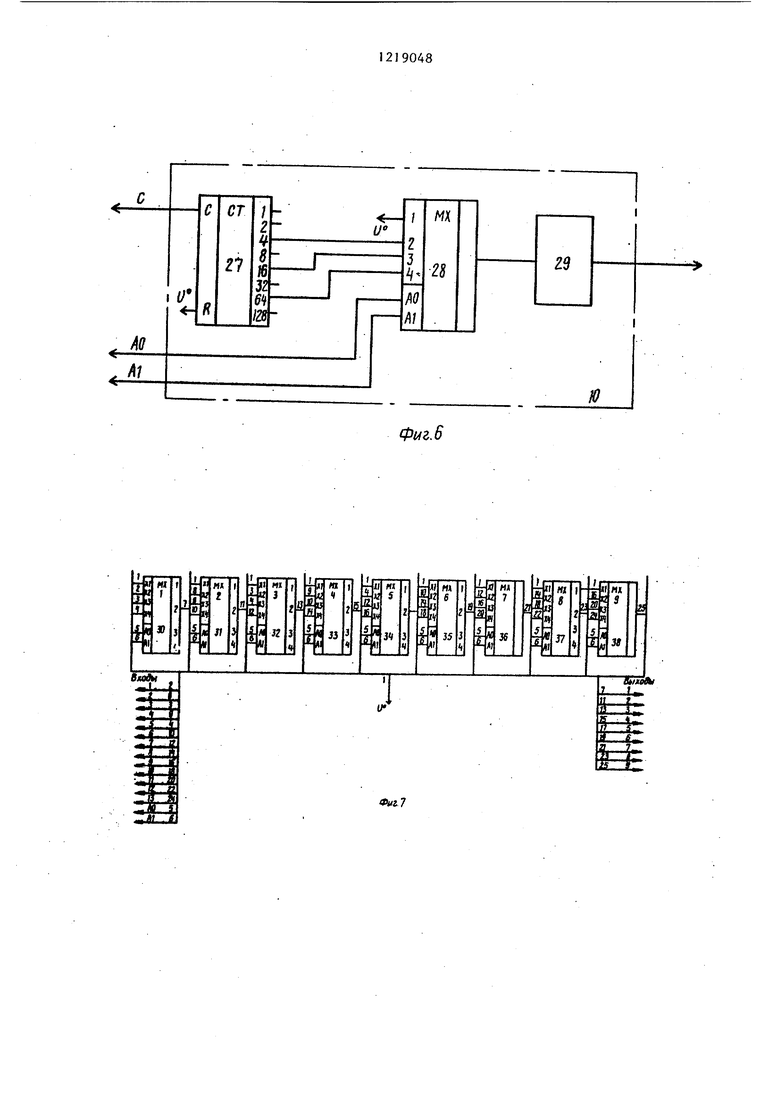

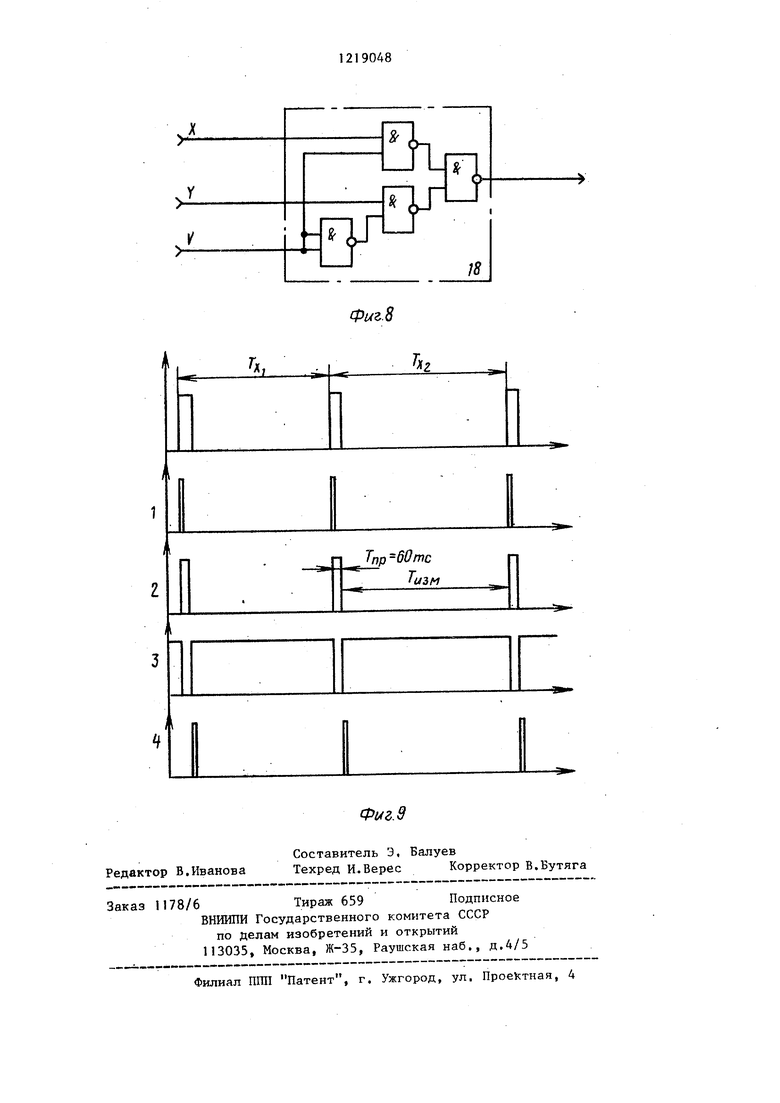

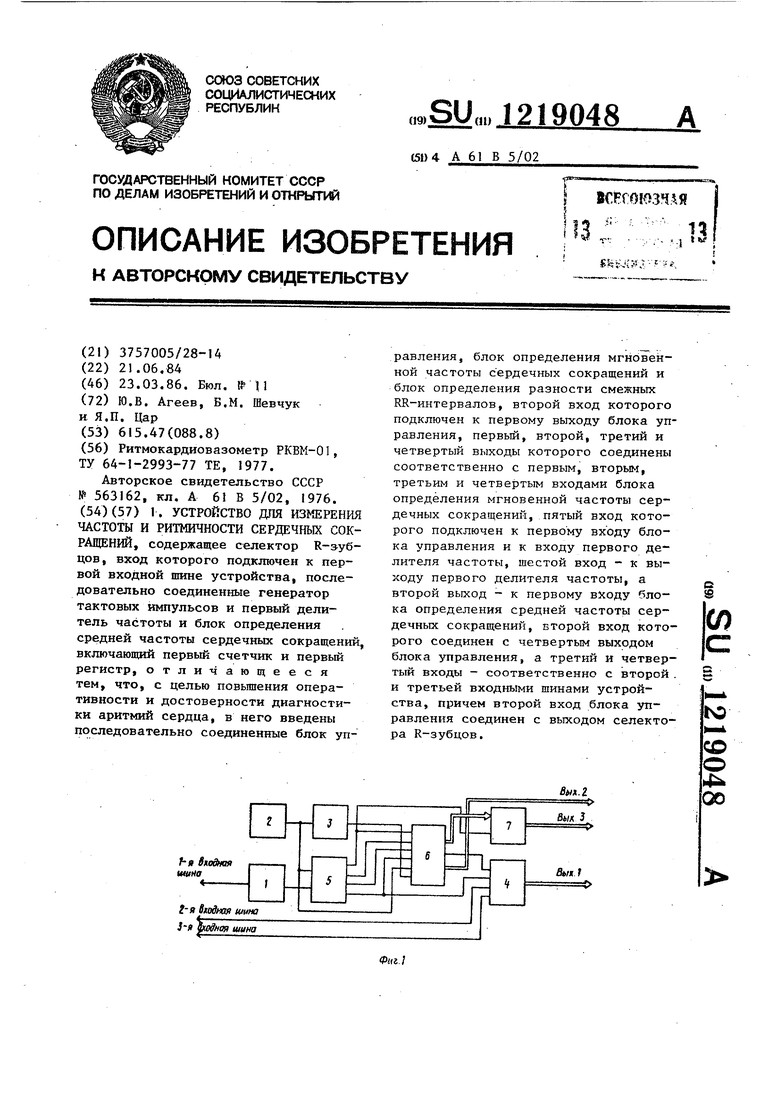

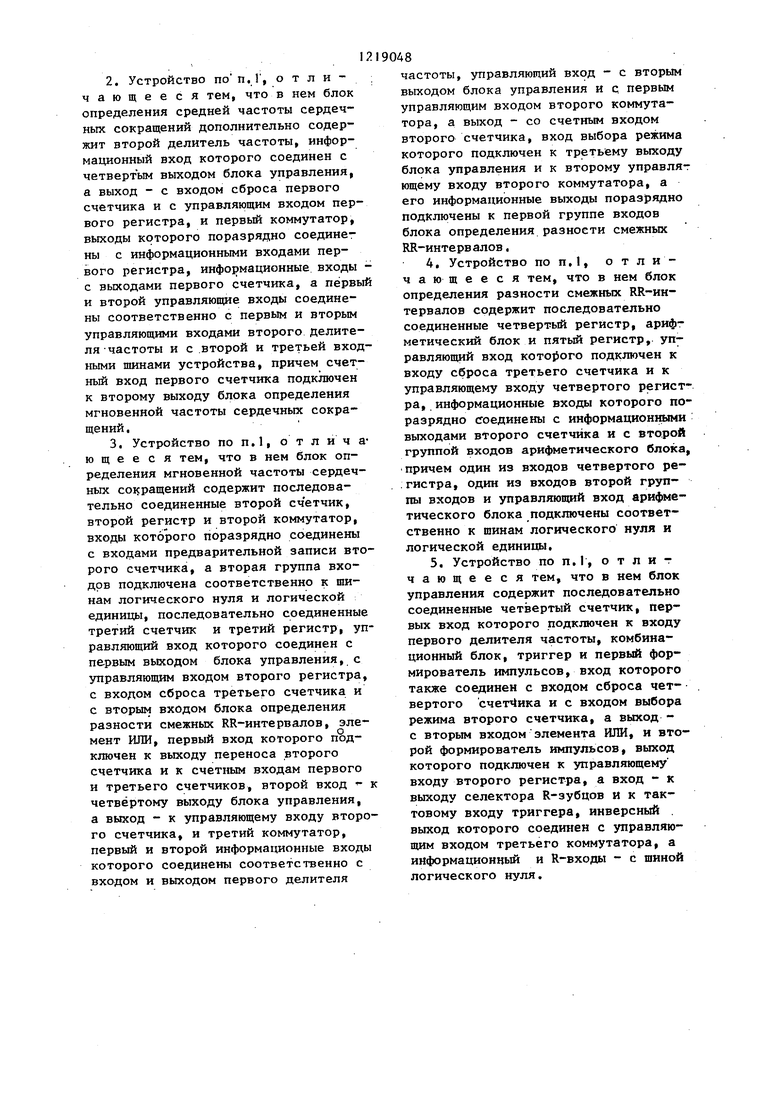

На фиг.1 представлена структурная электрическая схема устройства; на фиг,2 - блокопределения средней частоты сердечных сокращений; на фиг. 3 - блок определения мгновенной частоты сердечных сокращений; на фиг.4 - блок определения разности смежных RR-интервалов; на фиг.5 - блок управления; на фиг.6 - второй делитель частоты; на фиг,7 - первый коммутатор; на фиг. 8 - третий коммутатор; на фиг. 9 - временные диаграммы работы блока управления.

Устройство для измерения частоты и ритмичности сердечных сокращений содержит (фиг,1) селектор 1 R-зубцов вход которого подключен к первой входной шине устройства, последовательно соединенные генератор 2 тактовых импульсов и первый делитель 3 частоты, блок 4 определения средней частоты сердечных сокращений и последовательно соединенные блок 5 управления, блок 6 определения мгновенной частоты сердечных сокращений и блок 7 определения разности смежных RR-интервалов, второй вход которого подключен к первому выходу блока 5 управления, первый, второй, третий и четвертый выходы которого соединены соответственно с первым, вторым, третьим и четвертым входами блока 6 определения мгновенной частоты сердечных сокращений, пятый вход которого подключен к первому входу блока 5 управления и 1с входу первого делителя 3 частоты, шестой вход к выходу пер вого делителя 3 частоты, а второй выход - к первому входу блока 4 определения средней частоты сердечных сокращений, второй вход которого соединен с четвертым выходом блока 5 управления, а третий и четвертый входы- ;Соответственно с второй и третьей входными шинами устройства, причем второй вход блока 5 управления соединен с выходом селектора 1 R-зубцов, ;а блок 4 определения средней частоты

0482

сердечных сокращений включает первый счетчик 8 и первый регистр 9 (фиг.2). При этом блок 4 определения средней частоты сердечных сокращений до5 полнительно содержит (фиг.2) второй делитель 10 частоты, информационный вход которого соединен с четвертьтм выходом блока 5 управления, а выход - с входом сброса первого счетчика 8 и

0 с управляющим входом первого регистра 9 , и первый коммутатор 11, выходы которого поразрядно соединены с информационными входами первого регистра 9, информационные входы - с вы5 ходами первого счетчика 8, а первый и второй управляющие входы соединены соответственно с первым и вторьм управляющими входами второго делителя 10 частоты и с второй и третьей вход0 ными шинами устройства, причем счетный вход первого счетчика В подключен к второму выходу блока 6 определения мгновенной частоты сердечных .сокращений, а выходы первого регистра

5 9 соединены соответственно с первыми выходными шинами устройства.

Блок 6 определения мгновенной частоты сердечных сокращений содержит (фиг.З) последовательно соединенные второй счетчик 12, второй регистр 13 и второй коммутатор 14, выходы которого поразрядно соединены с входами предварительной записи второго счетчика 12, а вторая группа входов под5 ключена соответственно к шинам логического нуля и логической единицы, . последовательно соединенные третий счетчик 15 и третий регистр 16, управляющий вход которого соединен с первым выходом блока 5 управления, с управляющим входом второго регистра 13, с входом сброса третьего счетчика 15 и с вторым входом -блока 7 опре- ределения разности смежных RR-интервалов, элемент ИЛИ 17, первый вход которого подключен к выходу переноса второго счетчика 12 и к счетным входам первого счетчика 8 и третьего счетчика 15, второй вход - к четвертому выходу блока 5 управления, а выход - к управляющему входу второго счетчика 12, и третий коммутатор 18, первый и второй информационные входы которого соединены соответственно с

5 входом и выходом первого делителя 3 частоты, управляющий вход - с вторым выходом блока 5 управления и с первым управляющим входом второго ком0

5

0

мутатора 14, а выход - со счетным , входом второго счетчика 12, вход выбора режима которого подключен к третьему выходу блока 5 управления и к второму управляющему входу второго коммутатора 14, а его информационные выходы поразрядно подключены к первой группе входов блока 7 определения разности смежных RR-ин- тервалов. Выходы третьего регистра 16 соединены соответственно с вторыми выходными шинами устройства.

Блок 7 определение разности смежных RR-интервалов содержит (фиг,4) последовательно соединенные четвертый регистр 19, арифметический блок 20 и пятый регистр 21, управляющий вход которого подключен к входу сброса третьего счетчика 15 и к управляющему входу четвертого регистра I9, информационные входы которого поразрядно соединены с информационными выходами второго счетчика 12 и с вто; рой группой входов арифметического блока 20, причем один из входов четвертого регистра 19, один из входов второй группы входов и управляющий вход арифметического блока 20 подключены соответственно к щинам логического нуля и логической единицы. Выходы пятого регистра 21 соединены соответственно с третьими выходными щинами устройства.

Блок 5 управления содержит (фиг, 5) последовательно соединенные четвертый счетчик 22, первый вход которого подключен к входу первого делителя 3 частоты, комбинационный блок 23, триггер 24 и первьй формирователь 25 импульсов, вход которого также соединен с входом сброса четвертого счетчика 22 и с входом выбора режи- , ма второго счетчика 12, а выход - с вторым входом элемента ИЛИ 17,.и второй формирователь 26 импульсов, выход которого подключен к управляющему входу второго регистра 13, а вход - к выходу селектора 1 R-зубцов и к 1тактовому входу триггера 24, инверс- ный выход которого соединен с управляющим входом третьего коммутатора 18, а информационный и R-входы - с щиной логического нуля,

В предпочтительном варианте испол нения устройства- первый делитель 3 частоты с коэффициентом деления 1000 может быть выполнен на трех счетчиках 546ИЕ11. Второй делитель

10 частоты (фиг.6) состоит из счетчика 27, четырехканального мультиплексора 28 и формирователя 29 импульсов. Вход сброса счетчика 27 и 5 первый вход мультиплексора 28 подключены к шине логического нуля, а выходы третьего, пятого и седьмого разрядов счетчика 27 подключены соответственно к второму, третьему и

10 четвертому входам мультиплексора 28, Первый коммутатор 11 (фиг,7) состоит из девяти четырехканальных мультиплексоров 30 - 38, первые входы которых подключены к шине логического

15 нуля. Второй коммутатор 14 выполнен на двенадцати мультиплексорах с общим управлением. Третий коммутатор 18 выполнен на четырех логических элементах (фиг,8), Исходя из макси20 мальной .частоты сердечных сокращений 300 ми1ги наибольшего количества усредняемых устройством интервалов RR электрокардиосигнала (ЭКС).разрядность первого счетчика 8 выбрана рав25 ной 16, Комбинационный блок 23 выполнен на трех логических элементах (фиг,5) в виде дешифратора одного числа,

Устройство дл-я измерения частоты

30 и ритмичности сердечных сокращений работает следующим образом.

Селектор 1 R-зубцов формирует по- каждому R-зубцу поступающего на его вход ЭКС синхроимпульс (фиг,9), ко35 торый подается на второй вход блока управления. По фронту приходящего синхроимпульса на первом выходе блока 5 управления появляется короткий положительный импульс, которым про40 изводится запнсь содержимого второго счетчика 12 во второй регистр 13 блока 6 определения, мгновенной частоты сердечных сокращений и в четвертый регистр 19 блока 7 определения раз45 ности смежных RR-интервалов, а также запись содержимого третьего счетчика 15 в третий регистр 6 блок 6 определения мгновенной частоты сердечных сокращений с последующим обт

50 нулением третьего счетчика 15, Информация с третьего регистра I6 поступает на вторые выходные шины устройства. На втором и третьем выходах блока 5 управления по фронту прихо55 дящего импульса R-зубца формируются соответственно положительный и отрицательный импульсы фиксированной длительности (фиг,9) , в течение которого осуществляется преобразование измеряемого периода Т следования R-зубцов ЭКС в частоту сердечных сокращений, выраженную в . На время преобразования Тпр третий коммутатор 18 блока 6 определения мгновенной частоты сердеч-. ных сокращений подключает выход генератора 2 тактовых импульсов, следующих с частотой f,, к счетному входу второго счетчика 12, который в течение времени работает в режиме вычитания. Второй коммутатор 14 блока 6 определения мгновенной частоты сердечных сокращений на то же время подключает выходы второго регистра 13 к входам предварительной записи второго счетчика 12. Короткий положительный импульс с ч-етвер- того выхода блока 5 управления, ко- торьй появляется в момент окончания импульса на третьем выходе, блока 5 управления и формируется по его заднему фронту, поступает на информационный вход в -орого делителя 10 частоты блока 4 определения средней частоты сердечных сокращений, а также через элемент ИЛИ 17 на управляющий вход- второго счетчика 12 блока 6 определения мгновенной частоты сердечных сокращений. Фронтом импульса с первого выхода блока 5 управления во второй регистр 13 блока 6 определения мгновенной частоты сердечных сокращений записывается число N, пропорциональное длительности предьщущего измеряемого периода Т), следования R-зубцов ЭКС,

Далее в блоке 6 определения мгновенной -частоты сердечных сокращений происходит преобразование числа N в число NP, пропорциональное мгновенной частоте .сердечных сокращений, выраженной в . Число N, во втором счетчике 12 будет уменьшаться до нуля, так как последний работает в режиме вычитания.

Импульсом переноса положительной полярности, поступающим с выхода переноса второго счетчика 12 через элемент ИЛИ 17 на его управляющий вход, число N из второго регистра 13 через второй комм-утатор 14 снова запищется во второй счетчик 12 в момент, когда содержимое последнего станет равным нулю. Одновременно импульсы переноса подсчитываются третьим счетчиком 15.

Количество импульсов переноса с 5 выхода второго счетчика 12 равно

N

I up

OfiM

(1)

где TQP - время, за которое число N

10 станет равным нулю. как

ОБН

NX

f.

15 то

.NH

- TOP f

N.

(2)

(3)

По окончании времени преобразова- 20 ния Tf, второй коммутатор 18 подключает выход первого делителя 3 частоты к Счетному входу второго счетчика 12, который изменением уровня сигнала с третьего выхода блока 5 25 управления переводится в режим сложения на время паузы между R-зуб- цами T J,, , равное

т т - т

ИЭМ X nf

(4)

30 Второй коммутатор 14 на то же время подключает свои вторые входы к входам предварительной записи второго счетчика 12, По окончании времени преобразования импульсом с четверто-

35 го выхода блока 5 управления, поступающим через элемент ИЛИ 17 на управляющий вход второго счетчика 12, производится переписывание состояния вторых входов V второго коммутатора

40 14 во второй счетчик 12, Вторые входы второго коммутатора 14 (V-входы) подключены к напряжениям логической единицы V или логического нуля V таким образом, чтобы закодировать в

45 двоичном коде число Ng, компенсирующее потерю информации об измеряемом периоде Т за время преобразования Т„р

50 «Г Р- -

где ., |.,

К„ - коэффициент деления первого 55 делителя 3 частоты,

В данном случае No ранне 60 в де- сятичном коде или 000000111100 в двоичном коде.

N

I up

(1)

OfiM

где TQP - время, за которое число N

ОБН

NX

f.

(2)

.NH

- TOP f

N.

(3)

т т - т

ИЭМ X nf

рой коммутатор ключает свои вто предварительной тчика 12, По око образования импу

По окончании времени преобразования начинается подсчет числа Nj в течение интервала

NX (T,-Tnj,) f,,.-fj. (6)

Подставляя значение N из уравнения (6) в уравнение (3) и учитывая, ч то коэффициент деления Кп первого делителя 3 частоты равен f., /f , получаем

N.

Т„ Т

К

(7)

., /9 т,-.

Выбирая Т„р 60 мс, f|, 1 МГц и К и Ко 1000, получаем масштабный коэффициент К 60 и, следовательно, результат измерения частоты сердечных сокращений, выраженный в мин ,

Измерение среднего значения частоты сердечных сокращений осуществляется параллельно процессу измерения У1гновенной частоты се рдечных сокращений. Подсчет импульсов переноса с выхода переноса второго счетчика 12 блока 6 определения мгновенной частоты сердечных сокращений осуществляет первый счетчик 8 блока 4 определения, средней частоты сердечных сокращений, в котором накапливаются импульсы за несколько интервалов преобразования. Количество ус- редияемых интервалов RR определяется коэффициентом деления второго делителя 10 частоты, который может быть изменен переменной состояния его управляющих входов АО и А по второй и третьей входным шинам устройства,

В конкретном варианте выполнения устройства количество усредняемых интервалов RR выбрано равным 2, где J/ - целое положительное число, В этом случае операция усреднения (деления) заменяется операцией отбрасывания i младших разрядов результата, накапливающегося в первом счет- чикб 8, Указанная операция осуществляется первым коммутатором 11, который подключает q выходов первого счетчика 8 к информационным входам первого регистра 9, где q - количество разрядов первого счетчика 8, в данном случае равное 16, Значение i -может быть установлено равным трем, пяти или семи.

Для осуществления усреднения за 8, 32 и 128 интервалов RR второй делитель 10 частоты при подаче на его

управляющие входы Al и АО двоичных сигналов 01, 10, 11 будет выполнять деление входной частоты соответст 5 венно на В, 32 и 128 и на его выходе будет появляться соответственно каждый 8-й, 32-й и 128-й импульсы. Короткими импульсами с выхода второго делителя 10 производится запись через

10 первый коммутатор 11 содержимого первого счетчика 8 без трех или пяти или семи младших разрядов в первый регистр 9, т.е. запись результата усреднения соответственно за 8, 32

5 или 128 интервалов RR с последующим обнулением первого счетчика 8, С выхода первого регистра 9 информация поступает на первые выходные шины устройства. При сос тоянии второй и

20 третьей входных шин устройства 00 второй делитель 10 частоты вьцслюча- ется и первый коммутатор 11 подключает информационные входы первого регистра 9 к шине логического нуля ,

25 Управляющая комбинация 00 используется для выключения режима определения среднего значения частоты сердечных сокращений (ЧСС),

Измерение разности между соседними RR-интервалами ЭКС осуществляется блоком 7 определения разности смежных RR-интервалов параллельно процессу измерения мгновенной частоты сердечных сокращений. С выхода второго счетчика 12 блока 6 определения мгновенной ЧСС двоичный код очередного интервала RR поступает на информационные входы четвертого регистра

19и записывается в него по фронту импульса с первого выхода блока 5 управления.Одновременно результат вычитания кодов дв5гх смежных RR-интервалов , представленный в дополнительном коде, с выхода арифметического блока 20 переписьгаается в пятый регистр 21, с выхода которого-информаг ция поступает на третьи выходные шины устройства. Операция вычитания производится арифметическим блоком

20путем суммирования прямого двоичного кода текущего интервала RR с дополнительнь м кодом предшествующего интервала RR, Старший разряд результата является знаковым. В этом раз

ряде будет ноль, если разность кодов смежных RR-интервалов положительная, и единица, если разность отрицательная. Так как в остальных блоках устройства происходят операции над числами без знака, то на старший разряд информационных входов четвертого регистра 19 и на старший разряд второ группы входов арифметического блока 20 поданы соответственно напряжения логического нуля и логической единицы.

Блок 5 управления функционирует следующим образом.

В исходном состоянии триггер 24 включен и четвертый счетчик 22 поддерживается в нулевом состоянии по своему входу сброса высоким уровнем напряжения с прямого выхода триггера 24, По фронту приходящего на второй вход блока 5 управления синхроимпульса второй формирователь им- пульсов 26 формирует короткий положительный импульс, поступающий на первый выход блока 5 управления (фиг.9, эпюра 1), триггер 24 вьжлю- чается и разрешает счет четвертым счетчиком 22 импульсов, поступающих на первый вход блока 5 управления с частотой 1 Mrut Как только в четвертом счетчике 22 накопится 60000 импульсов, на выходе комбина- циониого блока 23 установится напряжение логической единицы, которое включит триггер 24 по его входу

установки в единичное состояние, ,Высокий уровень напряжения с прямого выхода триггера 24 обнуляет четвертый счетчик 22 и ;подсчет импульсов прекращается до прихода следующего синхроимпульса. Таким образом, на инверсном и прямом выходах триггера 24 формируются положительный и отрицательный импульсы длительностью 60 мс (фиг,9, эпюры 2 и 3), которые поступают на второй и третий выходы блока 5 управления. По афронту импульса с прямого выхода триггера 24 первый формирователь 25 импульсов формирует короткий положительный импульс, поступающий на четвертый выход блока 5 управления (фиг,9, эпюра 4), ;

Полученная на выходных шинах устройства информация может быть подана на различные внешние устройства, например, интерфейс ЭВМ, накопители информации, устройства индикации и др.

Обеспечиваемое устройством одновременное измерение мгновенной и средней частоты сердечных сокращений и разности смежных КК-инте.рвалов ЭКС позволит повысить эффективность и оперативность медико-биологических исследований при диагностике различных видов аритмий сердца.

Фиг.2.

rrt

Ё

мд

W

t/

и

cr

IZ

R&

вм

ke

фиг. 6

Редактор В.Иванова

Ф1/г.9

Составитель Э. Балуев

Техред И.Верес Корректор В.Бутяга

Заказ 1178/6 Тираж 659 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г. Ужгород, ул, Проектная, 4

Фиг.8

по -60 тс

| название | год | авторы | номер документа |

|---|---|---|---|

| Детектор экстрасистол | 1985 |

|

SU1377030A1 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА РОДОВОЙ ДЕЯТЕЛЬНОСТИ | 1998 |

|

RU2130645C1 |

| СПОСОБ ВЫЯВЛЕНИЯ АРИТМИИ ЭЛЕКТРОКАРДИОСИГНАЛА В РЕАЛЬНОМ ВРЕМЕНИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2321339C1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство для измерения частоты сердечных сокращений | 1990 |

|

SU1759401A1 |

| Устройство для измерения частоты пульса | 1984 |

|

SU1211662A1 |

| Устройство для анализа ритма сердца | 1986 |

|

SU1553049A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Устройство для регистрации ритма сердечной деятельности и характера его изменений | 1978 |

|

SU784867A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель частоты сердечных сокращений | 1976 |

|

SU563162A1 |

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

Авторы

Даты

1986-03-23—Публикация

1984-06-21—Подача