Изобретение относится к импульсной технике и может быть использовано в буферных каскадах часовых ,К-МОГ1 ИС.

Цель изобретения - увеличение мощности, отдаваемой в нагрузку выходным транзистором, за счет смещения подложки транзистора.

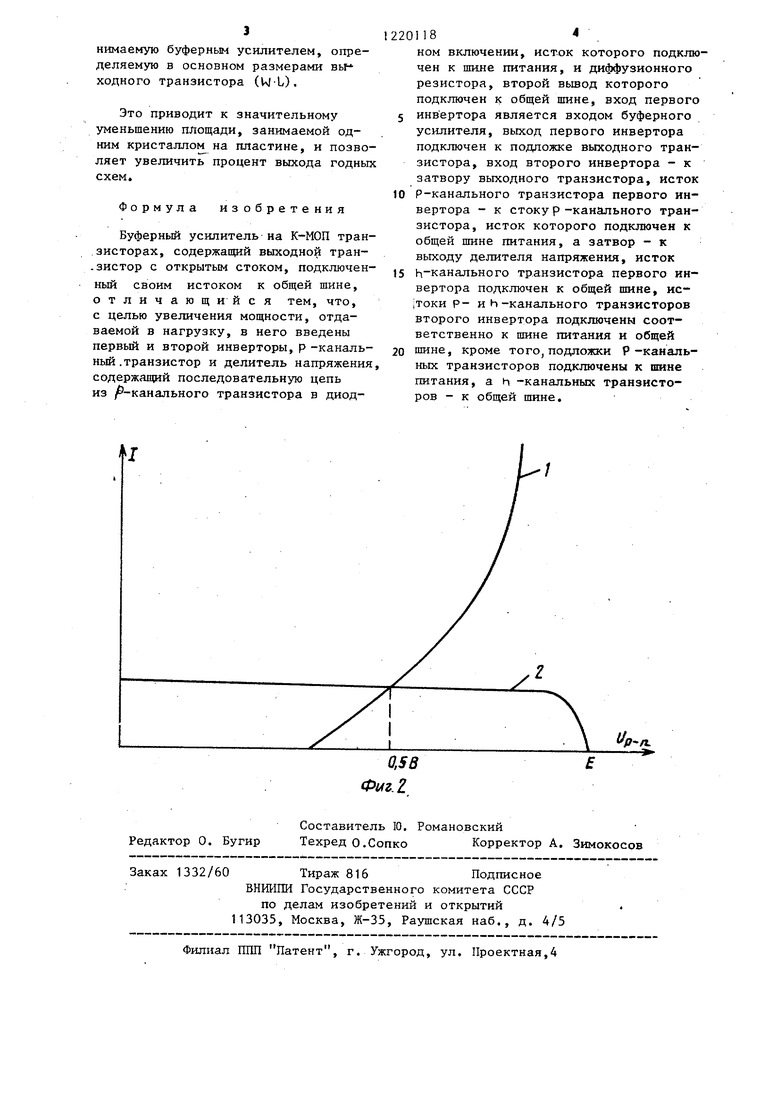

На фиг.1 показана электрическая схема устройства; на фиг,2 - вольт- амперные характеристики (ВЛХ) исто-- кового Р -h-перехода выходного трап-- зистора и Р-канального транзистора (где I - ток5 Е напряжение, кривая I ВАХ истокового Р-h-перехода выходного транзистора, кривая 2 - ВАХ Р-канального транзистора).

Буферный усилитель на К-МОП транзисторах содержит выходной транзистор 1 с открытым стоком 2«исток ко- торого подключен к общей шине 3, а подложка - к выходу первого инвертора 4, состоящего из п-канального транзистора 5 и Р-канального транзистора 6, исток которого подключен к стоку Р-канального транзистора 7,, подключенного истоком к шине 8 питания, а затвором - к делителю напряжения , включенному между шиной 8 питания и общей шиной 3 и состоящем из Р-канального транзистора 9 и диф™ фузионного резистора 10. Затворы транзисторов первого инвертора 4 подключены к входу 11, к нему же подключен второй инвертор 12 на трап-- эисторах 13 и 1Аэ выход инвертора 12 подключен к затвору выходного транзистора 1 с открытым стоком 2.

Устройство работает следующим образом.

Если на входе 11 высокий.уровень напряжения (логическая единица), то на выходе обоих инверторов нулевой уровень напряжения, выходной транзистор 1 заперт и его ток стока равен нулю. Если на вход 11 подан низкий уровень напряжения (логический нуль), то оба инвертора открыты, затвор транзистора 1 подключен к пзине питания, а его подложка связана с ис T04HFSKOM питания через генератор тока на транзисторе 7,

I

Делитель, состоящий из транзистора 9 в диодном включении и резистора 10, создает на затворе транзисто- pa 7 напряжение, превышающее пороговое напряжение этого транзистора на .небольшую величину, так, чтобы тран

зистор работал в пологой области ВДХ, т.е. транзистор 7 работает в режиме генератора тока. При зтом независимо от величины питания схемы на подложке транзистора 1 устанавливается напряжение, соответствующее границе отпирания его истокового Р-перехода3 т.е. примерно 0,5 В.

Величина тока, обеспечивающего смещение подложки, должна соответствовать лишь границе отпирания истокового Р -ti-перехода (не более 1 мкА), чтобы коэффициент усиления вертикального биполярного транзистора К- МОП структуры несущественно отличался от единицы.

Если величина напряжения смещения истокового Р -h-перехода транзистора о напряжение отпирания-этого транзистора уменьшается на величину

иГ .

iUorH--U,

Ug- составляющая порогового напряжения транзистора, обусловленная объемным заря дом j

f двойной потенциал Ферми. Лпя типичного случая iJg 0,75 В; f Одб В При и, 0,5 В имеем

йЬ1„,,,0,3&,

Длл порогового напряжения h-канального транзистора К-МОП ИС, равного 0,9 В, и напряжения питания 1,2 В (разряд батареи с номиналом 1j55 В) получается, что превышение напряжения на затворе данного транзистора над пороговым напряжением увогличивается в два раза, а, следовательно, ток через транзистор уве- лкчивается в четыре раза по формуле

I - 1 ft - /1 / -1 ( V 1- 2 Ро IT - ,

где К Л размеры транзисторРа,

удельная крутизна. Такикс образом, буферный усилитель на К-МОП транзисторах благодаря подключению к подложке выходного транзистора генератора тока смещения, двух инверторов и делителя напряжения позволяет увеличить выходной ток во внешней стоковой цепи в четьфе раза и тем самым повысить мощность, отдаваемую в нагрузку, в четыре раза либо при неизменной мощности y feHbm-iTb в четыре раза площадь,за- ,

3

нимаеную буферным усилителем, определяемую в основном размерами вы-- ходного транзистора (W-L),

Это приводит к значительному уменьшению площади, занимаемой одним кристаллом на пластине, и позволяет увеличить процент выхода годных схем.

Формула изобретения

Буферный усилитель на К-МОП транзисторах, содержащий выходной тран- -зистор с открытым стоком, подключенный своим истоком к общей шине, отличающийся тем, что, с целью увеличения мощности, отдаваемой в нагрузку, в него введены первый и второй инверторы,р-канальный .транзистор и делитель напряжения содержащий последовательную цепь из -канального транзистора в диодРедактор 0. Бугир

Составитель Ю. Романовский

Техред о.Сопко Корректор А. Зимокосов

Заках 1332/60 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная,4

118

ном включении, исток которого подключен к шине питания, и диффузионного резистора, второй вьшод которого подключен к общей шине, вход первого инвертора является входом буферного усилителя, выход первого инвертора подключен к подложке выходного транзистора, вход второго инвертора - к затвору выходного транзистора, исток

Р-канального транзистора первого инвертора - к стокур -канального транзистора, исток которого подключен к общей шине питания, а затвор - к выходу дехштеля напряжения, исток

Ь канального транзистора первого инвертора подключен к общей шине, ис- |токи р- и h-канального транзисторов второго инвертора подключены соответственно к шине питания и общей

шине, кроме того, подложки Р-канальных транзисторов подключены к шине питания, а h -канальных транзисторов - к общей шине.

Р-л

0,S8 Ф1Аг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Стабилизатор напряжения питания часовой интегральной схемы | 1985 |

|

SU1345165A1 |

| Формирователь сигнала начальной установки делителя частоты кварцевых наручных часов | 1986 |

|

SU1365041A1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ УРОВНЕЙ ЛОГИЧЕСКИХ СИГНАЛОВ НА КМОП-ТРАНЗИСТОРАХ | 1993 |

|

RU2085030C1 |

| Кварцевый генератор | 1983 |

|

SU1109855A1 |

| Кварцевый генератор | 1987 |

|

SU1425801A1 |

| ПОЛУПРОВОДНИКОВОЕ КЛЮЧЕВОЕ УСТРОЙСТВО | 2003 |

|

RU2268545C2 |

| Кварцевый генератор | 1987 |

|

SU1679599A1 |

| Устройство для подключения телефонного аппарата к абонентской линии | 1991 |

|

SU1780589A3 |

Изобретение относится к области импульсной техники и может быть использовано в буферных каскадах часовых интегральных схем. Цель изобретения - увеличение мощности, отдавае-, мой в нагрузку выходным транзистором, за счет смещения подложки транзистора. Устройство содержит выходной транзистор 1 с открытым стоком 2, общую шину 3, инверторы 4 и 12, h-канальные транзисторы 5 и 13 первого и второго инверторов,р -канальные транзисторы 6 и 14 первого и второго инверторов соответственно,Р-канальные транзисторы 7, шину питания 8, Р-канальный транзистор 9 в диодном включении, диффузионный резистор 10, вход устройства 11. Усилитель позволяет увеличить выходной ток во внешней стоковой цепи и мощность, отдаваемую в нагрузку, в 4 раза. 2 ил. (Л

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Интегральные схемы на МДП-при- борах./ Под ред | |||

| А | |||

| Карамзинского, М.: Мир | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| с | |||

| Приспособление для уменьшения дымовой тяги паровоза | 1920 |

|

SU270A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-03-23—Публикация

1984-07-25—Подача