Изобретение относится к электро- радиоизмерительной технике и может быть использовано при разработке фа- зометрических устройств повышенной точности.

Цель изобретения - повышение точности измерения, в случае когда на информационный сигнал наложена импульсная помеха, за счет того, что входной информационный сигнал, искаженный частично или полностью помехой, исключается из дальнейшей обработки и не используется.

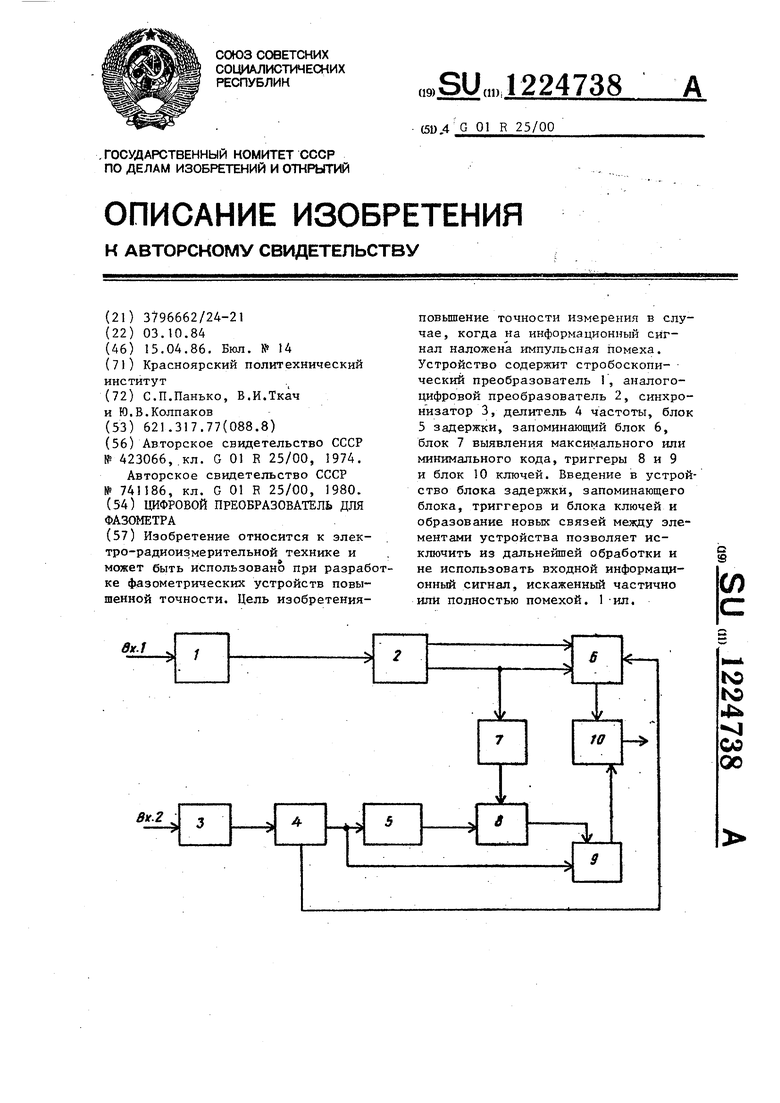

На чертеже изображена структурная схема цифрового преобразователя для фазометра.

Цифровой преобразователь для фазометра состоит из стробоскопического преобразователя 1, соединенного с аналого-цифровым преобразователем 2, синхронизатора 3, подключенного к делителю 4 частоты, блока 5 задержки, запоминающего блока 6, а также из последовательно включенных блока 7 выявления максимального или минимального кода, первого 8 и второго 9 триггеров, блока 10 ключей. Первый и второй входы запоминающего блока 6 подключены к первом и второму выходам аналого-цифрового преобразователя 2, третий вход запоминающего блока 6 - к второму выходу делителя 4 частоты, а выход запоминающего блока 6 соединен с первым входом блока 10 ключей. Выход блока IО ключей является выходом цирового преобразователя для фазометр

Цифровой преобразователь для фазометра работает следующим образом.

Входной информационный сигнал вместе Q положенной на него импульсной Помехой поступает на стробоскопический преобразователь 1. На синхронизатор 3 поступает опорное напряжение , а на его выходе присутствуют импульсы с периодом , где Т - период входного сигнала, Р - количество точек отсчета в одном периоде входного сигнала. Стробоскопический преобразователь 1 квантует входной сигнал по времени, т.е производит выборку и запоминание мгновенных значений входного сигнала в момент воздействия импульсов с выхода синхронизатора 3 на время, необходимое для обработки информации аналого-цифровым преобразователем. На первом выходе аналого-цифрового преобразователя 2 формирует5

0

ся цифровой код, пропорциональный мгновенному значению входного напряжения,, Цифровые эквиваленты мгновенных: значений входного напряжения по сигналу конец преобразования со второго выхода аналого-цифрового преобразователя заносятся в запоминающий блок 6 по адресам, формируе- ivibiM делителем 4 частоты, емкость которого равна количеству точек отсчета Р. Запоминающий блок 6 состоит из Р ячеек памяти. Разрядность каждой ячейки равна разрядности аналого-цифрового преобразователя 2. Таким образом, коды всех отсчетов располагаются в запоминающем блоке 6, На выход устройства коды отсчетов поступают только при открытых ключах блока 10 ключей. Количество ключей в блоке 10 ключей равно разрядности аналого-цифрового преобразователя 2, т.е. кажд,ый разряд кода отсчета проходит через свой ключ, а управляются все ключи одновременно. При от5 сутствии помех информация на выход устройства проходит с задержкой на один период входного сигнала. В те- черше первого периода происходит заполнение ячеек запоминающего блока 6 и только в следующем периоде входного сигнала коды отсчетов начинают проходить на выход в порядке поступления :их на вход запоминающего блока 6, В тот момент, когда код из ячейки запоминающего блока 6 поступает на вход блока 10 ключей, в эту же ячейку записывается код отсчета, получаемый в текущем периоде входного сигнала. Импульсная помеха, наложенная на сигнал, искажает значе- .ние кода отсчета с выхода аналого- цифрового преобразователя 2. Амплитуда входного сигнала не должна пре- вьшшть определенного порога Un, меньшего максимального размаха ам плитудной характеристики аналого- цифрового преобразователя 2. Тогда критерием появления импульсной помехи и искажения ею входного сигнала является появление максимально го (или минимального) значений кода. Факт появления одного из этих значений (превышение порога) выявляется блоком 7 выявления максимального или минимального кода и запомина5 ется первым триггером 8. Таким образом, первый триггер 8 фиксирует факт искажения входного сигнала импульсной помехой. Второй триггер 9

0

5

0

управляет работой блока 10 ключей. В случае, если в прошедшем периоде искажений не было, то второй триггер 9 стоит в положении, разрешающем работу ключей в блоке 10 ключей. Если бьшо-хотя бы одно искажение, то в конце периода входного сигнала импульсом с выхода .делителя 4 частоты второй триггер 9 переводится в состояние, запрещающее работу ключей. В этом состоянии второй триггер 9 стоит до конца вновь начавшегося периода. Установка первого триггера 8 в нулевое состояние производится несколько позднее переписи его состояния во второй триггер 9. Это обеспечивается блоком 5 задержки.

Таким образом, периоды входного сигнала, полностью или частично пораженные импульсной помехой, в дальнейшей работе не используются, что приводит к повышению точности измерения,

Погрешность прототипа в рассмотренном случае можно- оценить следующим путем.

Представим входной сигнал в виде

S(f)U sir(t t+tfc) + + Z U.sin(ia)-t+q);)

i «

(1)

где первое слагаемое - входной информационный сигнал амплитуды U , частоты « и фазы Cf, , а второе - импульсная помеха, состоящая из г гармоник частоты Шр, амплитудой U, с соответствующими фазами ср,- . При (1) можно говорить о поражении импульсной помехой каждого К-го пе- риода входного сигнала.

Поскольку время измерения ограничивается цельм числом-периодов входного сигнала T Z 2 tt/U (Z 1,2,3...), то результат измерения

Ч-гго (2)

где Cfj -фазовый сдвиг, вычисляемый в J-OM периоде входного сигнала .

При отсутствии импульсных помех последовательность cfj () представляет собой статически однородную последовательность случайных чисел с математическим ожиданием cf . В случае поражения импульсной помехой m периодов в последовательности ц

появляется m чисел - выбросов (с дискретного случайного процесса tf- . Тогда (2). можно записать в виде:

j Z-m I i,Ml

Zlcf. - i:(fj+i: ДУр . J P.O. J I 2 j o - p-0 I

Здесь значение выброса представлено &з ммой числа, принадлежащего (Q статически однородной совокупности , и случайного приращения дс . Погрешность измерения:

(

15

....

Для приближения оценки максимального значения погрешности положим:

Чр„ -ЗбО, Тогда

А .„, I 360°

(3)

в предлагаемом цифровом преобразователе для фазометра пораженный период исключается из дальнейшей обработки. Рассматриваемая погрешность исключается для и,,и ,

где и... - высота импульса помехи.

Для Uy Uq предлагаемое базовое устройство и прототип равноценны. Амплитуда сигнала Uj всегда меньше порога и„, т.е. . При малых значениях широкополосных шумов

легко обеспечить такие значения дО, при которых погрешность измерения йср предлагаемым устройством не превзойдет 1 . Принимая во внимание самый неблагоприятный случай ,

получим, что предлагаемое устройство эффективнее прототипа в , / /i(p 180 раз.

Формула изобретения

Цифровой преобразователь для фазометра, содержащий стробоскопический преобразователь, соединенный с аналого-цифровым преобразователем

и входом информационного сигнала, последовательно включенные синхро- низауор, вход которого соединен с входом опорного сигнала, и делитель частоты, отличающийся

тем, что, с целью повышения точности измерения, он снабжен блоком задержки, запоминающим блоком, последовательно включенным блоком выявления максимального или мияимально- го кода, первым триггером, вторым триггером,блоком ключей, причем первый и второй входы запоминающего блока подключены к первому и второму выходам аналого-цифрового преобразователя, третий вход запоминающего блока - к второму выходу делителя

частоты, а выход запоминающего бло- Шлителя частоты через блок задержки.

Редактор А.Ревин Заказ 1947/45

Составитель В.Шубин Техред Н.Бонкало

Корректор Е

Тираж 728Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/3

.Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная,4.

,ка - к первому входу блока ключей вход блока выявления максимального или кгинимального кода соединен с пер- 5 вым выходом аналого-цифрового преобразователя, при этом второй вход второго триггера подключен к первому выходу делителя частоты,а второй вход первого триггера-к первому вьпсоду деКорректор Е.Сирохман

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь для фазометра | 1986 |

|

SU1345135A1 |

| Измеритель сдвига фаз (его варианты) | 1982 |

|

SU1040432A1 |

| Измеритель сдвига фаз | 1982 |

|

SU1013872A1 |

| Цифровой фазометр | 1982 |

|

SU1033983A1 |

| Фазометр | 1982 |

|

SU1068837A1 |

| Цифровой фазометр и его варианты | 1982 |

|

SU1020781A1 |

| Измеритель сдвига фаз | 1977 |

|

SU741186A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Программируемый преобразователь напряжения произвольной формы в напряжение требуемой формы | 1990 |

|

SU1711303A1 |

| Цифровой фазометр | 1979 |

|

SU822075A1 |

Изобретение относится к элек- тро-радиоизмерительиой технике и может быть использовано при разработке фдзометрических устройств повышенной точности. Цель изобретенияповышение точности измерения в случае, когда на информационный сигнал наложена импульсная помеха. Устройство содержит стробоскопи- ческий преобразователь 1, аналого- цифровой преобразователь 2, синхронизатор 3, делитель 4 частоты, блок 5 задержки, запоминающий блок 6, блок 7 выявления максимального или минимального кода, триггеры 8 и 9 и блок 10 ключей. Введение в устройство блока задержки, запоминающего блока, триггеров и блока ключей и образование новых связей между элементами устройства позволяет исключить из дальнейшей обработки и не использовать входной информационный сигнал, искаженный частично или полностью помехой. 1ил, i (Л в ж. г to tc «4 «vl 00 00

| ЦИФРОВОЙ КОРРЕЛЯЦИОННЫЙ ФАЗОМЕТР | 1972 |

|

SU423066A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление в центрифугах для регулирования количества жидкости или газа, оставляемых в обрабатываемом в формах материале, в особенности при пробеливании рафинада | 0 |

|

SU74A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-04-15—Публикация

1984-10-03—Подача