Изобретение относится к измереиям в технике связи и может быть спользовано, для измерения уровня еременного напряжения.

Целью изобретения является повыение точности измерения за счет ввеения двух подциклов измерения - груого и точного преобразования, а ффект повышения точности в предагаемом измерителе заключается в том, что ступень цифроаналогового реобразования, производя подцикл грубого преобразования, дает возможность точной ступени цифроаналогового преобразования (ЦАП) произвести поддикл точного преобразования, при котором амплитуда входного переменного сигнала близка к напряжению на аналоговом входе ЦАП.

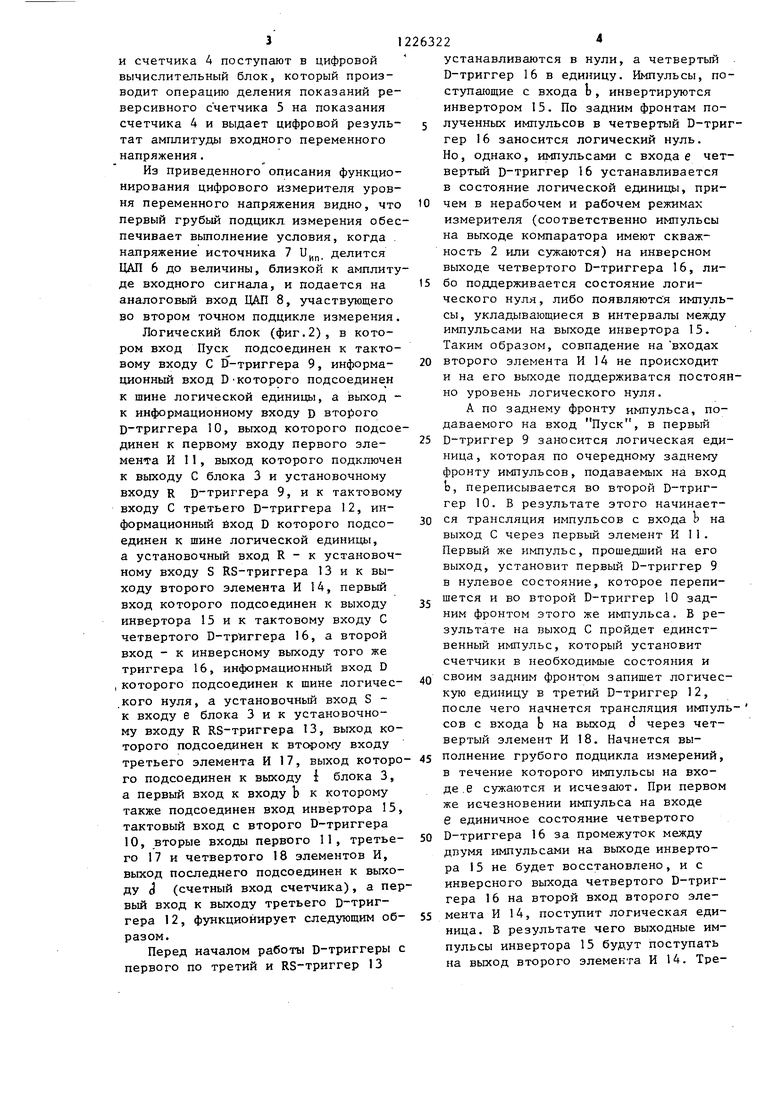

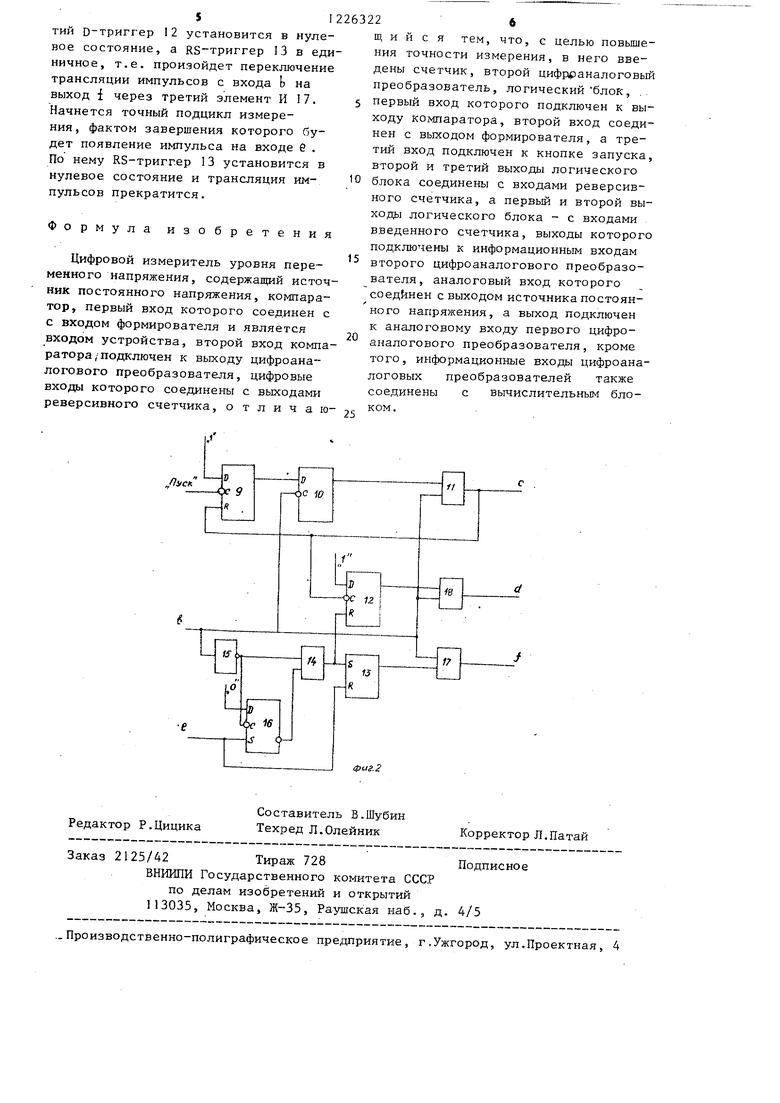

На фиг.1 приведена структурная схема устройства; на фиг.2 - принди- пиальная схема логического блока. Цифровой измеритель уровня переменного напряжения (фиг,1) содержит компаратор 1, первый вход кото- рого соединен с входом формирователя 2 и является входом устройства, выход компаратора I подключен к первому входу логического блока 3, к второму входу которого подключен выход формирователя 2, к третьему входу подключен выход кнопки запуска. Первый и второй выходы логического блока 3 подключены к входам счетчика 4, второй и третий выходы логичес кого блока 3 соединены с входам: реверсивного счетчика 5. Выходы счетчика 4 подключены к цифровым входам цифроаналогового преобразователя 6 и параллельно к цифровому вычислительному блоку. Аналоговый вход циф)ро- аналогового преобразователя 6 соединен с выходом источника 7 постоянного напряжения.

Выход цифроаналогового преобразователя 6 подключен к аналоговом / входу цифроаналогового преобразователя 8, Цифровые входы цифроаналогового преобразователя 8 соединены с выходами реверсивного счетчика 5 и параллельно с вычислительным блоком. Выход цифроаналогового преобразователя 8 подключен к второму входу компаратора 1 .

Устройство работает следующим образом.

Цикл измерения начинается подачей на вход Пуск логического блока 3 ко-

10

15

20

25

30

35

40

30

55

роткого импульса положительной поляр- ности. После чего выходы реверсивного счетчика 5 и счетчика 4 устанавливаются соответственно в единичные и нулевые состояния подачей на их установочные входы импульса с второго выхода логического блока 3.

В результате на выходе 6 установится напряжение, равное нулю, а ЦДЛ 8 будет работать в режиме трансляции напряжения с аналогового входа на выход. Таким обратом, исходное компенсирующее напряжение на втором входе компаратора 1 будет равно нулю.

Цикл измерения состоит из двух подциклов: грубого и точного измерения. При первом грубом подцикле логический блок 3 транслирует импульсы с входа b на свой первый вход J . Далее эти импульсы поступают на счет- ньй вход счетчика 4. С каждьгм периодом входного переменного сигнала двоичная комбинация на выходах счетчика 4 увеличивается на единицу и напряжение на выходе ЦАП 6 увеличивается на величины U2 Это напряжение, поступая через ЦАП 8 на второй вход компаратора 1, вызывает сужение импульсов на выходе последнего с каждым периодом. При превышении величины компенсирующего напряжения амплитуды входного сигнала импульсы на выходе компаратора 1 исчезают. Этот факт регистрируется логическим блоком 3, и он производит переключение трансляции импульсов формирователя 2 с первого выхода о на третий i . С этого момента начинается второй - точный подцикл измерения, в течение которого импульсь с выхода формирователя 2 через логический блок 3 постулают на вычитающий вход первого реверсивного счетчика 5, который при этом на каждом последующем периоде уменьшает двоичну -э комбинацию на своих выходах на единицу, вси:1едствие чего компенсирующее напряжение на выходе ЦАП 8 уменьшается на величины А,. Б момент времб .ни,, когда компенсирующее напряжение станет больше амплитуды входного сигнала, на выходе компаратора

1появляется импульс, который регистрируется блоком 3. По этому факту логический блок 3 прекращает трансляцию t:tMnynbcoB с выхода формирователя

2на свои выходы и цикл измерения заканчивается. Двоичные комбинации

с выходов реверсивного счетчика 5

и счетчика 4 поступают в цифровой вычислительный блок, который производит операцию деления показаний реверсивного счетчика 5 на показания счетчика 4 и выдает цифровой результат амплитуды входного переменного напряжения,

Из приведенного описания функционирования цифрового измерителя уровня переменного напряжения видно, что первый грубый подцикл измерения обеспечивает вьтолнение условия, когда . напряжение источника 7 и делится

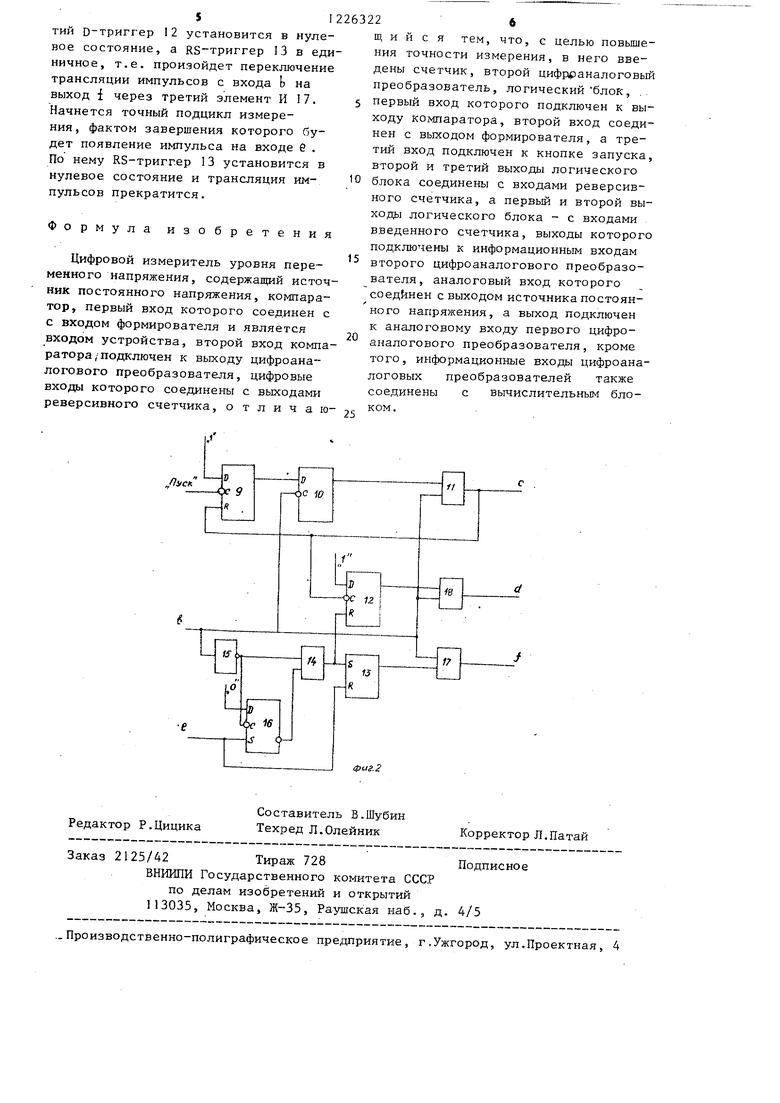

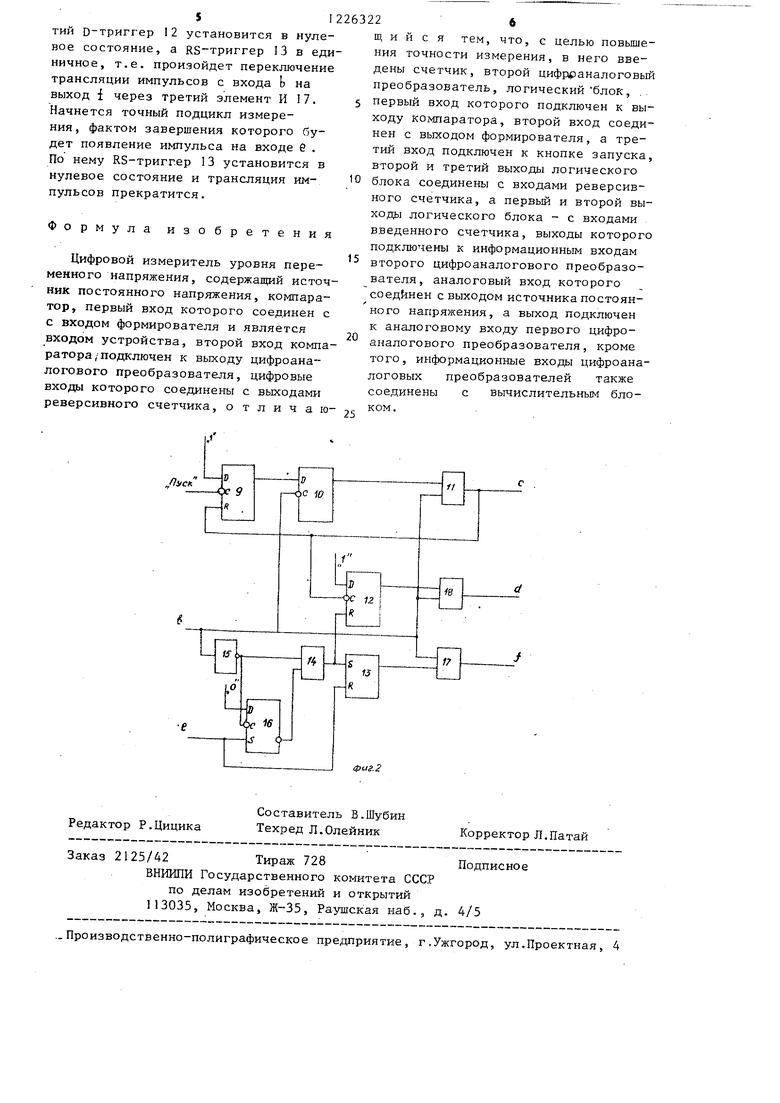

ЦАП 6 до величины, близкой к амплитуде входного сигнала, и подается на аналоговый вход ЦДЛ 8, участвующего во втором точном поддикле измерения. Логический блок (фиг.2), в котором вход Пуск подсоединен к тактовому входу С D-триггера 9, информа- ционньй вход D Которого подсоединен к шине логической единицы, а выход - к информационному входу D второго р-триггера 10, выход которого подсоединен к первому входу первого элемента И 11, выход которого подключен к выходу С блока 3 и установочному входу R в триггера 9, и к тактовому входу С третьего D-триггера 12, информационный йход D которого подсоединен к шине логической единицы, а установочный вход R - к установочному входу S RS-триггера 13 и к выходу второго элемента И 14, первый вход которого подсоединен к выходу инвертора 15 и к тактовому входу С четвертого D-трИггера 16, а второй вход - к инверсному выходу того же триггера 16, информационный вход D ,которого подсоединен к шине логического нуля, а установочный вход S - к входу е блока 3 и к установочному входу R RS-триггера 13, выход которого подсоединен к второму входу

устанавливаются в нули, а четвертый

D-триггер 16 в единицу. Импульсы, поступающие с входа Ь, инвертируются инвертором 15. По задним фронтам по5 лученных импульсов в четвертый D-триг гер 16 заносится логический нуль. Но, однако, импульсами с входае четвертый D TpHrrep 16 устанавливается в состояние логической единицы, при10 чем в нерабочем и рабочем режимах измерителя (соответственно импульсы на выходе компаратора имеют скважность 2 или сужаются) на инверсном выходе четвертого D-триггера 16, ли15 бо поддерживается состояние логического нуля, либо появляютс я импульсы, укладывающиеся в интервалы между импульсами на выходе инвертора 15. Таким образом, совпадение на входах

20 второго элемента И 14 не происходит и на его выходе поддерживатся постоян но уровень логического нуля.

А по заднему фронту импульса, подаваемого на вход Пуск, в первый

25 D-триггер 9 заносится логическая единица, которая по очередному заднему фронту импульсов, подаваемых на вход Ь, переписывается во второй D-триггер 10. В результате этого начинает30 ся трансляция импульсов с входа Ь на выход С через первый элемент И II. Первый же импульс, прошедший на его выход, установит первый D-триггер 9 в нулевое состояние, которое перепи,. шется и во второй D-трнггер 10 задним фронтом этого же импульса. Б результате на выход С пройдет единственный импульс, который установит счетчики в необходимые состояния и

4Q своим задним фронтом запишет логическую единицу в третий D-триггер 12, после чего начнется трансляция импуль сов с входа Ь на выход d через четвертый элемент И 18. Начнется вы50

третьего элемента И 17, выход которо- 45 полнение грубого подцикла измерений, го подсоединен к выходу i блока 3, а первый вход к входу Ь к которому также подсоединен вход инвертора 15, тактовый вход с второго D-триггера 10, вторые входы первого 11, третьего 1 7 и четвертого 18 элементов И, выход последнего подсоединен к выходу J (счетный вход счетчика), а первый вход к выходу третьего D-триггера 12, функционирует следующим об- 55 мента И 14, поступит логическая единица. В результате чего выходные им- разом,

Перед началом работы В-триггеры с пульсы инвертора 15 будут поступать первого по третий и RS-триггер 13 на выход второго элемента И 14. Тре

в течение которого импульсы на входе.е сужаются и исчезают. При первом же исчезновении импульса на входе е единичное состояние четвертого D-триггера 16 за промежуток между двумя импульсами на выходе инвертора I5 не будет восстановлено, и с инверсного выхода четвертого D-триггера 16 на второй вход второго эле226322

устанавливаются в нули, а четвертый

D-триггер 16 в единицу. Импульсы, поступающие с входа Ь, инвертируются инвертором 15. По задним фронтам по5 лученных импульсов в четвертый D-триггер 16 заносится логический нуль. Но, однако, импульсами с входае четвертый D TpHrrep 16 устанавливается в состояние логической единицы, при10 чем в нерабочем и рабочем режимах измерителя (соответственно импульсы на выходе компаратора имеют скважность 2 или сужаются) на инверсном выходе четвертого D-триггера 16, ли15 бо поддерживается состояние логического нуля, либо появляютс я импульсы, укладывающиеся в интервалы между импульсами на выходе инвертора 15. Таким образом, совпадение на входах

20 второго элемента И 14 не происходит и на его выходе поддерживатся постоянно уровень логического нуля.

А по заднему фронту импульса, подаваемого на вход Пуск, в первый

25 D-триггер 9 заносится логическая единица, которая по очередному заднему фронту импульсов, подаваемых на вход Ь, переписывается во второй D-триггер 10. В результате этого начинает30 ся трансляция импульсов с входа Ь на выход С через первый элемент И II. Первый же импульс, прошедший на его выход, установит первый D-триггер 9 в нулевое состояние, которое перепи,. шется и во второй D-трнггер 10 задним фронтом этого же импульса. Б результате на выход С пройдет единственный импульс, который установит счетчики в необходимые состояния и

4Q своим задним фронтом запишет логическую единицу в третий D-триггер 12, после чего начнется трансляция импуль- сов с входа Ь на выход d через четвертый элемент И 18. Начнется вы

полнение грубого подцикла измерений, мента И 14, поступит логическая единица. В результате чего выходные им- ,

в течение которого импульсы на входе.е сужаются и исчезают. При первом же исчезновении импульса на входе е единичное состояние четвертого D-триггера 16 за промежуток между двумя импульсами на выходе инвертора I5 не будет восстановлено, и с инверсного выхода четвертого D-триггера 16 на второй вход второго элетий о триггер 12 установится в нулевое состояние, а RS-триггер 13 в единичное, т.е. произойдет переключение трансляции импульсов с входа Ь на выход i через третий элемент И 17. Начнется точный подцикл измерения, фактом завершения которого будет появление импульса на входе б . По нему RS-тригг.ер 13 установится в нулевое состояние и трансляция импульсов прекратится.

Формула изобретения

Цифровой измеритель уровня переменного напряжения, содержащий источник постоянного напряжения, компаратор, первый вход которого соединен с с входом формирователя и является входом устройства, второй вход компаратора/подключен к вькоду цифроана- логового преобразователя, цифровые входы которого соединены с выходами реверсивного счетчика, отличающийся тем, что, с целью повышения точности измерения, в него введены счетчик, второй цифрраналоговый преобразователь, логический блок, .. первый вход которого подключен к выходу KOjvfflapaTOpa, второй вход соединен с выходом формирователя, а третий вход подключен к кнопке запуска, второй и третий выходы логического блока соединены с входами реверсивного счетчика, а первый и второй выходы логического блока - с входами введенного счетчика, выходы которого подключены к информационным входам второго цифроаналогового преобразователя, аналоговый вход которого соединен с выходом источника постоянного напряжения, а выход подключен к аналоговому входу первого цифро- аналогового преобразователя, кроме того, информационные входы цифроана- логовых преобразователей также соединены с вычислительным

Jtycn

фчг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем линейных алгебраических уравнений | 1984 |

|

SU1187157A1 |

| Аналого-цифровой преобразователь параметров диэлькометрического датчика | 1988 |

|

SU1547063A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Устройство для программного регулирования температуры | 1987 |

|

SU1541572A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| Следящий аналого-цифровой преобразователь | 1985 |

|

SU1283971A1 |

| ЛАЗЕРНЫЙ ДАТЧИК УЛЬТРАЗВУКОВЫХ КОЛЕБАНИЙ | 1992 |

|

RU2036415C1 |

| Емкостный уровнемер | 1987 |

|

SU1582020A1 |

| Следящий аналого-цифровой преобразователь | 1990 |

|

SU1757101A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКИ КОНТРАСТНОСТИ ВИДЕОСИГНАЛА | 1991 |

|

RU2037974C1 |

Изобретение относится к измерениям в технике связи. Цель изобретения - повышение точности измерений. Устройство содержит компаратор 1, формирователь 2, логический блок 3, счетчик 4, реверсивный счетчик 5, цифроаналоговые преобразователи ЦАЛ 6 и 8 и источник 7 постоянного напряжения. Введение в устройство счетчика ЦАП 8, логического блока и образование новых связей между элементами устройства позволяет проводить два подцикла.измерения (грубого и точного) преобразования. Причем ЦАП 6, производя подцикл грубого преобразования, дает возможность ЦАП 8 произвести подцикл точного преобразования, при котором амплитуда входного переменного сигнала близка к напряжению на аналоговом входе ЦАЛ 8. В описании дана принципиальная схема логического блока. 2 ил. Л 3Bf1 С (О (Л

Редактор Р.Цицика

Составитель В.Шубин Техред Л.Олейник

Заказ 2125/42 Тираж 728Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

.-Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор Л.Патай

| Патент США № 4194185, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ПРИБОР ДЛЯ ОПРЕДЕЛЕНИЯ ЖЕСТКОСТИ КАРТОНА ПРИ ИЗГИБЕ | 1972 |

|

SU426191A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-04-23—Публикация

1984-10-22—Подача