Изобретение относится к системам автоматического управления и может быть использовано для связи регулятора и оператора с исполнительным механизмом. ™

Известны устройства регулирования, в которых аналого-цифровое преобразование используется (в зависимости от режима управления) для воспроизведения аналогового сигнала, его хранения или ручного изменения с обеспечиваем безударности при переключении режимов управления.

Известны аналого-цифровые преобразователи (АЦП) следящего типа, которые могут быть использованы в системах управления.

Недостатком указаннь-х устройств является отсутствие в них регулируемых ограничителей уровня выходного сигнала, необходимость в которых возникает при сопряжении устройств управления с регулируемыми объектами и вызывается особенностями объектов или их регулирующих органов

Наиболее близким по технической сущности к. заявляемому является следящий АЦП, содержащий генератор импульсов, реверсивный счетчик, цифроаналоговый преобразователь, преобразующий состояние Счетчика в аналоговый сигнал, компаратор, на один зход которого подан входной аналоговый сигнал, а на другой - выходной сигXJ

«дед

ВЯСГП&

нал цифроаналогового преобразователя, который является одновременно выходным сигналом устройства. Выходной сигнал компаратора через устройство управгьния поступает на вход Напразление счета реверсивного счетчика.

Описанный АЦП не имеет ограничителей верхнего и нижнего уровней выходного сигнала. Кроме того, при использовании такого АЦП в системах управления проявляет- ся следующий недостаток: если на вход АЦП подан сигнал, которому соответствует состояние реверсивного) счетчика, близкое к переполнению (сигнал, близкий к нулю или к максимальному), даже при незнэчитель- ном сигнале помехи на входе АЦП происходит переполнение счетчика, чему соответствует автоколебательный режим, недопустимый в системах управления.

Цель изобретения - расширение обла- сти применения за счет возможности функционирования в системах управления, чувствительных к автоколебательным режимам.

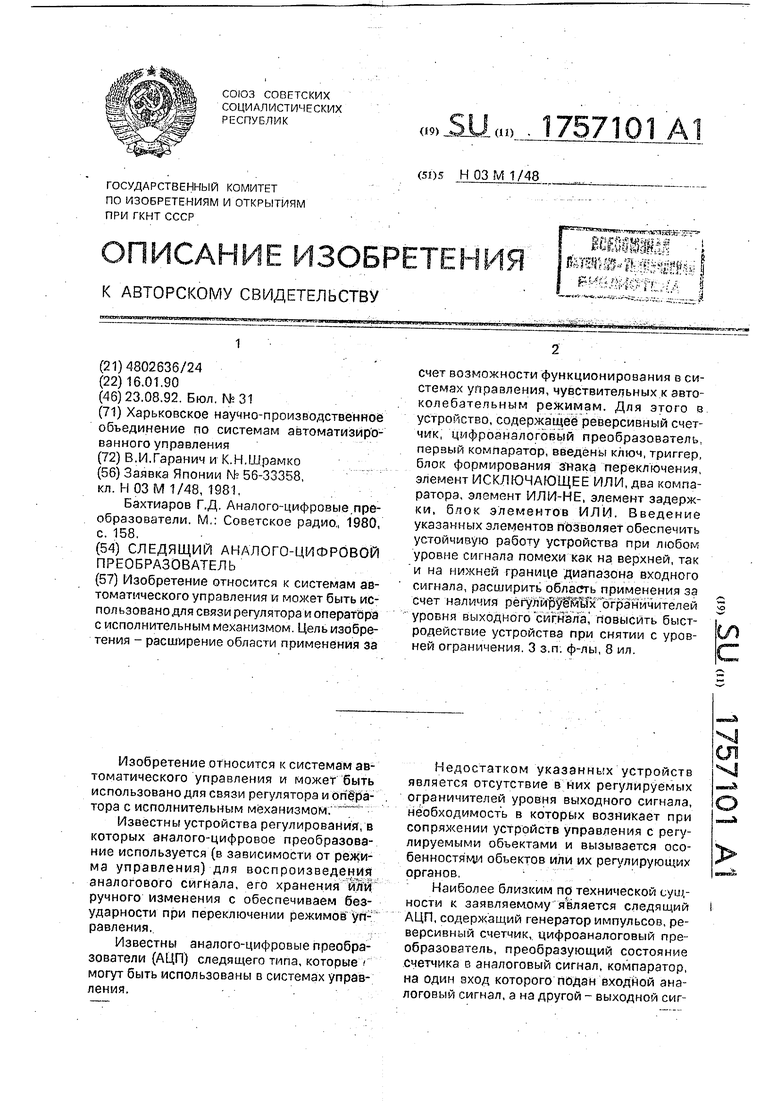

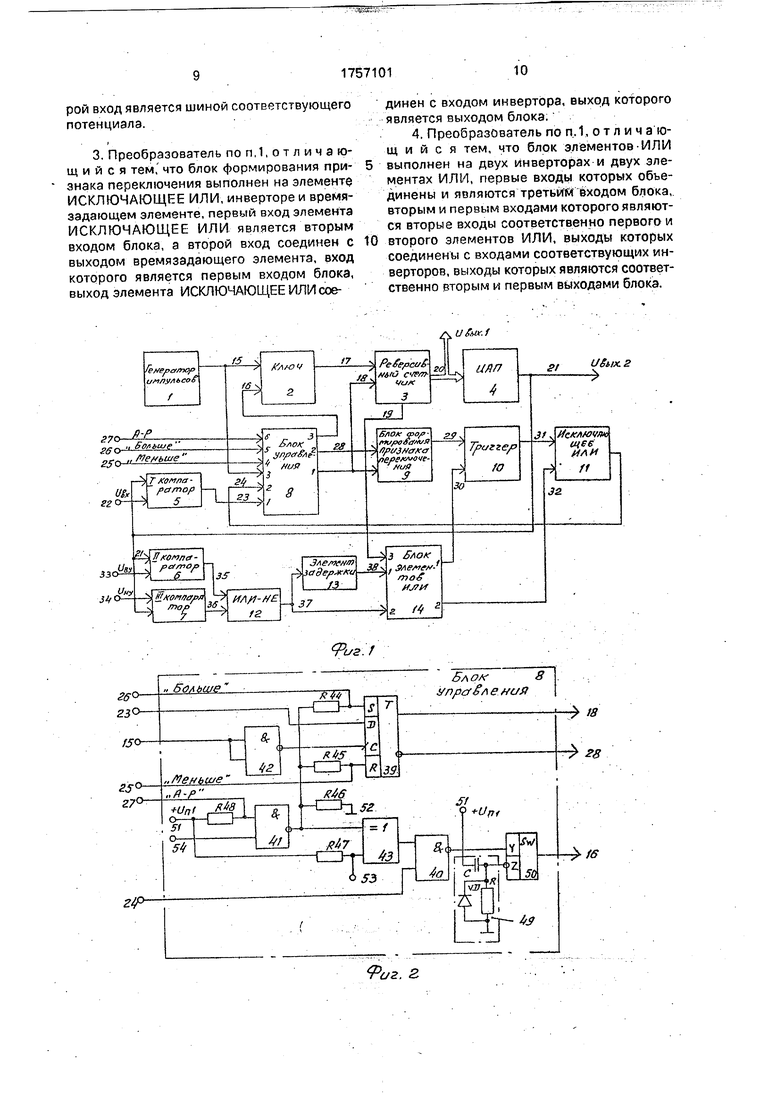

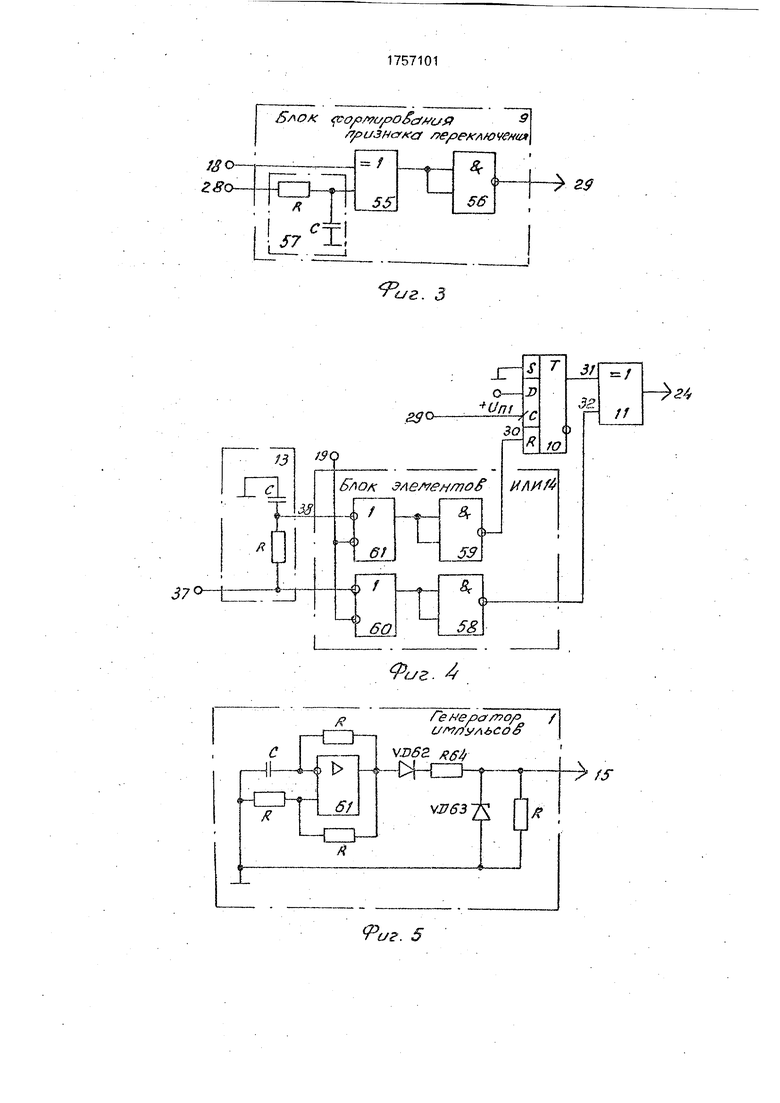

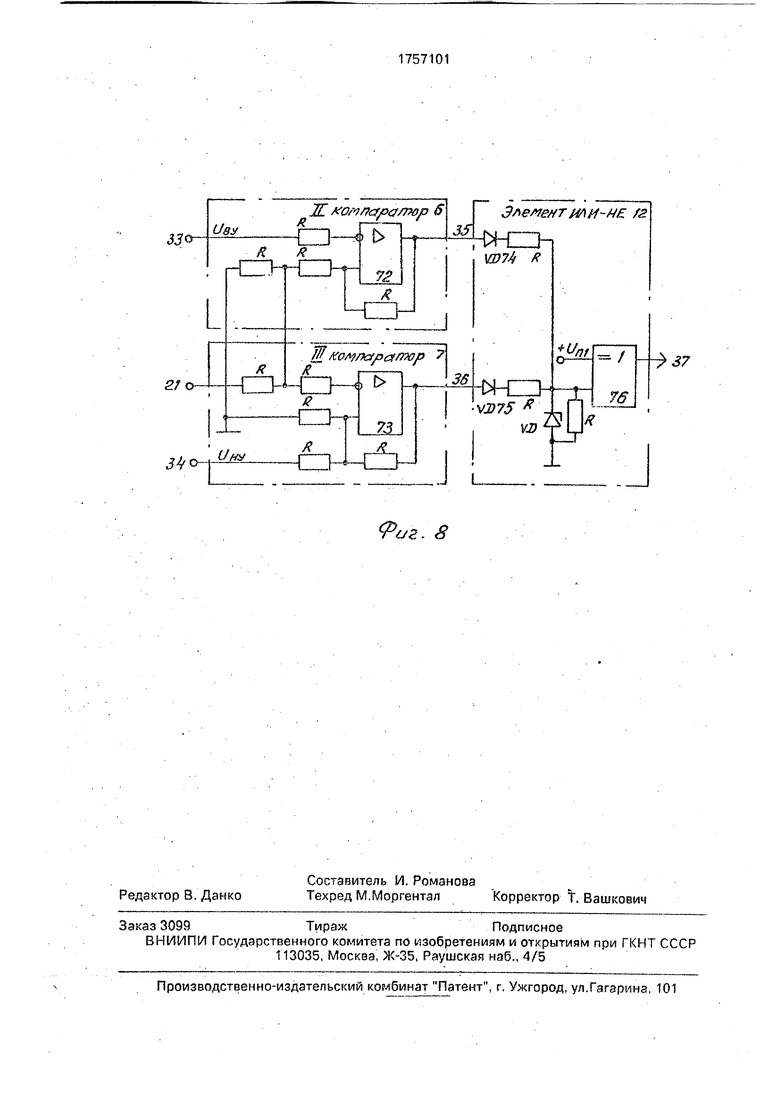

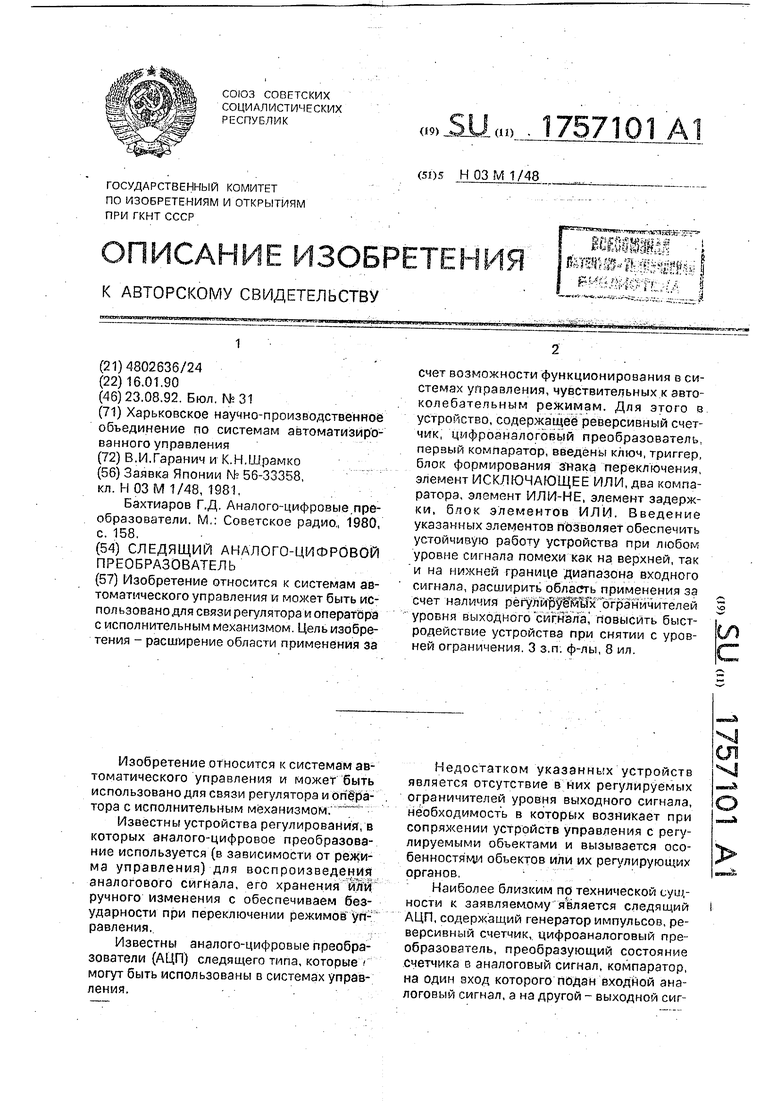

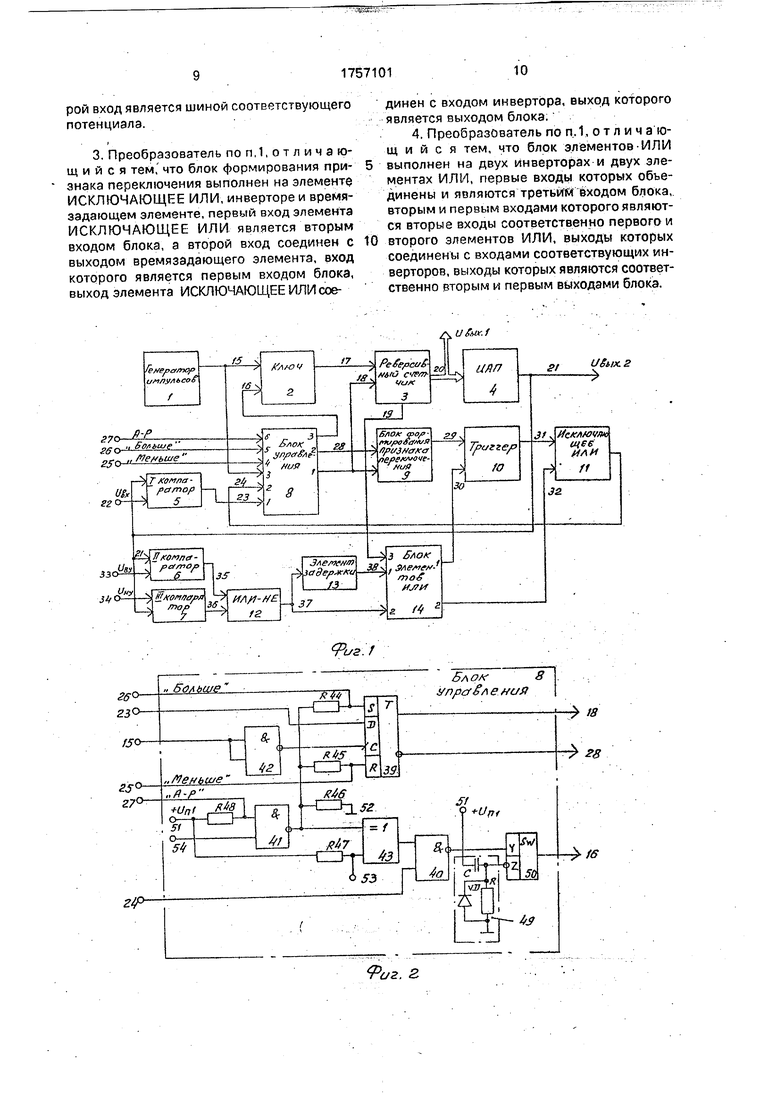

На фиг. 1 представлена структурная схе- ма следящего АЦП; на фиг, 2 - функциональная схема блока управления; на фиг. 3 - функциональная схема блока формирования признака переключения; на фиг. 4 - функциональная схема блока элементов ИЛИ; на фиг. 5 - функциональная схемз генератора импульсов; на фиг. 6 - функцио нальная схема реверсивного счетчика; на фиг. 7 - функциональная схема ЦАП; на фиг. 8 - функциональная схема второго и треть- его компараторов и элемента ИЛИ-НЕ.

Следящий АЦП (фиг. 1) содержит генератор 1 импульсов, ключ 2, реверсивный счетчик 3, ЦАП 4, первый 5, второй 6 и третий 7 компараторы, блок 8 управления, блок 9 формирования признака переключения, триггер 10, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11, элемент ИЛИ-НЕ 12, элемент 13 задержки, блок элементов ИЛИ 14.

На фиг. 1 обозначено: 15 и 16 - ин- формационный и управляющий входы ключа 2 соответственно; 17 - счетный вход; 18 - вход направления счета реверсивного счетчика 3; 19 - выход переполнения реверсивного счетчика 3; 20 - цифровые выхо- ды реверсивного счетчика 3, которые являются I выходной шиной устройства; 21 - аналоговый выход ЦАП 4, который является И выходной шиной устройства; 22 - зход- ная информационная шина, которая соединена с вторым входом первого компаратора 5; 23 и 24 - первый и второй входы блока 8 управления соответственно; 25- 27 входы управления устройства, которые соединены с четвертым, пятым и шестым вхрдами блока 8 управления соответственно;

28- второй выход блока 8 управления;

29и 30 - входы установки в единицу и в ноль триггера 10 соответственно; 31 - выход триггера 10; 32-первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ; 33 и 34 - шины управления верхним и нижним уровнями ограничения выходного сигнала соответственно, которые соединены с вторым входом второго компаратора бис первым входом третьего компаратора 7 соответственно; 35- 37 - первый, второй входы и выход элемента ИЛИ-НЕ 12 соответственно; 38 - выход элемента 13 задержки.

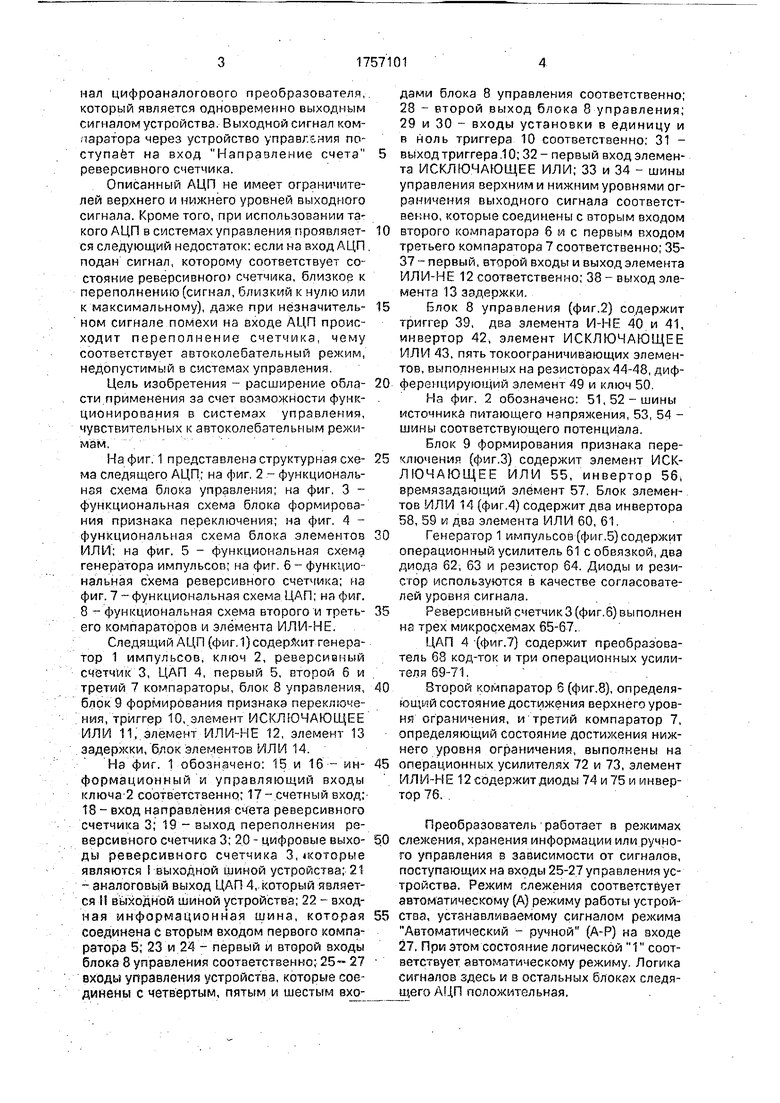

Блок 8 управления (фиг,2) содержит триггер 39, два элемента И-НЕ 40 и 41, инвертор 42, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 43, пятьтокоограничивающих элементов, выполненных на резисторах 44-48, дифференцирующий элемент 49 и ключ 50

На фиг. 2 обозначено: 51, 52-шины источники питающего напряжения, 53, 54 - шины соответствующего потенциала.

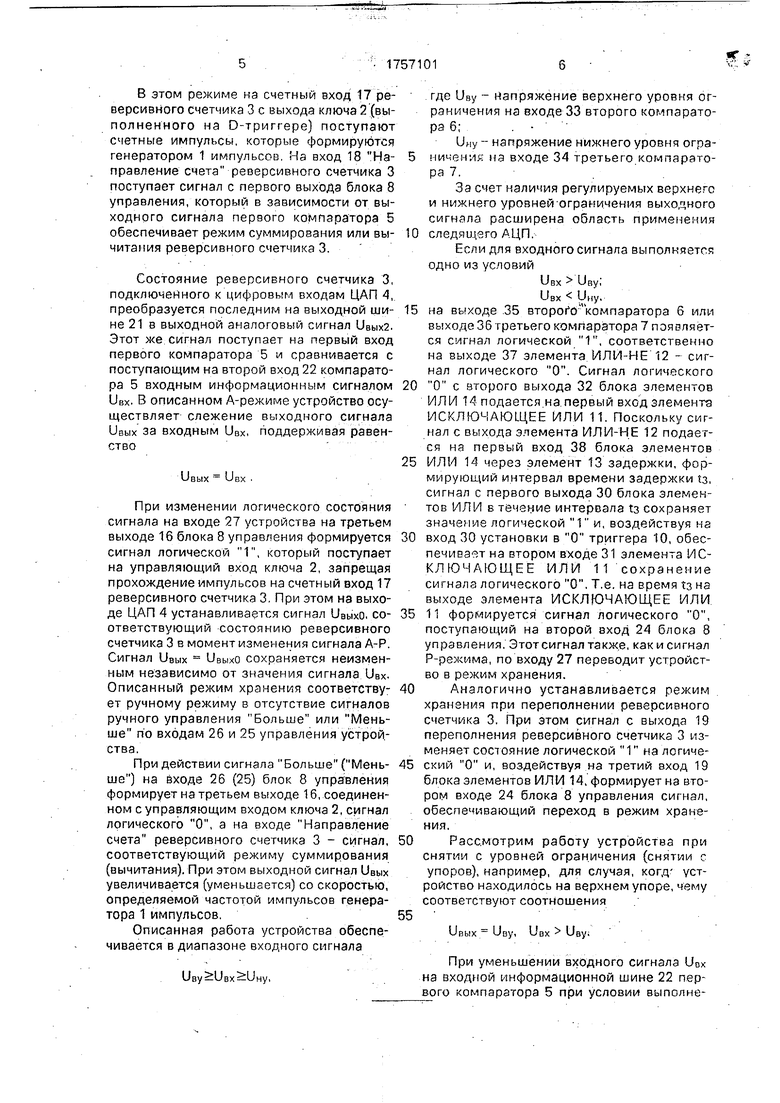

Блок 9 формирования признака переключения (фиг.З) содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 55, инвертор 56, времязздающий элемент 57, Блок элементов ИЛИ 14 (фиг.4) содержит два инвертора 58, 59 к два элемента ИЛИ 60, 61,

Генератор 1 импульсов (фиг.5) содержит операционный усилитель 61 с обвязкой, два диода 62, 63 и резистор 64. Диоды и резистор используются в качестве согласовате- лей уровня сигнала.

Реверсивный счетчик 3 (фиг.6} вы полней на трех микросхемах 65-67.

ЦАП 4 (фиг.7) содержит преобразователь 68 код-ток и три операционных усилителя 69-71,

Второй компаратор 6 (фиг.8), определяющий состояние достижения верхнего уровня ограничения, и третий компаратор 7, определяющий состояние достижения нижнего уровня ограничения, выполнены на операционных усилителях 72 и 73, элемент ИЛИ-НЕ 12 содержит диоды 74 и 75 и инвертор 76.

Преобразователь работает в режимах слежения, хранения информации или ручного управления в зависимости от сигналов, поступающих на входы 25-27 управления устройства. Режим слежения соответствует автоматическому (А) режиму работы устройства, устанавливаемому сигналом режима Автоматический - ручной (А-Р) на входе 27, При этом состояние логической 1 соответствует автоматическому режиму. Логика сигналов здесь и в остальных блоках следящего АЦП положительная,

В этом режиме на счетный вход 17 реверсивного счетчика 3 с выхода ключа 2 (выполненного на D-триггере) поступают счетные импульсы, которые формируются генератором 1 импульсов. На вход 18 Направление счета реверсивного счетчика 3 поступает сигнал с первого выхода блока 8 управления, который в зависимости от выходного сигнала первого компаратора 5 обеспечивает режим суммирования или вычитания реверсивного счетчика 3.

Состояние реверсивного счетчика 3, подключенного к цифровым входам ЦАП А, преобразуется последним на выходной шине 21 в выходной аналоговый сигнал ивых2. Этот же сигнал поступает на первый вход первого компаратора 5 и сравнивается с поступающим на второй вход 22 компаратора 5 входным информационным сигналом UBX. В описанном А-режиме устройство осуществляет слежение выходного сигнала ивых за входным DBX, поддерживая равенство

UBBIX UBX .

При изменении логического состояния сигнала на входе 27 устройства на третьем выходе 16 блока 8 управления формируется сигнал логической 1, который поступает на управляющий вход ключа 2, запрещая прохождение импульсов на счетный вход 17 реверсивного счетчика 3. При этом на выходе ЦАП 4 устанавливается сигнал УвыхО, соответствующий состоянию реверсивного счетчика 3 в момент изменения сигнала А-Р. Сигнал Квых Увыхо сохраняется неизменным независимо от значения сигнала UBX. Описанный режим хранения соответствует ручному режиму в отсутствие сигналов ручного управления Больше или Меньше по входам 26 и 25 управления устройства.

При действии сигнала Больше (Меньше) на входе 26 (25) блок 8 управления формирует на третьем выходе 16, соединенном с управляющим входом ключа 2, сигнал логического О, а на входе Направление счета реверсивного счегчика 3 - сигнал, соответствующий режиму суммирования (вычитания). При этом выходной сигнал ивых увеличивается (уменьшается) со скоростью, определяемой частотой импульсов генератора 1 импульсов.

Описанная работа устройства обеспечивается в диапазоне входного сигнала

ну,

где UBy - напряжение верхнего уровня ограничения на входе 33 второго компаратора 6;

UHy - напряжение нижнего уровня огра- 5 ниченик на входе 34 третьего компаратора 7.

За счет наличия регулируемых верхнего и нижнего уровней ограничения выходного сигняла расширена область применения 0 следящего АЦП.

Если для входного сигнала выполняется одно из условий

UBX Uayl UBX Uny.

5 на выходе 35 второго компаратора 6 или выходе 36 третьего компаратора 7 появляется сигнал логической 1, соответственно на выходе 37 элемента ИЛИ-НЕ 12 - сигнал логического О. Сигнал логического

0 О с второго выхода 32 блока элементов ИЛИ 14 подается на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11. Поскольку сигнал с выхода элемента ИЛИ-НЕ 12 подается на первый вход 38 блока элементов

5 ИЛИ 14 через элемент 13 задержки, формирующий интервал времени задержки ta, сигнал с первого выхода 30 блока элементов ИЛИ в течение интервала ts сохраняет значение логической 1 и, воздействуя на

0 вход 30 установки в О триггера 10, обеспечивает на втором входе 31 элемента ИС- КЛЮЧАЮЩЕЕ ИЛИ 11 сохранение сигнала логического О. Т.е. на время t3 на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

5 11 формируется сигнал логического О, поступающий на второй вход 24 блока 8 управления. Этот сигнал также, как и сигнал Р-режима, по входу 27 переводит устройство в режим хранения.

0 Аналогично устанавливается режим хранения при переполнении реверсивного счетчика 3. При этом сигнал с выхода 19 переполнения реверсивного счетчика 3 изменяет состояние логической 1 на логиче5 ский О и, воздействуя на третий вход 19 блока элементов ИЛИ 14, формирует на втором входе 24 блока 8 управления сигнал, обеспечивающий переход в режим хранения,

0 Рассмотрим работу устройства при снятии с уровней ограничения (снятии с упоров), например, для случая, когд устройство находилось на верхнем упоре, чему соответствуют соотношения

5

Ufibix Uay, UBX иву.

При уменьшении входного сигнала UDx на входной информационной шине 22 первого компаратора 5 при условии выполнеимя неравенства UBx UBy, выходной сигнал первого компаратора 5, действующий на первом входе 23 блока Вупрэвлени 1, вызывает изменение состояния первого 18 и второго 28 выходов блока 8 управления, воздействуя на блок 9 формирования признака переключения. Последний формирует короткий импульс, который подается из вход 29 установки в 1 триггера 10, в результате чего на выходе триггера 10 и на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 устанавливается сигнал логической 1. Последний переводит устройство в режим спе- жения, Аналогично происходит снятие с упора.

Таким образом, для устройства справедливы выражения

UE

UBX при

Увых UBy при UBX UBy;

ивых UHy при UBX U

ну.

Формула изобретения 1, Следящий аналого-цифровой преобразователь, содержащий генератор импульсов, последовательно соединенные реверсивный счетчик, цифроаналоговый преобразователь и первый компаратор, второй вход которого является входной информационной шиной, а выход соединен с первым входом блока управления, первый выход которого соединен с входом Направление счета реверсивного счетчика, отличающийся тем, что, с целью расширения области применения за счет возможности функционирования в системах управления, чувствительных к автоколебательным рожи- мам, в преобразователь введены ключ, триггер, блок формирования признака переключения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй м третий компараторы, элемент ИЛИ-НЕ, элемент задержки и блок эле- ментов ИЛИ, первый вход которого соединен с выходом элемента задержки, второй вход обьединен с входом элемента задержки и подключен к выходу элемента ИЛИ-НЕ, третий вход соединен с выходом переполнения реверсивного счетчика, а первый и второй выходы соединены соответственно с входом установки в О триггера и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом триггера, выход - С вторым входом блока управления, третий вход которого объединен с информационным входом ключа и соединен с выходом генератора импульсов, входы с четвертого по шестой блока управления являются соответствующими входами управления преобразователя, а второй и третий выходы соединены соответственно с первым входом блока формирования признака

переключения и управляющим входом ключа, выход которого соединен со счетным входом реверсивного счетчика, первый выход блока управления соединен с вторым входом блока формирования признака пе0 реключения, выход которого соединен с входом установки в 1 триггера, первый и второй входы элемента ИЛИ-ИЕ соединены соответственно с выходами второго и третьего компараторов, неинвертирующий вход

5 второго и инвертирующий вход третьего компараторов объединены и подключены к выходу цифрозналогового преобразователя, а инвертирующий вход второго компаратора и неинвертирующий вход третьего

0 компаратора являются шинами управления уровнями ограничения выходного сигнала, выходы реверсивного счетчика являются первой выходной шиной, а выход цифроана- логового преобразователя является второй

5 выходной шиной,

2. Преобразователь по п.1, о т л и ч а ю- щ и и с я тем, что блок управления выполнен на триггере, двух элементах И-НЕ, инверторе, элементе ИСКЛЮЧАЮЩЕЕ ИЛИ, пяти

0 юкосграничивающих элементах, выполненных на резисторах, дифференцирующем элементе и ключе, выход которого является третьим выходом блока управления, информационный вход ключа соединен с выходом

5 первого элемента И-НЕ, а управляющий вход через дифференцирующий элемент соединен с источником питающего напряжения, первый вход первого элемента И-НЕ соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ

0 ИЛИ, а второй вход является вторым входом блока управления, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом второго элемента И-НЕ и через резисторы с шиной соответствующего потенциала ис5 точника питания, с S-входом и с R-входом триггера, второй вход элемента ИСКЛЮЧА- ОЩЕЕ ИЛИ является шиной соответствующего потенциала и через резистор соединен с источником питающего напряжения, S0 вход триггера является пятым входом блока управления, R-вход - четвертым входом, D- вход первым входом, а С-вход соединен с выходом инвертора, вход которого является третьим входом блока управления, прямой

5 и инверсный выходы триггера являются соответственно первым и вторым выходами блока управления, первый вход второго элемента И-НЕ является шестым входом блока управления и через резистор соединен с источником питающего напряжения, а второй вход является шиной соответствующего потенциала.

3, Преобразователь по п, 1, о т л и ч а ю- щ и и с я тем, что блок формирования признака переключения выполнен на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ, инверторе и время- задающем элементе, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является вторым входом блока, а второй вход соединен с выходом времязадающего элемента, вход которого является первым входом блока, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ ссе0

динен с входом инвертора, выход которого является выходом блока.

4. Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что блок элементов ИЛИ выполнен на двух инверторах и двух элементах ИЛИ, первые входы которых объединены и являются третьим входом блока, вторым и первым входами которого являются вторые входы соответственно первого и второго элементов ИЛИ, выходы которых соединены с входами соответствующих инверторов, выходы которых являются соответственно вторым и первым выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регулирования температуры | 1986 |

|

SU1403025A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1987 |

|

SU1441479A1 |

| Цифровой измеритель добротности | 1988 |

|

SU1647456A1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С ФОРСИРОВКОЙ И КОРРЕКТОРОМ ПАРАЛЛЕЛЬНОЙ РАБОТЫ | 2023 |

|

RU2811685C1 |

| Устройство для моделирования петли гистерезиса | 1985 |

|

SU1305727A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2024194C1 |

| Преобразователь сигналов датчиков переменного тока | 1986 |

|

SU1332531A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1102036A2 |

| Реверсивный аналого-цифровой преобразователь | 1988 |

|

SU1612373A1 |

Изобретение относится к системам автоматического управления и может быть использовано для связи регулятора и оператора с исполнительным механизмом Цель изобретения - расширение области применения за счет возможности функционирования в системах управления, чувствительных к автоколебательным режимам. Для этого э устройство, содержащее реверсивный счетчик, цифроаналоговый преобразователь первый компаратор, введены ключ, триггер, блок формирования знака переключения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два компаратора, элемент ИЛИ-НЕ, элемент задержки, бток элементов ИЛИ. Введение указанных элементов позволяет обеспечить устойчивую работу устройства при любом уровне сигнала помехи как на верхней, так и на нижней границе диапазона входного сигнала, расширить область применения за счет наличия регулир еТйьТх ограничителей уровня выходного сигнала, повысить быстродействие устройства при снятии с уровней ограничения 3 з.п. ф-лы, 8 ил (Л

S70

гео

250

Фиг /

26®

23 О

Јfa

U&u-f

Блок8

упраЈ/ ения

$ 28

Фиг. г

13

л о

/i(9/r элелгем/яяб

J7o-|----+--Р

/

Фиг. 3

+ YC

30

ЗЯ s

о

//

ю

ИАИМ

/г. 4

Гене/за/ко/о / иплульсоб

Фиг. 5

Фиг. 6

Фиг. 7

Uey

R К

Ж 6

I-„,-..,- .,,., Г

t

72

L

ЛKo/y/ c{/ cfim/ Л fL, I

жи

Элемент te

№74 К

W

w

- /

Фиг. 8

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Бахтиаров Г.Д Аналого-цифровые преобразователи | |||

| М : Советское радио, 1980, с | |||

| Система механической тяги | 1919 |

|

SU158A1 |

Авторы

Даты

1992-08-23—Публикация

1990-01-16—Подача