1

Изобретение относится к области вычислительной техники, в частности к приоритетным устройствам, и может быть использовано для организации прерывания программ.

Цель изобретения - повьнцеиие быстродействия за счет двухфазной об- ,работки сигнала запроса.

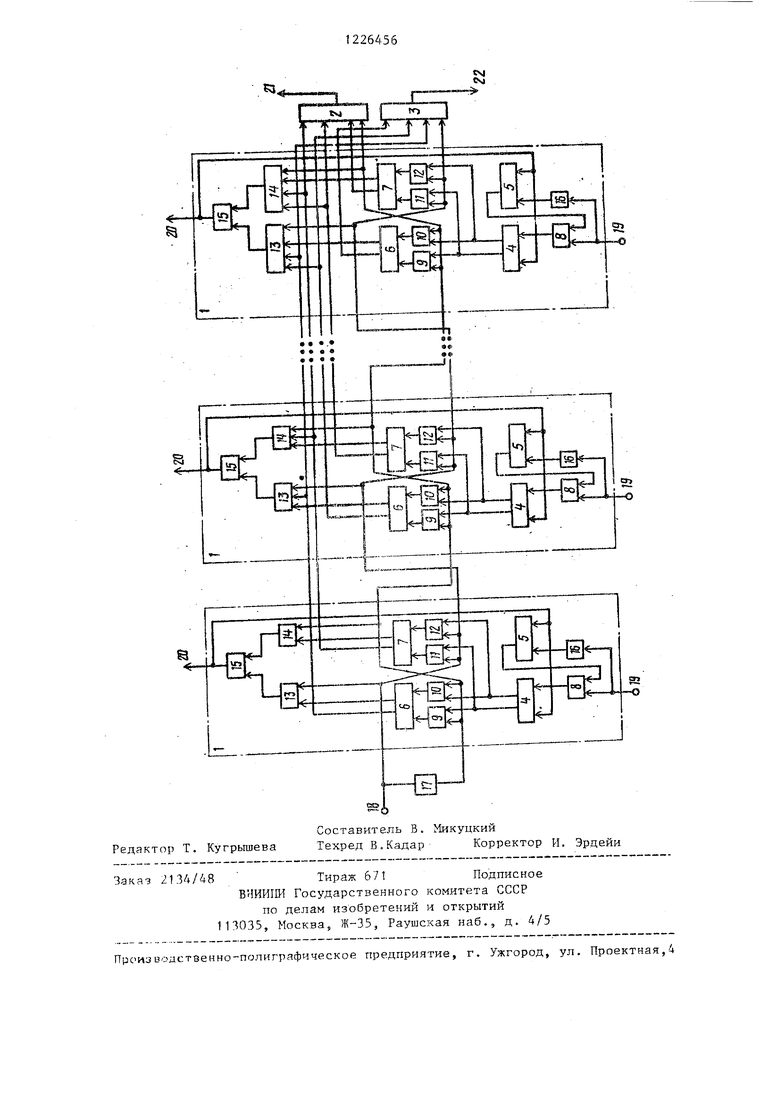

На чертеже представлена функциональная схема устройства.

Устройство содержит каналы 1,, элементы И 2 и 3,, триггеры 4-7 элементы И 8-14, элементы ИЛИ 15, элементы НЕ 16 и 17, тактовый вход 18, запросные входы 19, информационные выходы 20, тактовые выходы 27 и 28.

Устройство работает следующим образом.

На тактовый вход 18 поступает серия синхроимпульсов фазы F . На вы- ходе элемента НЕ 17 формируется инверсная синхросерия фазы F .. Перед началом работы на общую шину сброса (не показана) поступает импульс, который устанавливает триггеры 4-7 каждого из каналов в исходное нулевое состояние, образуя, при отсутствии запросных сигналов по входам 20, цепь сквозного переноса импульсов синхронизации фазы FY с входа 18 через элемент НЕ 17 и элемент И 2 на первый тактовый выход 21 и цепь сквозного переноса импульсов фазы F с входа 18 через элемент И 19 на второй тактовый

выход 22.

Предположим, что на запросные. , входы 19 всех трех каналов одновременно поступают сигналы запроса, В каждом канале сработает элемент И 8 и установит соответствующий триггер 4 в состояние 1. Для определенности на временной диаграмме будем считать, что запросные сигналы возникают в фазе синхросигнала

С задержкой на время срабатывания элементов И 10 установятся в состояние 1 триггеры 6 всех каналов 1. В hepBOM канале триггер 6 подает разрешающий сигнал на элемент И 13 своего канала и запрещает работу элементов И 13 всех последующих кангшов Далее импульс синхронизации фазы F открывает элемент И 13 первого канал и через элемент И 12 устанавливает в 1 триггеры 7 всех каналов, принявших запросы. Сигнал с выхода элемента И 13 через элемент ИЛИ 15

5

0 5

0

5

0 5

0 j

56

тупает на соответствующий выход 2С устройства, одновременно устанавли вая триггер 5 первого канала 1 в состояние , а триггер 4 - в состояние О. Последний подготавливает к открытию элемент И 9 и через элемент И 11 устанавливает в. О триггер 7 первого канала 1.

Триггер 7 второго канала 1 разрешает работу элемента И 14 своего канала, блокируя элементы И 14 после- каналов и элемент И 2. Синхроимпульс фазы F с выхода элемента И 14 через элемент И 15 второго канала 1 поступает на информационный выход 20, одновременно устанавливая в состояние 1 триггер 5 и в состояние О Триггер 4. Последний подготавливает к открытию элемент И 11 и устанавливает триггер 6 через элемент И 9 в исходное нулевое состояние, разрешая работу элемента И 13 следующего канала и выходного элемента И 3. Синхроимпульс фазы F -с выхода элемента И 13 третьего канала 1 через элемент ИЛИ 15 поступает на выход 20 и на входы триггеров 4 и. 5 своего канала. Триггер 4 устанавливается в состояние О, подготавливая к открытию элемент И 9 и устанавливая через элемент И 11 триггер 7 в состояние О. Последний деблокирует элемент И 14 своего канала и выходной элемент И 2.

Очередной импульс синхросерии фазы Fj через элемент И 9 канала производит сброс в исходное нулевое состояние триггера 6.Происходит разблокировка элемента И 13 канала и элемента И 3.

Таким образом, на первом тактовом выходе 21 и втором тактовом выходе 22 вычеркивается столько импульсов, сколько запросов поступает на .это время в устройство.

Очевидно, что устройство всегда выполняет свою функцию приоритетной селекции путем вычеркивания синхронизирующего импульса положительной либо с)трицательнэй фазы синхросерии время селекции всегда меньше периода, а в случае, когда поступили все запросы, время селекции возрастает в два раза.

Формула изобретения

Многоканальное устройство для приоритетной селекции импульсов,содержащее элемент НЕ и и каналов (п - число запросов), а в каждом канале три триггера, пять элементов И и элемент НЕ, причем в каждом канале запросньш вход.устройства соединен с первым входом первого элемента И и через элемент НЕ - с входом установки в ноль первого триггера, инверсный выход которого соединен с вторым входом первого элемента И, выход которого соединен с входом установки в 1 второго триггера, причем информационный выход каждого канала соединен с входами установки в 1 и в О соответственно первого и второго триггеров,а прямой и инверсный выходы второго триггера соединены с первыми входами соответственно второго и третьего элементов И, выходы второго и третьего элементов И соединены с входами установки в 1 и в О третьего триггера соответственно, при этом прямой выход третьего триггера соединен с первым входом четвертого элемента И, а тактовый вход устройства соединен с вторым входом четвертого элемента И первого канала, с первым входом пятого элемента И первого канала и с входом элемента НЕ, выход которого соединен с вторыми входами второго и третьего элементов И первого канала, отличающееся тем, что, с целью повышения быстродействия устройства, оно дополнительн о содержит два элемента И, а в каждом канале триггер, два элемента И и элемент ИЛИ, причем i-и вход (где i 1 - (h-1)j первого

5

элемента И соединен с инверсным выходом ч етвертого триггера -го канала и с соответствующим входом шестого элемента И J-го канала (где J (i+1)-h), ь,-и вход первого элемента И соединен с инверсным выходом четвертого триггера и -го канала, (л+1)-й вход первого элемента И соединен с вторыми входами второго и третьего элементов И всех каналов и соответствующими входами шестых элементов И всех каналов, i-ый вход второго элемента И соединен с инверсным выходом третьего триггера i-го канала и с соответствующим входом четвертого элемента И J -го канала, п -и вход второго элемента И соединен с инверсным выходом третьего триггера h-го канала (и+1)-й вход второго элемента И устройства соединен с соответствующими входами четвертых элементов И всех каналов и с первыми входами пятого и шестого элементов И каждого кана5 ла, вторые входы которых подключены соответственно к инверсному и прямому выходам второго триггера канала, в каждом канале выходы четвертого и шестого элементов И соединены с со0 ответствующими входами элемента ИЛИ, выход которого является информационным выходом устройства, при этом прямой выход четвертого триггера каждого канала подключен к соответствующему входу шестого элемента И канала, а выходы первого и второго элементов И устройства являются первым и вторым тактовыми выходами устройства соответственно.

0

5

53

Изобретение относится х области вычислительной техники. Цель изобретения - повышение быстродействия. С этой целью устройство дополнительно содержит два элемента И и в каждом канале триггер, Два элемента И и элемент ИЛИ. С соответствующими связями это устройство позволяет повысить быстродействие за счет двухфазной обработки сигнала запроса. Устройство может быть использовано для организации прерывания программ. 1 ил. (Л С ю к О5 ел О5

Редактор Т. Кугрьпиева

Составитель В. Микуцкий

Техред В.Кадар Корректор И. Эрдейи

Заказ 21 ЗА/48Тираж 671Подписное

ВЧИИ1Ш Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

| Многоканальное устройство дляпРиОРиТЕТНОй СЕлЕКции иМпульСОВ | 1979 |

|

SU817712A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для приоритетной селекции импульсов | 1975 |

|

SU607217A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-23—Публикация

1984-01-05—Подача