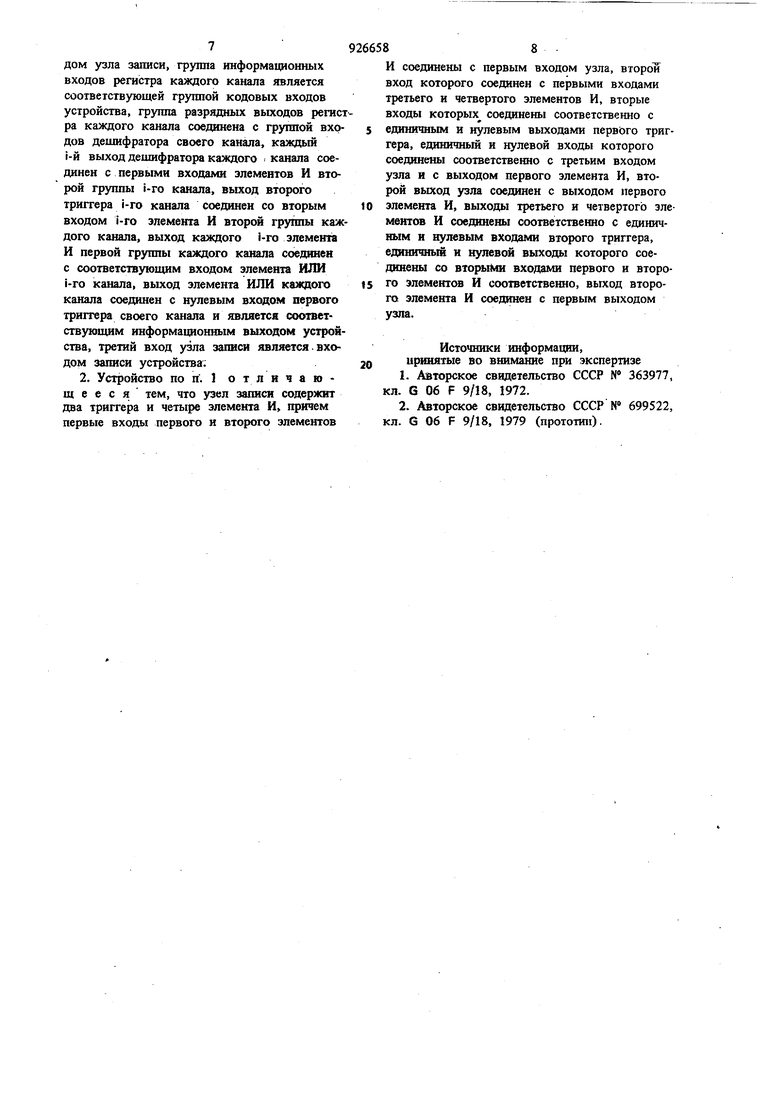

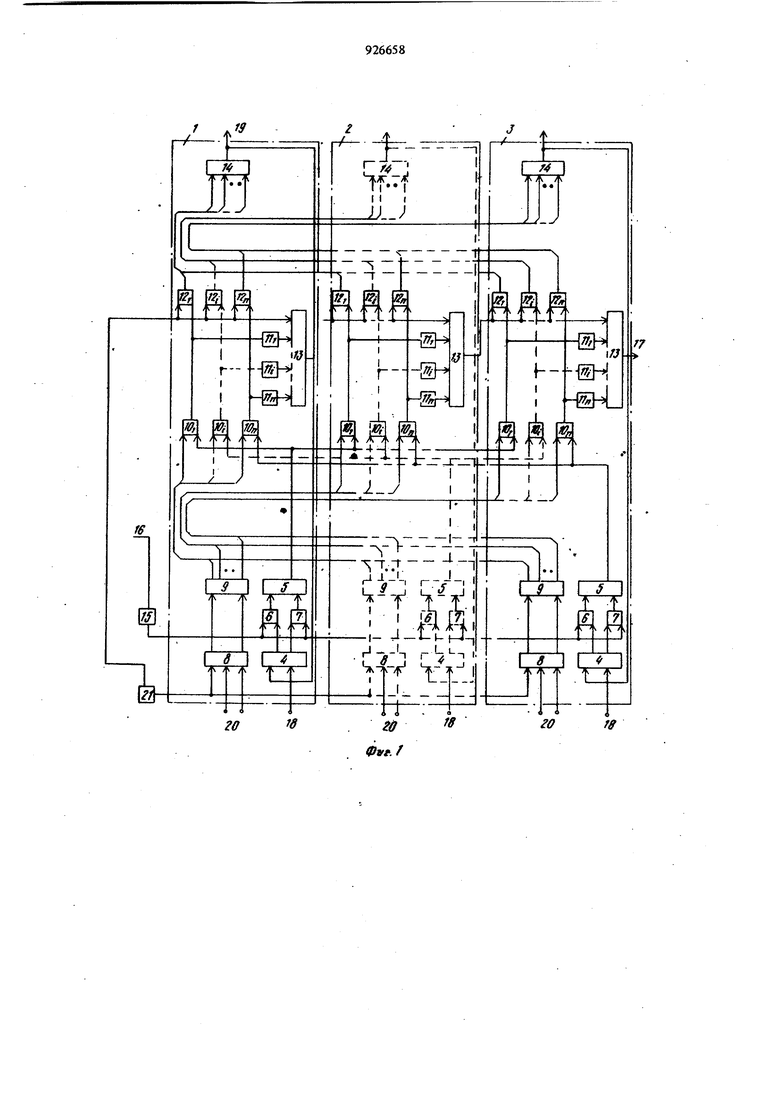

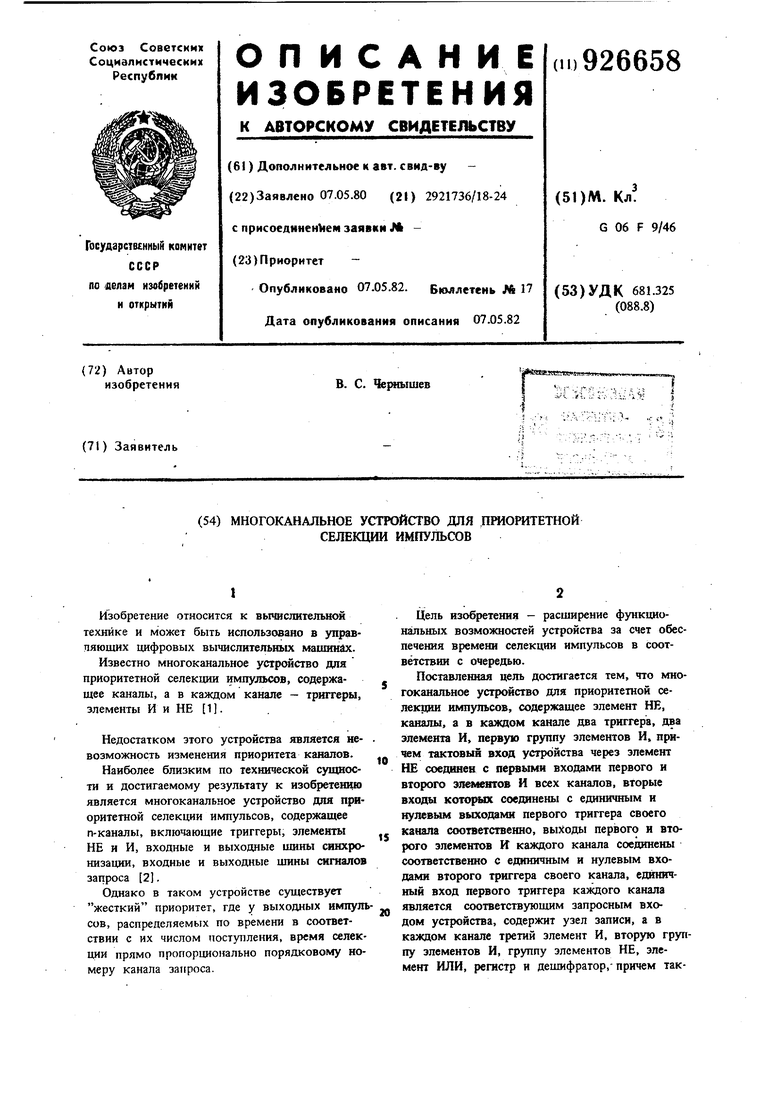

Изобретение относится к вычислительной технике и может быть использовано в управляющих цифровых вычислительных машинах. Известно многоканальное устройство для приоритетной селекции импульсов, содержащее каналы, а в каждом канале - триггеры, элементы И и НЕ 1. Недостатком этого устройства является невозможность изменения приоритета каналов. Наиболее близким по технической сущности и достигаемому результату к изобретению является многоканальное устройство для приоритетной селекции импульсов, содержащее п-каналы, включающие триггеры, элементы НЕ и И, входные и выходные шины синхронизации, входные и выходные шины сигналов запроса 2. Однако в таком устройстве существует жесткий приоритет, где у выходных импул СОВ, распределяемых по времени в соответствии с их числом поступления, время селекЩ1И прямо пропорционально порядковому номеру канала запроса. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения времени селекции импульсов в соответствии с очередью. Поставленная цель достигается тем, что многоканальное устройство для приоритетной селекции импульсов, содержащее элемент НЕ, каналы, а в каждом канале два триггера, два элемента И, первую группу элементов И, причем тактовый вход устройства через элемент НЕ соединеи с первыми входами первого и второго элементов И всех каналов, вторые входы которых соединены с единичным и нулевым выходами первого триггера своего канала соответственно, выходы первого и второго элементов И каждого канала соедннены соответственно с единичным и нулевым входами второго триггера своего канала, единичный вход первого триггера каждого канала является соответствующим запросным входом устройства, содержит уэел записи, а в каждом канале третий элемент И, вторую группу элементов И, группу элементов НЕ, элемент ИЛИ, регистр и дешифратор,- причем так392товый вход устройства соединен с первым входом узла записи, второй вход которого со динен с выходом элемента НЕ, первый выход узла записи соединен с первыми входами элементов И первой группы первого канала и с первым входом третьего элемента И первого канала, вторые входы элементов И первой группы каждого канала соединены с выходами соответствующих элементов И второй группы своего канала и через группу элементов НЕ - с входами со второго до п-го третьего элемента И своего канала, выход третьего .элемента И каждого i-ro канала соединен с первыми входами элементов И первой группы (|+1)-го канала и с первым входом третьего элемента И (i+l)-ro канала, вы ход третьего элемента И п-го канала является выходом объединения устройства, управляющий вход регистра -каждого канала соединен со вторым выходом узла записи, группа информационных входов регистра каждого канала является соответствующей группой кодовых входов устройства, группа разрядных выходов регистра каждого канала соединена с группой входов дешифратора своего канала, каждый i-й выход дешифратора каждого канала соединен с первыми входами элементов И второй грзттпы i-ro канала, выход второго триггера i-ro канала соединен со вторым входом i-ro элемента И второй группы каждо го канала, выход каждого i-ro элемента И первой группы каждого канала соединен с соответствующим входом элемента ИЛИ i-ro канала, выход элемента ИЛИ каждого канала соединен с нулевым входом первого триггера своего канала и является соответствующим информационным выходом устройства, третий вход узла записи, является входом записи устройства. Узел записи содержит два триггера и четыре элемента И, причем первые входы первого и второго элементов И соединены с первым входом узла, второй вход которого соединен с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с единичным и нулевым выходами первого триггера, единичный и нулевой входы которого соединены соответственно с третьим входом узла и с выходом первого элемента И, второй выход узла соединен с вы ходом первого элемента И, выходы третьего и четвертого элементов И соединены соответственно с единичным и нулевым входами второго триггера, единичный и нулевой выходы которого соединены со вторыми входами первого и второго элементов И соответственно, выход второго элемента И соединен с первым выходом узла. 4 На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2 - блок-схема узла записи. Устройство содержит каналы 1, 2 и 3, триггеры 4 и 5, элементы И 6 и 7, регистр 8, дешифратор 9, группа элементов И lOj1 On; группа элементов НЕ 11j -11 j, группа элементов И 12i-12n, элемент И 13, элемент ИЛИ 14, элемент НЕ 15, тактовый вход 16 устройства, выход 17 объединения устройства, запросный вход 18 устройства, информационный выход 19 устройства, группа кодовых входов 20 устройства и узел 21 записи. Узел 21 записи содержит вход 22 записи устройства, триггеры 23 и 24, элементы И Устройство работает следующим образом. Перед началом работы на общую пшну Гне показана) сброса триггеров 4 и 5 и регистров 8 показателей пр1 оритета поступает импульс сброса и устанавливает триггеры 4 и 5 и регистры 8 показателя приоритета в исходное нулевое состояние, образуя цепь сквозного переноса (если на входную шину 18 каждого из п-каналов не поступил ни один импульс запроса) импульсов синхронизации со входа 16 через элемент И 13 каждого из п-каналов на выход 17. Пусть на группах входов 20 сформирована очередь обработки поступающих запросов по входам 18 следующим образом: в первом канале - наивысший приоритет, а в п-канале наименьший, т.е. обработка запросов должна быть от канала 1 к п-ому каналу; и сигналом, выдаваемым узлом 21 записи на управляющие входы регистров 8, происходит запись их в соответствующие регистры 8. На, выходах дешифраторов 9 каждого из п-каналов возбуждаются определенные выходы, а именно в канале 1 - 1-й выход дешифратора, а в п-ом канале - п-ый выход дешифратора, определяющие приоритет (очередность) обработки запросов, зафиксированных в регистре 8 показателя приоритета. Пусть на входную, шину 18 каждого из п-каналов поступили одновременно запросы и зафиксировались в триггере 4 каждого из п-каналов то в пазу (до импульса синхронизации) через логический элемент И 7 каждого из каналов произойдет перезапись запроса в триггер 5. Единичные выходы триггеров 5 каждого из каналов поступают на входы группы элементов И (lOj-lOn), на другие входы котюрых поступают одноименные выходы дешифратора 9 каждого из каналов, определяющих показатель очереди (приоритет обработки). Очевидно, что в канале 1, в группе элементов И (lOj-lOn) на выходе элемента И lOi находится высокий потенилал, который являе ся разрешающим для одного из выходов эле мента И 121 группы , элементов И (12i-12n) и запрещающим через элемент НЕ lli группы элементов НЕ. (lli-llp) для элемента И 13. Приходящий первый импульс синхрооерии с входа 16поступает через элемент И 121 группы элементов И (12i-12n) на вход элемента ИЛИ 14 канала 1, а с его выхода на выход 19 и нулевой вход триггера 4, устанавливая его в нулевое состояние, блокируя элемент И 7 и подготавливает к открытию элемент И 6.. В паузе происходит установ триггера 5 канала 1 в нулевое состояние и на выходе элемента И lOi группы элементов И (lOi-lOn) появляется нулевой потенциал, являющийся уже запрещающим для элемента И 12i группы элемен тов ,И (12i -12п) и разрешающим через элемент НЕ 111 группы элементов НЕ (Hill п) для элементов И 13. Второй и последующий за ним импульсы синхросерии с выхода элемента И 13 поступают в следующий канал в качестве синхронизирующей серии, которая отличается от предыдущей (входной) отсутствием лишь импульса (первого), cejiegтированного на выход 19 первого каналаПроцесс селекции аналогичным образом распространяется до выхода 17, на котором . из входной серии вычеркивается столько импульсов, сколько запросов поступило за это время в устройство, согласно приоритета обработки, указанного в регистре показателя приоритета каждого из п-каналов. Рассмотрим работу узла 21. Перед началом работы на вход сброса (не показан) триггеров 4 и 5, 23 и 24 и регистров 8 каждого из п-каналов поступает импул сброса и устанавливает триггеры 4, 5, 23, 24 и регистр 8 в исходное нулевое состояние. Триггер 24 подготавливает к открытию элемент И 28 и импульсы синхронизации с . входа 16 поступают в устройство через .элемент И 28 и образуют цепь сквозного перено са до выхода 17. При окончании формирования на группах входов 20 очереди обработки поступающих запросов на вход 22 поступает импульс, который устанавливает триггер 23 в единичное состояние. Нулевой выход триггера 23 блокирует элемент И 26 и подготавливает элемент И 25 к открьгеанию, а в паузу (до импульса синхронизанди или после него) через элемент И 25 происходит перепись единицы триггера 23 в триггер 24, нулевой вход триггера 24 блокирует элемент И 28 и подготавливает элемент И 27, выход которого связан с входом первого канала. Далее первый импульс синхронизации поступает через 86 элемент И 27 на управляющий вход регистра 8 и нулевой вход триггера 23, производится запись сформированных предварительно кодов приоритета в регистры 8, также сброс триггера 23 в исходное нулевое состояние. В паузу в синхросерии происходит сброс триггера 24 и на выходе элемента И 28 появляется второй и последующие импульсы синхронизации, поступающие в канал 1 устройства в качестве синхронизирующей серии. Применение изобретения позволяет расишрить функциональные возможности устройства за счет обеспечения времени селекции импульсов в соответствии с очередью. Формула изобретения 1. Многоканальное устройство для приоритетной селекции, импульсов, содержащее элемент НЕ, каналы, а в каждом канале два триггера, два элемента И, первую группу элементов И, причем тактовый вход устройства через элемент НЕ соединен с первыми входами первого и второго элементов И всех каналов, вторые входы которых соединены соответственно с единичным и нулевым выходами первого триггера своего канала, выходы первого и второго элементов И каждого канала соединены соответственно с единичным и нулевым входами второго триггера своего канала, единичный вход первого триггера каждого канала является соответствующим запросным входом устррйства, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения времени селекиции импульсов в соответствии с очередаю, оно содержит узел записи, а в каждом канале третий элемент И, вторую группу элементов И, группу элементов НЕ, элемент ИЛИ, регистр и дешифратор. причем тактовьш вход устройства соединен с первым входом узла записи, второй вход которого соединен с выходом элемента НЕ, первый выход узла записи соединен с первыми входами элементов И первой группы первого канала и с первым входом треплго элемента И первого канала, вторые входы элементов И Первой группы каждого канала соединены с выходами соответствующих элементов И второй группы своего канала и через группу элементов НЕ - с соответствующими входами третьего элемента И своего канала, выход третьего элемента И каждого i-ro канала соединен с первыми входами эпемеитов И первой группы (i-H)-ro канала и с первым входом третьего элемента И {i+l)-ro канала, выход третьего элемента И п-го канала является выходом объеданения устройства, управляющий вход регистра каждого канала соединен со вторым выходом узла записи, группа информационных входов регистра каждого канала является соответствующей группой кодовых входов устройства, группа разрядных выходов регистра каждого канала соединена с группой входов дешифратора своего канала, каждый i-й выход деишфратора каждого канала соединен с первыми входами элементов И второй группы i-ro канала, выход второго триггера i-ro канала соединен со вторым входом 1-го элемента И второй группы каждого канала, выход каждого i-ro элемента И первой группы каждого канала соединен с соответствующим входом элемента ИЛИ i-ro канала, выход элемента ИЛИ каждого канала соединен с нулевым входом первого триггера своего канала и является соответствующим информационным выходом устройства, третий вход узла записи является входом записи устройства.

2. Устройство по п. 1 отличающееся тем, что узел записи содержит два триггера и четыре элемента И, причем первые входы первого и второго элементов

И соединены с первым входом узла, второЖ вход которого соединен с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с

единичным и нулевым выходами первого триггера, единичный и нулевой входы которого соединены соответственно с третьим входом узла и с выходом первого элемента И, второй выход соединен с выходом первого

элемента И, выходы третьего и четвертого элементов И соединены соответственно с единичным и нулевым входами второго триггера, едииичный и нулевой выходы которого соединены со вторыми входами первого и второго элементов И соответственно, выход второго элемента И соединен с первым выходом узла.

Источники информации, принятые во внимание при экспертизе

1.Авторское сввдетельство СССР N 363977, кл. G 06 F 9/18, 1972.

2.Авторское свидетельство СССР N 699522, кл. G 06 F 9/18, 1979 (прототип).

zz

го

Г8

Zff

Фаг, 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для приоритетной селекции импульсов | 1982 |

|

SU1096645A1 |

| Устройство для обслуживания запросов | 1985 |

|

SU1302280A1 |

| Многоканальное устройство динамического приоритета | 1981 |

|

SU970371A1 |

| Устройство для сопряжения цифровой вычис-лиТЕльНОй МАшиНы C КАНАлАМи СВязи | 1979 |

|

SU840876A1 |

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

| Многоканальное устройство для приоритетного управления | 1981 |

|

SU976445A1 |

| Устройство для распределения заданий между ЭВМ | 1989 |

|

SU1695300A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Устройство для управления очередностью обслуживания | 1987 |

|

SU1481765A2 |

| Устройство для обслуживания группы запросов | 1988 |

|

SU1562913A1 |

Авторы

Даты

1982-05-07—Публикация

1980-05-07—Подача