Изобретение относится к области вычислительной техники, в частности устройствам приоритетного обслуживания запросов, и может быть использовано в многопроцессорных вычислитель ных системах обработки данных,

Целью изобретения является расширение области применения за счет организации приоритета одновременно поступивших запросов,

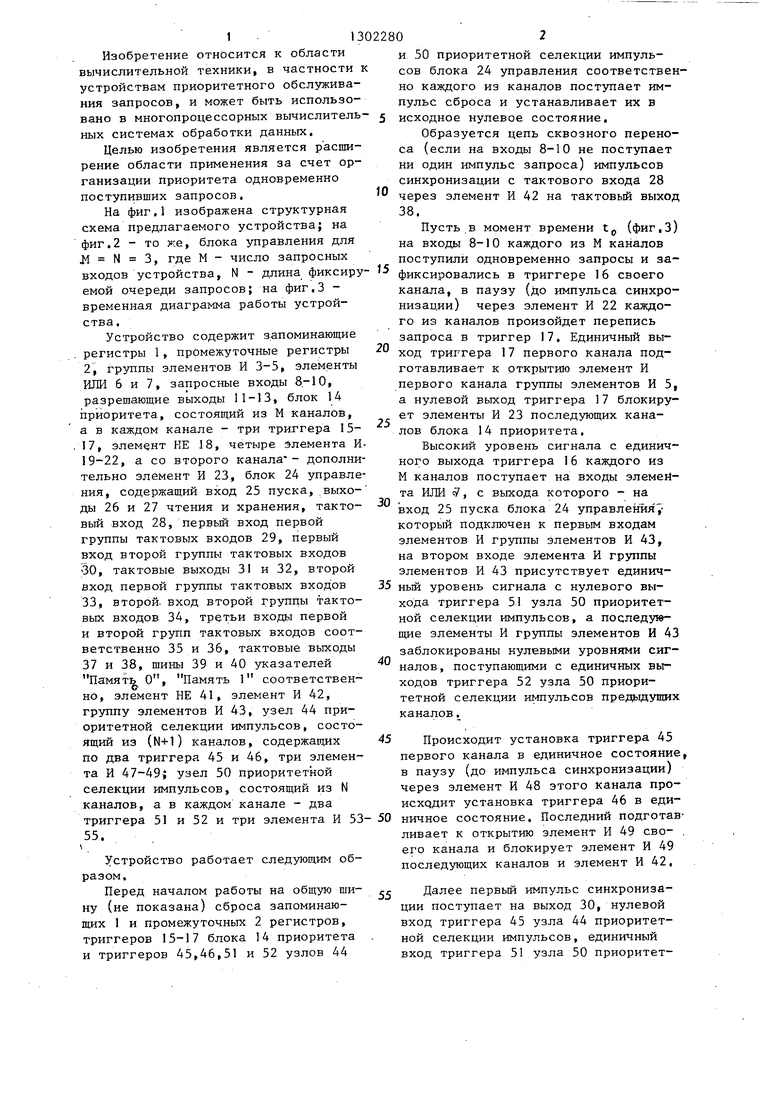

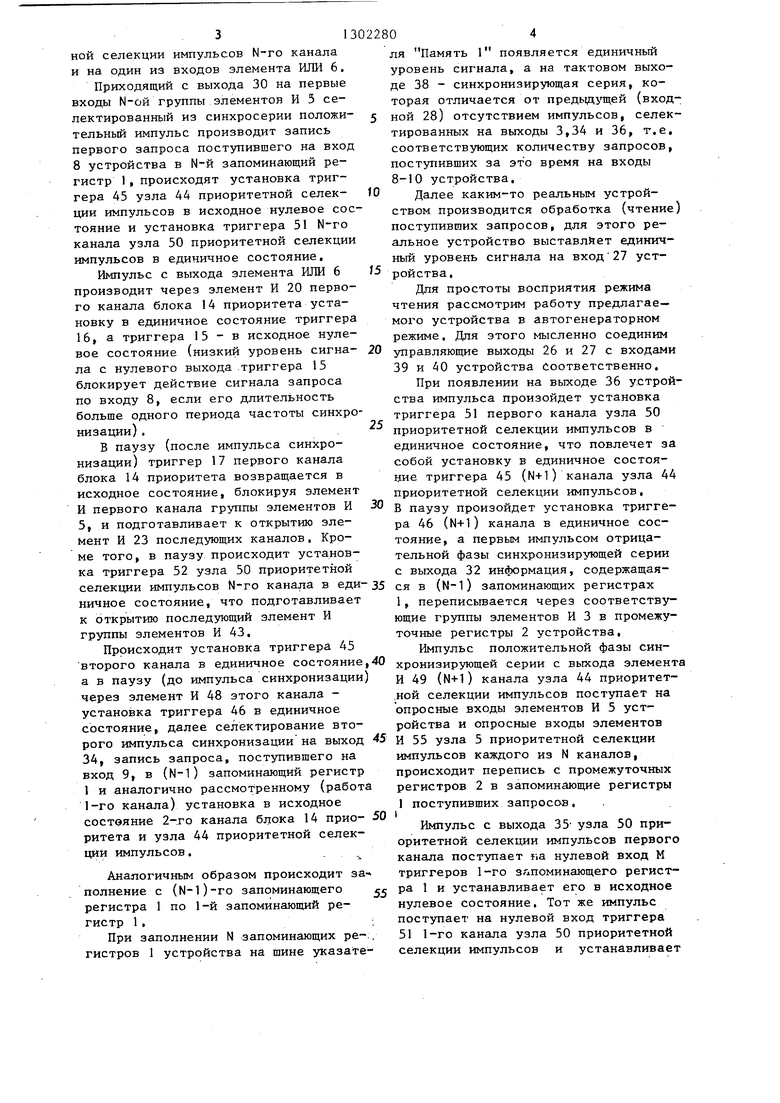

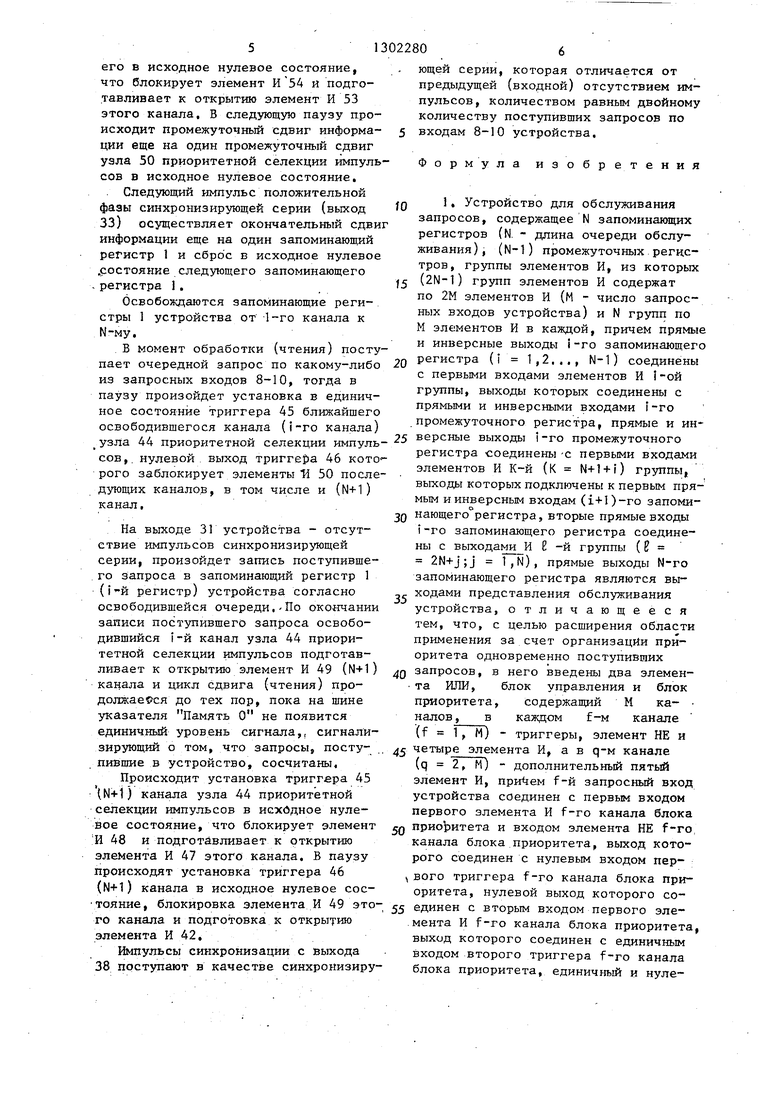

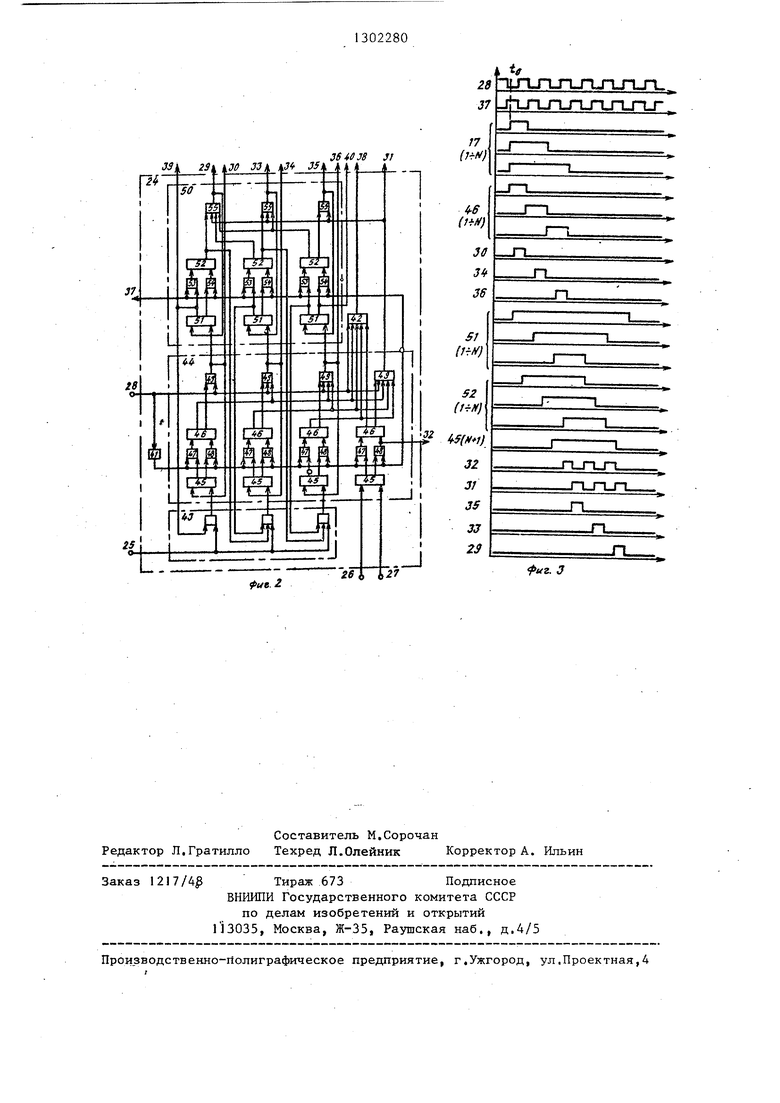

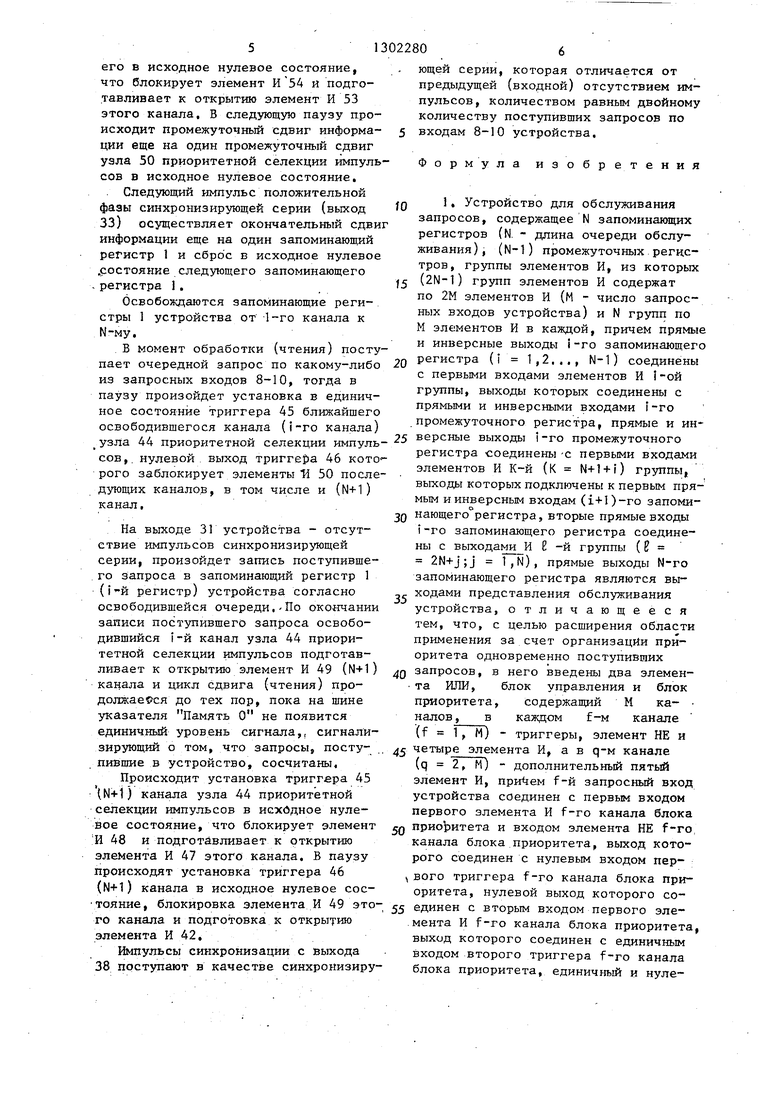

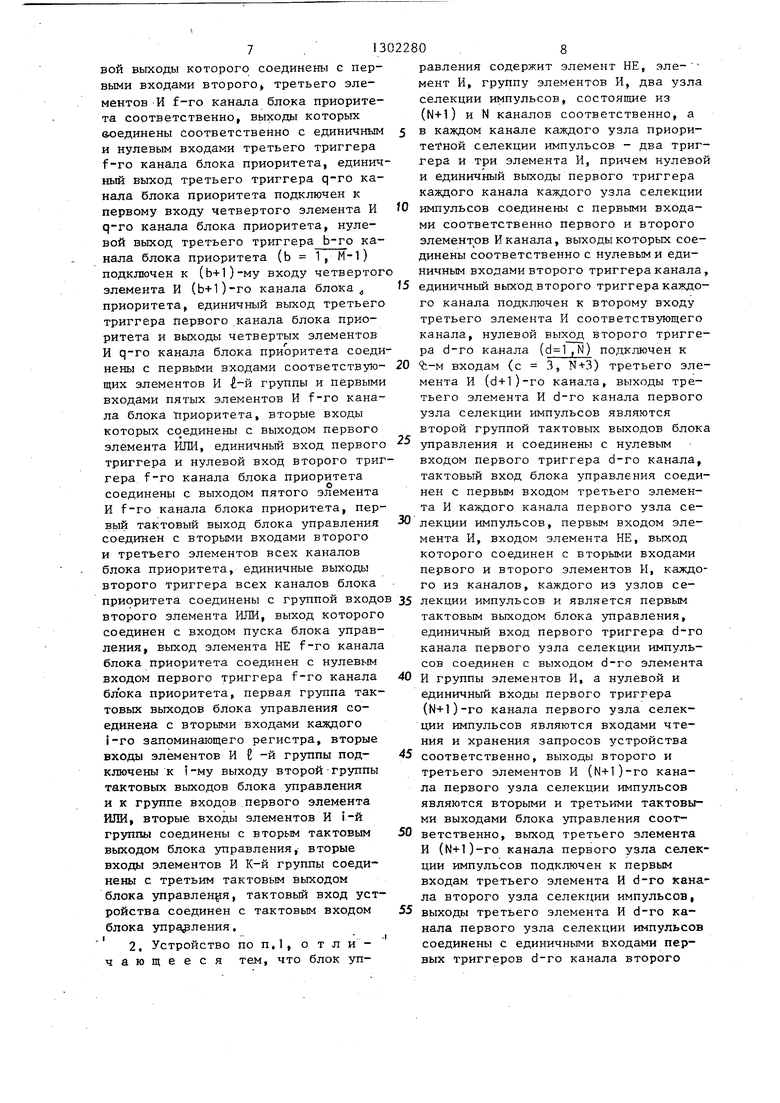

На фиг,1 изображена структурная схема предлагаемого устройства; на фиг,2 - то же, блока управления для Л N 3, где М - число запросных входов устройства, N - длина фиксиру емой очереди запросов; на фиг,3 - временная диаграмма работы устройства.

Устройство содержит запоминающие . регистры 1, промежуточные регистры 2, группы элементов И 3-5, элементы ИЛИ 6 и 7, запросные входы 8-10, разрешающие выходы 11-13, блок 14 приоритета, состоящий из М каналов, а в каждом канале - три триггера 15- 17, элемент НЕ J8, четыре Элемента И 19-22, а со второго канала - дополнительно элемент И 23, блок 24 управления, содержащий вход 25 пуска, выходы 26 и 27 чтения и хранения, такто- вый вход 28, первьш вход первой группы тактовых входов 29, первый вход второй группы тактовых входов 30, тактовые выходы 31 и 32, второй вход первой группы тактовых 33, второй, вход второй группы тактовых входов 34, третьи входы первой и второй групп тактовых входов соответственно 35 и 36, тактовые выходы 37 и 38, шины 39 и 40 указателей Память О, Память 1 соответственно, элемент НЕ 41, элемент И 42, группу элементов И 43, узел 44 приоритетной селекции импульсов, состоящий из (N+1) каналов, содержащих по два триггера 45 и 46, три элемента И 47-49; узел 50 приоритетной селекции импульсов, состоящий из N каналов, а в каждом канале - два триггера 51 и 52 и три элемента И 53

55.

Устройство работает следующим образом.

Перед началом работы на общую щи- ну (не показана) сброса запоминающих 1 и промежуточных 2 регистров, триггеров 15-17 блока 14 приоритета и триггеров 45,46,51 и 52 узлов 44

и 50 приоритетной селекции импульсов блока 24 управления соответственно каждого из каналов поступает импульс сброса и устанавливает их в исходное нулевое состояние.

Образуется цепь сквозного переноса (если на входы 8-10 не поступает ни один импульс запроса) импульсов синхронизации с тактового входа 28 через элемент И 42 на тактовьй выход 38.

Пусть,в момент времени t (фиг.З) на входы 8-10 каждого из М каналов поступили одновременно запросы и зафиксировались в триггере 16 своего канала, в паузу (до импульса синхронизации) через элемент И 22 каждого из каналов произойдет перепись запроса в триггер 17, Единичный выход триггера 17 первого канала подготавливает к открытию элемент И первого канала группы элементов И 5, а нулевой выход триггера 17 блокирует элементы И 23 последующих каналов блока 14 приоритета.

Высокий уровень сигнала с единичного выхода триггера 16 каждого из М каналов поступает на входы элемей- та ИЛИ , с выхода которого - на вход 25 пуска блока 24 управления который подключен к первым входам элементов И группы элементов И 43, на втором входе элемента И группы элементов И 43 присутствует единичный уровень сигнала с нулевого выхода триггера 51 узла 50 приоритетной селекции импульсов, а последующие элементы И группы элементов И 43 заблокированы нулевыми уровнями сигналов, поступающими с единичных выходов триггера 52 узла 50 приоритетной селекции импульсов предыдущих каналов,

Происходит установка триггера 45 первого канала в единичное состояние в паузу (до импульса синхронизации) через элемент И 48 этого канала про- исхчдит установка триггера 46 в единичное состояние. Последний подготавливает к открытию элемент И 49 сво- его канала и блокирует элемент И 49 последующих каналов и элемент И 42,

Далее первый импульс синхронизации поступает на выход 30, нулевой вход триггера 45 узла 44 приоритетной селекции импульсов, единичный вход триггера 51 узла 50 приоритетной селекции импульсов N-ro канала и на один из входов элемента ИЛИ 6,

Приходящий с выхода 30 на первые входы N-ОЙ группы элементов И 5 селектированный из синхросерии положи- тельный импульс производит запись первого запроса поступившего на вход 8 устройства в N-й запоминающий регистр 1 , происходят установка триггера 45 узла 44 приоритетной селек- ции импульсов в исходное нулевое состояние и установка триггера 51 N-ro канала узла 50 приоритетной селекции импульсов в единичное состояние,

Импульс с выхода элемента ИЛИ 6 производит через элемент И 20 первого канала блока 14 приоритета установку в единичное состояние триггера 16, а триггера 15 - в исходное нулевое состояние (низкий уровень сигна- ла с нулевого выхода .триггера 15 блокирует действие сигнала запроса по входу 8, если его длительность больше одного периода частоты синхронизации) .

В паузу (после импульса синхронизации) триггер 17 первого канала блока 14 приоритета возвращается в исходное состояние, блокируя элемент И первого канала грзшпы элементов И 5, и подготавливает к открытию элемент И 23 последующих каналов, Кроме того, в паузу происходит установка триггера 52 узла 50 приоритетной селекции импульсов N-ro канала в еди ничное состояние, что подготавливает к открытию последующий элемент И группы элементов И 43,

Происходит установка триггера 45 второго канала в единичное состояние а в паузу (до импульса синхронизации через элемент И 48 этого канала - установка триггера 46 в единичное состояние, далее селектирование второго импульса синхронизации на выход 34, запись запроса, поступившего на вход 9, в (N-I) запоминающий регистр 1 и аналогично рассмотренному (работ 1-го канала) установка в исходное состояние 2-го канала блока 14 прио- ритета и узла 44 приоритетной селекции импульсов.

Аналогичным образом происходит за полнение с (N-l)-ro запоминающего регистра 1 по 1-й запоминающий регистр 1 ,

При заполнении N запоминающих регистров 1 устройства на шине указате

ля Память 1 появляется единичный уровень сигнала, а на тактовом выходе 38 - синхронизирующая серия, которая отличается от предыд тцей (входной 28) отсутствием импульсов, селектированных на выходы 3,34 и 36, т.е. соответствующих количеству запросов, поступивших за это время на входы 8-10 устройства.

Далее каким-то реальным устройством производится обработка (чтение поступивших запросов, для этого реальное устройство выставляет единичный уровень сигнала на вход 27 устройства.

Для простоты восприятия режима чтения рассмотрим работу предлагаемого устройства в автогенераторном режиме, Для этого мысленно соединим управляющие выходы 26 и 27 с входами 39 и 40 устройства Соответственно,

При появлении на выходе 36 устройства импульса произойдет установка триггера 51 первого канала узла 50 приоритетной селекции импульсов в единичное состояние, что повлечет за собой установку в единичное состояние триггера 45 (N+1) канала узла 44 приоритетной селекции импульсов, В паузу произойдет установка триггера 46 (N+1) канала в единичное состояние, а первым импульсом отрицательной фазы синхронизирующей серии с выхода 32 информация, содержащаяся в (N-I) запоминающих регистрах 1, переписывается через соответствующие группы элементов И 3 в промежуточные регистры 2 устройства.

Импульс положительной фазы син- хронизир ующей серии с выхода элемент И 49 (N+I) канала узла 44 приоритет- ,нсй селекции импульсов поступает на опросные входы элементов И 5 устройства и опросные входы элементов И 55 узла 5 приоритетной селекции импульсов каждого из N каналов, происходит перепись с промежуточных регистров 2 в запоминающие регистры

1 поступивших запросов, 1

Импульс с выхода 35- узла 50 приоритетной селекции импульсов первого канала поступает на нулевой вход М триггеров 1-го зг поминающего регистра 1 и устанавливает его в исходное нулевое состояние. Тот же импульс поступает на нулевой вход триггера 51 1-го канала узла 50 приоритетной селекции импульсов и устанавливает

его в исходное нулевое состояние, что блокирует элемент И 54 и подготавливает к открытию элемент И 53 этого канала, В следующую паузу происходит промежуточный сдвиг информации еще на один промежуточный сдвиг узла 50 приоритетной селекции импульсов в исходное нулевое состояние,

. Следующий импульс положительной фазы синхронизирующей серии (выход 33) осуществляет окончательный сдвиг информации еще на один запоминающий регистр 1 и сбро с в исходное нулевое состояние следующего запоминающего - регистра ,

Освобождаются запоминающие регистры 1 устройства от 1-го канала к N-му,

В момент обработки (чтения) поступает очередной запрос по какому-либо из запросных входов 8-10, тогда в паузу произойдет установка в единичное состояние триггера 45 ближайшего освободившегося канала (i-ro канала)

ющай серии, которая отличается от предыдущей (входной) отсутствием импульсов, количеством равным двойному количеству поступивших запросов по входам 8-10 устройства.

Формула изобретения

JQ 1. Устройство для обслуживания запросов, содержащее N запоминающих регистров (N. - длина очереди обслуживания), (N-I) промежуточных регистров, группы элементов И, из которых

J5 (2N-1) групп элементов И содержат по 2М элементов И (М - число запросных входов устройства) и N групп по М элементов И в каждой, причем прямые и инверсные выходы i-го запоминающего

20 регистра (i 1,2..., N-1) соединены с первыми входами элементов И i-ой группы, выходы которых соединены с прямыми и инверсными входами i-го

сов,, нулевой выход тригге&а 46 которого заблокирует элементы И 50 последующих каналов, в том числе и (N+1) канал.

30

промежуточного регистра, прямые и ин.. „ 25 вареные выходы i-ro промежуточного

узла 44 приоритетной селекции импульрегистра соединены -с первыми входами

элементов И К-й (К N+1+i) грзшпы, выходы которых подключены к первым пря- мым и инверсным входам (i+l)-ro запоми- нающего°регистра, вторые прямые входы i-ro запоминающего регистра соединены с вьгходами И -и группы (Р 2N+j;j 1,N), прямые выходы N-ro запоминающего регистра являются выходами представления обслуживания устройства, отличающееся тем, что, с целью расширения области применения за счет организации приоритета одновременно поступивших

40

35

. На выходе 31 устройства - отсутствие импульсов синхронизирующей серии, произойдет запись поступившего запроса в запоминающий регистр 1 ({-и регистр) устройства согласно освободившейся очереди.-По окончании записи постз ившего запроса освободившийся i-й канал узла 44 приоритетной селекции импульсов подготавливает к открытию элемент И 49 (N+l) канала и цикл сдвига (чтения) про- должае1 ся до тех пор, пока на шине указателя Память О не появится единичный уровень сигнала,, сигнализирующий о том, что запросы, поступившие в устройство, сосчитаны.

Происходит установка триггера 45 (N+1) канала узла 44 приоритетной селекции импульсов в исходное нулевое состояние, что блокирует элемент ;И 48 и подготавливает к открытию элемента И 47 этого канала, В паузу происходят установка триггера 46 (N+I) канала в исходное нулевое сос- тояние, блокировка элемента И 49 это- ее го канала и подготовка к открытию элемента И 42,

Импульсы синхронизации с выхода 38 поступают в качестве синхронизирузапросов, в него введены два элемен- та ИЛИ, блок управления и блок приоритета, содержащий М ка- налов, в каждом f-м канале (f 1, М) - триггеры, элемент НЕ и

четыре элемента И, а в q-м канале (q 2, М) - дополнительный пятый элемент И, примем f-й запросный вход устройства соединен с первым входом первого элемента И f-ro канала блока

.jQ приоритета и входом элемента НЕ f-ro, канала блока приоритета, выход которого соединен с нулевым входом пер- вого триггера f-ro канала блока приоритета, нулевой выход которого соединен с вторым входом первого элемента И f-ro канала блока приоритета, выход которого соединен с единичным входом второго триггера f-ro канала блока приоритета, единичный и нулеющай серии, которая отличается от предыдущей (входной) отсутствием импульсов, количеством равным двойному количеству поступивших запросов по входам 8-10 устройства.

Формула изобретения

1. Устройство для обслуживания запросов, содержащее N запоминающих регистров (N. - длина очереди обслуживания), (N-I) промежуточных регистров, группы элементов И, из которых

(2N-1) групп элементов И содержат по 2М элементов И (М - число запросных входов устройства) и N групп по М элементов И в каждой, причем прямые и инверсные выходы i-го запоминающего

регистра (i 1,2..., N-1) соединены с первыми входами элементов И i-ой группы, выходы которых соединены с прямыми и инверсными входами i-го

30

35

40

ее

запросов, в него введены два элемен- та ИЛИ, блок управления и блок приоритета, содержащий М ка- налов, в каждом f-м канале (f 1, М) - триггеры, элемент НЕ и

четыре элемента И, а в q-м канале (q 2, М) - дополнительный пятый элемент И, примем f-й запросный вход устройства соединен с первым входом первого элемента И f-ro канала блока

.jQ приоритета и входом элемента НЕ f-ro канала блока приоритета, выход которого соединен с нулевым входом пер- вого триггера f-ro канала блока приоритета, нулевой выход которого соединен с вторым входом первого элемента И f-ro канала блока приоритета выход которого соединен с единичным входом второго триггера f-ro канала блока приоритета, единичный и нулевой выходы которого соединены с первыми входами второго третьего элементов И f-ro канала блока приоритета соответственно, выходы которых воединены соответственно с единичным и нулевым входами третьего триггера f-ro канала блока приоритета, единичный выход третьего триггера q-ro канала блока приоритета подключен к первому входу четвертого элемента И q-ro канала блока приоритета, нулевой выход третьего триггера канала блока приоритета (Ь 1, М-1) подключен к (Ь+1)-му входу четвертог элемента И {Ь+1)-го канала блока приоритета, единичный выход третьего триггера первого канала блока приоритета и выходы четвертых элементов

f5 единичный выход второго триггера каждого канала подключен к второму входу третьего элемента И соответствующего канала, нулевой выход второго триггера d-ro канала (,N) подключен к

И q-ro канала блока приоритета соединены с первыми входами соответствую- 20 -м входам (с 3, N+3) третьего эле- щих элементов И 1-й группы и первыми мента И (d+l)-ro канала, выходы третьего элемента И d-ro канала первого узла селекции импульсов являются второй группой тактовых выходов блока управления и соединены с нулевым входом первого триггера d-ro канала, тактовый вход блока управления соединен с первым входом третьего элемента И каждого канала первого узла се- 30

входами пятых элементов И f-ro канала блока Приоритета, вторые входы которых со единены с выходом первого элемента ИЛИ, единичный вход первого триггера и нулевой вход второго триггера f-ro канала блока приоритета

о соединены с выходом пятого элемента

25

И f-ro канала блока приоритета, первый тактовый выход блока управления соединен с вторыми входами второго и третьего элементов всех каналов блока приоритета, единичные выходы второго триггера всех каналов блока

лекции импульсов, первым входом элемента И, входом элемента НЕ, выход которого соединен с вторыми входами первого и второго элементов И, казкдо- го из каналов, каждого из узлов сеприоритета соединены с группой входов 35 лекции импульсов и является первым

второго элемента ИЛИ, выход которого соединен с входом пуска блока управления выход элемента НЕ f-ro канала блока приоритета соединен с нулевым входом первого триггера f-ro канала блока приоритета, первая группа тактовых выходов блока управления соединена с вторыми входами каждого i-ro запоминающего регистра, вторые входы элементов И 8 -и группы подключены к i-му выходу второй-группы тактовых выходов блока управления и к группе входов первого элемента ИЛИ, вторые входы элементов И i-й группь соединены с вторым тактовым выходом блока управления, вторые входы элементов И К-й группы соединены с третьим тактовым выходом блока управления, тактовый вход устройства соединен с тактовым входом блока управления,

2, Устройство по п,1, о т л и - чающееся тем, что блок управления содержит элемент НЕ, эле- мент И, группу элементов И, два узла селекции импульсов, состоящие из (N+I) и N каналов соответственно, а

в каждом канале каждого узла приоритетной селекции импульсов - два триггера и три элемента И, причем нулевой и единичный выходы первого триггера каждого канала каждого узла селекции

o импульсов соединены с первыми входами соответственно первого и второго элементов И канала, выходы которых соединены соответственно с нулевыми единичным входами второго триггера канала,

5 единичный выход второго триггера каждого канала подключен к второму входу третьего элемента И соответствующего канала, нулевой выход второго триггера d-ro канала (,N) подключен к

0 -м входам (с 3, N+3) третьего эле- мента И (d+l)-ro канала, выходы третьего элемента И d-ro канала первого узла селекции импульсов являются второй группой тактовых выходов блока управления и соединены с нулевым входом первого триггера d-ro канала, тактовый вход блока управления соединен с первым входом третьего элемента И каждого канала первого узла се- 0

20 30

25

-м входам (с 3, N+3) третьего эле- мента И (d+l)-ro канала, выходы третьего элемента И d-ro канала первого узла селекции импульсов являются второй группой тактовых выходов блока управления и соединены с нулевым входом первого триггера d-ro канала, тактовый вход блока управления соединен с первым входом третьего элемента И каждого канала первого узла се-

лекции импульсов, первым входом элемента И, входом элемента НЕ, выход которого соединен с вторыми входами первого и второго элементов И, казкдо- го из каналов, каждого из узлов сетактовым выходом блока управления, единичный вход первого триггера d-ro канала первого узла селекции импульсов соединен с выходом d-ro элемента

И группы элементов И, а нулевой и единичный входы первого триггера (N+l)-ro канала первого узла селекции импульсов являются входами чтения и хранения запросов устройства

соответственно, выходы второго и третьего элементов И (N+l)-ro канала первого узла селекции импульсов являются вторыми и третьими тактовыми выходами блока управления соответственно, выход третьего элемента И (N+l)-ro канала первого узла селекции импульсов подключен к первым входам третьего элемента И d-ro канала второго узла селекции импульсов,

выходы третьего элемента И d-ro канала первого узла селекции импульсов соединены с единичными входами первых триггеров d-ro канала второго

91

узла селекции импульсов, нулевой выход первого триггера d-ro канала вто роге узла селекции импульсов подключен к первому входу d-ro элемента И группы элементов И, единичный выход второго триггера h-ro канала (h а 2, N) второго узла селекции импульсов подключен к второму входу h-ro элемента И группы элементов Лц третьи входы элементов И группы соеди- вены с входом пуска блока управления нулевой выход первого триггера N-ro канала и единичный выход первого

10

триггера первого канала второго узла селекции импульсов являются выходами указателей Память О и Память 1, входы элемента И подключены к нулевому выходу второго триггера каждого из каналов первого узла приоритетной селекции импульсов и тактовому . входу блока управления, вь)ход является выходом сопряжения устройства, выходы третьего элемента И d-ro канала второго узла являются первой группой тактовых выходов блока управления .

А

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для приоритетной селекции импульсов | 1980 |

|

SU926658A1 |

| Многоканальное устройство для приоритетной селекции импульсов | 1982 |

|

SU1096645A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1536383A1 |

| Многоканальное устройство для приоритетной селекции импульсов | 1987 |

|

SU1460721A1 |

| Устройство для управления прерыванием программ | 1981 |

|

SU978150A1 |

| Многоканальное устройство для приоритетного управления | 1981 |

|

SU976445A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1319043A1 |

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Многоканальное устройство для управления очередностью запросов | 1982 |

|

SU1061143A1 |

Изобретение относится к вычислительной технике, в частности к устройствам приоритетного обслуживания запросов, и может быть использовано в вычислительных системах обра- ботки данных. Изобретение позволяет расширить область применения устройства за счет организации приоритета одновременно поступивших запросов. Устройство содержит 3N-1 групп элементов И (N - длина очереди), N запоминающих и N-I промежуточных регистров, элементы ИЛИ, блок приоритета, блок управления. Запросы, приходл- щие в устройство, запоминаются в блоке приоритета в порядке их поступления от 1-го канала к 0-му (М - число запросных входов устройства) и через элемент ИЛИ, как сигналы запуска, . поступают в блок управления. Блок управления производит выдачу тактовых импульсов основной- синхросерии в цепи управления устройством, в результате чего производится перепись запросов из блока приоритета. Устройство позволяет осуществить независимую запись/чтение запросов и привязать ввод/вьшод запросов к основной синхросерии, 1 з.п,ф-лы, 3 ил. сл со о tsD ЬО 00 о

1 I1

фие. 2

fTfJT.JTJTJ-aj-lJ-LrL.

риг. J

| Устройство для обслуживания запросов | 1982 |

|

SU1056196A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обслуживания запросов в порядке поступления | 1976 |

|

SU650078A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-07—Публикация

1985-12-09—Подача