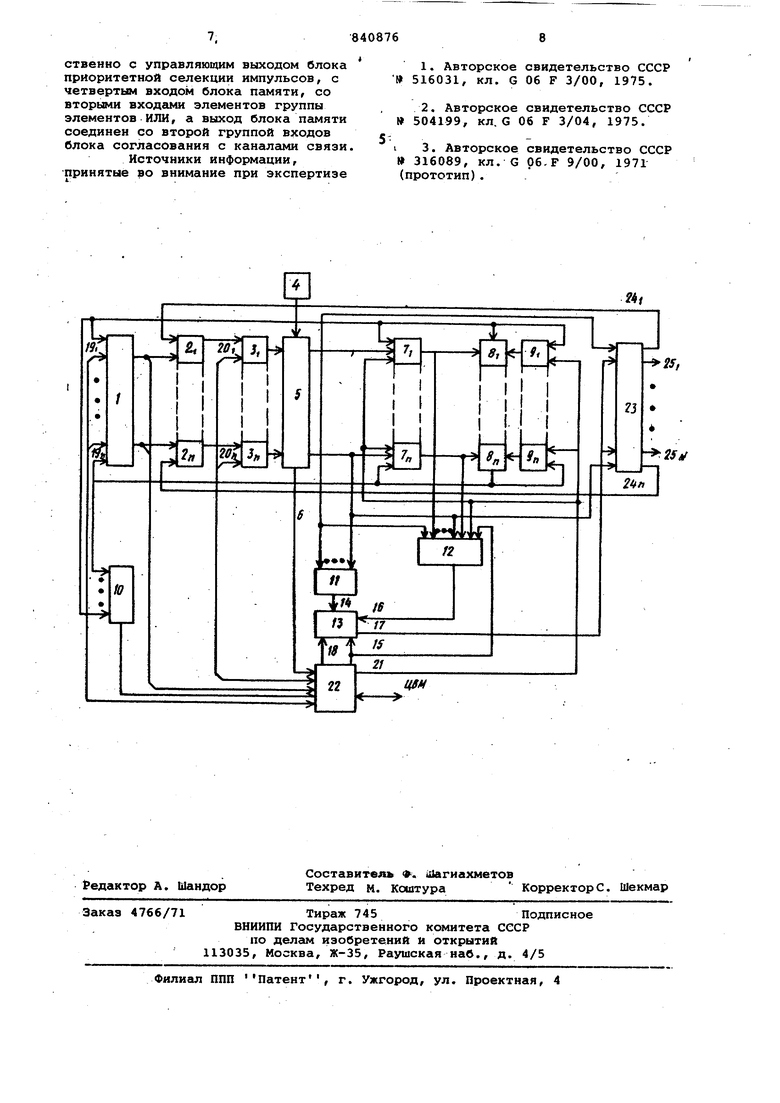

Изобретение относится к вычисли- гельной технике, в частности к устройствам передачи данных, и может быт.ь использовано в устройствах коммутации сообщений. Известно устройство для сопряже.ния цифровой вычислительной машины (ЦВМ) с каналс1ми- связи, содержащее блок коммутации, преобразователь кода, блок буферной памяти, блок управ пения коммутацией, регистры улравления, группы элементов И, узел распре деления управляющих сигналов, триггеры, узел формирования, кодовые шины, связанные с ЦВМ 1. Недостатком известного устройства является зависимость преобразования и передачи информации в последующие каналы связи от -предыдущего, т.е отсутствие независимой одновременной работы по каналам связи. Известно устройство для сопряжения с ЦВМ, содержащее долговременное запоминающее устройство (ДЗУ), регистр адреса, переключатель, блок начального пуска, регистр заявок и готовности, элементы И и ИЛИ 2. Недостатком этого устройства является низкое быстродействие, рбус ловленное его микропрограммной .реализацией. Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство для сопряжения цифровой вычислительной машины с каналами свя.зи, содержгицее блок согласования с каналами связи, блок согласования с ЦВМ, блок памяти, регистр, группу элемен- тов И, коммутатор 3. Недостатком устройства является малое быстродействие. ЦелЁ изобретения - повышение быстродействия. Поставленная цель достигается тем, что в устройство для сопряжения цифровой вычислительной машины с каналами связи, содержащее блок согласования с каналами связи, одни вы- . ходы которого являются группой выходов устройства, блок согласования с ЦВМ, вход-выход которого является входом-выходом устройства, блок памяти, первый вход которого сюединен с выходом коммутатора, регистр, выходы которого соединены с первым входом блока согласования с ЦВМ и с первыми входами элементов группы элементов И, а первый выход блока согласования с ЦВМ соединен с первыми входами регистра, введены блок приоритетной селекции импульсов, группа счетчиков сообщений, группа схем сравнения, группа регистров конечных адресов, группа элементов ИЛИ два элемента ИЛИ, причем выходы элементов группы элементов И соединены с первыми входами соответствующих элементов группы элементов ИЛИ, выходы которых соединены с информационными входами блока приоритетной селекции импульсов, каждый информационный выход блока приоритетной селекции ;импульсрв соединен с первым входом соответствующего счетчика группы счетчиков сообщений и с соответствующим входом группы входов блока согласования с каналами связи, выходи счетчиков группы счетчиков сообщений соединены с первыми входами соответствующих схем сравнеВИЯ, вторые входы которых соединены с выходами соответствующих регистров группы регистров конечных адресов, выход схемы сравнения соединен со вторым входом соответствующего счетчика группы счетчиков сообщений с соответствующим входом регистра и с первым входом соответствующего ре гистра группы регистров конечных ад ресов , другие выходы блока согласования с каналами связи соединены со вторыми входами соответствующих эле ментов группы элементов И, информационные выходы блока приоритетной селекции импульсов соединены через первый элемент ИЛИ со вторым входом блока памяти, выходы счетчиков груп пы счетчиков сообщений, информацион ные выходы блока приоритетной селек ции импульсов соединены с инфОЕ)мационными и управляющими входами ком мутатора соответственно, вторюй выход блока согласования с ЦВМ соедин с третьим входом блока памяти и с первым управляющим входом коммутато третий выход блока согласования с ЦВМ соединен со втора ш входами регистров группы регистров конечных адресов, с третьими входами счетчиков группы счетчиков сообщений н со вторым управляювщм входом коммутатора, выходы схем сравнения через второй элемент ИЛИ соединены со вторым входом блока согласования с ЦВМ, третий вход, четвёртый, пятый выход которого соединены соответственно с управляющим выходом блока приоритетной селекции импульсов, с четвертым входом блока памяти, со вторьвли входами элементов группы элементов ИЛИ, а выход блока памяти соединен со второй группой входов блока согласования с каналами связи На чертеже приведена блок-схема устройства. Устройство для сопряжения ЦВМ с налами связи содержит регистр 1, группы элементов И , группу элементов ИЛИ , генератор 4 импуль- сов, блок 5 приоритетной селекции импульсов, управляющий выход 6, группу счетчиков сообщёний, группу схем сравнения, группу регистров (, конечных адресов, элементы ИЛИ 10 и И, коммутатор 12, блок 13 памяти, со входами 14-16, выходом 17 и входом 18, входы 19 19j| регистра, входы группы Элементов ИЛИ, выход 21 блока согласования с ЦВМ, блок 22 согласования с ЦВМ, блок 23 согласования с каналами связи, выходы , , блока согласования с каналами связи. Устройство работает следующим образом. В исходном состоянии на выходе 6 схемы блока 5 приоритетной селекции импульсов присутствуют синхроимпульсы генератора 4 импульсов. При наличии, данных синхроимпульсов 22 блок сопряжения с ЦВМ производит запись массивов, предназначенных для передачи информации по различным направлениям в блок 13. Для этого на вход коммутатора 12 с выхода 21 блок 22 сопряжения с ЦВМ выставляет адрес с каждым информационным словом, поступающим на вход 18 и сигналом записи, поступающим на вход 15 блока 13 памяти и вход опроса коммутатора 12, производит заполнение блока 13 памяти массивами информации, предназначенными для передачи по различным направлениям. Далее блок 22 сопряжения с ЦВМ производит запись начальных адресов, записанных массивов информации в группу счетчиков , сообщений и конечных адресов в группу регистров 9 -9 конечных адресов. Начальные и конечные адреса соответствуют границам массива информации в блоке 13, предназначенной для передачи по различны направлениям. В регистр 1 по входам 19 19yj записываются единицы в те разряды, которые соответствуют выбранным направлениям (шины сигналов записи начальных и конечных адресов на чертеже не показаны). Далее блок 22сопряжения с ЦВМ производит вьадачу сигналов пуска по входам 20ч 20j| (количество сигналов пуска соответствует выбранным направлениям). Сигналы пуска приходят через группу элементов ИЛИ ), на .запросные входы блока 5 приоритетной селекции импульсов, который ПРОИЗВОДИТ .селектирование по данному импульсу из синхросерии генератора 4 импульсов, согласно приоритету пуска на выходные шины, связанные со счетными входами группы счетчиков 7 -7ц сообщений каждого из п направлений, входами- элемента ИЛИ 11, опросными входами коммутатора 12 и входами блока 23 сопряжения с каналами связи. С выхода элемента ИЛИ 11 сигналы поступают как сшнгхлы Чтение по входу 14 блока 13 памяти и согласно приоритету передачи производи ся считывание первых слов массивов информации из блока 13 памяти. Слова информации, считываемые и блока 13 памяти, поступают по выхо ду 17 в блок 23 сопряжения с канал бвязи, где происходит формирование кодограммы и выдача ее в каналы св зи . По концу формирования кодограммы блок 23 сопряжения с каналами связи выдает сигналы Конец сообще ния по выходам , которые поступают на одни входы группы элементов И , на другие входы которых поступает разрешающий потен циал единица с регистра 1 и про исходят следующие запросы, уже нача того формирования кодограмм самим у тройством, в блок 5 приоритетной селекции импульсов, поступающие с хода группы элементов И чере группы элементов ИЛИ Зч-3|1. Процессор обращения к блоку 13 памяти повторяется и идет до тех пор, пока показания счетчиков сообщений не совпадут с показаниями группы регистров 9 -9, конечных ад ресов. Группа схем ,сравнения производит выдачу сигналов сброса, которые осуществляют сброс счетчиков сообщений, регистров конечных адресов и разрядов реги стра 1, принадлежащим только тем Каналам, адрес счетчиков 7 -IJ, сообщений которых совпадает с конечным адресом группы регистров . 9( -9ц конечного адреса. Сигналы сброса с выходов схем , сравнения поступают на входы элемента ИЛИ 10 и с выхода элемента ИЛИ 10 как сигналы запроса н.а прерывание поступаю в блок .22 сопряжения с ЦВМ. ЦВМ опрашивает регистр 1 и на наличие нулевого состояния, бывшего единичным состоянием разряда, определяет освободившийся канал для передачи информации, в канал связи. Далее блок 22 сопряжения с ЦВМ ложег произвести запись нового массива информации по свободному напра лению.. Таким образом, применение изобретения за счет введения новых узлов и связей позволяет повысить быстродействие устройства. Формула изобретения Устройство для сопряжения цифровой вычислительной машины с каналами связи, содержащее блок согласования с каналами связи, одни вы воды которого являются группой ВЫХО дов устройства, блок согласования с ЦВМ, вход-выход которого является входом-выходом устройства, блок памяти, первый вход которого соединен с выходом коммутатора, регистр, выходы которого соединены с первым входом блока согласования с ЦВМ и с первыми входами элементов группы элементов И, а первый выход блока согласования с ЦВМ соединен с первыми входами регистра, отличающееся тем, что, с целью повышения быстродействия, оно содержит блок приоритетной селекции импульсов, группу счетчиков сообщений, группу схем сравнения, группу регистров конечных адресов, группу элементов ИЛИ и два элемента ИЛИ, причем выходы элементов группы элементов И соединены с первыми входами гоответствующих элементов группы элементов ИЛИ, выходы которых соединены с информационными входами блока приоритетной селекции импульсов, каждый информационный выход блока приоритетной селекции импульсов соединен с первым входом соответ.ствующего счетчика группы счетчиков сообщений и с соответствующим входом группы входов блока согласования с каналами связи, выходы счетчиков группы счетчиков сообщений соединены с первыми входами соответствующих схем сравнения, вторые вхоДы которых соединены с выходами соответствующих регистров группы регистров конечных адресов, выход схемы сравнения соединен со вторым входом соответствующего счетчика группы счетчиков сообщений, с соответствующим входом регистра и с первым входом соответствующего регистра группы регистров конечных адресов, другие выходы блока согласования с каналами связи соединены со вторыми входс1ми соответствующих элементов группы элементов И, информационные в исоды блока приоритетной селекции импульсов соединены через первый элемент ИЛИ со вторым входом блока памяти, выходы счетчиков группы счетчиков сообщений, информационные выходы блока приоритетной селекции импульсов соединены с информационными и управляющими входами коммутатора соответственно, второй выход блока согласования с ЦВМ соединен с третьим входом блока памяти и с первым управляющим входом коммутатора, третий выход блока согласования с ЦВМ соединен со вторыми входами регистров группы регистров конечных адресов,с третьими входами счетчиков группы счетчиков ообщений и со вторыми управляющим вхоом коммутатора,выходы схем сравнения iepe3 второй элемент ИЛИ соединены о вторым входом блока согласования ЦВМ, третий вход, четвертый, пяый выход которого соединены соответственно с управляющим выходом блока приоритетной селекции импульсов, с четвертым входом блока памяти, со вторыми входг1ми элементов группы элементов ИЛИ, а выход блока пгиияти соединен со второй группой входов блока согласования с каналами связи.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 516031, кл. G 06 F 3/00, 1975.

2.Авторское свидетельство СССР 504199, кл. G 06 F 3/04, 1975.

I 3. Авторское свидетельство СССР 316089, кл. G 06.F 9/00, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С ТЕЛЕГРАФНЫМИ КАНАЛАМИ СВЯЗИ | 1979 |

|

SU826332A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналами связи | 1983 |

|

SU1160421A1 |

| Устройство для сопряжения | 1982 |

|

SU1112359A1 |

| Многоканальный коммутатор | 1981 |

|

SU963046A1 |

| Многоканальное устройство для сопряжения абонентов с цифровой вычислительной машиной | 1986 |

|

SU1310831A2 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для сопряжения ЦВМ с абонентами | 1985 |

|

SU1322300A1 |

| Устройство для обмена информацией | 1974 |

|

SU732848A1 |

| Устройство для сопряжения процессора с памятью | 1983 |

|

SU1149272A1 |

Авторы

Даты

1981-06-23—Публикация

1979-08-06—Подача