1

изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных машинах (ЦВМ) для обмена информацией между оперативной памятью и внешними устройствами.

Целью изобретения является повышение пропускной способности селекторного канала.

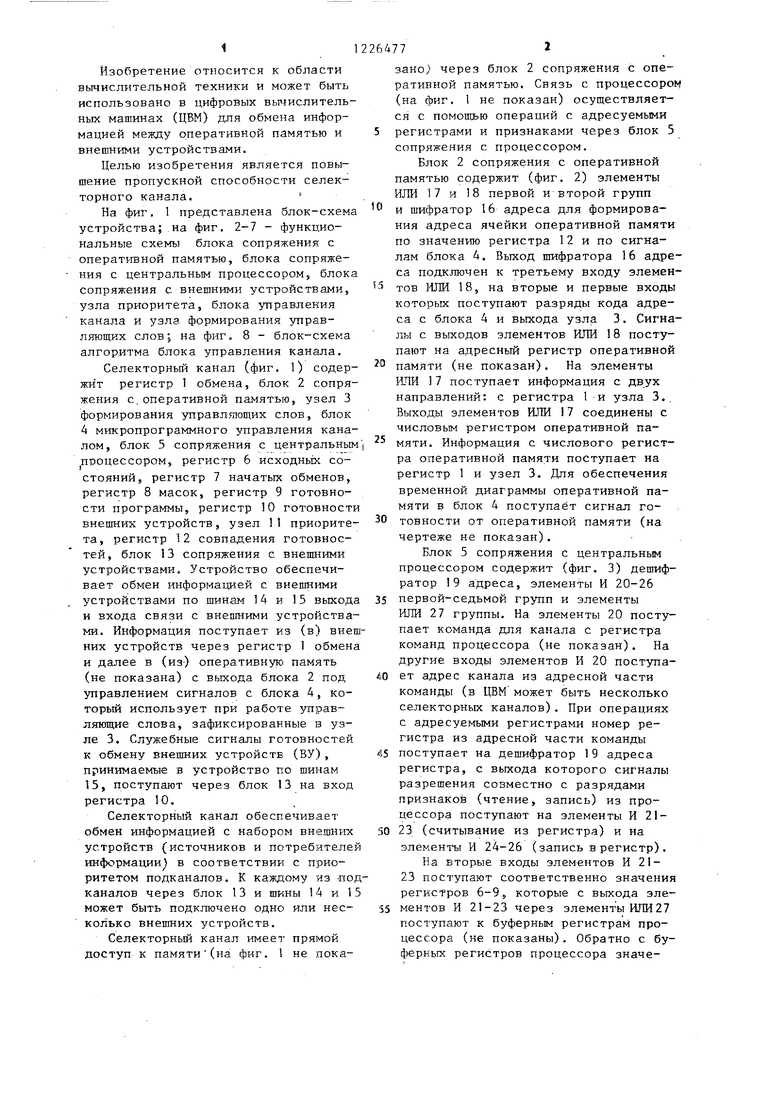

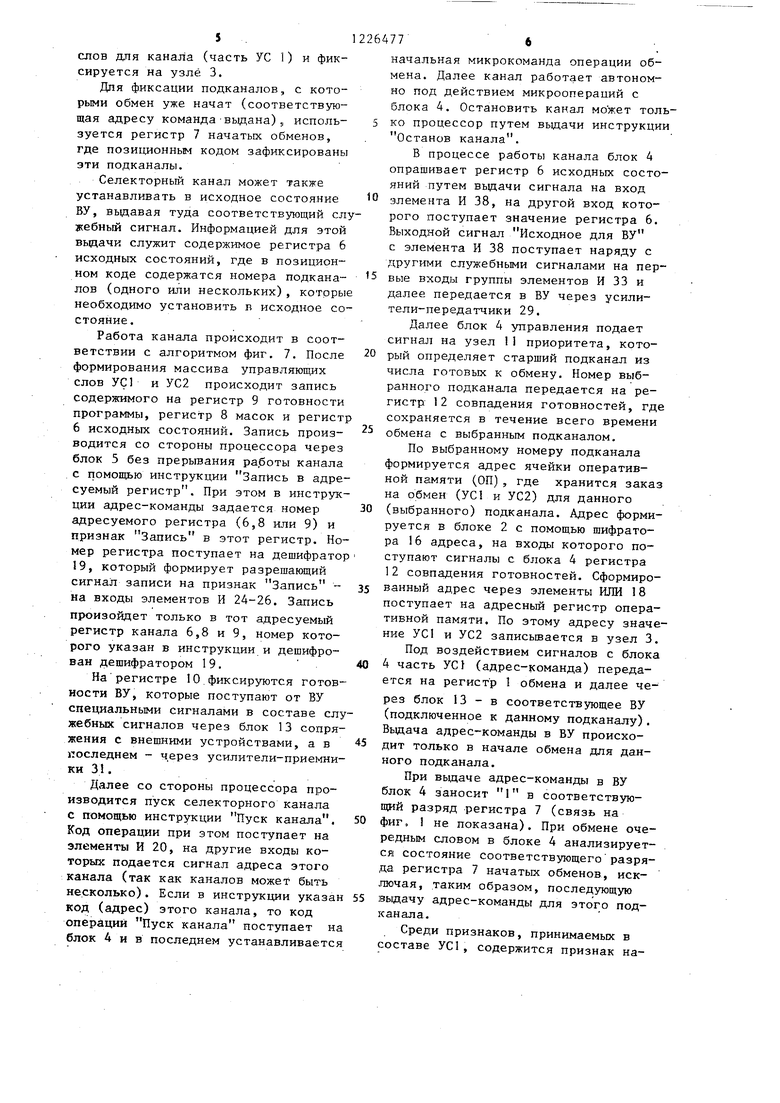

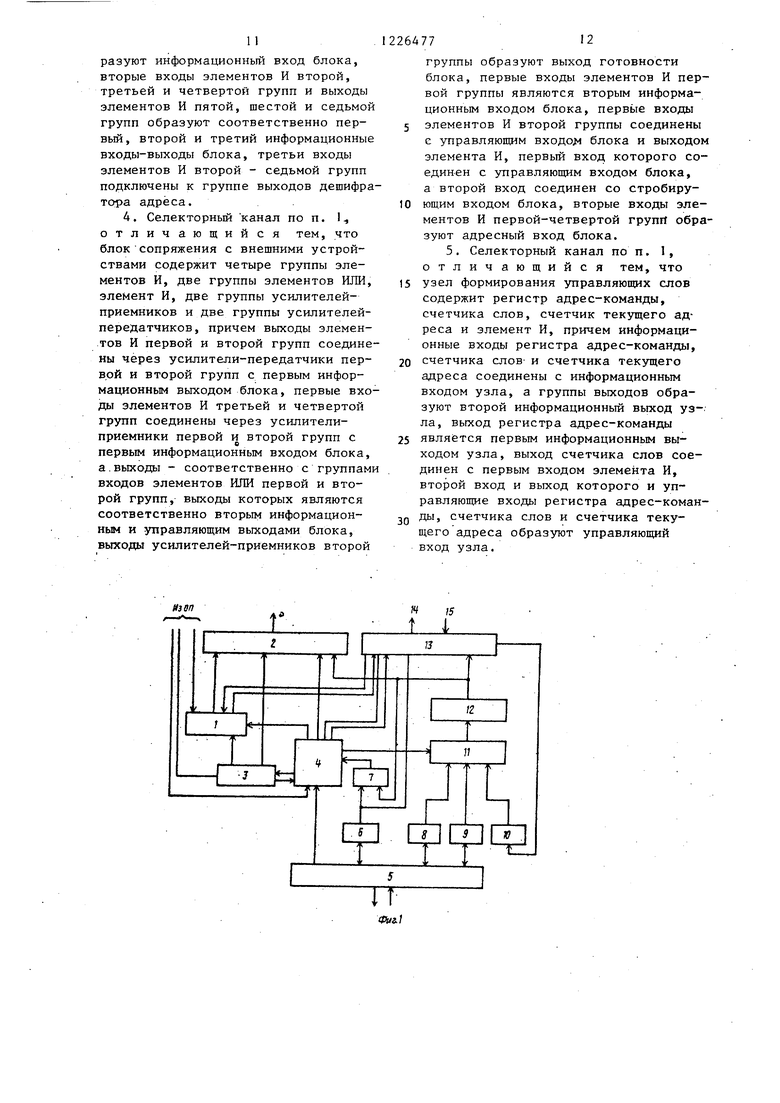

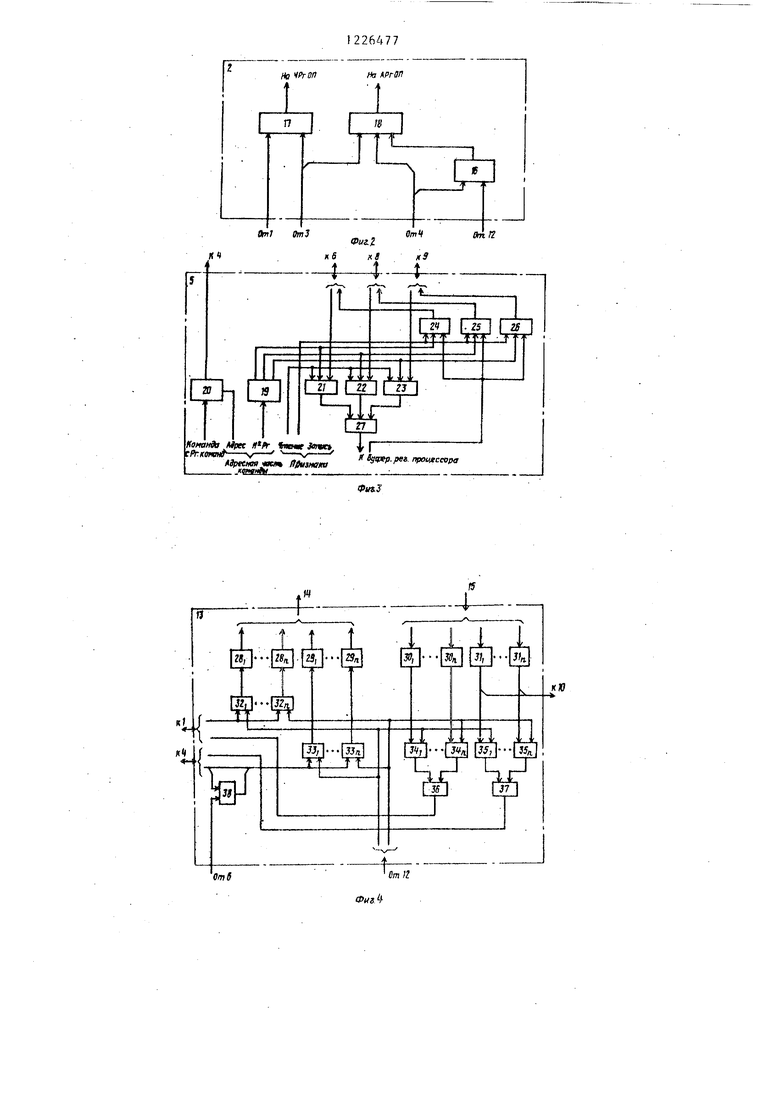

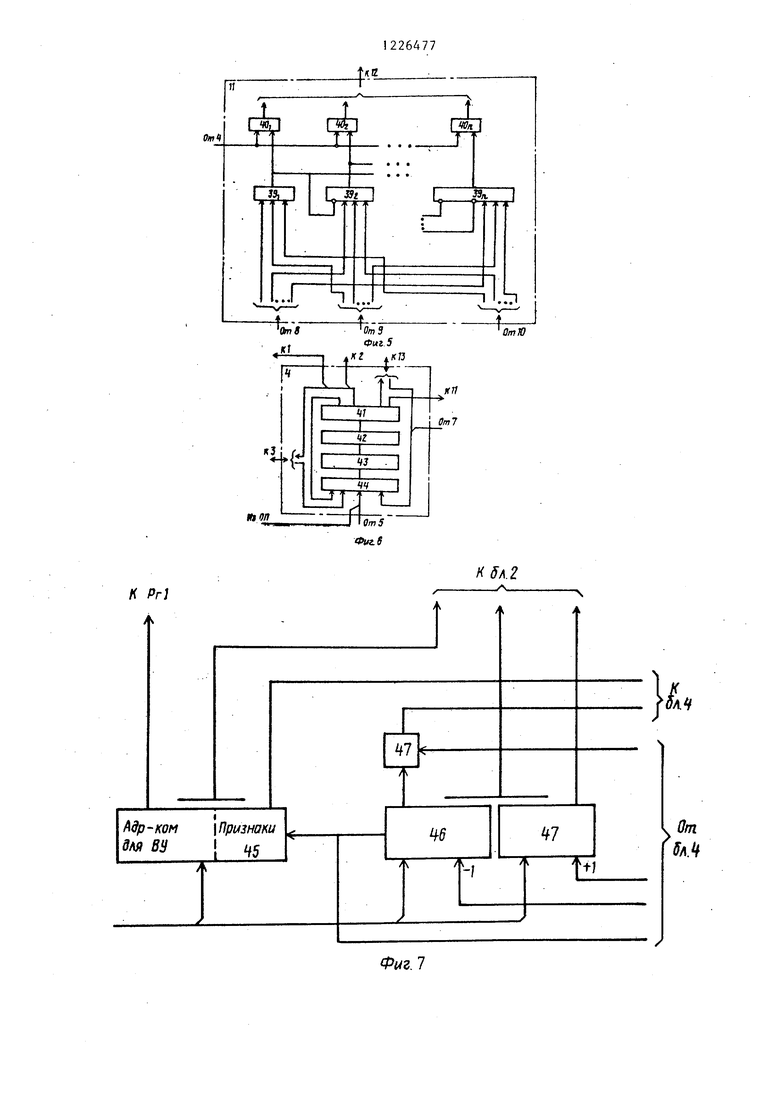

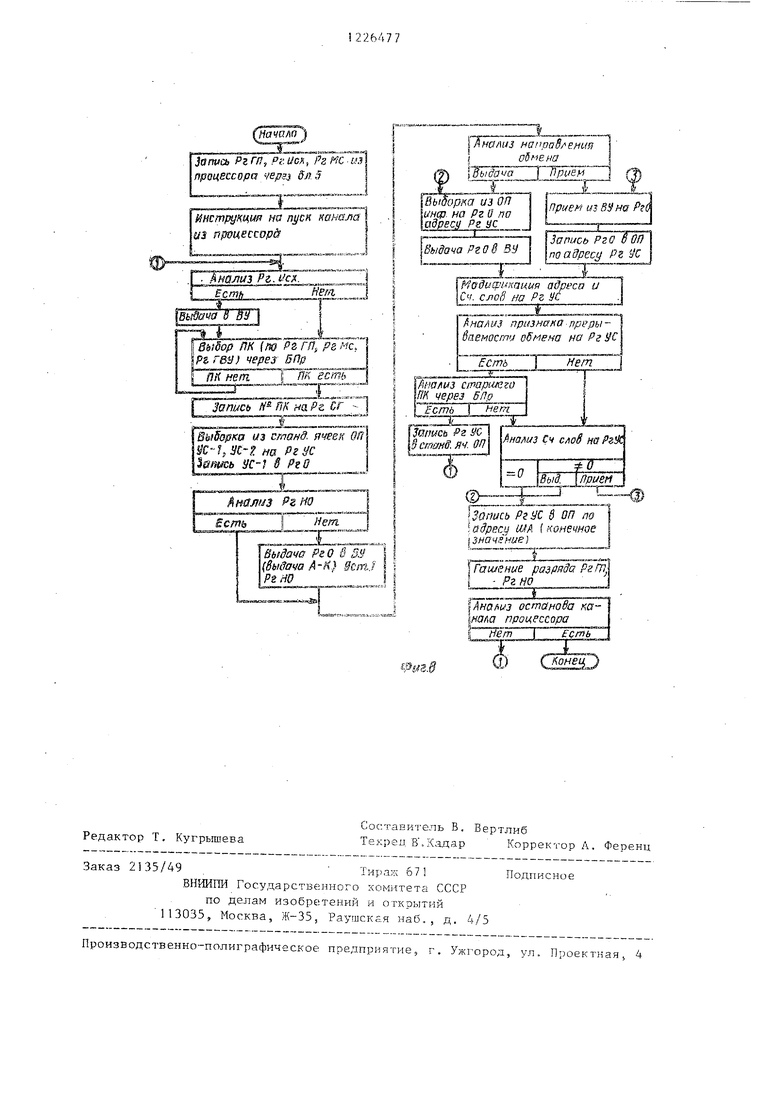

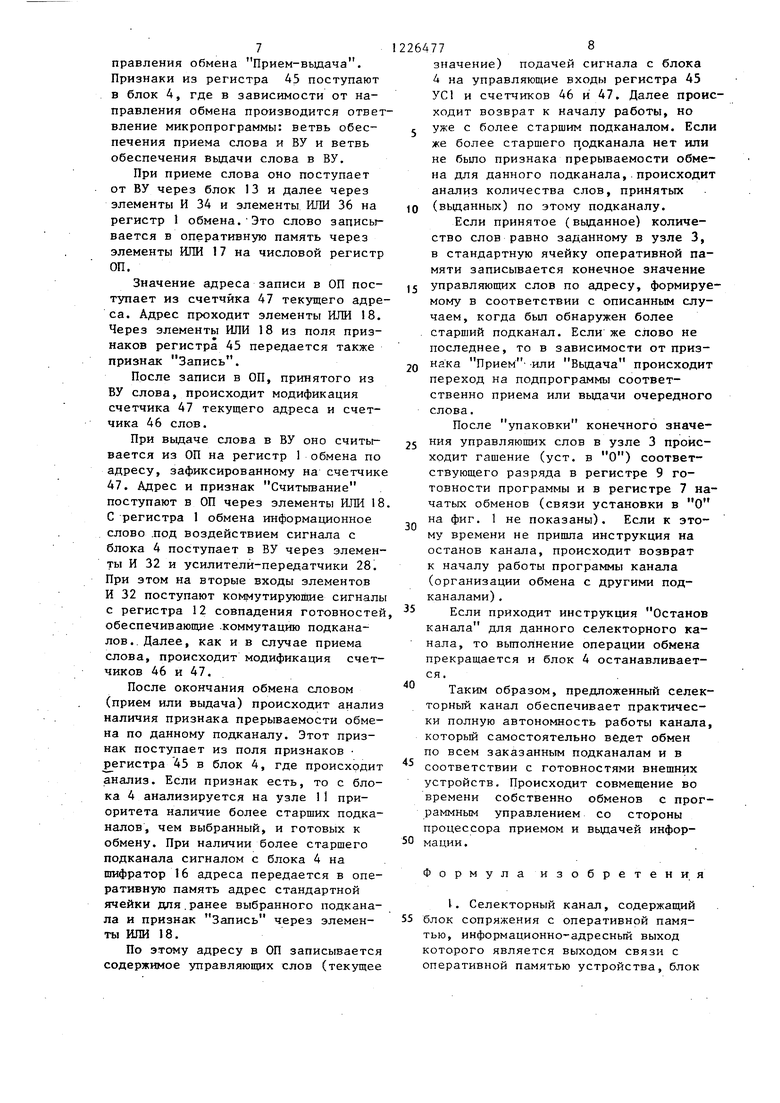

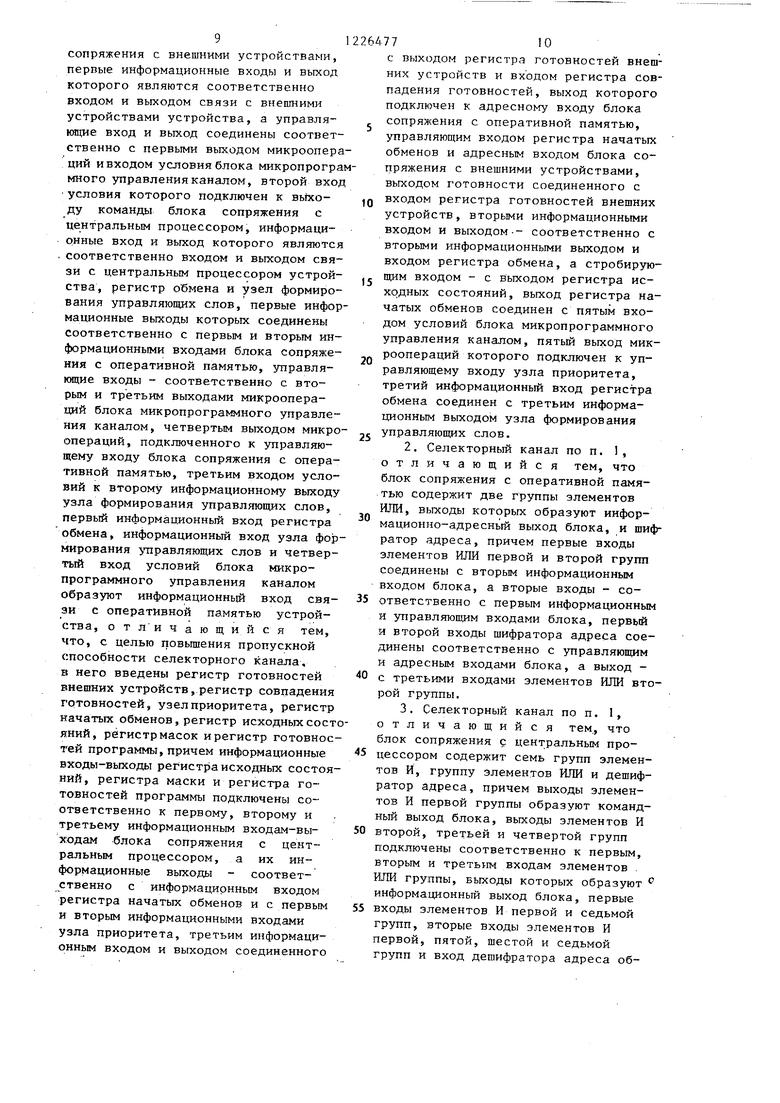

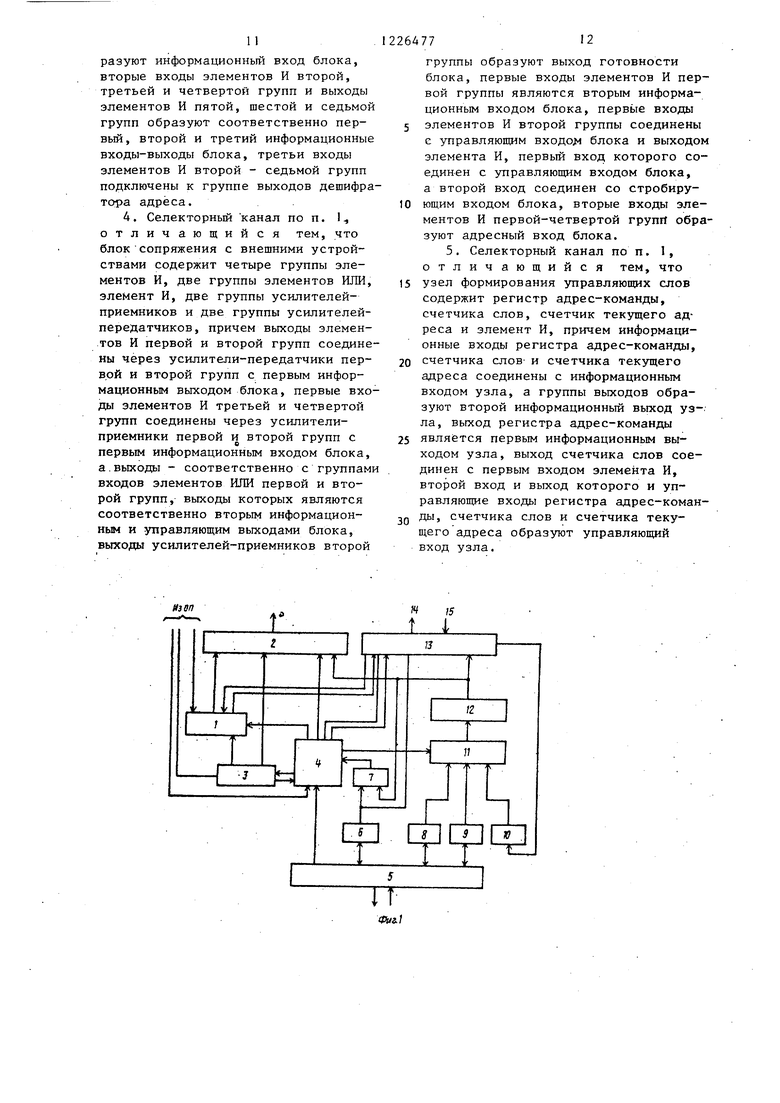

На фиг. 1 представлена блок-схема устройства;.на фиг. 2-7 - функциональные схемы блока сопряжения с оперативной памятью, блока сопряжения с центральным процессором, блока сопряжения с внешними устройствами, узла приоритета, блока управления канала и узла формирования управляющих слов; на фиг, 8 - блок-схема алгоритма блока управления канала.

Селекторный канал (фиг. 1) содержит регистр 1 обмена, блок 2 сопряжения с.оперативной памятью, узел 3 формирования управляющих слов, блок 4 микропрограммного управления каналом, блок 5 сопряжения с центральным процессором, регистр 6 исходньгх состояний, регистр 7 начатых обменов, регистр 8 масок, регистр 9 готовности программы, регистр 10 готовности внешних устройств, узел П приоритета, регистр 12 совпадения готовнос- тей, блок 13 сопряжения с внешними устройствами. Устройство обеспечивает обмен информацией с внетними устройствами по шинам 14 и 15 выхода и входа связи с внешними устройствами. Информация поступает из (в) внешних устройств через регистр 1 обмена и далее в (из) оперативнук память (не показана) с выхода блока 2 под управлением сигналов с блока 4, который использует при работе управляющие слова, зафиксированные в узле 3, Служебные сигналы готовностей к обмену Внешних устройств (ВУ), принимаемые в устройство по шинам 15, поступают через блок 13 на вход регистра 10.

Селекторный канал обеспечивает обмен информацией с набором внешн -гх устройств (источников и потребителей информации в соответствии с приоритетом подканалов. К каждому из подканалов через блок 13 и шины 14 и 15 может быть подключено одно или несколько внешних устройств.

Селекторный канал имеет прямой доступ к памяти (на фиг. 1 не пока |

226477

зано) через блок 2 ратикной памятью

10

|;5

20

25

30

35

XiO

45

SO

сопряжения с one- Связь с процессором (на фиг. 1 не показан) осуществляется с помоп1ью операций с адресуемыми регистрами и признаками через блок 5 сопряжения с процессором.

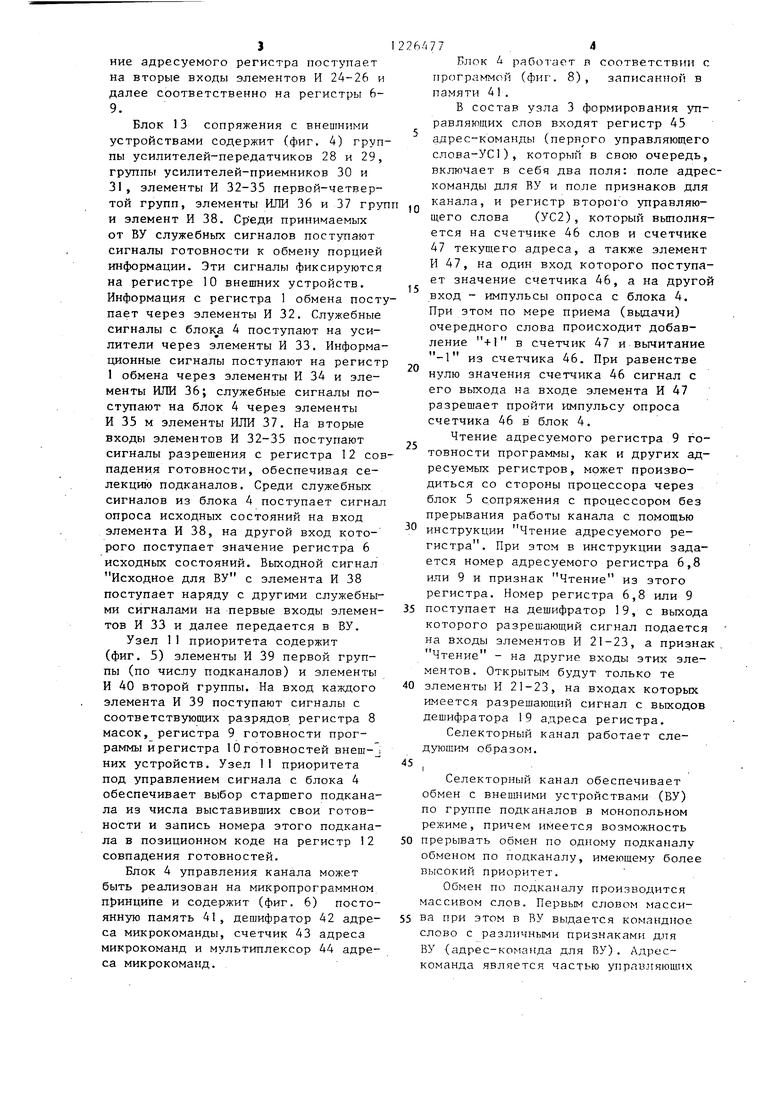

Блок 2 сопряжения с оперативной памятью содержит (фиг. 2) элементы ИЛИ 17 и 18 первой и второй групп и шифратор 16 адреса для формирования адреса ячейки оперативной памяти по значению регистра 12 и по сигналам блока 4. Выход щифратора 16 адреса подк.пючен к третьему входу элементов ИЛИ 18, на вторые и первые входы которых поступают разряды кода адреса с блока 4 и выхода узла 3. Сигналы с выходов элементов ИЛИ 18 поступают на адресный регистр оперативной памяти (не показан). На элементы ИЛИ 17 поступает информация с двух направлений: с регистра 1 и узла 3.. элементов ИЛИ 17 соединены с числовым регистром оперативной памяти. Информация с числового регистра оперативной памяти поступает на регистр 1 и узел 3. Для обеспечения временной диаграммы оперативной памяти в блок 4 поступает сигнал готовности от оперативной памяти (на чертеже не показан).

Блок 5 сопряжения с центральным процессором содержит (фиг. 3) дешифратор 19 адреса, элементы И 20-26 цервой-седьмой групп и элементы ИЛИ 27 группы. На элементы 20 поступает команда для канала с регистра команд процессора (не показан). На другие входы элементов И 20 поступает адрес канала из адресной части команды (в ЦВМ может быть несколько селекторных каналов). При операциях с адресуемъми регистрами номер регистра из адресной части команды поступает на дешифратор 19 адреса регистра, с выхода которого сигналы разрешения совместно с разрядами признаков (чтение, запись) из процессора поступают на элементы И 21- 23 (считывание из регистра) и на элементы И 24-26 (запись в регистр). На вторые входы элементов И 21- 23 поступают соответственно значения регистров 6-9, которые с выхода элементов И 21-23 через элементы ИЛИ27 поступают к буферным регистрам процессора (не показаны). Обратно с бу- iJiepHbix регистров процессора значение адресуемого регистра поступает на вторые входы элементов И 2А-26 и далее соответственно на регистры 6- 9.

Блок 13 сопряжения с внешними устройствами содержит (фиг. 4) группы усилителей-передатчиков 28 и 29, группы усилителей-приемников 30 и 31, элементы И 32-35 первой-четвер- той групп, элементы ИЛИ 36 и 37 гру и элемент И 38. Среди принимаемых от ВУ служебных сигналов поступают сигналы готовности к обмену порцией информации. Эти сигналы фиксируются на регистре 10 внешних устройств. Информация с регистра 1 обмена постпает через элементы И 32. Служебные сигналы с 4 поступают на усилители через элементы И 33. Информационные сигналы поступают на регист 1 обмена через элементы И 34 и элементы ИЛИ 36; служебные сигналы поступают на блок 4 через элементы И 35 м элементы ИЛИ 37. На вторые входы элементов И 32-35 поступают сигналы разрешения с регистра 12 сопадения готовности, обеспечивая селекцию подканалов. Среди служебных сигналов из блока 4 поступает сигна опроса исходных состояний на вход элемента И 38, на другой вход которого поступает значение регистра 6 исходных состояний. Выходной сигнал Исходное для ВУ с элемента И 38 поступает наряду с другими служебными сигналами на первые входы элементов И 33 и далее передается в ВУ.

Узел 11 приоритета содержит (фиг. 5) элементы И 39 первой группы (по числу подканалов) и элементы И 40 второй группы. На вход каждого элемента И 39 поступают сигналы с соответствующих разрядов регистра 8 масок, регистра 9 готовности программы и регистра 10 готовностей внеш-j них устройств. Узел 11 приоритета под управлением сигнала с блока 4 обеспечивает выбор старшего подканала из числа выставивших свои готовности и запись номера этого подканала в позиционном коде на регистр 12 совпадения готовностей.

Блок 4 управления канала может быть реализован на микропрограммном, принципе и содержит (фиг. 6) постоянную память 41, дешифратор 42 адреса микрокоманды, счетчик 43 адреса микрокоманд и мультиплексор 44 адреса микрокоманд.

10

226477 . 4

Блок 4 работает в соответствии с программой (фиг. 8), записантгой в памяти 41.

В состав узла 3 формирования управляющих слов входят регистр 45 адрес-команды (первого управляющего слова-УС), который в свою очередь, включает в себя два поля: поле адрес- команды для ВУ и поле признаков для канала, и регистр второх о управляющего слова (УС2), который выполняется на счетчике 46 слов и счетчике 47 текущего адреса, а также элемент И 47, на один вход которого поступает значение счетчика 46, а на другой вход - импульсы опроса с блока 4. При этом по мере приема (вьдачи) очередного слова происходит добавление + в счетчик 47 и вычитание -1 из счетчика 46. При равенстве нулю значения счетчика 46 сигнал с его выхода на входе элемента И 47 разрещает пройти импульсу опроса счетчика 46 в блок 4.

Чтение адресуемого регистра 9 готовности программы, как и других адресуемых регистров, может производиться со стороны процессора через блок 5 сопряжения с процессором без прерывания работы канала с помощью инструкции Чтение адресуемого регистра. При этом в инструкции задается номер адресуемого регистра 6,8 или 9 и признак Чтение из этого регистра. Номер регистра 6,8 или 9 35 поступает на дешифратор 19, с выхода которого разрешающий сигнал подается на входы элементов И 21-23, а признак. Чтение - на другие входы этих элементов. Открытым будут только те элементы И 21-23, на входах которых имеется раэрешаюпщй сигнал с выходов дешифратора 19 адреса регистра.

Селекторный канал работает следующим образом.

25

30

40

,

Селекторный канал обеспечивает

обмен с внесшими устройствами (ВУ) по группе подканалов в монопольном режиме, причем имеется возможность

прерывать обмен по одному подканалу обменом по подканалу, имеющему более высокий приоритет.

Обмен по подканалу производится ассивом слов. Первым словом массива при этом в ВУ выдается командное слово с различными признаками для ВУ (адрес-ко 1анда для ВУ) . Адрес- команда является частью упраиляюших

СЛОВ для канала (часть УС 1) и фиксируется на узле 3.

Для фиксации подканалов, с которыми обмен уже начат (соответствующая адресу команда-выдана)S используется регистр 7 начатых обменов, где позиционньм кодом зафиксированы эти подканалы.

Селекторный канал может также устанавливать в исходное состояние ВУ, выдавая туда соответствующий служебный сигнал. Информацией для этой вьиачи служит содержимое регистра 6 исходных состояний, где в позиционном коде содержатся номера подканалов (одного или нескольких), которы необходимо установить в исходное состояние.

Работа канала происходит в соответствии с алгоритмом фиг. 7. После формирования массива управляющих слов УС) и УС2 происходит запись содержимого на регистр 9 готовности программы, регистр 8 масок и регист 6 исходных состояний. Запись производится со стороны процессора через блок 5 без прерывания работы канала с помощью инструкции Запись в адресуемый регистр. При этом в инструкции адрес-команды задается номер адресуемого регистра (6,8 или 9) и признак Запись в этот регистр. Номер регистра поступает на дешифрато 19, который формирует разрешающий сигнал записи на признак Запись - на входы элементов И 24-26. Запись произойдет только в тот адресуемый регистр канала 6,8 и 9, номер которого указан в инструкции и дешифрован дешифратором 19.

На регистре 10 фиксируются готовности ВУ, которые поступают от ВУ специальными сигналами в составе сл жебньЕХ сигналов через блок 13 сопряжения с внешними устройствами, а в последнем - ч.ерез усилители-приемники 3.

Далее со стороны процессора производится пуск селекторного канала с помощью инструкции Пуск канала. Код операции при этом поступает на элементы И 20, на другие входы которых подается сигнал адреса этого канала (так как каналов может быть несколько). Если в инструкции указа код (адрес) этого канала, то код операций Пуск канала поступает н блок 4 и в последнем устанавливаетс

0

0

5

5

начальная микрокоманда операции обмена. Далее канал работает автономно под действием микроопераций с блока 4. Остановить канал может только процессор путем выдачи инструкции Останов канала.

В процессе работы канала блок 4 опрашивает регистр 6 исходных состояний путем вьщачи сигнала на вход элемента И 38, на другой вход которого поступает значение регистра 6. Выходной сигнал Исходное для БУ с элемента И 38 поступает наряду с други1 1и служебными сигналами на пер- 5 вые входы группы элементов И 33 и далее передается в ВУ через усилители-передатчики 29.

Далее блок 4 управления подает сигнал на узел 11 приоритета, который определяет старший подканал из числа готовых к обмену. Номер выбранного подканала передается на регистр 12 совпадения готовностей, где сохраняется в течение всего времени обмена с выбранным подканалом.

По выбранному номеру подканала формируется адрес ячейки оперативной памяти (ОП), где хранится заказ на обмен (УС1 и УС2) для данного (выбранного) подканала. Адрес формируется в блоке 2 с помощью шифратора 16 адреса, на входы которого поступают сигналы с блока 4 регистра 12 совпадения готовностей. Сформированный адрес через элементы ИЛИ 18 поступает на адресный регистр оперативной памяти. По этому адресу значение УС1 и УС2 записьшается в узел 3.

Под воздействием сигналов с блока 4 часть УС 1 (адрес-команда) передается на регистр 1 обмена и далее через блок 13 - в соответствующее ВУ (подключенное к данному подканалу). Вьщача адрес-команды в ВУ происходит только в начале обмена для данного подканала.

При вьщаче адрес-команды в ВУ блок 4 заносит 1 в соответствующий разряд регистра 7 (связь на фиг, не показана). При обмене очередным словом в блоке 4 анализируется состояние соответствующего разряда регистра 7 начатых обменов, иск- .пючая, таким образом, последующую вьщачу адрес-команды для этого подканала.

Среди признаков, принимаемых в составе УС1, содержится признак на0

5

5

0

7

правления обмена Прием-вьщача. Признаки из регистра 45 поступают в блок 4, где в зависимости от направления обмена производится ответвление микропрограммы: ветвь обеспечения приема слова и ВУ и ветвь обеспечения выдачи слова в ВУ.

При приеме слова оно поступает от ВУ через блок 13 и далее через элементы И 34 и элементы ИЛИ 36 на регистр 1 обмена. Это слово записывается в оперативную память через элементы ИЛИ 17 на числовой регистр ОП.

Значение адреса записи в ОП поступает из счетчика 47 текущего адреса. Адрес проходит элементы ИЛИ 18. Через элементы ИЛИ 18 из поля признаков регистра 45 передается также признак Запись.

После записи в ОП, принятого из ВУ слова, происходит модификация счетчика 47 текущего адреса и счетчика 46 слов.

При выдаче слова в ВУ оно считывается из ОП на регистр 1 обмена по адресу, зафиксированному на счетчике 47. Адрес и признак Считывание поступают в ОП через элементы ИЛИ 18 С регистра 1 обмена информационное слово .под воздействием сигнала с блока 4 поступает в ВУ через элементы И 32 и усилители-передатчики 28. При этом на вторые входы элементов И 32 поступают коммутирующие сигналы с регистра 12 совпадения готовностей обеспечивающие .коммутацию подканалов.. Далее, как и в случае приема слова, происходит модификация счетчиков 46 и 47.

После окончания обмена словом (прием или выдача) происходит анализ наличия признака прерываемости обмена по данному подканалу. Этот признак поступает из поля признаков регистра 45 в блок 4, где происходит анализ. Если признак есть, то с блока 4 анализируется на узле 11 приоритета наличие более старщих подканалов, чем выбранный, и готовых к обмену. При наличии более старшего подканала сигналом с блока 4 на шифратор 16 адреса передается в оперативную память адрес стандартной ячейки дпя.ранее выбранного подканала и признак Запись через элементы ИЛИ 18.

По этому адресу в ОП записывается содержимое управляющих слов (текущее

264778

значение) подачей сигнала с блока 4 на управляющие входы регистра 45 УС1 и счетчиков 46 и 47. Далее происходит возврат к началу работы, но уже с более старшим подканалом. Если же более старшего п одканала нет или не было признака прерываемости обмена для данного подканала,.происходит анализ количества слов, принятых

0 (выданных) по этому подканалу.

Если принятое (выданное) количество слов равно заданному в узле 3, в стандартную ячейку оперативной памяти записывается конечное значение

)5 управляющих слов по адресу, формируемому в соответствии с описанным случаем, когда был обнаружен более старший подканал. Если же слово не последнее, то в зависимости от приз2Q нака Прием или Выдача происходит переход на подпрограммы соответственно приема или выдачи очередного слова.

После упаковки конечного значе25 ния управляющих слов в узле 3 происходит гащение (уст. в О) соответствующего разряда в регистре 9 готовности программы и в регистре 7 начатых обменов (связи установки в О на фиг. 1 не показаны). Если к этому времени не пришла инструкция на останов канала, происходит возврат к началу работы программы канала (организации обмена с другими подканалами) .

35 Если приходит инструкция Останов канала для данного селекторного канала, то вьтолнение операции обмена прекращается и блок 4 останавливается .

Таким образом, предложенный селекторный канал обеспечивает практически полную автономность работы канала, которьм самостоятельно ведет обмен по всем заказанным подканалам и в

соответствии с готовностями внешних устройств. Происходит совмещение во времени собственно обменов с программным управлением со стороны процессора приемом и выдачей инфор50 нации.

Формула изобретения

I. Селекторный канал, содержащий 55 блок сопряжения с оперативной памятью, информационно-адресный выход которого является выходом связи с оперативной памятью устройства, блок

30

опряжения с внешними устройстваьш,

ервые информационные входы и выход оторого являются соответственно входом и выходом связи с внешними стройствами устройства, а управлящие вход и выход соединены соответственно с первыми выходом микроопераций и входом условия блока микропрограммного управления каналом, второй вход

условия которого подключен к вьЬсо- ду команды блока сопряжения с центральным процессором, информационные вход и выход которого являются

соответственно входом и выходом связи с центральным процессором устройства, регистр обмена и узел формирования управляющих слов, первые информационные выходы которых соединены соответственно с первым и вторым информационными входами блока сопряжения с оперативной памятью, управля- кицие входы - соответственно с вторым и третьим выходами микроопераций блока микропрограммного управления каналом, четвертым выходом микроопераций, подключенного к управляющему входу блока сопряжения с оперативной памятью, третьим входом условий к второму информационному выходу узла формирования управляющих слов, первый информационный вход регистра

обмена, информационный вход узла формирования правляющих слов и четвертый вход условий блока микропрограммного управления каналом образуют информационный вход связи с оперативной памятью устройства, отл ичающийся тем, что, с целью повьшения пропускной способности селекторного канала, в него введены регистр готовностей внешних устройств, регистр совпадения готовностей, узел приоритета, регистр начатых обменов,регистр исходных состояний, регистр масок и регистр готовностей программы, причем информационные входы-выходы рег истра исходных состояний, регистра маски и регистра готовностей программы подключены соответственно к первому, второму и третьему информационным входам-выходам блока сопряжения с центральным процессором, а их информационные выходы - соответственно с информационным входом регистра начатых обменов и с первым и вторым информационными входами узла приоритета, третьим информаци- онньм входом и выходом соединенного

5

с выходом регистра готовностей внешних устройств и входом регистра совпадения готовностей, выход которого подключен к адресному входу блока сопряжения с оперативной памятью, управляющим входом регистра начатых обменов и адресным входом блока сопряжения с внешними устройствами, выходом готовности соединенного с

входом регистра готовностей внешних устройств, вторыми информационными входом и выходом-- соответственно с вторыми информационными выходом и входом регистра обмена, а стробирую- щим входом - с выходом регистра исходных состояний, выход регистра начатых обменов соединен с пятым входом условий блока микропрограммного управления каналом, пятый выход микроопераций которого подключен к управляющему входу узла приоритета, третий информационный вход регистра обмена соединен с третьим информа- ционньпУ выходом узла формирования

5 управляющих слов.

2.Селекторный канал по п. I, отличающийся тем, что блок сопряжения с оперативной памятью содержит две группы элементов ИЛИ, выходы которых образуют инфор- мационно-адресньгй выход блока, и щиф- ратор адреса, причем первые входы элементов ИЛИ первой и второй групп соединены с вторым информационным входом блока, а вторые входы - со5 ответственно с первым информационным и управляющим входами блока, первый и второй входы шифратора адреса соединены соответственно с управляющим и адресным входами блока, а выход 0 с третьими входами элементов ИЛИ второй группы.

3.Селекторный канал по п. 1, отличающийся тем., что блок сопряжения с центральным про5 цессором содержит семь групп элементов И, группу элементов ИЛИ и дешифратор адреса, причем выходы элементов И первой группы образуют командный выход блока, выходы элементов И

0 второй, третьей и четвертой групп подключены соответственно к первым, вторым и третьим входам элементов . ИЛИ группы, выходы которых образуют информа:ционный выход блока, первые

5 входы элементов И первой и седьмой групп, вторые входы элементов И первой, пятой, Шестой и седьмой групп и вход дешифратора адреса об0

разуют информационный вход блока, вторые входы элементов И второй, третьей и четвертой групп и выходы элементов И пятой, шестой и седьмой групп образуют соответственно первый, второй и третий информационные входы-выходы блока, третьи входы элементов И второй - седьмой групп подключены к группе выходов дешифратора адреса.

4. Селекторный канал по п. 1., отличающийся тем, что блок сопряжения с внешними устройствами содержит четыре группы элементов И, две группы элементов ИЛИ, элемент И, две группы усилителей- приемников и две группы усилителей- передатчиков, причем выходы элементов И первой и второй групп соединены через усилители-передатчики первой и второй групп с первым информационным выходом блока, первые входы элементов И третьей и четвертой групп соединены через усилители- приемники первой и второй групп с первым информационным входом блока, а выходы - соответственно с группам входов элементов ИЛИ первой и второй групп, выходы которых являются соответственно вторым информационным и управляющим выходами блока, выходы усилителей-приемников второй

группы образуют выход готовности блока, первые входы элементов И первой группы являются вторым информационным входом блока, первые входы

элементов И второй группы соединены с управляющим входо 1 блока и выходом элемента И, первый вход которого соединен с управляющим входом блока, а второй вход соединен со стробирующим входом блока, вторые входы элементов И первой-четвертой групй образуют адресный вход блока.

5. Селекторный канал по п. 1, отличающийся тем, что

узел формирования управляющих слов содержит регистр адрес-команды, счетчика слов, счетчик текущего адреса и элемент И, причем информационные входы регистра адрес-команды,

счетчика слов и счетчика текущего адреса соединены с информационным входом узла, а группы выходов образуют второй информационный выход узла, выход регистра адрес-команды

является первым информационным выходом узла, выход счетчика слов соединен с первым входом элемента И, второй вход и выход которого и управляющие входы регистра адрес-команды, счетчика слов и счетчика текущего адреса образуют управляющий вход узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1978 |

|

SU750473A1 |

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

| Устройство для сопряжения процессоров обмена с внешними устройствами | 1984 |

|

SU1257650A1 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Устройство для сопряжения | 1980 |

|

SU947849A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения | 1984 |

|

SU1166126A2 |

| Устройство для сопряжения | 1978 |

|

SU813401A2 |

| Система обмена | 1978 |

|

SU809138A1 |

Изобретение относится к области вычислительной техники и может быть использовано в ЭВМ для обмена информацией между оперативной памятью и внешними устройствами. Целью изобретения является повышение пропускной способности канала. Поставленная цель достигается тем, что в селекторный канал, содержащий блоки сопряжения с оперативной памятью, внешними устройствами и центральньм процессором, блок микропрограммного управления каналом, регистр обмена и узел формирования управляющих слов, введены регистры готовностей внешних устройств, регистр совпадения готоБностей, узел приоритета, регистр начатых обменов, регистр исходных состояний , регистр массы и регистр готовностей программы. 4 з.п. ф-лы, 8 ил. i т to О) 419 -Nj sj

изеп

Г

Г . TJ

ф ффСЦ

ТТ

Фиг.

к

к5Kiк9

-4-4--4-втП

W Izs гв

а

ffl

юсжзс-д

КатнЛ Hpet Чпянве Затп 4 Г

XOHIHf V 11 .- .

fipKmjM аеизная, «Зчяр. i. птхссора

«OTguft/, ,;,

Cm 5

ffm/Z

Г

thni

;

0m 8

JLL

1

11

n3

oit

и

.г I

r

t j .

От 5 fmS

ОтЮ

;г7/

4J

От

.г I

От 5 fmS

др-ком Признаки дм ВВ 5

47

Ч

tn

От 5лМ

Фиг. 1

Начат

Запись Рг г/7, рг:. иск, Рг МС ш процессора /epsj 8л. 5

MHcmfH/кцт на nj/cn i anajja J3 процессоре

, выдача

Выборка из дп инср. на Рг О по адрес / PS ус

Ана/шз HafifldS/ efn,} обменаI

ПВыдача Рго8 ВУ

Пpit ем изВУна Т

Запис ьРго ТО) noadpecij Рг з С

Анализ Pz..

Her/t

Г

выбор лк (по Pz гп, ре , Ре БПр

7иПкпГ ° 1Г к с

Janucb ЯЛ т Рг сг

Л

Выборка us сгпанд. ячеек ОП УС-1,К-. на Зегдасб AT- 6 PeS

Выдаче РгО 8 8,У (8ы(7та А-К} Sent} PS НО

Моди(1 ика14т адреса и Сч. слод на Рг УС

ж- f нал из признака преры - 6aeMOcm j обмена на Рг УС

l/fw/wj cinapuiew Ш через ВПр

i cmb

fjO/WCu PsW}

Sc.frisfie. /. ОП

АноАиз f у слов не Рг

ffpifeti

(.

l onucb РгХ § on т

.; йдреси ША {конечное 13начё ние}

I Гашение разряде PsfTl, Ргно

Редактор Т, Кугрьппева Заказ 2135/49

Составитель В. Вер

Техрец В .Кздар

Тираж 67 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприеп

Ана(из останова ка нам npoi eccopa

пет

Есть

Составитель В. Вертлиб

Техрец В .Кздар Корректор А. Ференц

Подписное

тие, г. Ужгород, ул. Проектная, 4

| Селекторный канал | 1981 |

|

SU1029175A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дроздов Е | |||

| А | |||

| и др | |||

| ЭВМ единой серии | |||

| М.: Машиностроение, 1976, рис | |||

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1986-04-23—Публикация

1983-12-30—Подача