(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессоров обмена с внешними устройствами | 1984 |

|

SU1257650A1 |

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

| Устройство для сопряжения | 1979 |

|

SU840868A2 |

| Устройство для сопряжения | 1980 |

|

SU947849A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Устройство для сопряжения | 1978 |

|

SU736086A1 |

| Устройство для сопряжения | 1984 |

|

SU1166126A2 |

| Устройство для сопряжения | 1978 |

|

SU809139A2 |

| Устройство для сопряжения | 1978 |

|

SU813401A2 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

1

Изобретение относится к вычислитеаьной технике -и может быть использовано в вычислительных системах.

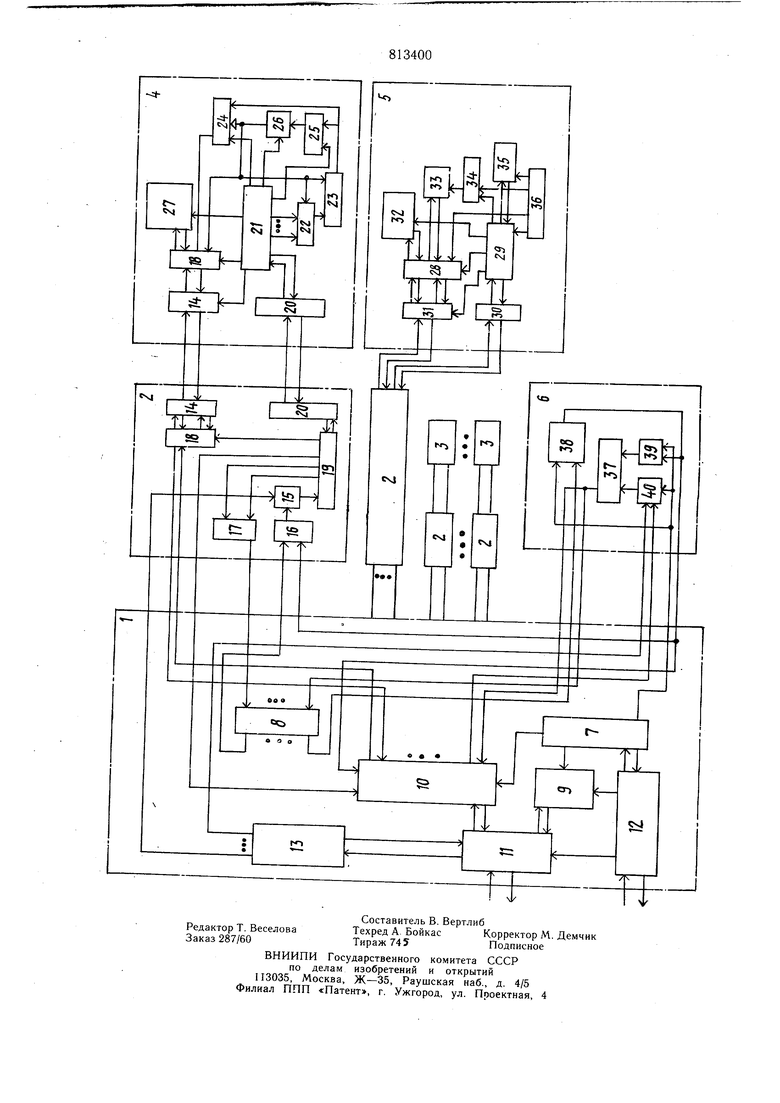

По основному авт. св. № 736086 известно устройство для сопряжения, содержащее подканалы абонентов, блок приоритета, блок синхронизации, регистр готовности программы, коммутатор информации, блок контроля по модулю, регистр обмена, первые вход и выход которого являются соответственно первыми управляющими входом и выходом устройства, а вторые входы информационными входом и выходом устройства, блок управления обменом первые,вход и выход которого являются соответственно первыми управляющими входом и выходом устройства, а вторые вход и выход подключены соответственно к первым выходу и входу блока синхронизации, второй и третий выходы которого соответственно подключены к первым входам подканалов абонентов и управляющему входу блока приоритета, входы запросов и выходы разрешения которого соединены соответственно с первыми выходами и вторыми входами соответствующих подканалов абонентов, третьи входы которых подключены к управляющим выходам регистра готовности программы, подключенного информационными входами и выходами соответственно ко вторым выходу и входу регистра обмена, а управляющим входом - к четвертому выходу блока синхронизации, пятый выход которого соединен с третьим входом блока контроля по модулю, подключенного первым входом и выходом соответственно к третьим выходу и входу регистра обмена, а вторым входом - к третьему выходу блока управления, четвертый выход которого подключен к пятому входу регистра обмена, четвертые выход и вход которого соединены соответственно с информационными входом и выходом коммутатора информации, управляющий вход KOTOS рого подключен к шестому выходу блока синхронизации, а выходы и входы группы информационных входов и выходов и входы группы адресных входов соединены соответственно с четвертыми входами, вторыми и третьими выходами соответствующих подканалов абонентов, информационные входы и выходы и управляющие входы и выходы которых являются соответственно вторыми информационными входами и выходами и вторыми управляющими входами и выходами устройства. Кроме того, каждый подканал абонента содержит узел управления, регистр служебных сигналов, первые вход и выход которого соединены соответственно с первым выходом и входом узла управления, а вторые выход и вход являются соответственно управляющими выходом и .входом подканала, коммутатор типа передачи, соединенный первыми входом и выходом соответственно с первыми выходом и входом регистра обмена подканала, вторые вход и выход которого являются соответственно четвертым входом и вторым выходом подканала, элемент И; первый вход которого является третьим входом подканала, а выход соединен со вторым входом узла управления, третий и четвертый выходы которого соединены соответственно с третьими входами коммутатора типа передачи и регистра обмена подканала, а пятый выход - с третьим выходом подканала, треггер готовности, соединенный входом и выходом соответственно с шестым выходом узла управления и с первым выходом подканала, информационные вход и выход которого являются соответственно вторыми входом и выходом коммутатора типа передачи, и элемент ИЛИ, входы которого являются соответственно первым и вторым входами подканала; а выход соединен со вторым входом элемента И 1. Недостаток этого устройства состоит в низкой надежности устройства и достоверности передачи информации, что обусловлено отсутствием контроля тракта обмена на интервалах времени, когда отсутствует обмен между абонентами и процессом обмена. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в устройство для сопряжения введена группа блоков имитации внешнего устройства и блок имитации интерфейса, причем информационные и управляющие входы и выходы каждого блока имитации внешнего устройства соединены соответственно со вторыми информационными и управляю. щими выходами и входами соответствующего подканала абонента, первый вход блока имитации интерфейса подключен ко второму выходу блока синхронизации, первый выход и второй вхоа - к соответствующим входу и выходу блока приоритета, третий вход - к соответствующему выходу регистра готовности программы, второй выход и четвертый вход - к соответствующим входу и выходу группы информационных входов и выходов коммутатора информации, а третий выход - к соответствующему входу группы адресных входов коммутатора информации. Кроме того, блок имитации интерфейса содержит триггер готовности программы, выход которого соединен с первым и вторым выходами блока, а первый и второй входы - соответственно с выходами первого и второго элементов И, и триггер работы контрольного подканала, epвый вход которого соединен со вторым входом блока, второй вход -с первыми входами блока и первого и второго элементов И, а выход - с третьим выходом блока и вторым входом первого элемента И, второй вход второго элемента И является .четвертым входом блока. Кроме того, блок имитации внешнего устройства содержит коммутатор типа передачи, информационные вход и выход которого являются соответственно информационными входом и выходом блока, регистр обмена, соединенный двухсторонними связями с коммутатором типа передачи и узлом свертки, регистр служебных сигналов. первые вход и выход которого являются соответственно управляющими входом и выходом блока, а вторые вход и выход соединены соответственно с первыми выхоДО и входом узла синхронизации,, второй. третий и четвертый выходы которого подключены соответственно . к управляющему входу коммутатора типа передач, входу узла контроля и первому входу регистра обмена, вторым входом соединенного с выходом триггера выработки шахматных кодов, а третьим входом - с выходом элемента И, входом счетчика сдвигов, первым входом дешифратора нуля и счетным входом триггера выработки шахматных кодов, первый вход которого соединен с выходом дещифратора нуля и первым входом триггера пуска, а второй вход - с пятым выходом узла синхронизации, шестой и седьмой выходы которого подключены соответственно ко второму входу триггера пуска, соединенного выходом с первым входом элемента И, и второму входу элемента И, второй вход дешифратора нуля соединен с выходом счетчика сдвигов, группа входов которого подключена к группе выходов узла синхронизации. При этом блок имитации внещнего устройства содержит коммутатор типа передачи, информационные вход и выход которого являются соответственно информационными входом и выходом блока, регистр обме соединенный двухсторонними связями с коммутатором типа передачи и узлом свертки, регистр служебных сигналов, первые вход и выход которого являются соответственно управляющими входом и выходом блока, а вторые вход и выход соединены соответственно с первыми выходом и управляЮщим входом узла синхронизации, второй, третий и четвертый выходы которого соединены соответственно с управляющим входом коммутатора типа передачи, входом узла свертки и первым входом регистра обмена, выход и второй вход которого подключены соответственно к информационным входу и выходу памяти, адресный вход которой соединен с выходом регистра адреса, входом подключенного к пятому выходу узла синхронизации, шестой выход и первый установочный вход которого соединены соответственно с первым входом и выходом счетчика числа слов, подключенного вторым входом к первому выходу узла ввода, второй выход которого соединен с третьим входом регистра обмена, а третий выход - со вторым установочным входом узла синхронизации. На чертеже представлена блок-схема устройства. Устройство содержит мультиплексор 1, подканалы 2 абонента, внешние устройства 3, блок 4 имитации внешнего устройства, выдающего или принимающего слова «шахматной структуры, блок 5 имитации внешнего устройства, выдающего или принимающего массивы слов произвольной структуры, блок б имитации интерфейса. Мультиплексор 1 состоит из блока 7 синхронизации, блока 8 приоритета, блока 9 контроля по модулю, коммутатора 10 информации,, регистра 11 обмена, блока 12 управления обменом с процессором и регистра 13 готовности программы. Каждый подканал 2 абонента включает коммутатор 14 типа передачи, элемент И 15, элемент И 16, триггер 17 готовности подканала, регистр 18 обмена, узел 19 управления подканала и регистр 20 служебных сигналов. Блок 5 кроме коммутатора 14 типа передачи, регистра 18 обмена и регистра 20 служебных сигналов содержит узел 21 синхронизации, счетчик 22 сдвигов, дешифратор 23 нуля, триггер 24 выработки шахматных кодов, триггер 25 пуска, элемент 26 и узел 27 свертки. Блок 6 содержит регистр 28 обмена, узел 29 синхронизации, регистр 30 служебных сигналов, коммутатор 31 типа передачи, узел 32 свертки, память 33, регистр 34 адреса, счетчик 35 числа сл.ов и узел 36 ввода (наборное устройство). Блок 7 содержит триггер 37 готовности программы, триггер 38 работы контрольного подканала, элементы И 39 и 40. Устройство работает следующим образом. Процессор обмена в начале работы выдает в мультиплексор I команду рабочего режима, которая расшифровывается и по которой устанавливаются в соответствующие . состояния подканалы 2. Затем процессор обмена для задания набора внешних устройств, с которыми необходимо производить обмен, выдает в мультиплексор 1 значение регистра готовности программы. Мультиплексор 1 производит пуск только тех подканалов 2, в соответствующих триггерах регистра 13 которых записаны единицы. Далее запущенные подканалы 2 работают одновременно и независимо, выдавая или принимая одно с.дово информации из внешнего устройства 3 в соответствии с конкретной временной диаграммой последнего. Выдача или прием одного слова подканала 2 заканчивается выдачей сигнала готовности к обмену мультиплексору I, который с помощью блока 8 приоритета схемы определяет старший подканал 2 из числа выставивших свои готовности и организует выдачу (прием) Слова из него в процессор обмена или наоборот. Обмен информацией с процессором обмена происходит в два этапа. На первом этапе мультиплексор 1, анализируя регистр 13, формирует и передает номер старшего подканала 2 из числа выставивших свои готовности в позиционном коде с контрольными разрядами по модулю 3 в процессор обмена, который по этому номеру готовит адрес буферной зоны памяти для записи или считывания слова информации. На втором этапе происходит собственно передача слова информации из выбранного подканала 2 в процессор обмена или наоборот из процессора обмена в один из подканалов 2 для дальнейшей передачи во внешнее устройство. После окончания второго этапа цикл обмена повторяется с тем же самым или с другим подканалом 2. Таким образом, имеет место режим мультиплексного обмена с разделением времени канала между многими внешними устройствами и процессором обмена. Обмен с каждым подканалом и соответствующим внешним устройством происходит, как правило, массивом слов. Об окончании массива сообшает служебный признак конца обмена, принимаемый В подканал 2 от внешнего устройства или от процессора обмена в зависимости от того, кто определяет длину массива. В обоих случаях этот подканал 2 исключается из обмена посредством установки в «О соответствующего триггера регистра 13 и последующей установки в исходное состояние самого подканала 2 со стороны мультиплексора 1. Исключение подканала 2 из обмена может также происходить при программном задании от процессора обмена нового значения регистра готовности программы с нулем в соответствующем разряде. Соответствующие подканалы 2 обеспечивают прием (выдачу) слов заданной струк туры от подключенных к ним блоков имитации в соответствии с конкретным типом . интерфейса последнего и передачу (прием) его в принятом режиме мультиплексного обмена в (из) процессор обмена. Таким образом, наряду с обменами с реальными внешними устройствами происходит обмен по мультиплексному каналу с «фиктивными внешними устройствами (блоки 4 и 5), введенными в устройство. Чтобы не происходило существенного увеличения времени на обмен с реальными внешними устройствами из-за затрат времени канала на обмен с указанными «фиктивными внешними устройствами, последним назначен в мультиплексоре самый низкий приоритет. При увеличении потока информации в канале обмен с «фиктивными внешними устройствами может быть прекращен программным заданием нового значения регистра 13 готовности программы, поступающего с нулями в разрядах, соответствующих «фиктивным внешним устройствам. . Введение блоков 4 и 5 имитации внешних устройств позволяет в начале работы и в процессе работы непрерывно контролировать оборудование как собственно мультиплексного канала, так и всего тракта вплоть до сопряжения подканалов с мультиплексором. В процессе работы устройства информация и; служебные сигналы поступают по двусторонним линиям связи от (в) процессора обмена (на чертеже не показан), причем информация поступает на (из) регистр 11, а служебные сигналы в (из) блок 12 управления обменом с процессором. С выхода регистра 11 обмена информация поступает по двусторонней связи в (из) подканалы 2 через коммутатор 10. Непосредственно обменом информацией с процессором обмена управляет в соответствии с временной диаграммой последнего блок 12. Блок 7 обеспечивает взаимодействие всех блоков мультиплексора 1 и подканалов 2. На соответствующие входы блока 8 поступают сигналы готовности к обмену от тех подканалов 2, которые готовы к обмену очередным словом информации. Блок 8 приоритета под воздействием сигнала с блока 7 синхронизации обеспечивает выдачу сигнала на один (старший) из подканалов 2, который через коммутатор 10 подключается к регистру I1 на время передачи номера соответствующего подканала, выбранного блоком 8 и слова информации в (из) процессор обмена. Блок 7, обеспечив передачу номера и слова информации в (из) регистр обмена, выдает сигнал в блок 9 и в блок 12, который обеспечивает передачу номера подканала 2, а затем слова информации в (из) процессор обмена. Закончив передачу очередного слова информации блок 12 выдает сигнал блоку 7 о том, что регистр 11- свободен и готов к передаче слова информации из другого подканала. Выбранный с блока 8 подканал подает сигнал на коммутатор 10, который обеспечивает прохождение информации от (в) выбранного подканала. Все подканалы 2 имеют одинаковую структуру, причем коммутатор 14 типа передачи предназначен для выбора формы передачи информации между , регистром 18 и внешним устройством (последовательной или параллельной) . Выбор формы передачи определяет конкретное внешеее устройство. Регистр 20 служебных сигналов предназначен для фиксации при приеме от внещнего устройства и для выдачи во внешнее устройство служебных сигналов, сопутствующих иачальному этапу обмена, установившемуся этапу и заключительному этапу обмена информацией с срответствующим внешним устройством или имитатором. На входы элемента И 16 приходят в разное время сигналы пуска узла 19 от блоков 8 и 7. С выхода элемента И 16 сигнал пуска проходит через элемент И 15 только при наличии разрешающего потенциала на выходе соответствующего триггера регистра 13 готовности программы. При приеме информации от внешнего устройства коммутатор 14 под воздействием сигнала с узла 19 открывает соответствующие цепи (параллельные или последовательные) выдачи информации на регистр 18, а при выдаче информации во внешнее устройство открываются соответствующие цепи (параллельные или последовательные) приема ин формации от регистра 18.Выдача или прием слова от внешнего устройства заканчивается установкой в «единичное состояние триггера 17 готовности подканала и переходом подканала 2 в состояние ожидания связи с регистром 11 обмена. Мультиплексор 1, анализируя с помощью блока 8 готовности подканалов 2, выбирает старший из них и обеспечивает обмен словом информации через регистр 11 с процессором обмена. В процессе работы устройства блок 4 имитации вырабатывает и выдает в соединенный с ним подканал 2 массив слов, состоящий из двух типов слов заданной структуры: первое «шахматное слово и второе «шахматное слово. Работу всех блоков 4 с целью выработки «щахматных слов, контроля их и организации обмена в соответствии с технологией обмена, принятой в соответствующем внешнем устройстве, организует узел 21. Выработка «шахматных слов происходит следующим образом. По сигналу из узла 21 в счетчик 22 устанавливается код, соответствующий числу разрядов формируемого слова, затем триггер 25 пуска устанавливается в состояние «1, и тактовые импульсы из узла 21 через элемент И 26 поступают на счетный вход счетчика 22 сдвигов счетный вход триггера 24, вход дещифратора 23 и вход сдвига регистра 18 обмена. Триггер 24, переключаясь по счетному входу, подает попеременно высокий или. низкий уровень на D-вход первого триггера сдвигового регистра 18, вследствие чего в разряды регистра 18 последовательно записываются «1 и «О и формируется слово «шахматноййструктуры . При отсчете заданного числа разрядов с выхода дешифратора 23 посту-i пает сигнал на установ «О триггера 24 и триггера 25 и процесс формирования «шахматного кода прекращается. После формирования слова на регистре 18 производится его контроль узлом 27 на соответствие заданному и через коммутатор 14 под воздействием сигнала с узла 21 выдаётся в подканал 2. С регистра 20 служебных сигналов при выдаче (приеме) слова информации выдаются (принимаются) служебные сигналы в соответствии с заданной временной диаграммой конкретного внешнего устройства, которое имитирует блок 4. Шахматное слово второго типа отличается от первого тем, что в нем «1 размещаются на месте «О и наоборот. При выработке «шахматного слова второго типа с узла 21 предварительно устанавливается в «1 триггер 24 и далее работа схемы происходит как при выработке первого. После выработки второго «шахматного кода, узел 21 обеспечивает выдачу (прием) первого «щахматного слова и так далее. Узел 21 может быть выполнен как микропрограммное устройство, тогда управление и синхронизация обменом в соответствии с конкретной временной диаграммой внешнего устройства обеспечивается работой микропрограммы, заданной в памяти микрокоманд узла 21. Изменяя микропрограмму можно получить соответствующую диаграмму обмена, имитирующую работу внешнего устройства. Блок 5 имитации внешнего устройства. выдающего или принимающего массивы слов произвольной структуры в соответствии с технологией обмена, принятой при работе соответствующего внещнего устройстза, ,работает следующим образом. С узла 36 производится пуск узла 29 и запись информационного слова в регистр 28 обмена имитатора и начального адреса ячейки памяти 33 в регистр 34. Затем под управлением узла 29 производится запись слова в ячейку 33 памяти и добавление «1 к коду адреса в регистр 34. После этого с помощью узла 36 производится запись второго слова в регистр 28 и далее под управлением узла 29 запись слова в следующую ячейку памяти 33. Далее процесс повторяется вплоть до записи необходимого числа слов в память 33. Для выдачи информации в подканал на счетчик 35 числа слов устанавливается с зла 36 код количества слов, которое надо выдать. По сигналу с узла 29 на регистр 34 устанавливается начальный адрес массива и производится считывание из памяти 33 и запись на регистр 28 первого информационного слова. Затем слово контролируется узлом 32 на соответствие контрольным кодом и через коммутатор 31 выдается в подканал. С регистра 30 служебных сигналов под управлением узла 29 производится выдача (прием) управляющих сигналов в соответствии с заданной временной диаграммой обмена. После выдачи первого слова добавляется «1 в счетчик 35 и регистр 34. Затем производится считывание из памяти 33, запись в регистр 28 и выдача в подканал следующего слова и т. д. до тех пор, пока счетчик 35 числа слов не отсчитает заданное число слов. После отсчета заданного числа слов по сигналу из узла 29 на регистр 34 устанавливается снова начальный адрес, считывается из памяти 33 первое слозо и выдача массива в подканал повгоряется. В режиме приема информации из подканала с узла 36 задается начальный адрес ячейки памяти 33, который вводится в регистр 34 и количество слов, которое надо принять, на счетчик 35 числа слов. Слова принимаются из подканала через коммутатор 31 в регистр 28, где контролируются с помощью узла 32 и далее записывают я в память 33 по адресу, зафиксированному на регистре 34. Прием, контроль и запоминание информационных слов производится под управ Узла 20. Для проверки правильности прохождения информации принятый блоком 5 массив по сигналам с узла 36 пословно считывается из памяти 33 на регистр 28 обмена и сравнивается с заданными кодами визуально или с помощью соответствующей схемы сравнения и индикатора ошибок (на чертеже не показаны). Блок 6 представляет собой упрощенный имитатор, служащий для проверки интерфейса, в соответствии с которым подключаются подканалы к мультиплексору 1, и проверки работы мультиплексора 1. Блок 6 может подключаться к мультиплексору 1 вместо и по технологии подканала 2. Блок 6 работает следующим образом, При наличии «1 в соответствующем разряде вновь поступившего процессора обмена содержимого регистра 13 готовности программы на вход элемента И. 40 поступает разрешающий потенциал. Сигнал запуска подканалов, подаваемый из блока 7 через элемент И 40 наступает на «единичный вход триггера 37 готовности программы и устанавливает его в стостояние «1. Сигнал с выхода триггера 37 подается на соответствующий вход блока 8 приоритез означая готовность данного контрольного подканала к обмену. Б случае выбора блоком 8 данного подканала по его сигналу производится установ в «.1 триггера 38 работы контрольного подканала, с выхода которого подается сигнал на соответствующий вход коммутатора, для выдачи номера подканала и информации. После цикла обмена-выдачи .номера контрольного подканала и информации («нулевое слово с контрольными разрядами) из блока 7 возможно поступление импульсного сигнала об окончании обмена, который производит через элемент И 39 установ «О триггера 37 готовности программы, тем самым исключая контрольный подканал из обмена и сигнала на установ «О триггера 38 работы контрольного подканала. Если сигнала об окончании обмена нет, то триггер 37 остается в состоянии «1, вновь подавая сигнал на блок 8. При выборе последним данного контрольного подканала происходит передача номера данного подканала и «нулевого слова информации с контрольными разрядами. Таким образом, предлагаемое устройство, позволяет повысить надежность устройства и достоверность передаваемой информации посредством осуществления большей глубины контроля на протяжении всего тракта приема (выдачи) информации ,вне зависимости от состояния внешних устройств (работа-пауза). Формула изобретения 1. Устройство для сопряжения по авт. св. № 736086, отличающееся тем, что, с целью повышения надежности устройства, в него введена группа блоков имитации внешнего устройства и блок имитации интерфейса, причем информационные и управляющие входы и выходы каждого блока имитации внешнего устройства соедин-ены соответственно со вторыми информационными и управляющими выходами и входами соответствующего подканала абонента, первый вход блока имитации интерфейса подключен ко второму выходу блока синхронизации, первый выход и второй вход- к соответствующему входу и выходу блока приоритета, третий вход - к соответствующему выходу регистра готовности программы, второй выход и четвертый вход - к соответствующим входу и выходу группы информационных входов и выходов коммутатора информации, а третий выход - к соответствующему входу группы адресных входов коммутатора информации. 2. Устройство по п. 1, отличающееся тем, что блок имитации интерфейса содержит триггер готовности программы, выход которого соединен с первым и вторым выходами блока, а первый и второй входы - соответственно с выходами первого и второго элементов И, и триггер работы контрольного подканала, первый вход которого соединен со вторым входом блока, второй вход - с первыми входами блока и первого и второго элементов И, а выход с третьим выходом блока и вторым входом первого элемента И, второй вход второго элемента И является четвертым входом блока. 3. Устройство по п. 1, отличающееся тем, что блок имитации внешнего устройства содержит коммутатор типа передачи, информационные вход и выход которого являются соответственно информационными входом и выходом блока, регистр обмена, соединенный двухсторонними связями с коммутатором типа передачи-и узлом свертки, регистр служебных сигналов, первые вход и выход которого являются соответственно управляющими входом и выходом блока, а вторые вход и цыход соединены соответственно с первыми выходом и входом узла синхронизации, второй, третий и четвертый выходы которого подключены соответственно к управляющему входу коммутатора типа передач, входу узла контроля и первому входу регистра обмена. вторым входом соединенного с выходом триггера выработки шахматных кодов, а третьим входом - с выходом элемента И, входоти счетчика сдвигов, первым входом дешифратора «уля и счетным входом триггера выработки шахматных кодов, первый вход которого соединен с выходом дешифратора нуля и первым входом триггера пуска, а второй вход - с пятым выходом узла синхронизации, шестой и седьмой выходы которого подключены соответственно ко второму входу триггера пуска, соединенного выходом с первым входом элемента И, и второму входу элемента И, второй вход дешифратора нуля соединен с выходом счетчика сдвигов, группа входов которого синхрони . 4. Устройство по п. 1, отличающееся тем, что блок имитации внешнего устройства содержит коммутатор типа передачи, информационные вход и выход которого являются соответственно информационными входом и выходом блока, регистр обмена, соединений двухсторонними связями с коммутатором типа передачи и узлом свертки, регистр служебных сигналов, первые вход и выход которого являются соответственно управляющими входом и выходом блока, а вторые вход и выход соединены соответственно с первыми выходом и управляющим входом узла синхронизации, второй, третий и четвертый выходы которого соединены соответственно с управляющим входом коммутатора типа передачи, входом узла свертки и первым входом регистра обмена, выход и второй вход которого подключены соответственно к информационным входу и выходу памяти, адрьсный вход которой соединен с выходом регистра адреса, входом подключенного к пятому выходу узла синхронизации, шестой выход и первый установочный вход которого соединены соответственно с первым входом и выходом счетчика числа слов, подключенного вторым входом к первому выходу узла ввода, второй выход которого соединен с третьим входом регистра обмена, а третий выход - со вторым установочным входом узла синхронизации. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство ССР № 736086, кл. G 06 F 3/04, 03.01.78.

Авторы

Даты

1981-03-15—Публикация

1978-11-02—Подача