(54) УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1980 |

|

SU947849A1 |

| Устройство для сопряжения процессоров обмена с внешними устройствами | 1984 |

|

SU1257650A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Устройство для сопряжения | 1984 |

|

SU1166126A2 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения | 1978 |

|

SU736086A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для сопряжения | 1979 |

|

SU840868A2 |

I

Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных системах с общими внешними устройствами.

Известны устройства для обмена информацией, содержаш,ие коммутатор, подключенный к внешним устройствам и к блоку оперативной памяти, соединенному со счетчиками адресов записи и считывания и с группой процессоров, блок памяти подканалов, соединенный со счетчиками адресов записи и считывания и с блоком анализа состояний последовательно соединенные регистр состояния блока оперативной памяти, подключенный к блоку анализа состояний, и блок приоритетов, подключенный к группе процессоров и к блоку памяти подканалов 1.

Недостаток этих устройств состоит в низкой пропускной способности ввиду отсутствия возможности совмеш,ения обменов с программным управлением приемом и выдачей информации сразу для всех или нескольких подключенных внешних устройств.

Наиболее близким к предлагаемому по сущности технического решения является устройство для сопряжений, содержащее подканалы абонентов и блок коммутации

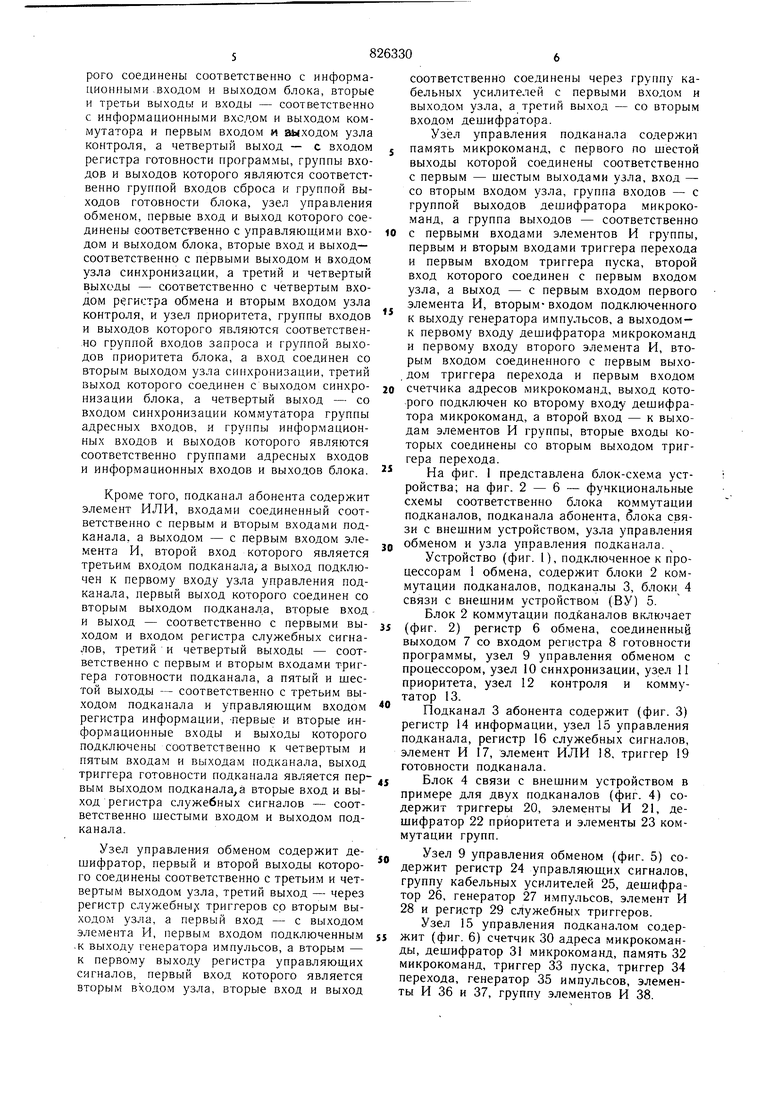

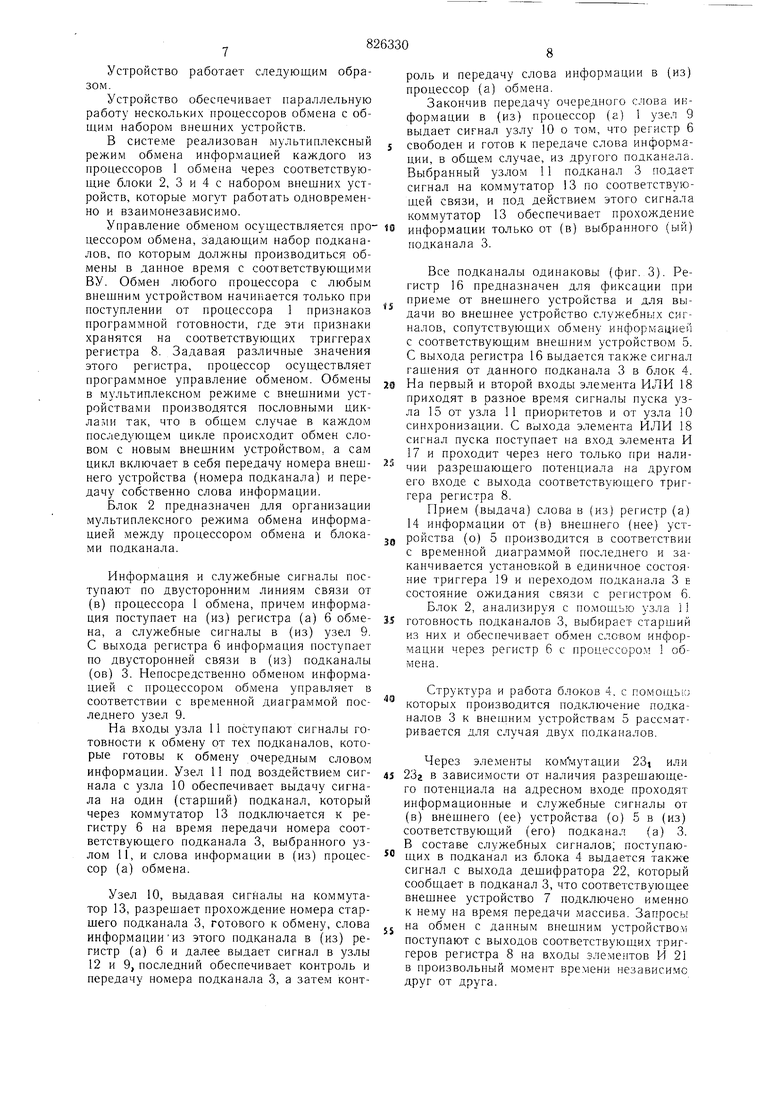

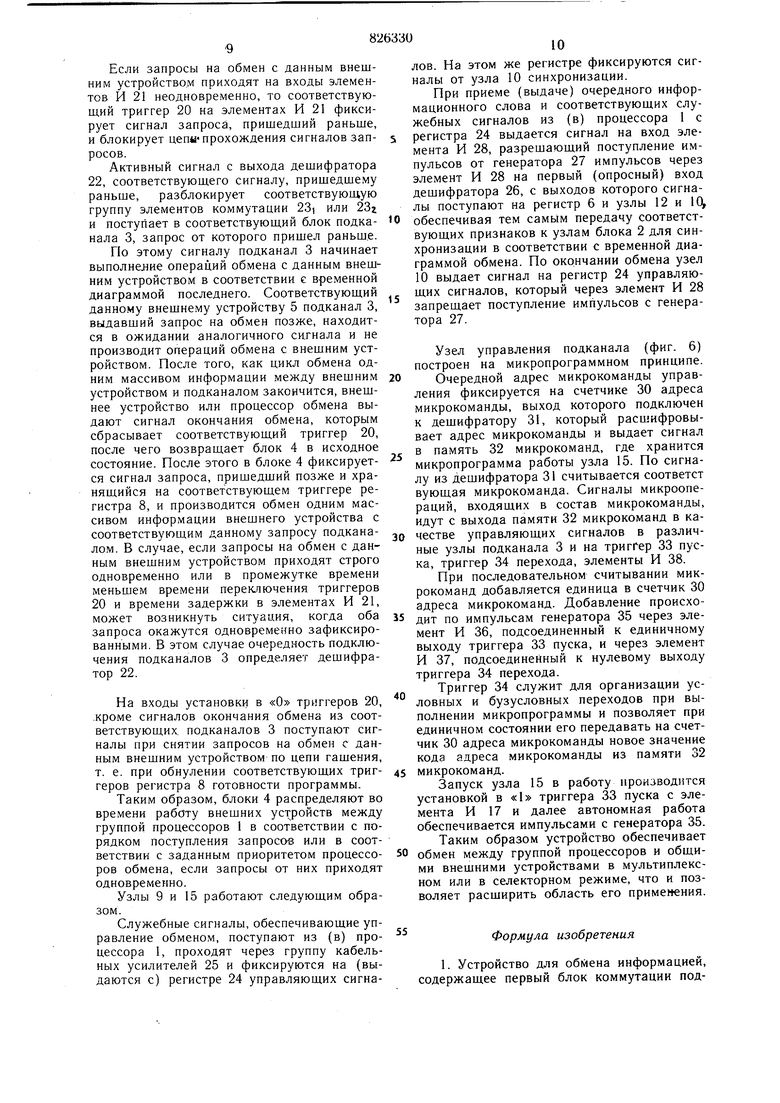

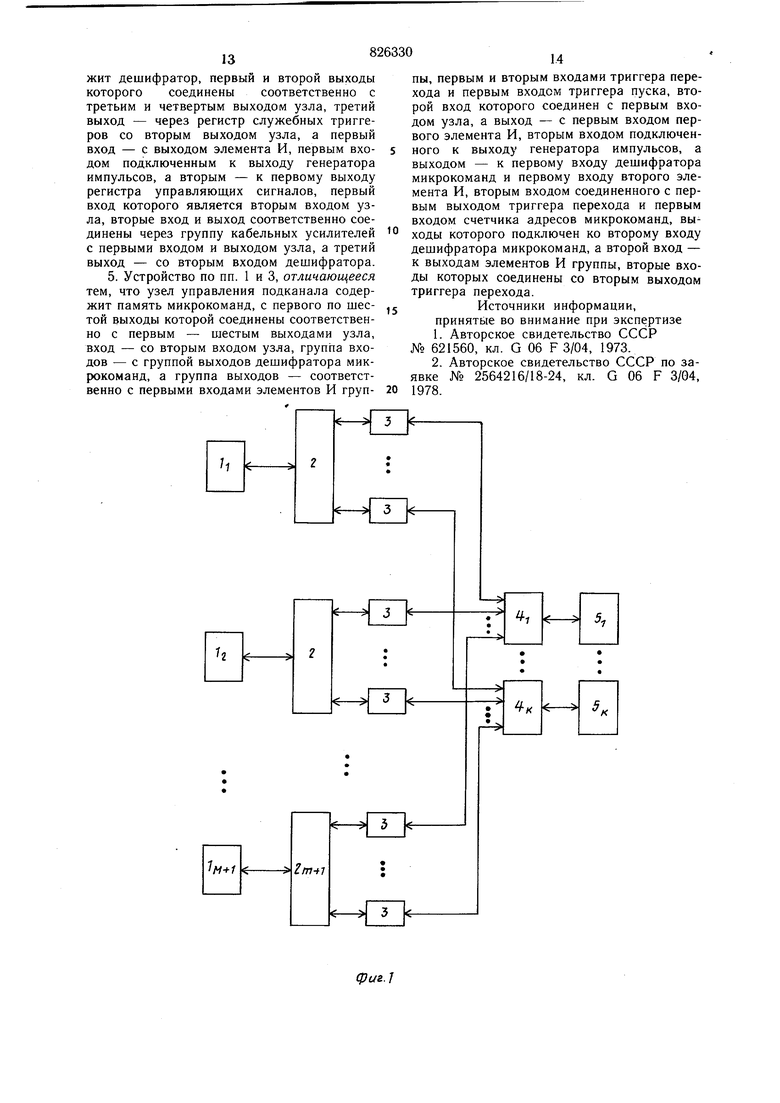

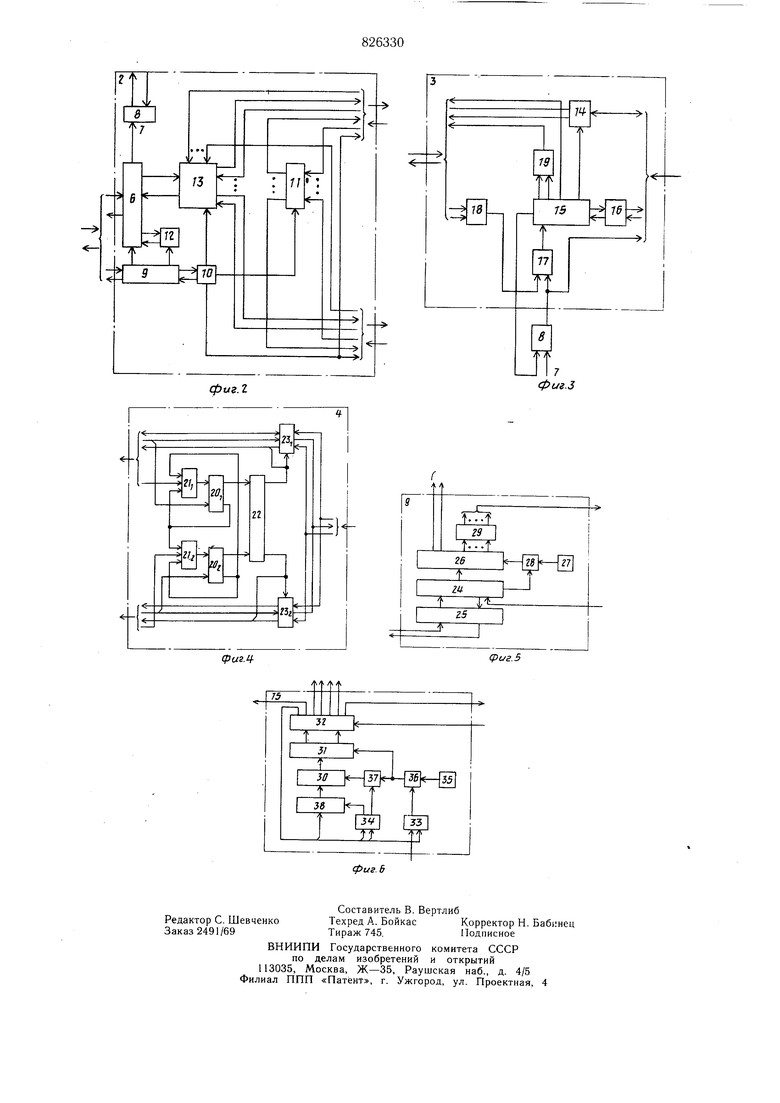

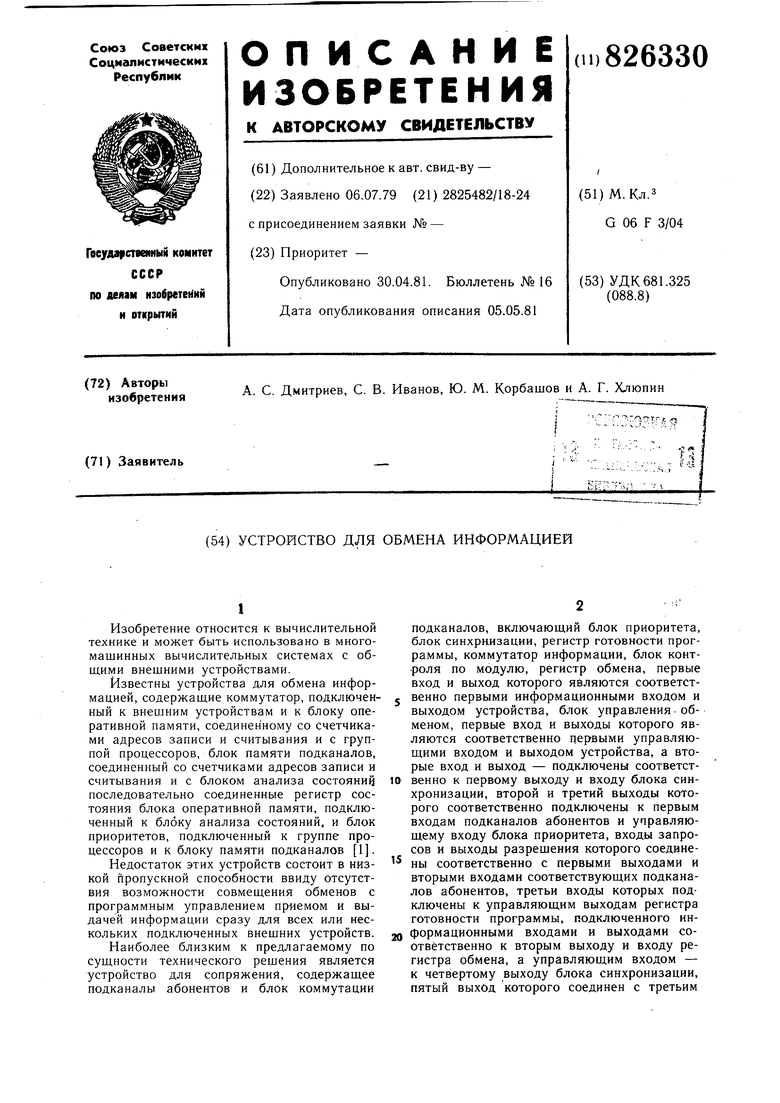

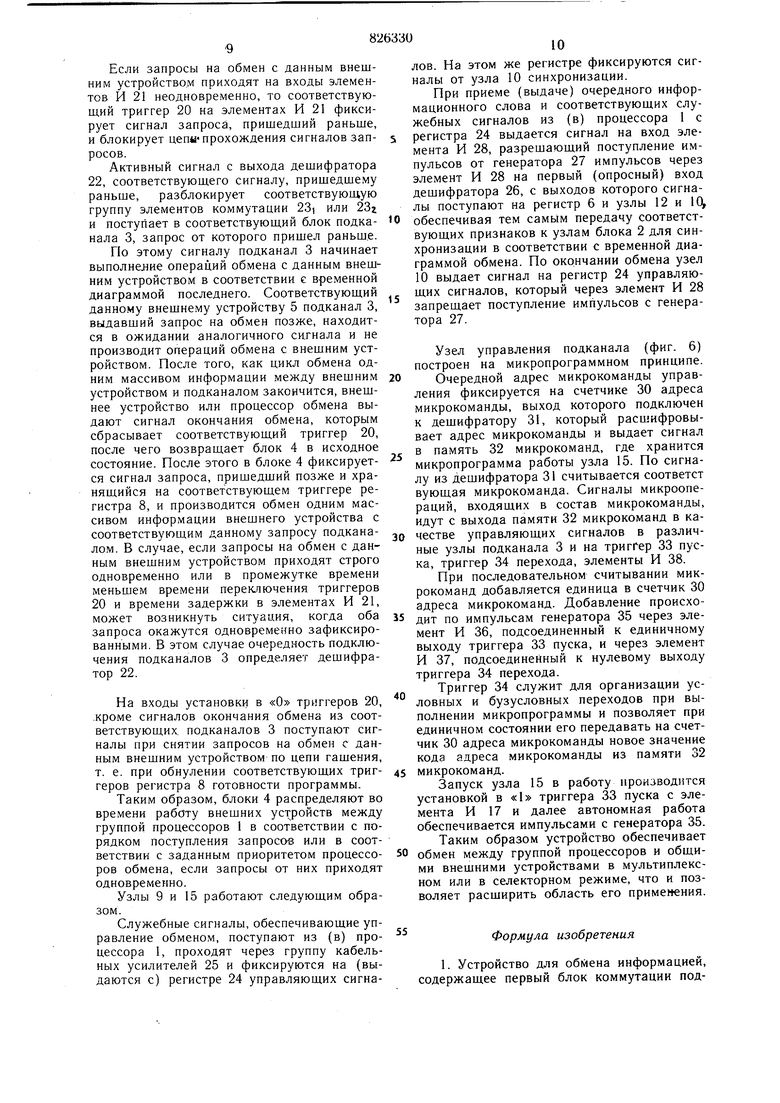

подканалов, включающий блок приоритета, блок синхрнизации, регистр готовности программы, коммутатор информации, блок контроля по модулю, регистр обмена, первые вход и выход которого являются соответственно первыми информационными входом и выходом устройства, блок управления. обменом, первые вход и выходы которого являются соответственно первыми управляющими входом и выходом устройства, а вторые вход и выход - подключены соответственно к первому выходу и входу блока синхронизации, второй и третий выходы которого соответственно подключены к первым входам подканалов абонентов и управляющему входу блока приоритета, входы запросов и выходы разрещения которого соединены соответственно с первыми выходами и вторыми входами соответствующих подканалов абонентов, третьи входы которых подключены к управляющим выходам регистра готовности программы, подключенного информационными входами и выходами соответственно к вторым выходу и входу регистра обмена, а управляющим входом - к четвертому выходу блока синхронизации, пятый выход которого соединен с третьим входом блока контроля по модулю, подключенного первым входом и выходом соответственно к третьим выходу и входу регистра обмена, а вторым входом - к третьему выходу блока управления, четвертый выход которого подключен к пятому входу регистра обмена, четвертые выход и вход которого соединены соответственно с информационными входом и выходом коммутатора информации, управляющий вход которого подключен к шестому выходу блока синхронизации, а выходы группы информационных входов и выходов и входы группы адресных входов соединены соответственно с четвертыми входами, вторыми и третьими выходами соответствующих подканалов абонентов, информационные входы и выходы и управляющие входы и выходы которых являются соответственно вторыми информационными входами и выходами и вторыми управляющими входами и выходами устройства. Кроме того, каждый подканал абонента содержит узел управления, регистр служебных сигналов, первые вход и выход которого, соединены соответственно с первыми выходом и входом узла управления, а вторые выход и вход являются соответственно управляющими выходом и входом подканала, коммутатор типа передачи, соединенный первыми входом и выходом соответственно с первым выходом и входом регистра обмена подканала, вторые вход и выход которого являются соответственно четвертым входом и вторым выходом подканала, элемент И, первый вход которого является третьим входом подканала, а выход соединен со вторым входом узла управления, третий и четвертый выходы которого соединены соответственно с третьими входами коммутатора типа передачи и регистра обмена подканала, а пятый выход - с третьим выходом подканала, триггер готовности, соединенный входом и выходом соответственно с шестым выходом узла управления и с первым выходом подканала, информационные вход и выход которого являются соответственно вторыми входом и выходом .коммутатора типа передачи, и элемент ИЛИ, входы которого являются соответственно первым и вторым входами подканала, а выход соединен со вторым входом элемента И 2. Недостаток этого устройства состоит в ограниченной области применения, обусловленной невозможностью обмена нескольких процессоров обмена с общими внешними устройствами. Цель изобретения - расширение области применения устройства. Поставленная цель достигается тем, что в устройство, содержащее первый блок коммутации подканалов, информационные и управляющие входы и выходы которого являются соответственно первыми информационными и управляющими входами и выходами устройства, и первую группу подканалов абонентов, причем первый вход i-ro (1 1ТЮ подканала абонентов первой группы соединен с выходом синхронизации блока коммутации подканалов, а второй,третий и четвертый входы и первый, второй, третий и четвертый выходы - соответственно с i-тыми выходами группы выходов приоритета, группы выходов готовности и группы информационных выходов и i-тыми входами группы запросных входов, группы адресных входов, группы входов сброса и группы информационных входов блока коммутации подканалов, введены М блоков коммутации подканалов, М групп подканалов абонентов и К блоков связи с внешним устройством, причем первый вход i-rp подканала абонента j-ой группы (J 2,М + 1) соединен с выходом синхронизации j-ro блока коммутации подканалов, а второй, третий и четвертый входы и первый, второй, третий и четвертый выходы - соответственно .с i-тыми выходами группы выходов приоритета, группы выходов готовности и группы информационных выходов с i-тыми входами группы запросных входов, группы адресных входов, группы входов сброса и группы информационных входов j-ro блока коммутации подканалов, а каждый блок связи с внешним устройством содержит М + 1 групп элементов коммутации, дещифратор приоритета, М + 1 триггеров и М + 1 элементов И, причем адресные входы элементов коммутации т-той группы (т 1.М + 1) подключены к ш-тому выходу дешифратора приоритета, т-тый вход которого соединен с единичным выходом ш-того триггера, подключенного единичным входом к выходу т-того элемента И, а нулевым выходом - к гп-тым входам блокировки элеммнтов И, вход разрешения т-го элемента И i-ro блока связи с внешним устройством соединен с третьим входом i-ro подканала абонента т-ой группы, пятые и шестые вход и выход которого подключены соответственно к первым и вторым информационным входам и выходам элементов коммутации ш-ой группы i-ro блока связи с внешним устройством, вторые вход и выход которых подключены соответственно к нулевому входу ш-го триггера и ш-му выходу дешифратора приоритета того же блока связи с внешним устройством, а третьи и четвертые информационные входы и выходы - соответственно с третьими и четвертыми информационными входами и выходами элементов коммутации других групп того же блока связи с внешним устройством и группой информационных и управляющих входов и выходов устройства информационные и управляющие выходы j-ro блока коммутации являются соответственно j-ыми информационными и управляющими входом и выходом устройства. Блок коммутации подканалов соедржит регистр обмена, первые вход и выход которого соединены соответственно с информационными .входом и выходом блока, вторые и третьи выходы и входы - соответственно с информационными входом и выходом коммутатора и первым входом я выходом узла контроля, а четвертый выход - с входом регистра готовности программы, группы входов и выходов которого являются соответственно группой входов сброса и группой выходов готовности блока, узел управления обменом, первые вход и выход которого соединены соответственно с управляющими входом и выходом блока, вторые вход и выходсоответственно с первыми выходом и входом узла синхронизации, а третий и четвертый выходы - соответственно с четвертым входом регистра обмена и вторым входом узла контроля, и узел приоритета, группы входов и выходов которого являются соответствен.но группой входов запроса и группой выходов приоритета блока, а вход соединен со вторым выходом узла синхронизации, третий выход которого соединен с выходом синхронизации блока, а четвертый выход - со входом синхронизации коммутатора группы адресных входов, и группы информационных входов и выходов которого являются соответственно группами адресных входов и информационных входов и выходов блока. Кроме того, подканал абонента содержит элемент ИЛИ, входами соединенный соответственно с первым и вторым входами подканала, а выходом - с первым входом элемента И, второй вход которого является третьим входом подканала, а выход подключен к первому входу узла управления подканала, первый выход которого соединен со вторым выходом подканала, вторые вход и выход - соответственно с первыми выходом и входом регистра служебных сигналов, третий и четвертый выходы - соответственно с первым и вторым входами триггера готовности подканала, а пятый и шестой выходы - соответственно с третьим выходом подканала и управляющим входом регистра информации, -первые и вторые информационные входы и выходы которого подключены Соответственно к четвертым и пятым входам и выходам подканала, выход триггера готовности подкапала является первым выходом подканалами вторые вход и выход регистра служебных сигналов - соответственно щестыми входом и выходом подканала. Узел управления обменом содержит дешифратор, первый и второй выходы которого соединены соответственно с третьим и четвертым выходом узла, третий выход - через регистр служебны.х триггеров со вторым выходом узла, а первый вход - с выходом элемента И, первым входом подключенным .к выходу генератора импульсов, а вторым - к первому выходу регистра управляющих сигналов, первый вход которого является вторым входом узла, вторые вход и выход соответственно соединены через группу кабельных усилителей с первыми входом и выходом узла, а третий выход - со вторым входом дешифратора. Узел управления подканала содержит память микрокоманд, с первого по шестой выходы которой соединены соответственно с первым - шестым выходами узла, вход - со вторым входом узла, группа входов - с группой выходов дешифратора микрокоманд, а группа выходов - соответственно с первыми входами элементов И группы, первым и вторым входами триггера перехода и первым входом триггера пуска, второй вход которого соединен с первым входом узла, а выход - с первым входом первого элемента И, вторым-входом подключенного к выходу генератора импульсов, а выходом- к первому входу дешифратора микрокоманд и первому входу второго элемента И, вторым входом соединенного с первым выходом триггера перехода и первым входом счетчика адресов микрокоманд, выход которого подключен ко второму входу дешифратора микрокоманд, а второй вход - к выходам элементов И группы, вторые входы которых соединены со вторым выходом триггера перехода. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - 6 - функциональные схемы соответственно блока коммутации подканалов, подканала абонента, блока связи с внешним устройством, узла управления обменом и узла управления подканала. Устройство (фиг. I), подключенное к процессорам 1 обмена, содержит блоки 2 коммутации подканалов, подканалы 3, блоки 4 связи с внешним устройством (ВУ) 5. Блок 2 коммутации подканалов включает (фиг. 2) регистр 6 обмена, соединенный выходом 7 со входом регистра 8 готовности программы, узел 9 управления обменом с процессором, узел 10 синхронизации, узел 11 приоритета, узел 12 контроля и коммутатор 13. Подканал 3 абонента содержит (фиг. 3) регистр 14 информации, узел 15 управления подканала, регистр 16 служебных сигналов, элемент И 17, элемент ИЛИ 18, триггер 19 готовности подканала. Блок 4 связи с внешним устройством в примере для двух подканалов (фиг. 4) содержит триггеры 20, элементы И 21, дешифратор 22 приоритета и элементы 23 коммутации групп. Узел 9 управления обменом (фиг. 5) содержит регистр 24 управляющих сигналов, группу кабельных усилителей 25, дешифратор 26, генератор 27 импульсов, элемент И 28 и регистр 29 служебных триггеров. Узел 15 управления подканалом содержит (фиг. 6) счетчик 30 адреса микрокоманды, дешифратор 31 микрокоманд, память 32 микрокоманд, триггер 33 пуска, триггер 34 перехода, генератор 35 импульсов, элементы И 36 и 37, группу элементов И 38. Устройство работает следующим образом. Устройство обесаечивает параллельную работу нескольких процессоров обмена с общим набором внешних устройств. В системе реализован мультиплексный режим обмена информацией каждого из процессоров 1 обмена через соответствующие блоки 2, 3 и 4 с набором внещних устройств, которые .могут работать одновременно и взаимонезависимо. Управление обменом осуществляется процессором обмена, задающим набор подканалов, по которым должны производиться обмены в данное время с соответствующими ВУ. Обмен любого процессора с любым внешним устройством начи1;ается только при поступлении от процессора 1 признаков программной готовности, где эти признаки хранятся на соответствующих триггерах регистра 8. Задавая различные значения этого регистра, процессор осуществляет программное управление обменом. Обмены в мультиплексном режиме с внешними уст ройствами производятся пословными циклами так, что в общем случае в каждом последующем цикле происходит обмен словом с новым внещним устройством, а сам цикл включает в себя передачу номера внешнего устройства (номера подканала) и передачу собственно слова информации. Блок 2 предназначен для организации мультиплексного режима обмена информацией между процессором обмена и блоками подканала. Информация и служебные сигналы поступают по двусторонним линиям связи от (в) процессора 1 обмена, причем информация поступает на (из) регистра (а) 6 обмена, а служебные сигналы в (из) узел 9. С выхода регистра 6 информация поступает по двусторонней связи в (из) подканалы (ов) 3. Непосредственно обменом инфор.мацией с процессором обмена управляет в соответствии с временной диаграммой последнего узел 9. На входы узла 11 поступают сигналы готовности к обмену от тех подканалов, которые готовы к обмену очередным словом информации. Узел 11 под воздействием сигнала с узла 10 обеспечивает выдачу сигнала на один (старший) подканал, который через коммутатор 13 подключается к регистру 6 на время передачи номера соответствующего подканала 3, выбранного узлом 11, и слова информации в (из) процессор (а) обмена. Узел 10, выдавая сигналы на коммутатор 13, разрешает прохождение номера старщего подканала 3, готового к обмену, слова информациииз этого подканала в (из) регистр (а) 6 и далее выдает сигнал в узлы 12 и 9, последний обеспечивает контроль и передачу номера подканала 3, а затем контроль и передачу слова информации в (из) процессор (а) обмена. Закончив передачу очередного слова информации в (из) процессор (а) 1 узел 9 выдает сигнал узлу 0 о том, что регистр 6 свободен и готов к передаче слова информации, Б общем случае, из другого подканала. Выбранный узлом 11 подканал 3 подает сигнал на коммутатор 13 по соответствующей связи, и под действием этого сигнала коммутатор 13 обеспечивает прохождение информации только от (в) выбранного (ый) подканала 3. Все подканалы одинаковы (фиг. 3). Регистр 16 предназначен для фиксации при приеме от внешнего устройства и для выдачи во внешнее устройство служебных сигналов, сопутствующих обмену информацией с соответствующим внешним устройством 5. С выхода регистра 16 выдается также сигнал гашения от данного подканала 3 в блок 4. На первый и второй входы элемента ИЛИ 18 приходят в разное время сигналы пуска узла 15 от узла 11 приоритетов и от узла 10 синхронизации. С выхода элемента ИЛИ 18 сигнал пуска поступает на вход элемента И 17 и проходит через него только при наличии разрешающего потенциала на другом его входе с выхода соответствующего триггера регистра 8. Прие.м (выдача) слова в (из) регистр (а) 14 информации от (в) внешнего (нее) устройства (о) 5 производится в соответствии с временной диаграммой последнего и заканчивается установ(ой в единичное состояние триггера 19 и переходом подканала 3 Е состояние ожидания связи с регистром 6. Блок 2, анализируя с помощью узла 11 готовность подканалов 3, выбирает старший из них и обеспечивает об.мен словом информации через регистр б с процессором I обмена. Структура и работа блоков 4, с помощьк; которых производится подключение подканалов 3 к внешним устройствам 5 расс.матривается для случая двух подканалов. Через элементы коммутации 23t или 23г в зависимости от наличия разрешающего потенциала на адресном входе проходят информационные и служебные сигналы от (в) внещнего (ее) устройства (о) 5 в (из) соответствующий (его) подканал (а) 3. В составе служебных сигналов; поступающих в подканал из блока 4 выдается также сигнал с выхода дешифратора 22, который сообщает в подканал 3, что соответствующее внешнее устройство 7 подключено именно к нему на время передачи массива. Запросы на обмен с данным внешним устройством поступают с выходов соответствующих триггеров регистра 8 на входы элементов И 21 в произвольный момент времени независимо друг от друга. Если запросы на обмен с данным внешним устройством приходят на входы элементов И 21 неодновременно, то соответствующий триггер 20 на элементах И 21 фиксирует сигнал запроса, пришедший раньше, и блокирует цепы-прохождения сигналов запросов. Активный сигнал с выхода дешифратора 22, соответствуюш,его сигналу, пришедшему раньше, разблокирует соответствующую группу элементов коммутации 23) или 23 и поступает в соответствующий блок подканала 3, запрос от которого пришел раньше. По этому сигналу подканал 3 начинает выполнение операций обмена с данным внешним устройством в соответствии е временной диаграммой последнего. Соответствующий данному внещнему устройству 5 подканал 3, выдавший запрос на обмен позже, находится в ожидании аналогичного снгнала и не производит операций обмена с внешним устройством. После того, как цикл обмена одним массивом информации между внешним устройством и подканалом закончится, внешнее устройство или процессор обмена выдают сигнал окончания обмена, которым сбрасывает соответствующий триггер 20, после чего возвращает блок 4 в исходное состояние. После этого в блоке 4 фиксируется сигнал запроса, пришедший позже и хранящийся на соответствующем триггере регистра 8, и производится обмен одним массивом информации внешнего устройства с соответствующим данному запросу подканалом. В случае, если запросы на обмен с данным внешним устройством приходят строго одновременно или в промежутке времени меньшем времени переключения триггеров 20 и времени задержки в элементах И 21, может возникнуть ситуация, когда оба запроса окажутся одновременно зафиксированными. В этом случае очередность подключения подканалов 3 определяет дешифратор 22. На входы установки в «О триггеров 20, .кроме сигналов окончания обмена из соответствующих, подканалов 3 поступают сигналы при снятии запросов на обмен с данным внешним устройством по цепи гашения, т. е. при обнулении соответствующих триггеров регистра 8 готовности программы. Таким образом, блоки 4 распределяют во времени работу внешних устройств между группой процессоров 1 в соответствии с порядком поступления запросов или в соответствии с заданным приоритетом процессоров обмена, если запросы от них приходят одновременно. Узлы 9 и 15 работают следующим образом. Служебные сигналы, обеспечивающие управление обменом, поступают из (в) процессора 1, проходят через группу кабельных усилителей 25 и фиксируются на (выдаются с) регистре 24 управляющих сигнаЛОВ. На этом же регистре фиксируются сигналы от узла 10 синхронизации. При приеме (выдаче) очередного информационного слова и соответствующих служебных сигналов из (в) процессора 1 с регистра 24 выдается сигнал на вход элемента И 28, разрещающий поступление импульсов от генератора 27 импульсов через элемент И 28 на первый (опросный) вход дещифратора 26, с выходов которого сигналы поступают на регистр 6 и узлы 12 и 0, обеспечивая тем самым передачу соответствующих признаков к узлам блока 2 для синхронизации в соответствии с временной диаграммой обмена. По окончании обмена узел 10 выдает сигнал на регистр 24 управляющих сигналов, который через элемент И 28 запрещает поступление импульсов с генератора 27. Узел управления подканала (фиг. 6) построен на микропрограммном принципе. Очередной адрес микрокоманды управления фиксируется на счетчике 30 адреса микрокоманды, выход которого подключен к дешифратору 31, который расшифровывает адрес микрокоманды и выдает сигнал в память 32 микрокоманд, где хранится микропрограмма работы узла 15. По сигналу из дешифратора 31 считывается соответст вующая микрокоманда. Сигналы микроопераций, входящих в состав микрокоманды, идут с выхода памяти 32 микрокоманд в качестве управляющих сигналов в различные узлы подканала 3 и на триггер 33 пуска, триггер 34 перехода, элементы И 38. При последовательном считывании микрокоманд добавляется единица в счетчик 30 адреса микрокоманд. Добавление происходит по импульсам генератора 35 через элемент И 36, подсоединенный к единичному выходу триггера 33 пуска, и через элемент И 37, подсоединенный к нулевому выходу триггера 34 перехода. Триггер 34 служит для организации условных и бузусловных переходов при выполнении микропрограммы и позволяет при единичном состоянии его передавать на счетчик 30 адреса микрокоманды новое значение кода адреса микрокоманды из памяти 32 микрокоманд. Запуск узла 15 в работу производится установкой в «1 триггера 33 пуска с элемента И 17 и далее автономная работа обеспечивается импульсами с генератора 35. Таким образом устройство обеспечивает обмен между группой процессоров и общиМИ внешними устройствами в мультиплексном или в селекторном режиме, что и позволяет расширить область его применения. Формула изобретения 1. Устройство для обмена информацией, содержащее первый блок коммутации подщие

кана.юв, t ni) и iniiв г

DOT

входы и lil J. г

и и

hn

ветствеино п pt i устIуправляют 11 абО jt

ройства, им 1 г 1 1)1 1,К) нентов, причем первый вход 1-го i,i подканала абопсмггов первой rpyi соединен с выходом с;1пхронпзацнн блока коммутации подканалов, а второй, третий к че вертый входы и первый, второй, третий и четвертый выходы - СООТВетеТВеПНО с

выходами группы выходов приоритета, группы выходов готовности и группы инфорк;:ционных ввгходов и i-TBiMH входами группы запросных входов, rpynribi адресных зходов, группы входов сброса и группы информационнв1х входов блока коммутации по;; каналов, отличающееся тем, что, с п,ел::(: расширения области применения устройств:, в него введены М блоков коммутации подканалов, Л групп подканалов абоиептоо и К блоков связи с внешним устройством, причем первый ),капала абоиел та j-ой группы iJ 2,М +1) соединен с выходом синхронизации j-ro блока коммутации подканалов, а вторОЙ, третий и четвер тый входв и первый, второй, третий и четвертв|й выходы --- соответственно с 1-тв1МИ выходами rpyiniK выходов приоритета, группы выходов готовности и группы информационпых ВВ1ХОДОВ с i-тыми выходами группы занроспв1х входов, группы адресных входов, гругшы входов сброса и группы информационных входов j-ro блока коммутации подканалов, а каждый блок связи с BHenJHHM устройством содержит М - I г)уг:л элементов коммутации, де1аифратор приоритета, М -- 1 григгероБ и М - 1 э,;еме(:тов И поичем .цзесные входы эле 1ентоБ коммутации П1-ТОЙ группы (т КМ + : гп-тому ньгходу einndipaTOpa iii-тый вход хсугорого соединен выхо.том триггепа, подедин и чиым входе N1 к ВЬХОДЛ гп-того элемспт;; И , а пу,певым входом --- -: П1-ТЫМ входам б.покировки элементов ) вход разрен епия пт-го элемепта И i-ro блока связи е внепп)им устройством соед|-;неп с третьим входом i-ro подканала аооп-епта т-ой грунты, пятые и иеетые вход i; выход, которого под.ключснь соответственно к первым и вторым ин(|)орма11,ион1Пз1м входам и выходам элементов коммутации т-ой группы i-ro блока связи с внешним устройством, вторые вход и вв1ход которых подключепв еоответствеппо к нулевому входу т-го тригтера и гп-му выходу дешифратора приоритета того же блока евязи с внешним устройством, а третви и четвертв1е информ ациопцые в,ходь; и выходы - соответствеги-и) с третьими и четвертыми информационпькми входами и выходами элементов коммутации других групп того же блока связи с впеним устройством и гп-ой группой информационнв Х и управляюндих входов и ввпходов устройства, информационные и управляющие выходы j-io б.юка коммум;;ц;1и являются соответстве)Ц;о -сл;и имформни, и уг1рав.7й ОП им{-; ихсдом и В1,хс;ч; х-лгисуйс в а.

2, Устройство по п. L ог/:1- :.:г и1геся тем, что блок коммутацуП-: содержит регистр обмена, первые вход и зыход которого соедииены cooTBc-ic- BCHHo с информацио1 ными входом и ВВ1ХОДОМ б,,1ои:э вторые и третьи выходы и вход,ы - соответетвенно с И1 формационгцэ;ми входом и ьыхо.;,ом коммутатора и перв|)пч входом и ВВ1ХОДОМ узла контроля, а четвертый выходе входом регистра готовности программы, ;-руипы входов и выходов которого являются соответственно гру.пюй входов сброса к |руппой выходов гслч вчссти бло;-д. :-с: yiiDau.-ieni- H odNeuoM, первые вхпл - ;;;:л;.;Л л()то)ого соединены еиответсгвсг-ч,; : i.равл пп1Ц1-1л-1и входом и вь-ходом блоха вто

вылп-; выходом и входом уз,:|а смгтхронизад;- и. а )етий и четвертый -- соответстгенно с четвертые входом регистра

узс;; приоритета, группы входов i-i ;)Ыходов которого являются соответетвенпо группой уходов запроса и гругпюй выходов нриори ч-та блока, а вход соед1-1неп со вторь:м выходом узла синхронизации, третий выход которого соединен е ввпходом синхтюнизации блока, а четвертый выход -- со входом сипхропизации коммутатора гр)ч:|;Ы адрес :ь х входов, и грунпь ипформацихипых входов и выходов которого яв,:1яются соответствен1:() группами адресных входов и кифоомаi HOHHj4X входов и 1Я 1ХОДОВ .

тем, ч1о ,т абонента содержит 5лс.vieiT .И., BX.viafriM гзедин-: . . ие: :;елпс; с лсрвым к В:0 М.;л: л;-,,;.;.. хздчзма и I, чгирс;й 15хс;д кото ;о:о .--с-- вхо/и)м подканала, а выход Г:од, л nci ;OMV вхо..;, узла уп)авлспи : ходкапача, первый выход которого coe/niHCn со вторым выхо.;;,ом подка11а, вторые вход п --соответственно е пcjBh i хь ходом и влодом )егистра слу(.крбиых сигналов, третий и четвертый 1)ыход.ы - соответственно с перв1ям к итооым входам -; триггера готовности подкапа,.1а. а лятый и птестой выходь; - соответс ве1П-п х с третьи.м вв1ходом

подканала i-; у;;раз;1ЯЮ1цим з.:с);ц:М регистра ин1рорма гии, первые и вторь;е информационные входы и Ь,;ходы которого подключены соответс:т ;с ;о к четвер:Ь м и входам и выходаь; лодкапала, зыход тригчх-ра I OTOBности нодкана.ла является ireptiixxi Ь1Ходом |;о.чкана,:;а, а вторые вход и хыход регнстрй служеб1 Ь1Х сигналов -- еоогветс. венно ajecтымп вхо.1,ом и выходом iio;i aKa;ia. жит дешифратор, первый и второй выходы которого соединены соответственно с третьим и четвертым выходом узла, третий выход - через регистр служебных триггеров со вторым выходом узла, а первый вход - с выходом элемента И, первым входом подключенным к выходу генератора импульсов, а вторым - к первому выходу регистра управляющих сигналов, первый вход которого является вторым входом узла, вторые вход и выход соответственно соединены через группу кабельных усилителей с первыми входом и выходом узла, а третий выход - со вторым входом дешифратора. 5. Устройство по пи. 1 и 3, отличающееся тем, что узел управления подканала содержит память микрокоманд, с первого по шестой выходы которой соединены соответственно с первым - шестым выходами узла, вход - со вторым входом узла, группа входов - с группой выходов дешифратора микрокоманд, а группа выходов - соответственно с первыми входами элементов И группы, первым и вторым входами триггера перехода и первым входом триггера пуска, второй вход которого соединен с первым входом узла, а выход - с первым входом первого элемента И, вторым входом подключенного к выходу генератора импульсов, а выходом - к первому входу дешифратора микрокоманд и первому входу второго элемента И, вторым входом соединенного с первым выходом триггера перехода и первым входом счетчика адресов микрокоманд, выходы которого подключен ко второму входу дешифратора микрокоманд, а второй вход - к выходам элементов И группы, вторые входы которых соединены со вторым выходом триггера перехода. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 621560, кл. G 06 F3/04, 1973. 2.Авторское свидетельство СССР по заявке № 2564216/18-24, кл. G 06 F 3/04, 1978.

Авторы

Даты

1981-04-30—Публикация

1979-07-06—Подача