Изобретение относится к вычислительной технике и может быть использовано для сопряжения ЦВМ с внешни.ми устройствами.

По основному авт. св. 736086 известно устройство для сопряжения, содержащее подканалы абонента, блок приоритета, блок синхронизации, ре гистр готовности программы, коммутатор информации, блок контроля по модулю, регистр обмена, первые вход и выход которого являются соответственно первыми информационными входом и выходом устройства, блок управления обменом, первые вход и выход которого являются соответственно первыми управлякицими входом и выходом устройства, а вторые вход и выход подключены соответственно к первым выходу и входу блока синхронизации, второй и третий выходы которого соответственно подключены к первым входам подканалов абонента и управляющему входу блока приоритета, входы запросов и выходы разрешения которого соединены соответственно с первыми выходами и вторыми входами соответствующих подканалов абонента, третьи входы которых подключены к управляющим выходам регистра готовности програмлг, подключенного информационньвв входами и выходгши со-, .ответственно ко вторым выходу и входу регистра обмена, а управляющим входом - к четвертому выходу блока синхронизации, пятый выход которого соединен с третьим входом блока контроля по модулю, подключенного первыми входом и выходом соответст10венно к третьим выходу и входу регистра обмена, а вторым входом - к треть€ у выходу блока управления, четвертый вьосод которого подключен к пятому входу регистра обмена, чет15вертые выход и вход которого соединены соответственно с инфо 1ационными входом и выходом коммутатора информации, управляющий вход которого подключен к шестому выходу блока

20 синхронизации, а выходы и входы группы информационных входов и выходов и входы группы адресных входов соединены соответственно с четвертыми входами, вторыми и третьими выходами соответствующих подканалов абонентов, информационные входы и выходы и управляющие входы и выходы которых являются соответственно вторыми информационными входами и вы30ходами устройства, а каждый подканал абонента содержит узел управле-ния, регистр служебных сигналов, первые вход и выход которого соединены соответственно с первыми выходом и входом узла управления, а вторые выход и вход являются соответственно управляющими выходом и входом подканала, коммутатор типа передачи, первые вход и выход которого соединены соответственно с первым выходом и входом регистра обмена подканала, а вторые вход и выход являются соответственно информационными входом и выходом подкансша, вторле вход и выход регистра обмена являются соответственно четвертым входом и вторым.выходом подканала, элемент И, первый вход которого является третьим входом подканала, а выход соединен со вторым входом узла управления третий и четвертый выходы которого соединены соответственно с третьими входами коммутатора типа передачи и регистра обмена подканала, а пятый выход - с третьим выходом подканала, триггер готовности, соединенный входом и выходом соответственно с шестым выходом узла управления и с первым выходом подканала, и элемент ИЛИ входы которого являются соответственно первым и вторым входами подканала а. выход соединен со втором входом элемента И С1.

Недостаток устройства - низкая достоверность обмена информацией, что обусловлено отсутствием контроля передачи информации между процессоро и периферийными устройствами контроля работоспособности отдельных. узлов и устройства в целом.

Цель изобретения - повышение Достоверности обмена информацией.

Поставленная цель достигается тем что в устройство введены два регистра неисправности, три элемента ИЛИ, блок элементов ИЛИ и триггер неисправности передачи, причем выход триггера неисправности передачи соединен с третьим входом блока управления обменом, а вход - со вторым выходом блока контроля по модулю, третий и четвертый выходы которого соединены соответственно с первым и вторым входами первого регистра неисправности, четвертый вход блока контроля по модулю, соединен с выходом блока элементов ИЛИ, входы которого соединены с четвертыми выходами соответствующих подканалов абонента, первый и второй выхода1 первого регистра неисправности соединены соответственно с пятым входом блока управления обменом, и с шестым входом блока управления обменом и с пятыми входами подканалов абонента, третий выход первого регистра неисправности соединен с первым дополнительным входом коммутатора информации, трети

четвертый и пятый входы - соответственно с выходами первого, второго и третьего элементов ИЛИ, группы входов которых соединены соответственно с пятыми, шестыми и седьмыми выходами подканалов обонента, восьмые выходы которых подключены к группе входов второго регистра неисправности , выход которого подключен ко второму дополнительному входу коммутатора информации, шестые входы подканалов абонента соединены с седьмым выходом блока синхронизации, пятый выход регистра обмена соединен с шестым выходом блока управления обменом, а также тем, что подканал абонента содержит регистр служебных сигналов, первые вход и выход которого подключены соответственно к первым выходу и входу узла управления, вторые выход и вход - соответственно к управляющему входу и выходу подканала и через первый триггер неисправности к пятому выходу подканала, а третий вход - к первому выходу узла контроля подканала, первые и вторые входы и выходы регистра обмена подканала соединены соответственно с первыми выходом и входом коммутаторатипа передачи и четвертым входом и вторым выходом подканала, второй и третий входы узла управления соединены соответственно с выходом первого элемента и и шестым входом подканала, а второй выход через триггер готовности - с первым выходом подканала, первый вход первого элемента И соединен с третьим входом подканала, а второй выход - с выходом элемента ИЛИ, первый .и второй входы которого являются соответственно первым и втоpaBvm входами подканала, вторые вход и выход коммутатора типа передачи являются соответственно инфогя гадионными входом и выходом канала, третий вход соединен с третьим выходом узла управления, четвертый - восьмой выходы которого подключены соответственно к третьему входу регистра обмена подканала,. третьему выходу подканала, первому входу узла контроля подканала, первому входу элемента И и четвертому выходу подканала, вторые вход и выход узла контроля подканала соединены соответственн с третьим выходом и четвертым входом коммутатора типа передачи, а третий и четвертый выйрды соответственно через второй и третий триггеры неисправности с шестым и седьмым выходами подканалов, второй вход и выход второго элемента И является соответственно пятым входом и восьмым выходом подканала, и тем, что блок управления обменом содержит группу элементов И, первые входы KOTOJ JX соединены соответственно с третьим, четвертым и пятым входами блока.

.узел постоянной памяти, первый вход и выход которого соединены соответственно с шестым входом и четвертым выходом блока, вторые вход и выход соответственно со вторыми входом и выходом блока, а третьи выход и входсоответственно с пятым выходом блока и выходом дешифратора адреса микрокоманд, вход которого через счетчик адреса микрокоманд подключен к пер вому выходу модификатора адреса микрокоманд, первым входом соединенного с четвертым узла постоянной памяти, а вторыми входом и выходомсоответственно с первыми входом и выходом блока, вторые входы элементов И группы соединены со вторим входом блока, а выходы соответствую11их элементов И группы подключены к первому и второму выходам блока, и тем, что узел управления подканала содержит постоянную память, группа выходов которой соединена соответственно с первым - восьмым выходами узла, вход постоянной памяти соединен через дешифратор адреса микрокоманд с выходом счетчика адреса микрокоманд, а выход - с входом модификатора адреса микрокоманд группа входов которого подключена соответственно к первому - третьему входам узла, а выход - к входу счетчика адреса микрокоманд, и тем, что узел контроля подканала содержит триггер тестового режима, вход и выход которого соединены соответственно с первыми входом и выходом узла генератор кодов и регистр контроля, входы которых подключены к первому входу узла, а выходы соответственно ко второму и четвертому .выходами узла,, и счетчик сдвигов два входа и йыход которого соединены соответственно с первым и вторым входами и третьим выходом узла.

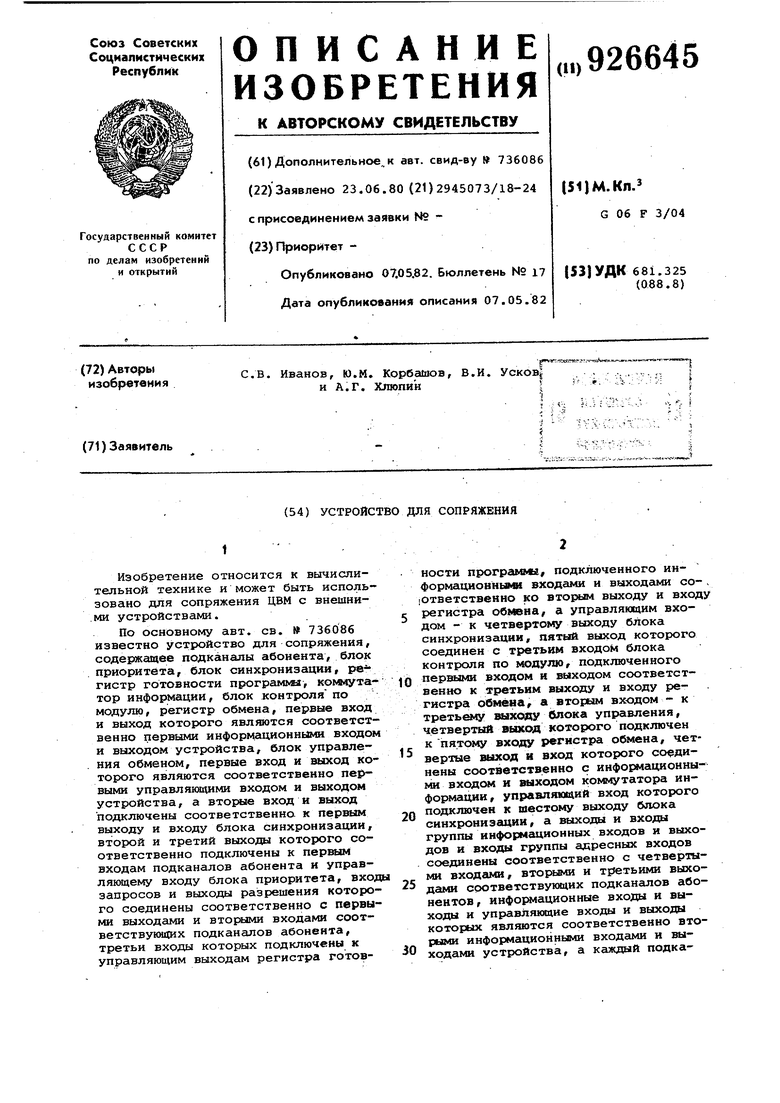

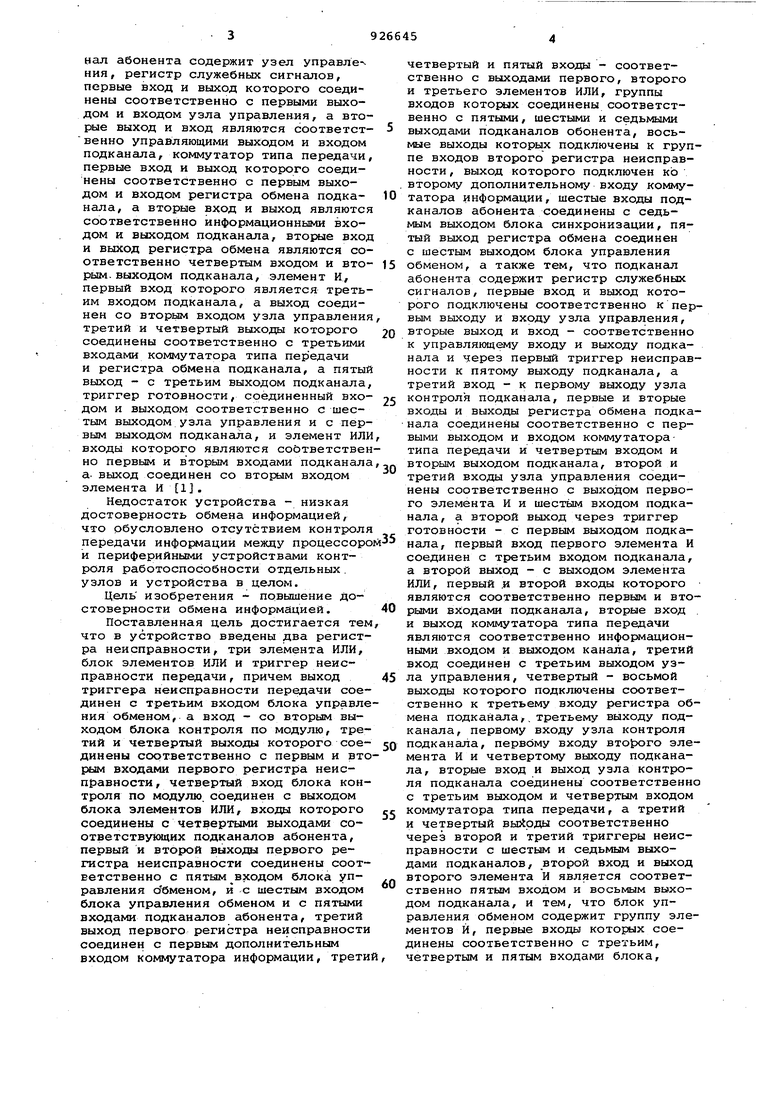

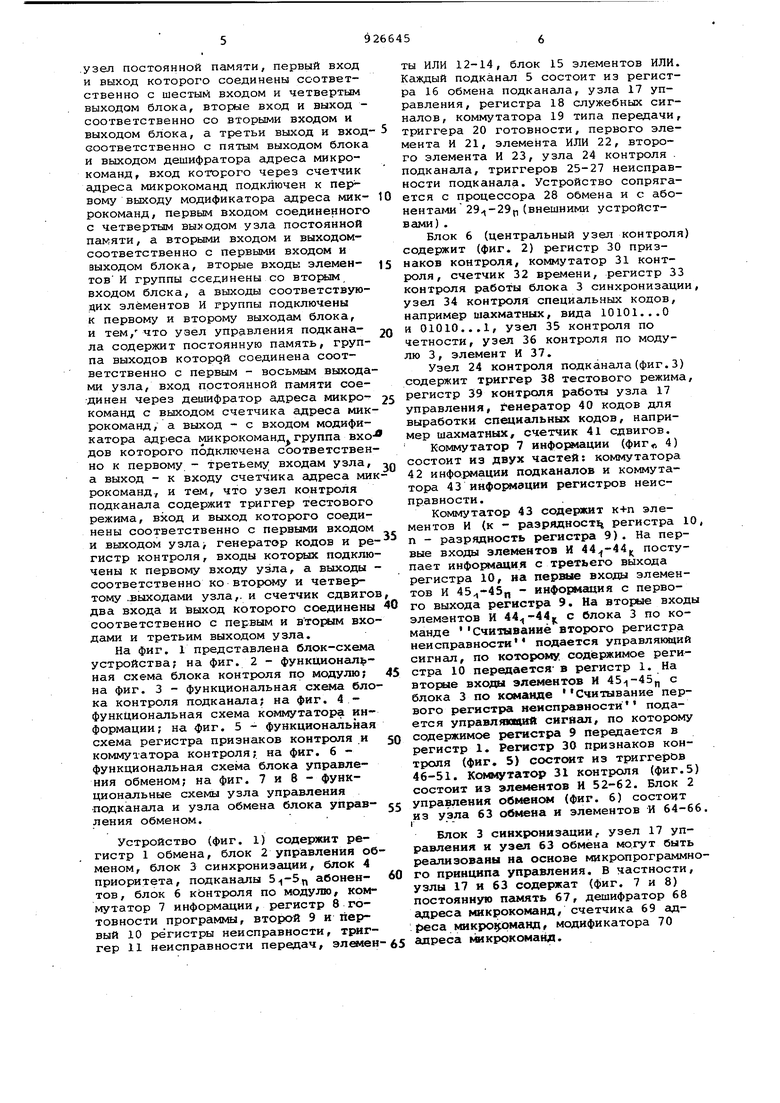

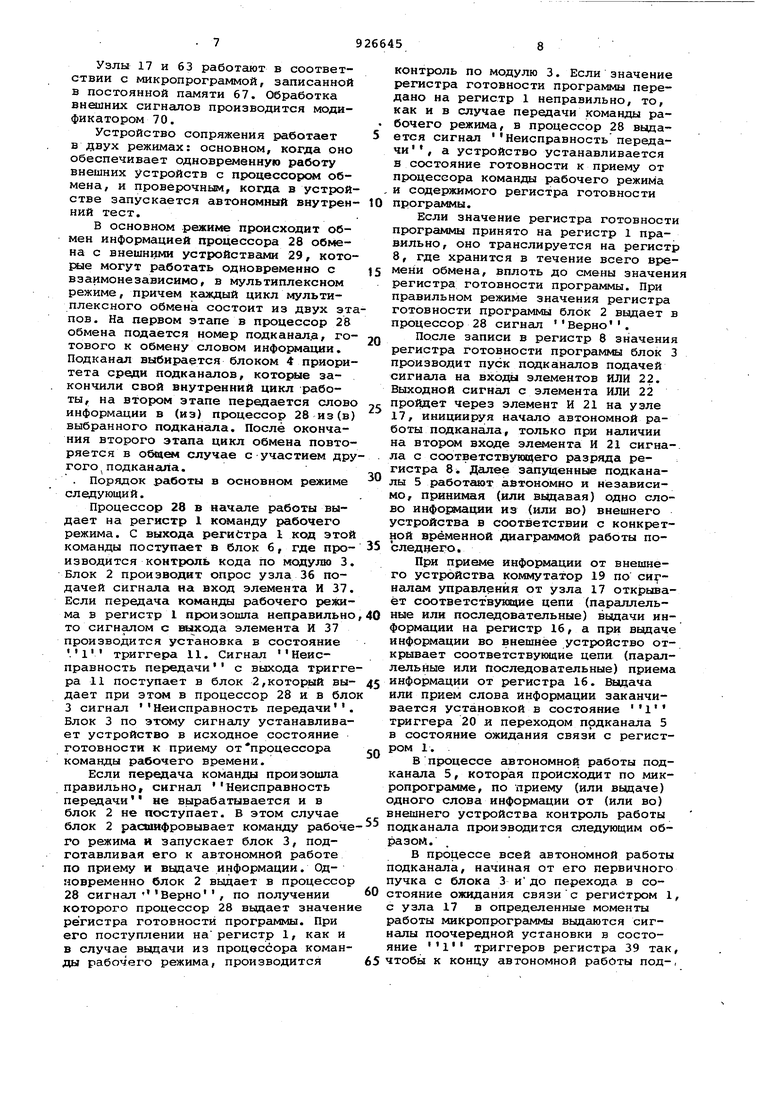

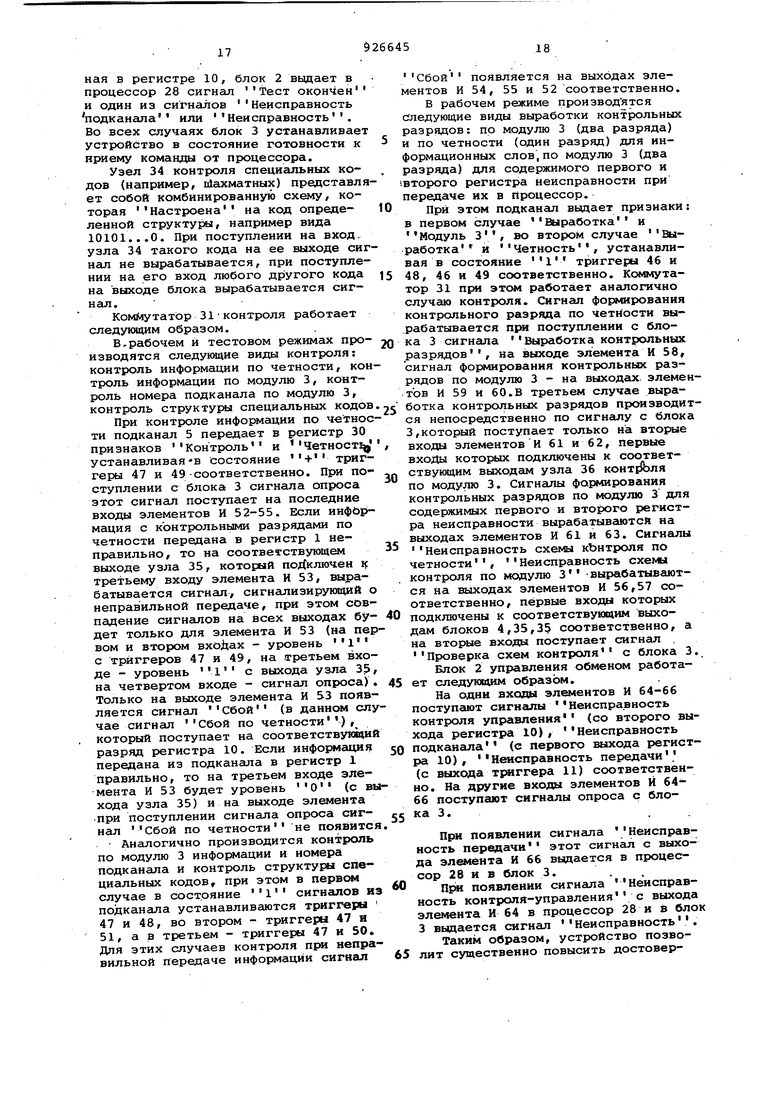

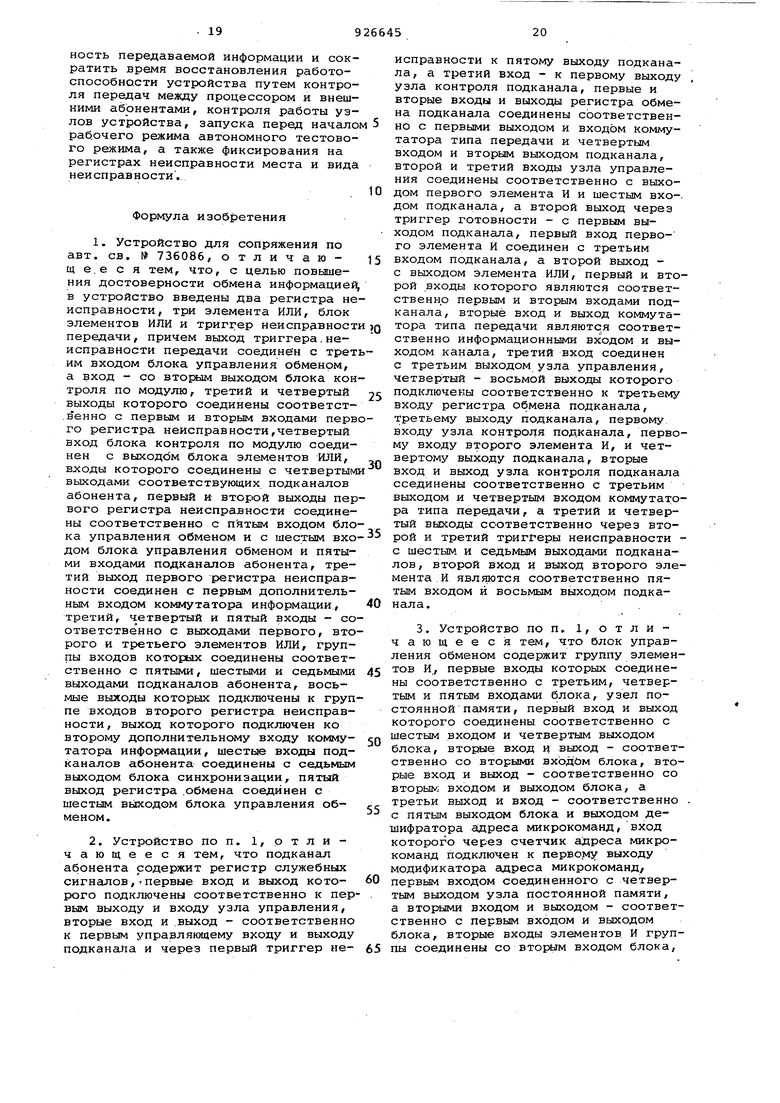

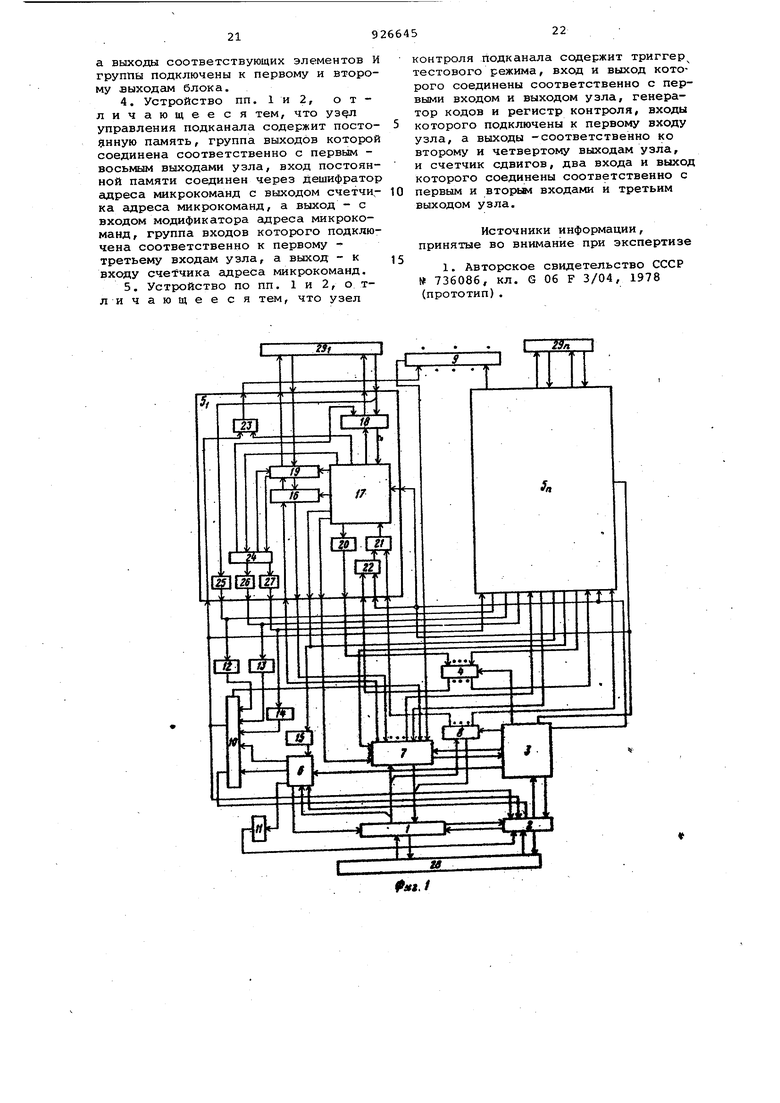

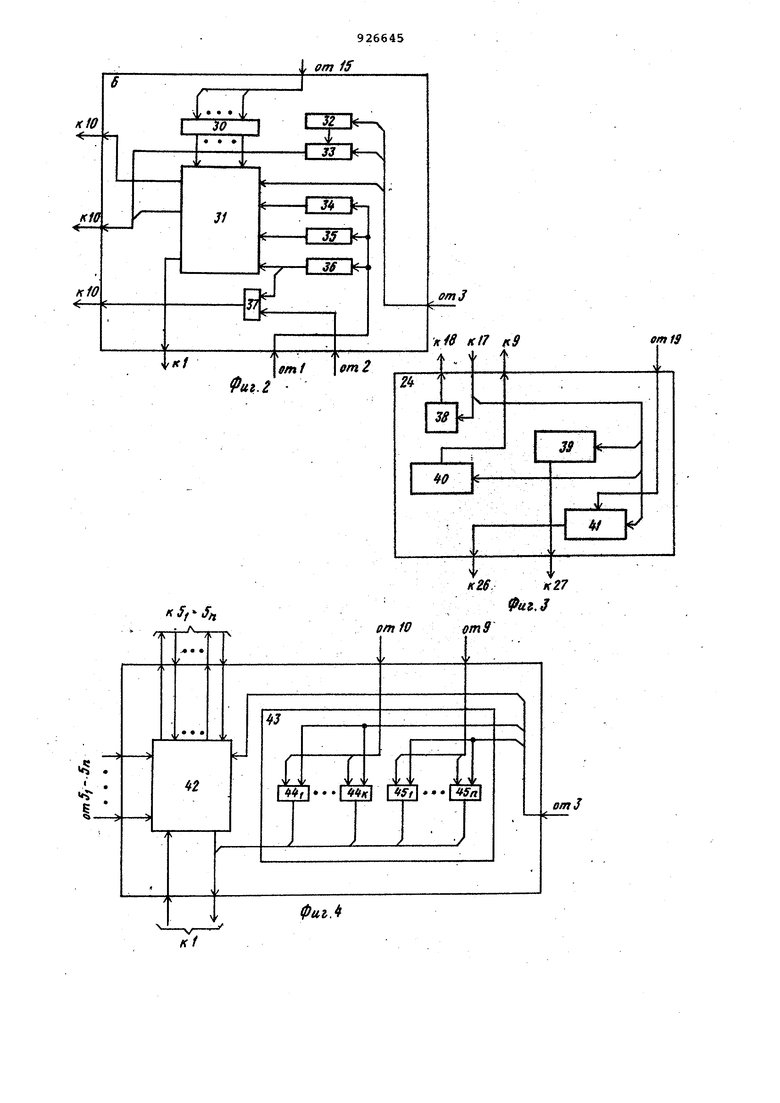

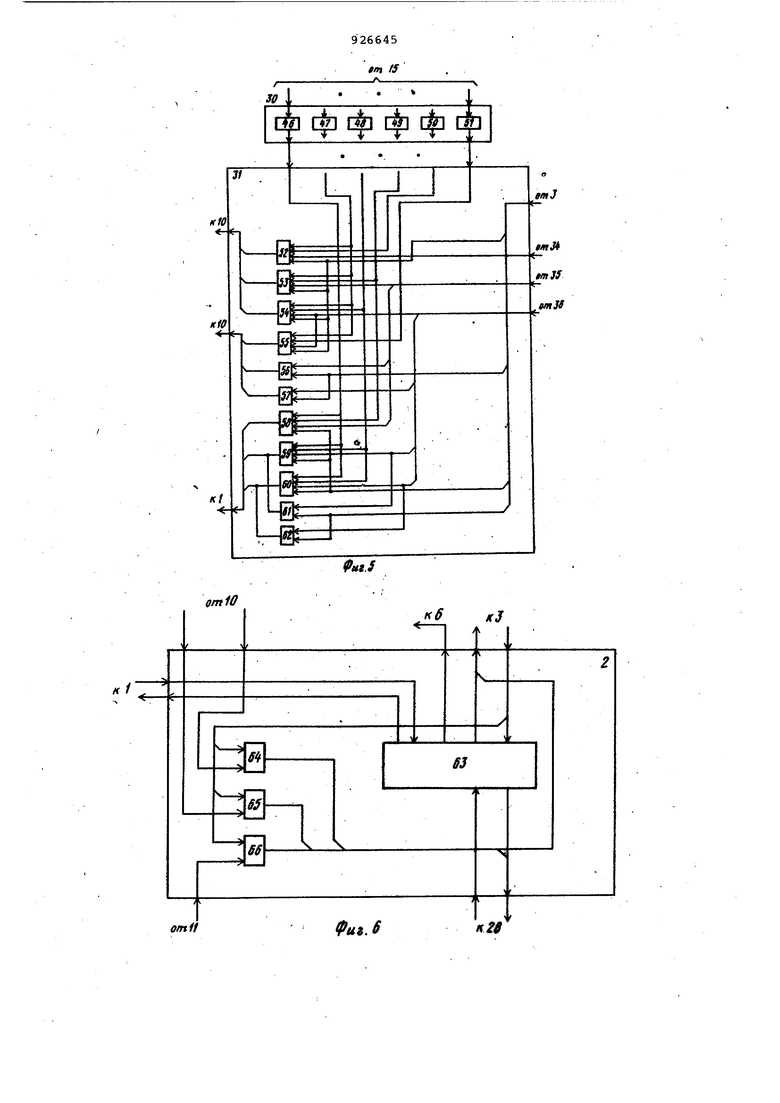

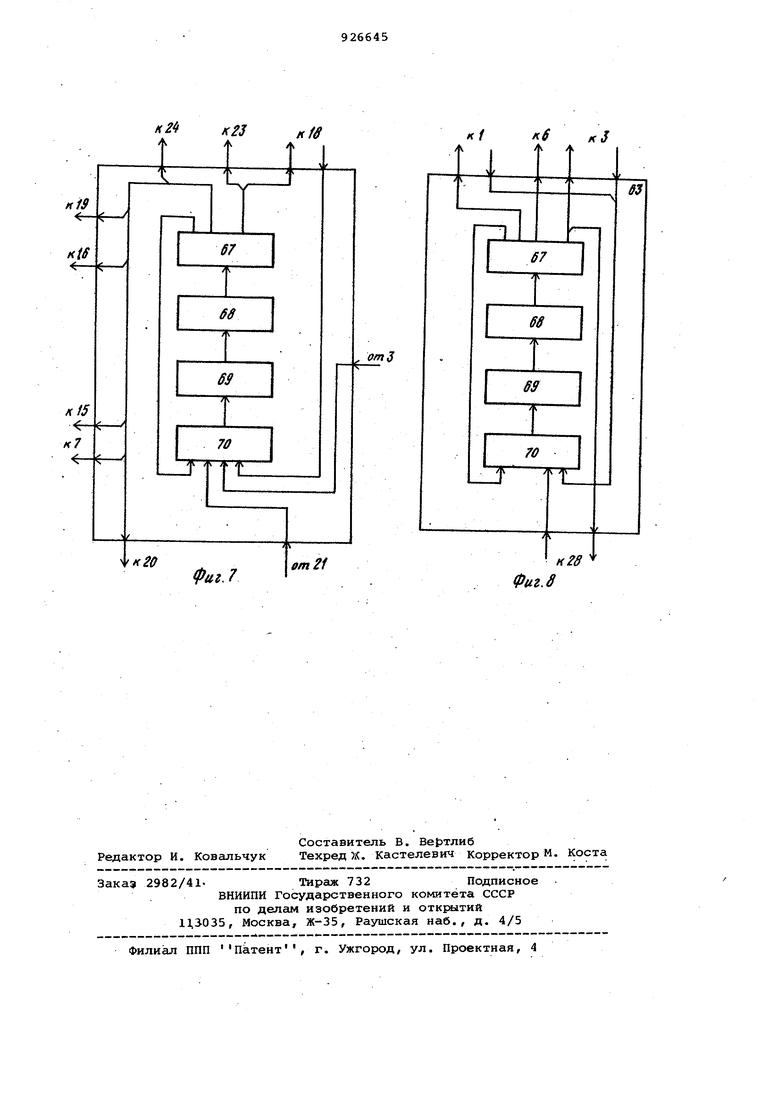

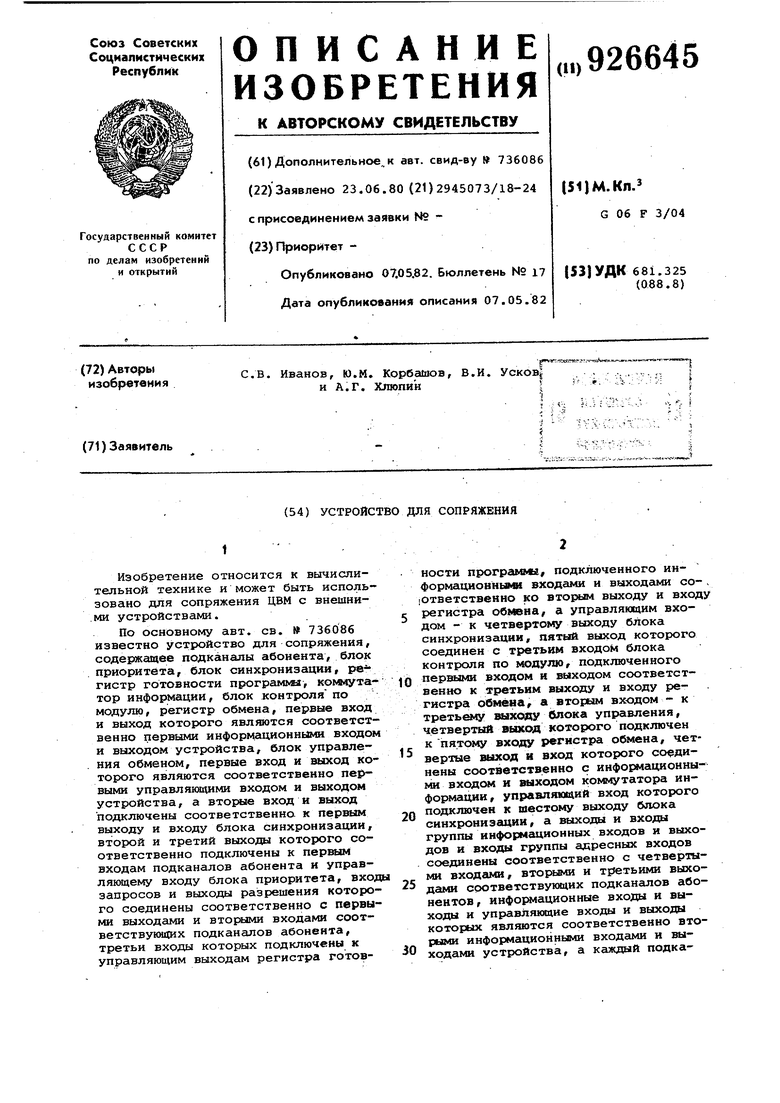

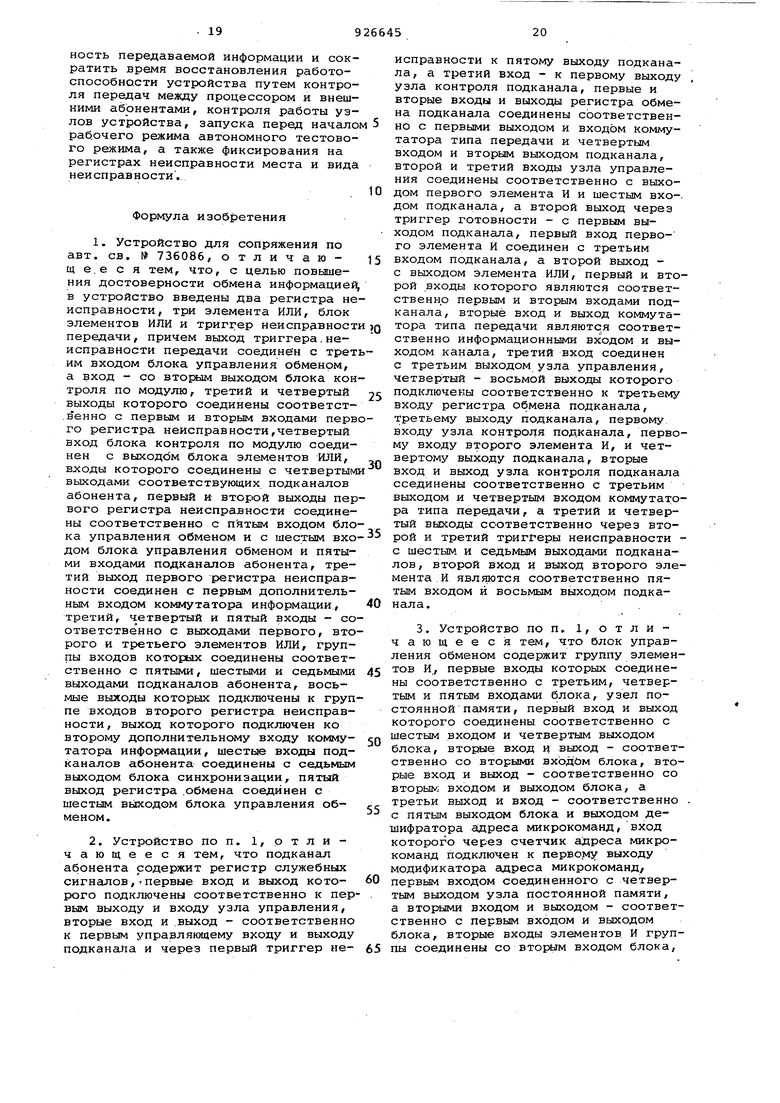

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - функционал ная схема блока контроля по модулю; на фиг. 3 - функциональная схема блока контроля подканала; на фиг. 4 функциональная схема коммутатора информации; на фиг. 5 - функциональная схема регистра признаков контроля и коммутатора контроля; на фиг. 6 функциональная схема блока управления обменом; на фиг. 7 и 8 - функциональные схемы узла управления подканала и узла обмена блока управления обменом.

Устройство (фиг. 1) содержит регистр 1 обмена, блок 2 управления обменом, блок 3 синхронизации, блок 4 приоритета, подканалы 5-|-5 абонентов, блок 6 контроля по модулю, коммутатор 7 информации, регистр 8 готовности программы, второй 9 и первый 10 регистры неисправности, триггер 11 неисправности передач, элоленты или 12-14, блок 15 злементов ИЛИ. Каждый подканал 5 состоит из регистра 16 обмена подканала, узла 17 управления, регистра 18 служебных сигналов, коммутатора 19 типа передачи, триггера 20 готовности, первого элемента и 21, элемента ИЛИ 22, второго элемента И 23, узла 24 контроля . подканала, триггеров 25-27 неисправности подканала. Устройство сопрягается с процессора 28 обмена и с абонентами (1 (внешними устройствами) .

Блок 6 (центральный узел контроля содержит (фиг. 2) регистр 30 признаков контроля, коммутатор 31 контроля, счетчик 32 времени, регистр 33 контроля работы блока 3 синхронизаци узел 34 контроля специальных кодов, например шахматных, вида 10101...О и 01010... 1, узел 35 контроля по четности, узел 36 контроля по модулю 3, элемент И 37.

Узел 24 контроля подканала(фиг.3) содержит триггер 38 тестового режима регистр 39 контроля работы узла 17 управления, Генератор 40 кодов для выработки специальных кодов, например шахматных, счетчик 41 сдвигов.

Коммутатор 7 информации (фиг« 4) состоит из двух частей: коммутатора 42 информации подканалов и коммутатора 43 информации регистров неисправности.

Коммутатор 43 содержит к+п элементов И (к - разрядност регистра 1 п - разрядность регистра 9). На первые входы элементов И , поступает информация с третьего выхода регистра 10, на первые входы элементов И - информация с первого выхода регистра 9. На вторые вход элементов И 44.,-44 с блока 3 по команде Считывание второго регистра неисправности подается управлякиций сигнал, по которому. сод1вржимое регистра 10 передается- в регистр 1. На вторые входы элементов И 45-,-45 с блока 3 по команде Считывание первого регистра неисправности подается управляов1Ий сигйсш, по которому содержимое регистра 9 передается в регистр 1. Регистр 30 признаков контроля (фиг. 5) состоит из триггеров 46-51. Коммутатор 31 контроля (фиг.5 состоит из элементов И 52-62. Блок 2 управления обменом (фиг. 6) состоит из узла 63 обмена и элементов И 64-6

Блок 3 синхронизации, узел 17 управления и узел 63 обмена мо.гут быть реализованы на основе микропрограммнго принципа управления. В частности, узлы 17 и 63 содержат (фиг. 7 и 8) постоянную 67, дешифратор 68 адреса микрокоманд, счетчика 69 адреса микро ррманд, модификатора 70 адреса aIкpoкoмaнд. Узлы 17 и 63 работают в соответствии с микропрограммой, записанной в постоянной памяти 67. Обработка внешних сигналов производится модификатором 70, Устройство сопряжения работает в двух режимах: основном, когда оно обеспечивает одновременную работу внешних устройств с процессором обмена, и проверочным, когда в устройстве запускается автономный внутренНИИ тест. В основном режиме происходит обмен информацией процессора 28 обмена с внешними устройствами 29, котоЕжле могут работать одновременно с взаимонезависимо, в мультиплексном режиме, причем каждый цикл мультиплексного обмена состоит из двух эт пов. На первом этапе в процессор 2& обмена подается номер подканалу, готового к обмену словом информации. Подканал выбирается блоком 4 приоритета среди подканалов, которые закончили свой внутренний цикл работы на втором этапе передается слово информации в (из) процессор 28 из(в выбранного подканала. После окончания второго этапа цикл обмена повторяется в общем случае с участием дру гого подканала. . Порядок работы в основном режиме следующий. Процессор 28 в начале работы выдает на регистр 1 команду рабочего режима. С выхода регистра 1 код этой команды поступает в блок 6, где производится контроль кода по модулю 3 Блок 2 производит опрос узла 36 подачей сигнала на вход элемента И 37 Если передача команды рабочего режима в регистр 1 произошла неправильно то сигналом с выхода элемента И 37 производится установка в состояние . триггера 11. Сигнал Неисправность передачи с выхода тригге ра 11 поступает в блок 2,который вы дает при этом в процессор 28 и в бл 3 сигнал Неисправность передачи Блок 3 по этому сигналу устанавливает устройство в исходное состояние готовности к приему отпроцессора команды рабочего времени. Если передача команды произошла правильно, сигнал Неисправность передачи не вырабатывается и в блок 2 не поступает. В этом случае блок 2 расшифровывает команду рабоч го режима и запускает блок 3, подготавливая его к автономной работе по приему и выдаче информации. Одновременно блок 2 выдает в процессо 28 сигнал Верно, по получении которого процессор 28 выдает значени регистра готовности программы. При его поступлении на регистр 1, как и в случае выдачи из процессора команды рабочего режима, производится контроль по модулю 3. Если значение регистра готовности программы передано на регистр 1 неправильно, то, как и в случае передачи команды рабочего режима, в процессор 28 выдается сигнал Неисправность передачи, а устройство устанавливается в состояние готовности к приему от процессора команды рабочего режима и содержимого регистра готовности программы. Если значение регистра готовности программы принято на регистр 1 правильно, оно транслируется на регистр 8, где хранится в течение всего времени обмена, вплоть до смены значения регистра готовности программы. При правильном режиме значения регистра готовности программы блок 2 вьщает в процессор 28 сигнал Верно. После записи в регистр 8 значения регистра готовности программы блок 3 производит пуск подканалов подачей сигнала на входы элементов ИЛИ 22. Выходной сигнал с элемента ИЛИ 22 пройдет через элемент И 21 на узле 17, инициируя начало автономной работы подканала, только при наличии на втором входе элемента И 21 сигнала с соответствующего разряда регистра 8 Далее запущенные подканалы 5 работают автономно и независимо, принимая (или вьасцавая) одно слово инфор лации из (или во) внешнего устройства в соответствии с конкретной временной диаграммой работы последнего. При приеме информации от внешнего устройства коммутатор 19 по сигналам управления от узла 17 открывает соответствуюощё цепи (параллельные или последовательные) выдачи информации на регистр 16, а при выдаче информации во внешнее устройство открывает соответствующие цепи (параллельные или последовательные) приема информации от регистра 16. Выдача или прием слова информации заканчивается установкой в состояние i триггера 20 и переходом подканала 5 в состояние ожидания связи с регистром 1. В процессе автономной работы подканала 5, которая происходит по микропрограмме, по приему (или выдаче) одного слова информации от (или во) внешнего устройства контроль работы подканала производится следующим образом. В процессе всей автономной работы подканала, начиная от его первичного пучка с блока 3 и до перехода в состояние ожидания связи с регистром 1, с узла 17 в определенные моменты работы микропрограммы выдаются сигналы поочередной установки в состояние триггеров регистра 39 так, чтобы к концу автономной работы под-, канала все триггеры регистра 39 находились в состоянии . После установки в cocTOHHjie триггера 20 узел 17 производит опрос состояния регистра 39, При этом, если хотя бы один из триггеров регистра 39 находился в состоянии О, например, из-за сбоя в работе узла 17, в резул тате чего не был установлен в состоодин или несколько триггеров регистра 39, на выходе регйстра 39 вырабатывается сигнаш, который устанавливает в состояние триг гер 27, Кроме того, если подканал 5 принимает информацию от внешнего уст ройства в последовательном коде, npo изводится контроль количества разрядов в принятом слове информации. Для этого,, перед приемом слова в Е егистр 16 сигналом с узла 17 производится предварительная запись двоичного кода всчетчик 41, при этом код должен быть таким, чтобы при прибавлении к нему двоичного кода, соответствующего принятой для конкретного абонента разрядности слова информацииj происходило переполнение счетчика 41 с установкой в состояние О всех его разрядов. После записи, кода в счетчик 41i.e производитсяприем слова информации на регистр 16, причем сигналы сдвига информации 16 и на счетчик 41. По окончании приема слова информации с узла 17 производится опрос состояния счетчика 41. В том случае, если хотя бы один из его разрядов находится в состоянии , например, когда 1из-за себя или в работе вноинего устройства, или при передаче инфор мации из внешнего устройства в подканал, или в работе коммутатора 19 происходит пропадание хотя -бы одного разряда слова информации, в результате чего число разрядов, поступивших на регистр 16 (и на счетчик 41) оказалось меньше положенного, с выхода счетчика вырабатывается сиг нал, который устанавливает в состояние триггер 26. Кроме того, если в процессе выдачи (или приёма) информации во внешнем устройстве про исходит сбой, внешнее устройство выдает служебный сигнал Сбой внешнего устройства , который фиксируется на триггере 25, устанавливая его в состояние Обмен информацией подканалов 5 е процессором обмена происходит в два этапа. На первом этапе блок 3, подавая сигнал на блок 4, выделяет номер ста шего подканала из числа выставивших свои готовности. Блок 4 разрешает ра боту одного подканала 5 выдавая сиг нал через первый вход элемента ИЛИ 2 и элемент И 21 на узел 17, который через соответствующий вход коммутатора 7 записыйает номер этого подканала, в позиционном коде, т.е. с в одном из разрядов с контрольными разрядами по модулю 3 в регистр 1. После этого блок 3 производит опрос узла 36 подачей сигнала на коммутатор 31, на соответствующем выходе которого в случае неправильной передачи номера подканала или неправильной выработки контрольных разрядов по модулю 3 для номера подканала появляется сигнал Сбой номера подканала .. Регистр 10 неисправности состоит из двух частей, причем первой части регистра соответствует первый выход регистра, а второй части - второй выход. В первой части регистра 10 фиксируются неисправности, которые появились при работе подканала (каждому виду неисправности соответствует определенный триггер). При установке в состояние Ч одного или нескольких разрядов первой части регистра 10 на его первом выходе появляется интегральный сигнал Неисправность подканала . Во второй части регистра 10 фиксируются неисправности, обнаруженные в работе блока 3, блока 4 и блока 6, при этом н, втором выходе регистра 10 появляется интегральный сигнал Неисправность контроля-управления. СигнсШ Сбой номера подканала устанавливает в состояние соответствуювдий разряд второй части регистра 10, на выходе которого появляется интегральный сигнал Неисправность контроля-управления, поступакщий в блок 2, в этом случае вьдает в процессор 28 сигнал Неисправность. Одновременно блок 2 выдает этот же сигнал в блок 3, который, получив сигнал Неисправность устанавливает устройство в исходное срстояниа готовности к приему от процессора команды рабочего режима или команды на считывание содержимого первого и (или)- второго регистра неисправности. Если номер подканала в регистр 1 передан неправильно, сигнал Неисправность контроля-управления не вырабатывается, в этом случае блок 3 запускает блок 2, который управляет вьадачей номера выбранного подканала из регистра 1 по информационньам шинам в параллельном коде в процессор 28. Процессор по принятому номеру подканала готовит адрес буферной зоны памяти для записи или -считывания слова информации. На втором этапе происходит собственно передача слова информации от выбранного подканала 5 в регистр 1 через коммутатор 7 или наоборот, из

регистра 1 в подканал 5 через коммутатор 7. Обмен словом информации при этом происходит в параллельном коде, причем обменом управляет узел 17 и блок 3.

Выдача слова информации из подканала 5 в процессор 28 происходит следующим образом.

После подготовки адреса буферной зоны памяти процессор 28 через блок 2 выдает в блок 3 сигнал начала передачи слова информации из подканала При этом блок 3 вьадает в узлы 17 все подканалов сигнал начала передачи слова информации в регистр 1, а в коммутатор 7 - управляющий сигнал, по которому происходит передача слова информации из регистра 16 подканала через коммутатор 7 в регистр 1. Сигнал начала передачи слова информации воспринимается только одним из подканалов, а именно тем, номер.которого передан в процессор. По этому сигналу узел 17 выдает в блок б на регистр 30, каждый разряд которого соответствует определенному виду контроля или выработки контрольных разрядов, признаки контроля, установкой в состоянии Ч соответствующих разрядов регистра 30, и управляющий сигнал на соответствующий вход коммутатора 7..

После передачи слова информации из регистра 16 в регистр 1 блок 4 производит опрос коммутатора 31, в котором этот сигнал опроса подключается к одному из выходов узлов 34-36 в соответствии с содержимым регистра 30.

Если передача слова информации из регистра 16 (или в общем случае из внешнего устройства 29) в регистр 1 произведена неправильно, на соответствующем выходе коммутатора 31 появляется сигнал Сбой, например, Сбой по четности , или Сбой по модулю 3. , который устанавливает в состояние соответствующий разряд первой части регистра 10.

Одновременно с опросом коммутатор 31 сигналом с блока 3 (не показано) Производится передача содержимого триггеров 25-27 данного подканала в регистр 10 через элементы ИЛИ 12-14 Соответственно. Если при работе подканала по приему слова информации от внешнего устройства происходит сбой в работе узла 17 или появляется сигнал неисправности от внешнего устройства, или при работе подканала в последовательном коде происходит сбо то соответствующие триггеры 25-27 находятсяв состоянии и в это состояние устанавливаются соответствующие им разряды первой части регисра 10.

При установке одного или нескольких разрядов первой части регистра 1

в состояние i с выхода регистра 10 вырабатывается интегральный сигнал Неисправность подканала , который поступает на входы элементов И 23 всех подканалов, и в блок 2. После передачи слова информации с регистра 16 на регистр 1 с узла 17 только того подканала, который находится в состоянии обмена с регистром 1, на соответствующий вход элемента И 23 этого подканала поступает сигнал опроса. При появлении сигнала опроса на выходе элемента И 23 появляется сигнал, который устанавливает в состояние i соответствующий этому подканалу разряд регистра 9. В результате блок 2 выдает в процессор и в блок 3 сигнал Неисправность подканала , блок 3 по этому сигналу устанавливает устройство в исходное состояние готовности к приему от процессора командам рабочего режима или команды на считывание первого и (или) второго регистра неисправности, в регистре 9 позиционным входом записан номер подканала, .при работе которого произошла неисправность, а в регистре 10 зафиксирован вид неисправности.

Если передача информации из регисра 16 (или в общем случае из внешнего устройства 29) в регистр 1 произведена правильно и отсутствуют неисправности в работе узла 17 и внешнего устройства, т.е. все триггеры первой части регистра 10 находятся в состоянии О, сигнал Неисправность подкансша на первом выходе регистра 10 не появляется. В этом слчае блок 3 подает на блок 6 сигнал Выработка контрольных разрядов и передает управление блоку 2. Если информация от внешнего устройства, соответствующего данному подканалу, передается с контролем по модулю 3, то разряд в 1эегистре 30, соответствующий выработке контрольных разрядов, находится в состоянии , и контрольные разряды содержимого регистра 1 не изменяются. Блок 2 производит передачу содержимого регистра 1 в процессор 28.

Если информация от внешнего устройства поступает с контрольными разрядами, например по четности, то в регистре 30 в состоянии i находяся разряды Выработка контрольных разрядов и Модуль 3. Сигналы с выходов этих разрядов подключают в коммутаторе 31 сигнал Выработка контрольных разрядов , поступающий с блока 3, к выходу узла 36. С соответствующего выхода коммутатора 31 произведено гашение в регистре 1 контрольных разрядов по четности и запись их нового значения для контроля по модулю 3. После этого блок 2 производит передачу содержимого ре1истра 1 в процессор 28, Вьщача слова -информации из процессора 28 в подканал производится следующим образом. После приема слова информации от процессора на регистр 1 блок 2 прои водит контроль содержимого регистра 1 по модулю 3 подачей сигнала опрос на блок 6. В случае отсутствия сигнала неисправности передачи с триггера 11 блок 2 передает управление блоку 3. Блок 3 выдает в узлы 17 все подканалов сигнал управления, который воспринимается только работающим подканалом, номер которого передан в процессор. По этому сигналу подканал выдает в блок 6 на регистр 30 признаки контроля.. После этого блок 3 вьщает в блок 6 сигнал Выработка контрольных разрядов . Действия производимые по этому сигналу, аналогичны случаю выработки контрольных разрядов при пер-едаче информации из подканала абонента в регистр 1. При этом, если информация во внешнее устройство, соответствующее данному подканалу, передается с контролем по модулю 3, то разряд Выработка контрольных в регистре 30 нй ходится в состоянии О, и контрол ные разряды содержимого регистра 1 не изменяются. После этого блок 3 выдает на узлы 17 всех подканалов сигнал Начало передачи информации который воспринимается только работа ющим подканалом, и сигнал на управляющий вход коммутатора 7. По сигналам управления, поступающим на ком мутатор 7 с блока 3 и с узла 17 работающего подканала, производится.пе редача содержимого регистра I в регистр 16 соответствующего подканала После этого подканал 5 автономно передает слово информации во внешнее устройство. После окончания этого этапа цикл обмена повторяется в общем случае с участием другого подканала, этом перед началом нового цикла .обмена блок 3 производит гашение регистра 3 (связи не показаны). При каждом цикле обмена подканала 5 с процессором 28 контроль работы блоков 3 и 6 производится следующим образом. В начале цикла обмена блок 3 производит запись в счетчик .32 двоичног кода, соответствующего длительности одного цикла обмена подканала с процессором, и производит пуск счетчика 32. В течение цикла обмена блок 3 как и в случае контроля работы узла. 17, последовательно устанавливает разряды регистра в состояние 33. По истечении времени, отвеяенного для обмена, происходит переполнение счетчика 32, и с его выхода вырабатывается сигнал, которыя поступает на регистр 33, В том случае, когда хотя бы один из разрядов регистра 33 находится в состоянии О, с выхода регистра 33 вырабатывается сигнал Неисправность блока синхронизации, который устанавливает в состояние 1 соответствуклдий разряд второй части регистра 10. С выхода регистра 10 вырабатывается интегральный сигнал Неисправность контроля-управления, по которому блок 2 вырабатывает и передает в блок Зин процессор сигнал Неисправность. По, этому сигналу блок 3 устанавливает устройство в состояние готовности к приему от процессора 28 команды рабочего режима или команды на считывание первого и (или) второго регистра неисправности. Кроме того, при неправильной работе узлов 35 и 36 встроенные в них схемы контроля вырабатывают сигналы неисправности. Блок 3 по окончании каждого цикла обмена производит опрос этих схем подачей сигнала Проверка схем контроля на коммутатор 13, При неисправности узлов 35 и 36 на соответствующем выходе коммутатора 31 в.ырабатываются сигналы Неисправность схемы контроля по четноцти Неисправность схемы контроля по и модулю 3, которые устанавливают в соответствующие разсостояниеряды второй части регистра 10. С выхода регистра 10 при этом вырабатывается сигнал Неисправность контроля-управления, по которому блок 2 передает сигнал Неисправность в блок 3 и в процессор. По этому сигналу блок 3 производит установку устройства в состояние готовности к приему от процессора команды рабочего режима или команды на считывание первого и (или) второго регистра неисправности. Таким образом, в режиме обмена информацией с внешним устройством процессор 28 может получить сигналы НеисНеисправность передачи правность подканала и Неисправность, По этим сигналам, а также по содержимым регистров 9 и 10, которые могут быть переданы в процессор по специальной команде Считывание первого (второго) регистра неисправности, можно судить о виде неисправности и локализовать с определенной точностью неисправный узел устройства. Например, при получении процессором сигнала Неисправность передачи и при нулевом состоянии регистра 10 можно считать, что неисправны регистр 1 или (и) блок 2. Если одновременно с сигналом Неисправность передачи в состоянии находится разряд второй части регистра 1.0 Неисправность схемы контроля по модулю 3, то неисправным может быть блок 6. Считывание содержимого регистра 9(10) производится следующим образом Процессор 28 ввдает на регистр 1 команду Считывание первого (второго), регистра неисправности . Если команда передана на регистр 1 правильно, блок 2 расшифровывает команду и передает управление блоку 3. С блока 3 на коммутатор 7 выдается сигнал управления, по которому производится передача содержимого регистра 9(10) на регистр 1 через коммутатор 7. После этого по сигналу с блока 3 блок 6 производит выработку значения контрольных разрядов по модулю 3 для содержимого первого (второго) регистра неисправности и запись значения на регистр 1. После выработки контрольных разрядов, блок 2 производит вьщачу содержимого.регистра 1 в процессор 28. При получении команды рабочего ре жима после ее расшифровки и запуска блока 3 (с блока 2) блОк 3 перед началом работы всегда производит гашение первого и второго регистров неисправности и триггера 11 В проверочном режиме устройство работает следующим образом. Проверочный режим, при котором запускается внутренний автономный тест устройства, задается процессором. Для этого процессор 28 выдает на регистр 1 команду Тест. При этом, как и в случав пер.едачи команд и информации в рабочем режиме, произ водится контроль принятого на регист 1 кода команды по модулю 3. Если передача команды произведена правильно, блок 2 расшифровывает-команду и запускает блок 3, подготавливая его к автономной работе по организации режима Тест. Блок 3 устанавливает в состояние все разряды регистра 8, имити руя готовность программы к обмену с всеми внешними устройствами. После этого блок 3 выдает в узлы 17 всех подканалов сигнал Тестовый режим и производит пуск всех подканалов 5 подачей сигнала на входы элементов ИЛИ 22. Далее подканалы работают ав тономно и независимо друг от друга, при этом каждый подканал работает следующим образом. Сигналом с узла 17 производится пуск генератора 40, устанавливая в состояние 1 триг гер 38, и производится блокировка шин связи с внешним устройством (подачей управляющих сигналов на коммутатор 19 и регистр 18), по кото рым производится передача информации и управляющих сигналов. Сигнал с еди ничного выхода триггера.- 38. поступае в регистр 18, имитируя наличие управляющих сигналов внешнего устройства. После этого в генераторе 40 вырабатывается и передается в регистр 1Б через коммутатор 19 специальный код,например шахматный,вида 10101.. .0 или 01010... 1. После записи в регистр 16 специального кода узел 17 выполняет те же действия по приему слова от внешнего устройства, что и в рабочем режиме, но при этом узел 17 работает не по реальным,а по имитированньгм управлякнцим сигналам и не выдает сигнал записи информации в регистр 16, так как там уже записан специальный код. После окончания действия по приему слова информации от внешнего устройства узел 17 устанавливает в состояние триггер 20 и переходит в состояние ожидания обмена с регистром 1. Циклы обмена подканалов абонентов с регистром 1 организуются также, как и в случае рабочего режима, т.е. с предварительной вьвдачей в регистр 1 номера подканала и с выдачей в блок 6 признаков контроля, но в тестовом режиме есть несколько отличий от обмена в рабочем режиме. Во-первых, номера подканалов и коды, поступившие на регистр 1 с регистров 16 в процессор 28 не передаются, после контроля правильности их передачи в регистр 1 сигналом с блока 2 каждый раз производится гашение регистра 1, т.е. установка его в состояние О. Во-вто|)ых, в процессе циклов обмена при тестовом режиме производится только два вида контроля содержимого регистра 1, а именно, при передаче номера подканала - контроль по модулю 3,при передаче специальных кодов с регистров 16 (одного истого же для всех подканалов) - контроль структуры этого кода, поэтому все подканалы передают в регистр 30 одни и те же признаки контроля (при передаче номера подканала - контроль по модулю 3, при передаче кода - контроль структуры специального кода). Так же, как и в рабочем режиме, в тестовом режиме производится контроль работы узла 17 подканала, блоков 3 ,,и 6, на регистре 10 фиксируется вид неисправности, а на регистре 9 позиционным кодом нсииер подканала, при работе которого произошла неисправность. После окончания режима Тест, в если неисправность не была обнаружена, т.е. не было сигналов неисправности на выходахрегистра 10, блок 2 выдает в йроцессор 28 сигнал Тест окончен и управлякнций сигнал в блок 3, который устанавливает устройство в состояние готовности к приему команды от процессора. Если в режиме Тест была обнаружена неисправность, зафиксированная в регистре 10, блок 2 вьщает в процессор 28 сигнал Тест окончен и один из сигналов Неисправность подканала или Неисправность. Во всех случаях блок 3 устанавливает устройство в состояние готовности к приему команды от процессора. Узел 34 контроля специальных кодов (например, г ахматных) представля ет собой комбинированную схему, которая Настроена на код определенной структуЕЯл, например вида 10101...0. При поступлении на вход, узла 34 такого кода на ее выходе сиг нал не вырабатывается, при поступлении на его вход любого другого кода на выходе блока вырабатывается сигнал. Коммутатор 31контроля работает следующим образом. В грабочем и тестовом режимах производятся следунндие виды контроля: контроль информации по четности, кон троль информации по модулю 3, контроль номера подканала по модулю 3, контроль структуры специальных кодов При контроле информации по четнос ти подканал 5 передает в регистр 30 признаков Контроль и Четност1|| устанавливая-в состояние + триггеры 47 и 49 соответственно. При поступлении с блока 3 сигнала опроса этот сигнал поступает на последние входы элементов И 52-55. Если информация с контрольными разрядами по четности передана в регистр 1 неправильно, то на соответствующем выходе узла 35, который подключен i третьему входу элемента И 53, вырабатывается сигнсш, сигнёшизирующий о неправильной передаче, при этом совпадение сигналов на всех выходах будет только для элемента И 53 (на пер вом и втором Bxoijax - уровень с триггеров 47 и 49, на третьем входе - уровень с выхода узла 35, на четвертом входе - сигнал опроса). Только на выходе элемента И 53 появляется сигнал Сбой (в данном слу чае сигнал Сбой по четности ), который поступает на соответствующий разряд регистра 10. Если информация передана из подканала в регистр 1 правильно, то на третьем входе элемента И 53 будет уровень О (с вы хода узла 35) и на выходе элемента при поступлении сигнала опроса сигнал Сбой по четности не появится Аналогично производится контроль по модулю 3 инфогмации и номера подканала и контроль структу специальных кодов, при этом в первом случае в состояние i сигналов из подканала устанавливаются триггеры 47 и 48, во втором - триггеры 47 и 51, а в третьем - триггеры 47 и 50. Для этих случаев контроля при неправильной передаче информации сигнаил Сбой появляется на выходах элементов И 54, 55 и 52 соответственно. В рабочем режиме производил тс я Следующие виды выработки контрольных разрядов: по модулю 3 (два разряда) и по четности (один разряд) для информационных слов,по модулю 3 (два разряда) для содержимого первого и второго регистра неисправности при передаче их в процессор. При этом подканал выдает признаки: в первом случае Выработка и Модуль 3, во втором случае Выработка и Четность, устанавливая в состояние Ч триггеры 46 и 48, 46 и 49 соответственно. Коммутатор 31 ufM этом работает аналогично случаю контроля. Сигнал формирования контрольного разряда по четности вы.рабатывается при поступлении с блока 3 сигнала Выработка контрольных разрядов , на выходе элемента И 58, сигнал форвлирования контрольных разрядов по модулю 3 - на выкодах. элементов И 59 и 60.В третьем случае выработка контрольных разрядов производится непосредственно по сигнгшу с блока 3,который поступает только на вторые входы элементов И 61 и 62, первые входы которых подключены к соответствующим выходам узла 36 конт|А5ля по модулю 3. Сигналы формирования контрольных разрядов по модулю 3 для содержимых первого и BTOjxDro регистра неисправности вырабатываются на выходах элементов И 61 и 63. Сигналы Неисправность схемы кЬнтроля по четности , Неисправность схемы контроля по модулю 3вырабатываются на выходах элементов И 56,57 соответственно, первые входы которых подключены к соответствующим выходам блоков 4,35,35 соответственно, а на вторые входы поступает сигнал , Проверка схем контроля с блока 3. Блок 2 управления обменом работает следукхдим образом. На одни входы элементов И 64-66 поступают сигналы Неисправность контроля управления (со второго выхода регистра 10), Неисправность подканала (е первого выхода регистра 10), Неисправность передачи (с выхода Т1жггера 11) соответственно. На другие входы элементов И 6466 поступают сигналы опроса с блока 3. При появлении сигнала Неисправность передачи этот сигнал с выхода элемента И 66 выдается в процессор 26 и в блок 3. . При появлении сигнала Неисправность контроля-управления с выхода элемента И 64 в процессор 28 и в Олок 3 выдается сигнал Неисправность. Таким образом, устройство позволит существенно повысить достоверность передаваемой информации и сократить время восстановления работоспособности устройства путем контроля передач между процессором и внешними абонентами, контроля работы узлов устройства, запуска перед начало рабочего режима автономного тестового режима, а также фиксирования на регистрах неисправности места и вида неисправности . Формула изобретения 1. Устройство для сопряжения по авт. св. № 736086, отличающ е.е с я тем, что, с целью повышения достоверности обмена информацией в устройство введены два регистра не исправности, три элемента ИЛИ, блок элементов ИЛИ и триггер неисправност передачи, причем выход триггера.неисправности передачи соединен с трет им входом блока управления обменом, а вход - со BTOjxjM выходом блока кон троля по модулю, третий и четвертый выходы которого соединены соответст.венно с первым и вторым входами перв го регистра неисправности,четвертый вход блока контроля по модулю соединен с выходом блока элементов ИЛИ, входы которого соединены с четвертым выходами соответствующих подканалов абонента, первый и второй выходы пер вого регистра неисправности соединены соответственно с п;атым входом бло ка управления обменом и с шестым вхо дом блока управления обменом и пятыми входами подканалов абонента, третий выход первого регистра неисправности соединен с первым дополнительным входом коммутатора информации, третий, четвертый и пятый входы - со ответственно с выходами первого, вто рого и третьего элементов ИЛИ, группы входов КОТО1ХДХ соединены соответственно с пятыми, шестыми и седьмыми выходами подканалов абонента, восьмые выходы которых подключены к груп пе входов второго регистра неисправности , выход которого подключен ко второму дополнительному входу коммутатора информации, шестые входы подканалов абонента соединены с седьмым выходом блока синхронизации, пятый выход регистра .обмена соединен с шестым вькодом блока управления обменом. 2. Устройство по п. 1, отличающееся тем, что подканал абонента содержит регистр служебных сигналов,первые вход и выход которого подключены соответственно к пер вьм выходу и входу узла управления, вторые вход и .выход - соответственно к первым управлякицему входу и выходу подканала и через первый триггер неисправности к пятому выходу подканала, а третий вход - к первому выходу узла контроля подканала, первые и вторые входы и выходы регистра обмена подканала соединены соответственно с первыми выходом и входом коммутатора типа передачи и четвертым входом и вторым выходом подканала, второй и третий входы узла управления соединены соответственно с выходом первого элемента И и шестым вхо-. дом подканала, а второй выход через триггер готовности - с первым выходом подканала, первый вход первого элемента И соединен с третьим входом подканала, а второй выход с выходом элемента ИЛИ, первый и второй входы которого являются соответственно первым и вторым входами подканала, вторые вход и выход коммутатора типа передачи являютс.я соответственно информационными входом и выходом канала, третий вход соединен с третьим выходом узла управления, четвертый - восьмой выходы которого подключены соответственно к третьему входу регистра обмена подканала, третьему выходу подканала, первому входу узла контроля подканала, первому входу второго элемента И, и четвертому выходу подканала, вторые вход и выход узла контроля подканала соединены соответственно с третьим выходом и четвертым входом комлутатора типа передачи, а третий и четвертый выходы соответственно через второй и третий триггеры неисправности с шестым и седьмым выходами подканалов , второй вход и выход второго элемента И являются соответственно пятым входом и восьмым выходом подканала, 3. Устройство по п. 1, отличающееся тем, что блок управления обменом содержит группу элементов И., первые входы которых соединены соответственно с третьим, четвертым и пятым входами е5лока, узел постоянной памяти, первый вход и выход которого соединены соответственно с шестым входом и четвертым выходом блока, BTOfftae вход и выход - соответственно со вторыми входим блока, вторые вход и выход - соответственно со BTOpbiN; входом и выходом блока, а третьи выход и вход - соответственно с пятым выходом блока и выходом дешифратора адреса микрокоманд, вход которого через счетчик адреса микрокоманд подключен к первому выходу модификатора адреса микрокоманд, первым входом соединенного с четвертым выходом узла постоянной памяти, а вторыми входом и выходом - соответственно с первым входом и выходом блока, вторые входы элементов И группы соединены со вторым входом блока.

а выходы соответствующих элементов И группы подключены к первому и второму выходам блока.

4.Устройство пп. 1 и 2, отличающееся тем, что управления подканала содержит постоанную память, группа выходов которой соединена соответственно с первым восьмым выходами узла, вход постоянной памяти соединен через дешифратор адреса микрокоманд с выходом счетчика адреса микрокоманд, а выход - с входом модификатора адреса микрокоманд, группа входов которого подключена соответственно к первому третьему входам узла, а выход - к входу счетчика адреса микрокоманд.

5.Устройство по пп. 1 и 2, о тличающееся тем, что узел

контроля Подканала содержит триггер тестового режима, вход и выход которого соединены соответственно с первыми входом и выходом узла, генератор кодов и регистр контроля, входы которого подключены к первому входу узла, а выходы -соответственно ко второму и четвертому выходам узла, и счетчик сдвигов, два входа и выход которого соединены соответственно с

0 первым и вторьм входами и третьим выходом узла.

Источники информации, принятые во внимание при экспертизе

5

1. Авторское свидетельство СССР 736086, кл. G 06 F 3/04, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1978 |

|

SU813401A2 |

| Устройство для сопряжения | 1984 |

|

SU1166126A2 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Устройство для сопряжения | 1978 |

|

SU809139A2 |

| Устройство для сопряжения | 1978 |

|

SU736086A1 |

| Устройство для сопряжения | 1979 |

|

SU840868A2 |

| Устройство для сопряжения | 1980 |

|

SU947849A1 |

| Устройство для сопряжения процессоров обмена с внешними устройствами | 1984 |

|

SU1257650A1 |

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

Фиг.

(.л

42

Ч «4Ч| «У/

фиъЛ к1в к 17

к26.

к27

azJ

{яп9

от 10

г

fn

втЗ ц9

ч-У-I

±3

ч

SS

Фиь.6

otnil

к 29

К 2 кгз

KfS

фиг. 7

к6

Ki

-4

sy

н28

Фиг.д

Авторы

Даты

1982-05-07—Публикация

1980-06-23—Подача