(54) СИСТЕМА СТАБИЛИЗАЦИИ ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь интервалов времени в цифровой код | 1984 |

|

SU1255984A2 |

| Преобразователь кода в длительность задержки сигнала | 1985 |

|

SU1287292A1 |

| Устройство задержки импульсов | 1980 |

|

SU917326A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

| Цифровой фазометр | 1983 |

|

SU1128187A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство управления скоростью дискового носителя информации | 1986 |

|

SU1455361A1 |

| Устройство поиска псевдослучайной последовательности | 1991 |

|

SU1788592A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

Изобретение относится к радиоэлектронным система с время-импупьсным представлением информации, в частности к радиоэлектронному оборудованию навигационных радиома5псов, а также к аппаратуре контроля бортовых измерителей дальности и предназначено для стабилизации задержки в тракте аппаратуры контроля, а также для формирования временных интервалов между импупьсамн, несу- Q шими передаваемую информацию.

Известно цифровое устройство для формирования задержки импупьсов, содержащее тактовый генератор, выход которого .. соединен с первым входом логического блока, второй вход которого соединен с источником импульсов запуска, выход по гического блока подключен к входу двоичного счетчика, выходы разрядов кото- м рого соединены с первыми входами блока сравнения, вторые входы которого подктб чены к выходам соответствующих разрядов запоминающего регистра, а выход

блока Сравнения соединен, с выхоДом уотройства l,

I Однако уст йств6 имеет недостаточную точность.

Известно устройство задержки, содер- . жащее последовательно соединенные первый блок преобразования, блок регулиру емой задержки, второй блок преобразова:ния, выход которого подключен к выходу устройства и к первому входу триггера, второй вход Которого соединен с вхогдом первого блока преобразования и входом устройства, а выход указанного триггера подключен к первому входу дифференцирующего блока и первому входу счетчика, второй вхсд которого соединен с выходом кварцев( генераягора, а выход указанного счетчика подключен к второму входу дифференпирукяцего блока,выхёй котсфсйго подсоединен к :управлякхцему входу бпснка регушруемой задержки .

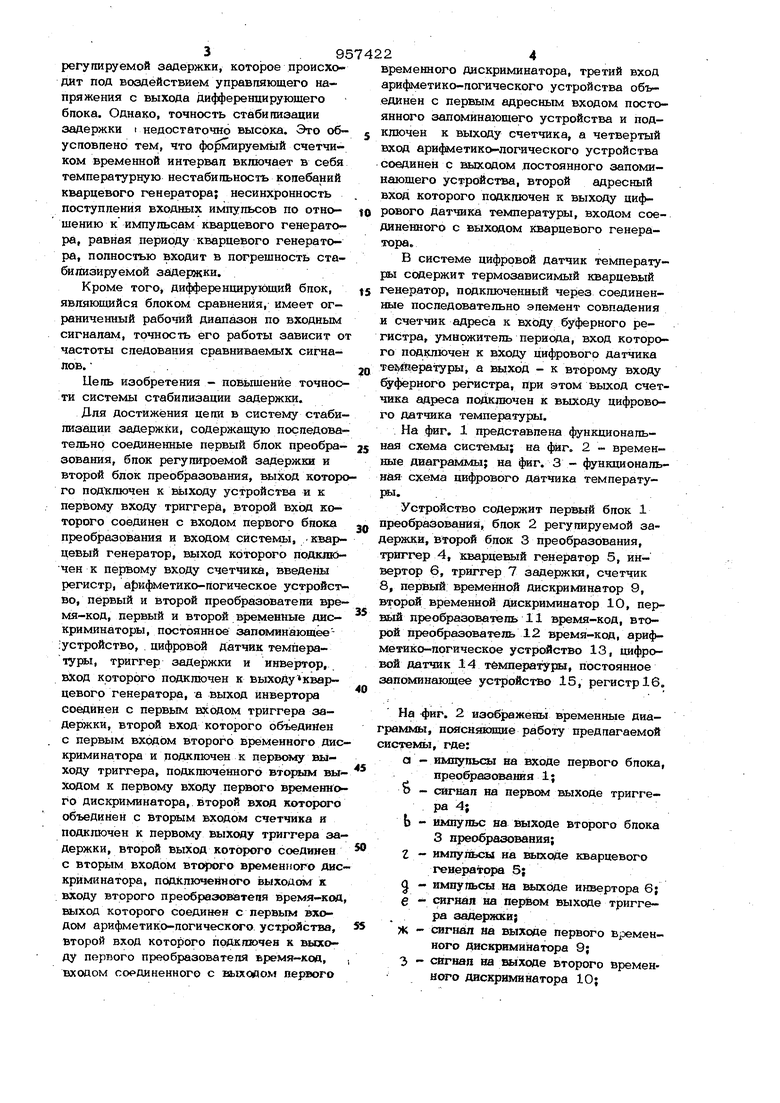

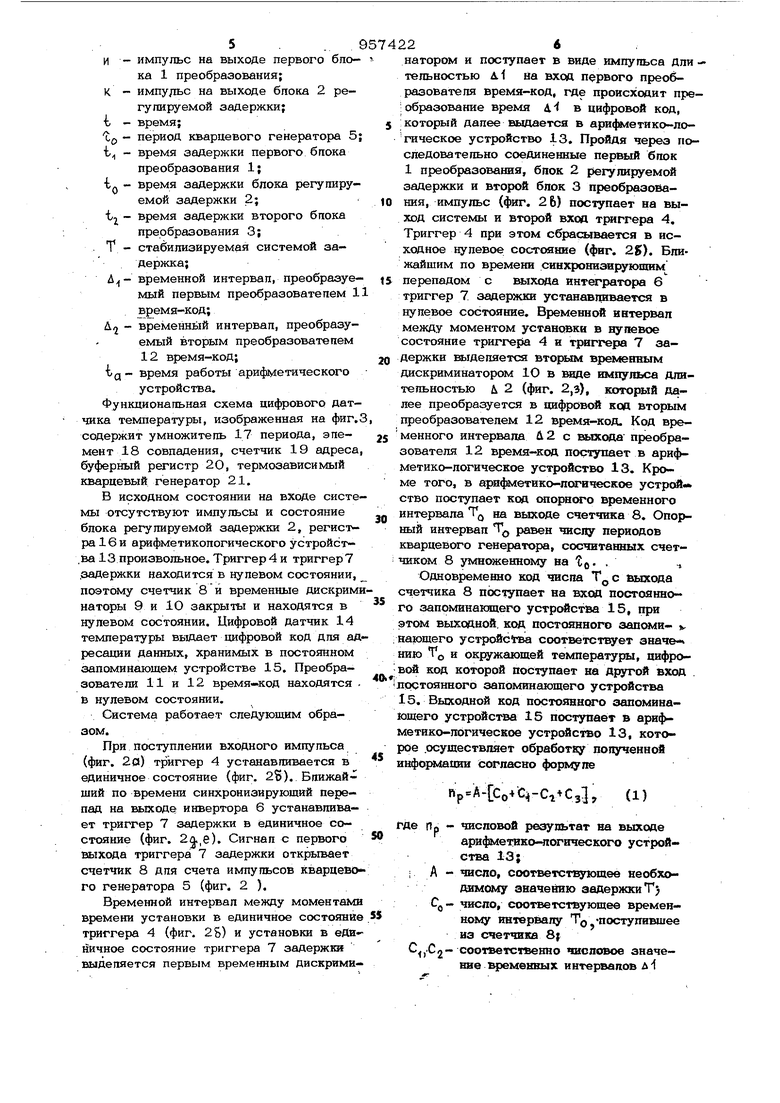

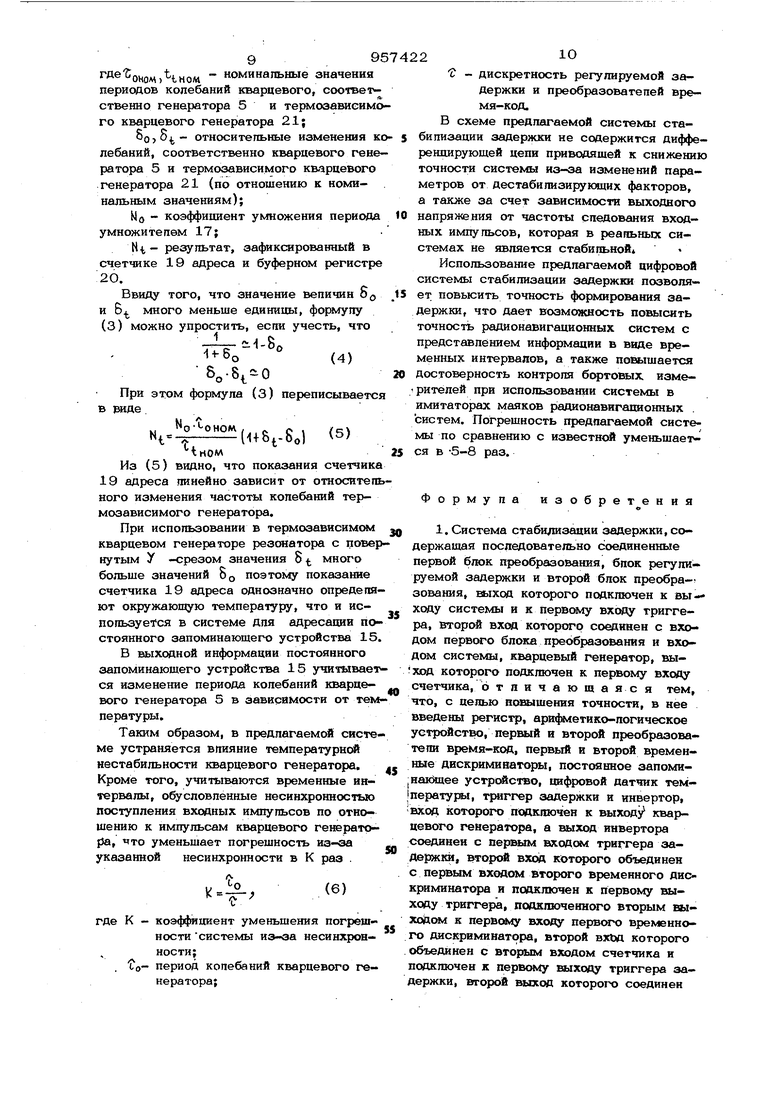

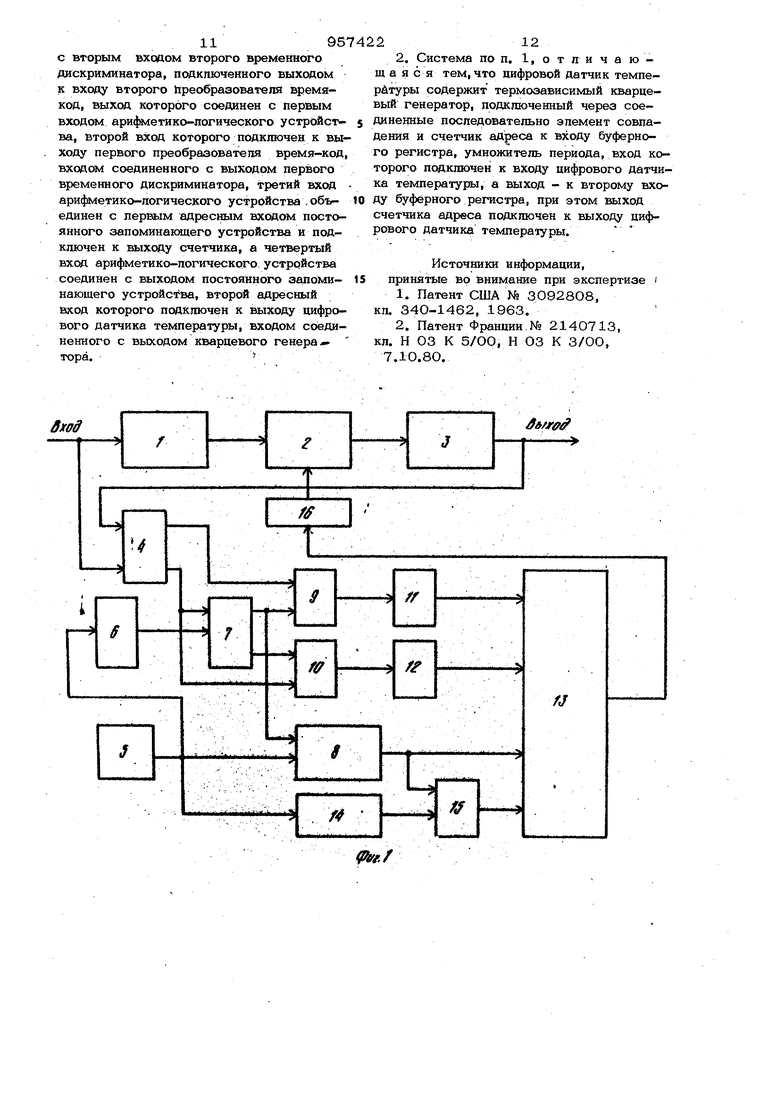

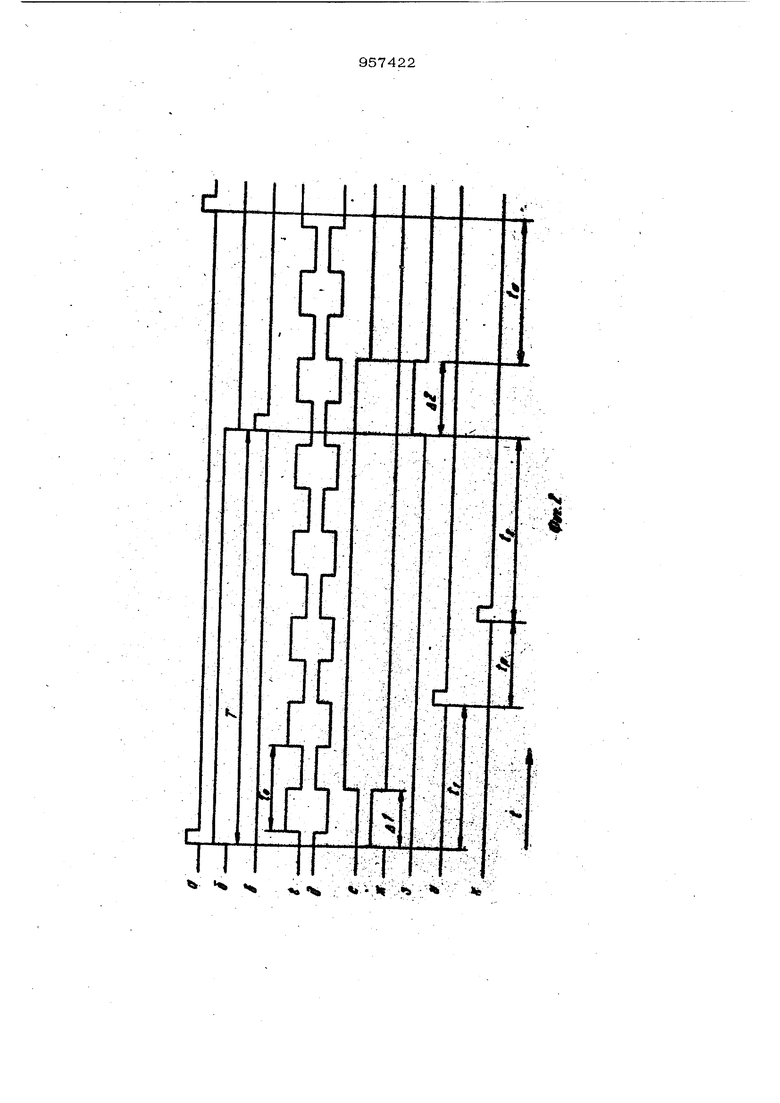

В устройстве производится стабипиза- шя задержки входных импульсов в блоках преобразования за счет изменения регулируемой задержки, KOTOJaoa происходит под воздействием управляющего напряжения с выхода дифференцирующего бпока. Однако, точность стабилизации задержки (недостаточно высока. Зто обусповпено тем, что формируемь1Й счетчиком временной интервал включает в себя температурную нестабильность колебаний кварцевого генератора; несинхронность поступления входшзгх импульсов по отношению к импульсам кварцевого генерато ра, равная периоду кварцевого генератора, полностью входит в погрешность стабилизируемой задержки. Кроме того, дифференцирующий блок, являющийся блоком сравнения, имеет ограниченный рабочий диапазон по входным сигналам, точность его работы зависит о частоты следования сравниваемых сигналов. . Цель изобретения - повьпиенйе точности системы стабилизации задержки. Для достижения цели в систему стабилизации задержки, содержаи гю последовательно соединенные первый блок преобразования, блок регулирремой задержки и второй блок преобразования, выход котор го под слючен к вь1ходу устройства и к первому входу триггера, второй вход которого соединен с входом первого блока преобразования и входом системы, кварцевый генератор, выход которого подключен к первому входу счетчика, введены регистр, а{зифметико-Логическое устройст во, первый и второй преобразователи вре мя-код, первый и второй временные дискриминаторы, постоянное запоминающее:устройство, цифровой Датчик температуры, триггер задержки и инвертор, вход которого подключен к выхоДу кварцевого генератора, а выход инвертора соединен с первым входом триггера задержки, второй вход которого объединен с первым входом второго временного дис криминатора и подключен к первому выходу триггера, подключенного вторым вы ходом к первому входу первого временно го дискриминатора, второй вход которого объединен с вторым входом счетчика я подключен к первому выходу триггера за держки, второй выход которого соединен с вторым входом вто}юго временного дис криминатора, подключенного выходом к входу второго преобраэоватевя время-код выход которого соединен с первым входе арифметико-логического устройства, второй вход которого подключен к выходу первого преобразователя время-код, входом соединенного с выходом первого Временного дискриминатора, третий вход арифметико-логического устройства объединен с первым адресным входом постоянного запоминающего устройства и подключен к выходу счетчика, а четвертый вход арифметико-логического устройства соединен с выходом достоянного запоминающего устройства, второй адресный вход которого подключен к выходу цифрового датчика температуры, входом соединенного с выходом кварцевого генератора. В системе цифровой датчик температуры содержит термозависимый кварцевый генератор, подключенный через соединенные последовательно элемент совпадения и счетчик адреса к входу буферного регистра, умножитель периода, вход которого подключен к входу цифрового датчика тешературы, а выход - к второму входу буферного регистра, при этом выход счетчика адреса подключен к выходу цифрового датчика температуры. На фиг. 1 представлена функциональная схема системы; на фиг. 2 - временные диаграммы; на фиг. 3 - функциональная схема цифрового датчика температуры. Устройство содержит первый блок 1 преобразования, блок 2 регулируемой задержки, второй блок 3 преобразования, триггер 4, кварцевый генератор 5, инвертор €, триггер 7 задержки, счетчик S, первый временной дискриминатор 9, второй временной Дискриминатор 1О, первый преобразоватешь 11 время-код, второй преобразователь 12 время-код, арифметико-логическое устройство 13, цифровой датчик 14 температуры, постоянное запоминающее устройство 15, регистр 16. На фиг. 2 изображены временные диаграммь, поясняющие работу предлагаемой системь, где: а - импульсы на входе первого блока, преобразования 1; о - сигнал на первом выходе триггера 4; Ь - импульс на выходе второго блока 3 преобразования; г - импульсы на вькоДе кварцевого генератора 5; - импупьсы на выходе инвертора 6; е - сигнал на первом выходе триггера задержки; Ж - сигнал на выходе первого временного дискриминатора 9; 3 - сигнал на выходе второго временното дискриминатора 10; 5.. 9574 - импульс на выходе первого бло- ка 1 преобразования; К - импудьс на выходе блока 2 регулируемой задержки; t - время; to - период кварцевого генератора 5; t - время задержки первого блока преобразования 1; i- - время задержки блока регулируемой задержки 2; i, - время задержки второго бпока преобразования 3; Т - стабилизируемая системой задержка; временной интервал, преобразуе- tS мый первым преобразователем 11 время-код; Д - временный интервал, преобразуемый вторым преобразователем 12 время-код; tg- время работы арифметического устройства. Функдионапьная схема цифрового датчика температуры, изображенная на фиг. содержит умножитель 17 периода, эпемент 18 совпадения, счетчик 19 адреса буферный регистр 20, термозависимый кварцевый генератор 21. В исходном состоянии на входе систе мы отсутствуют импульсы и состояние блока регулируемой задержки 2, регист ра 16 и арифметикологического устройст.ва 13 произвольное. Триггер 4 и триггер 7 .задержки находится в нулевом состоянии, поэтому счетчик 8 и временные дискрим наторы 9 и 10 закрыты и находятся в нулевом состоянии. Цифровой датчик 14 температуры выдает цифровой код Для ад ресации данных, хранимых в постоянном запоминающем устройстве 15. Преобразователи 11 и 12 время-код находятся в нулевом состоянии. Система работает следующим образом. При поступлении входного импульса (фиг. 2а) триггер 4 устанавливается в единичное состояние (фиг. 2S). Бяижайший по времени синхронизирующий перепад на ш 1ходе инвертора 6 устанавливает триггер 7 задержки в единичное состояние (фиг. 2,е). Сигнал с первого выхода триггера 7 задержки открывает счетчик 8 дпя счета имлупьсов кварцево го генератора 5 (фиг. 2 ). Временной интервал между моментам времени установки в единичное состояни триггера 4 (фиг. 25) и установки в еди ничное состояние триггера 7 задержки выделяется первым временным дискрими 5 10 26 натором и поступает в виде импупьса Дпи - тельностью Д.1 на вхоа первого преобразователя время-код, где происходит пре: образование время Д в цифровой код, который далее выдается в ари(|яу1етико-ло- гическое устройство 13. Пройдя через последовательно соединенные первый блок 1 преобразования, бпок 2 регулируемой задержки и второй бпок 3 преобразоваНИН, импульс (фиг. 26) поступает на выход системы и второй вход триггера 4. Триггер 4 при этом сбрасывается в исходное нулевое; состояние (фиг. 2$). Ближайшим по времени синхронизирующим перепадом с ш 1хода интетратора 6 триггер 7 задержки устанавливается в нулевое состояние. Временной интервал между моментом установки в нулевое состояние триггера 4 и триггера 7 задержка выделяется втором временным дискриминатором 1О в 1тде импульса длительностью & 2 (фиг. 2,з), который далее преобразуется в цифровой код вторым преобразователем 12 время-код. Код временного интервала U2 с выхода преобразователя 12 время-код поступает в арифметико-логическое устройство 13. Кроме того, в арифметико-погическое устрой- ство поступает код сшорвото временного интервала TQ на выходе счетчика 8. Опорный интервал равен числу периодов кварцевого генератора, сосчитанных счетчиком 8 умноженному на to- ., Одновременно код числа Т с выхода счетчика 8 поступает на вход постоянного запоминающего устройства 15, при этом выходной, код постоянного запоми- v нающего устройс а соответствует значе н нию и окружающей температуры, цифровой код которой поступает на другой вход . лрстоянного запоминающего устройства 15. Выходной код постоянного запоминающего устройства 15 поступает в ари4 метико-логичесЕое устройство 13, которое .осуществляет обработку полученной инфо ялации согласно формуле , где Пр - числовой результат на выходе арифметвко-логвческого устройства 13; i А - число, соответствующее необходимому значению задержки Т) CQ- число, соответствующее временному интервалу TQ -поступившее из счетчика 8| .Cj- соогветственно чнсловое значение временных интервалов Д{ и д 2 j поступившее с выходов прюобразователей время-код 11 и 12; Cj - числовое значение поправки из постоянного запоминающего уст ройства 15. Результат вычисления по формуле (1) из арифметико-логического устройства 13 передается в регистр 16, выходной сигнап которого управляет блоком 2 регулируёмой задержки. Регулируемая задержка изменяется на величину (Пр) lnp4) + Up), -(2) рде 1 - дискретность регулируемой задержки;й,Т - отклонение задержки Т от заданного значения; Д - отклонение задержки первого блока 1 преобразования от номинального значения; отклонение задержки второго блока 3 преобразования от номинального значения; д1р- отклонение задержки блока регу лируемой задержки от номиналь ного значения. Знак импульс в первой части равенства (2) означает, что изменение регулируемой задержки направлено противоположно направлению изменения задержки Т, Изменения задержки Т являются мед ленно изменяющимися во времени, так как обусловлены изменениями из-за старения элементов и изменение окружающей температуры. Поэтому число Пр в регистре 16 в установившемся режиме является неизменным. При этом суммарная задерж ка первого блока 1 преобразования блока 2 регулируемой задержки и второго блока преобразования равна заданному зн чению задержки Т . С прихшом каждого последующего импульса на вход системы ош1са гаая работа систекил повторяется. Время to, (фиг. 26) для работы арифметико-логического устройства 13 Выбирается в соответствии с его быстродействием. Блок 2 регулируемой задержки может быть реализован в виде цифровой линии задержки, управляемой цифровым кодом. Преобразователи 11 и 12 время-код реализуется, например, в виде рециркуляционного преобразователя. Временные дискриминаторы 9 и 10 реализуются на логических эпементэх ин тегральных микросхем серии 130 типа 13О ЛГМ. Триггер 4, триггер 7 задержки, инвертор 6, счетчик 8, регистр 16, арифметико-логическое устройство 13 реализуются на элементах интегральных микросхем серии 133, 136, 130, К 589 по Известным схемам. Поставленное запоминающее устройство 15 реализуется на интегральных микросхемах типа 558РР1. Реализация блоков, преобразования зависит от их конкретного назначения. Цифровой датчик температуры реализуется на интегральных микросхемах серий 133, 13О по схеме, приведенной на фип,3. В исходном состоянии счетчик 19 адреса -находится в нулевом состоянии, элемент 18 совпадения закрыт. Частота колебаний термозависимого кварцевого генератора соответствует. температуре окружающей среды. Цифровой датчик температуры работает следующим образом. Умножитель 17 периода представляющий собой двоичный счетчик, производит умножение периода кварцевого генератора 5 на величину MQ, При этом , на выходе умножителя 17 периода форми руются импупьсы, длительность которых равна (MO-to). На время действия выходного импульса умножителя 17 периода элемент 18 совпадения открывается и на его выход поступают импульсы от тер- . мозависимого кварцевого генератора 21, которые подсчитываются счетчиком 1-9 адреса. После окончания выходного импульса умножителя 17 периода элемент 18 совпадения закрывается, а счетчик 19 адреса остается в состоянии, соответствующем числу импульсов термозависимого кварцевого генератора 21 с периодом , прощедших через элемент 18 совпадения. Затем в момент окончания выходного импульса умн.ожителя 17 периода число из счетчика 19 адреса переписывается в буферный регистр 2О, после чего счетчик 19 адреса сбраысвается в нулевое состояние (цепи сброса счетчика 19 не показаны). С приходом следующего выходного импульса умножителя периода процесс формирования адреса повторяется. Поскольку в установивщемся режиме температура окружающей среды постоянна, в буферном регистре 2О хранится число, соответствующее этой температуре. Работа цифрового датчика температуры описывается следующим выражением: .o- OHowll--St) ) 99 )ЧнОМ - номинальные значения периодов колебаний кварцевого, соответственно генератора 5 и термозависимо го кварцевого генератора 21; o,5i.- относительные изменения к лебаний, соответственно кварцевого гене ратора 5 и термозависимого кварцевого генератора 21 (по отношению к номинальным значениям); M(j - коэффициент умножения периода умножителем 17; Nt- результат, зафиксированный в счетчике 19 адреса и буферном регистре 20. Ввиду того, что значение величин о и Б много меньше единицы, формулу (3) можно упростить, если учесть, что . 5,. При этом формула (З) переписываетс в риде О-OHOW (U8t-8o) 5) Из (5) видно, что показания счетчика 19 адреса линейно зависит от относител ного изменения частоты колебаний термозависимого генератора. При испошьзовании в термозависимом кварцевом генераторе резонатора с повер нутым У -срезом значения S t много больше значений Б о поэтому показание счетчика 19 адреса однозначно определя ют окружающую температуру, что и используется в системе для адресации по стоянного запоминающего устройства 15 В выходной информации постоянного запоминающего устройства 15 учитывает ся изменение периода колебаний кварцевого генератора 5 в зависимости от тем пературы. Таким образом, в предлагаемой систе ме устраняется влияние температурной нестабильности кварцевого генератора. Кроме того, учитываются временные интервалы, обусловленные несинхронностью поступления входных импульсов по отношению к импульсам кварцевого генератр{За, что уменьшает погрешность иа-ва указанной несинхронности в К раз . -где К - коэф({ициент уменьшения погрешности системы из-за несинхронности;Го- период колебаний кварцевого генератора;2 - дискретность регулируемой задержки и преобразователей время-код. В схеме предлагаемой системы стабипизации задержки не содержится дифференцирующей цепи приводящей к снижению точности системы из-за изменений параметров от дестабилизирующих факторов, а также за счет зависимости выходного напряжения от частоты следования входных импульсов, которая в реальных системах не является стабильной « Использование предлагаемой цифровой системы стабилизации задержки позволяет повьюить точность формирования задержки, что дает возможность повысить точность радионавигацио шых систем с представлением информации в виде временных интервалов, а также повышается достоверность контроля бортовых измеФителей при использовании системы в имитаторах маяков радионавигационных . систем. Погрешность предлагаемой системы по сравнению с известной уменьшается в -5-8 раз. Формула изобретения 1. Система стабилизации задержки, содержащая последовательно соединенные первой блок преобразования, блок регулируемой задержки и второй блок преобразования, выход которого подключен к выходу системы и к первому входу триггера, второй вход которого соединен с входом первого блока преобразования и входом системы, кварцевый генератор, выхор. которого подключен к nejffiOMy входу счетчика, 6 тличающаяся тем, что, с целью псшышения точности, в нее введены регистр, ари({ыетико-логическое устройство, перыцй и второй преобразователи время-код, первый и второй временные дискриминаторы, постоянное аапоминакйцее устрсйство, цифровой датчик температуры, триггер задержки и инвертор, вход которого подключен к ы 1ходу кварцевого генератора, а выход инвертора соединен с первым входом триггера задержки, второй вход котсфого объединен с первым вхсмом второго временного дискриминатора я подключен к первому выходу триггера, подключенного вторым выхоДом к первому входу первсяч временного дискриминатора, второй вхьа которого объединен с вторым входом счетчика и подключен к первому выходу триггера задержки, второй выход которого соединен

с вторым входом второго временного дискриминатора, подключенного выходом к входу второго йреобразователя времякод, выход которого соединен с первым входом ари4 1етико-погического устройства, Второй вход которого подкгаочен к выходу первого преобразователя время-код входом соединенного с выходом первого временного дискриминатора, третий вход арифметико-логического устройства .обт единен с первым адресным входом постоянного аапоминакицего устройства и подключен к выходу счетчика, а четвертый вход арифметико-логического устройства соединен с выходом постоянного запоминающего устройства, второй адреснзый вход которого подключен к выходу цифрового датчика температуры, входом соединенного с выходом кварцевого генера. тора.

Лг%

/

/8

f

Источники информации, принятые во внимание при экспертизе

A/fff

ff

-5

//

тт

« % ч, ,

N

.;

S Ч|

v.viit: :/ /

Авторы

Даты

1982-09-07—Публикация

1981-01-04—Подача