Внеш. запцск.

Фиг.}

Изобретение относится к электроизмерительной технике и может быть использовано построения быстродействующих аналого-цифровых преобразователей (ALP) повышенной точности

Цель изобретения - повьшение точности и, увеличение быстродейств1- я.

На фиг. 1 приведена функционсшь- Н.ЗЛ схема устройства аналого-цифро - вого преобразования ; на фиг.. 2 . функционельная схема арифметико-логического устройства (АЛУ),

Устройство аналого-цифрового преобразования содержит АЦП ср. 1 п старших разрядов, регистр 2 памяти, АЛУЗ;, . выходной N-рязрядньш регистр 4, элемент 5 задержки усшштель 6 разности, АЦП, 7 младжнх разрядов, цифро- аналоговьш преобразовател.ь 8 (1.№), постоянное запоминающее устройство 9 (ПЗУ) j блок 10 управления,, цифровой сумматор 11, оперативное запошлнаю- ш,ее устройство 12 (ОЗУ) j переключатель 13, элемент ИЛИ 14, блок 15 фор- мкрования образдовьо: сигналов, вы- нолненньй на узле 16 задания р(,, блок 1 м источник 1В опорного напря

ние 12.

обнуляется содержимое ячеек ОЗУ

Рассмотрим работу устройства в ре жиме непосредственного преобразования входного сигнала на конкретном примере. Допустим, что число разрядов всего устройства, включая знаковый разряд, , число разрядов АЦП. 1

to п 4, 7 N - п + m 8(m 1, где m - число разрядов коррекции, см. известное устройство), а диапазон U (-1,024В) - (+1,024В). Так же, как и в известном устройстве,

15 здесь в качестве узла 8 используется грубый быстродействующий интегральный ЦАП (к примеру 1118 ПА1). Инструментальная погрешность такого ЦАП значительна и в несколько раз превы20 шает требования, предъявляемые к узлу 8 в составе устройства аналого-цифрового преобразования,

Допустим, что значения разрядных уровней ЦАП 8 с учетом их инструмен25 тальных погрешностей равны: U, 128- 3 125 мВ; а 256 + 2 258 мВ; t ns 512 - 4 508 мВ; и„ -1024 +

жекия„ Узел первом

16 задания режимов

эй: fi

19. втором 20,

и

переключателях„

Блок 17 выполнен на элементе

22g счетчике 23 имтс льсов, элементе

И 24,

15 и генераторе 26

rj триггере

Й1.11ТУЛЬСОВ .

Блок 10. управления состоит из трех последовательно соединенных злементов задержки выходы .которых ;-:; вход первого из них через формиро- Е ятели -с шульсов .п:о;;(ключены к выхо дам устройства 10 управления,

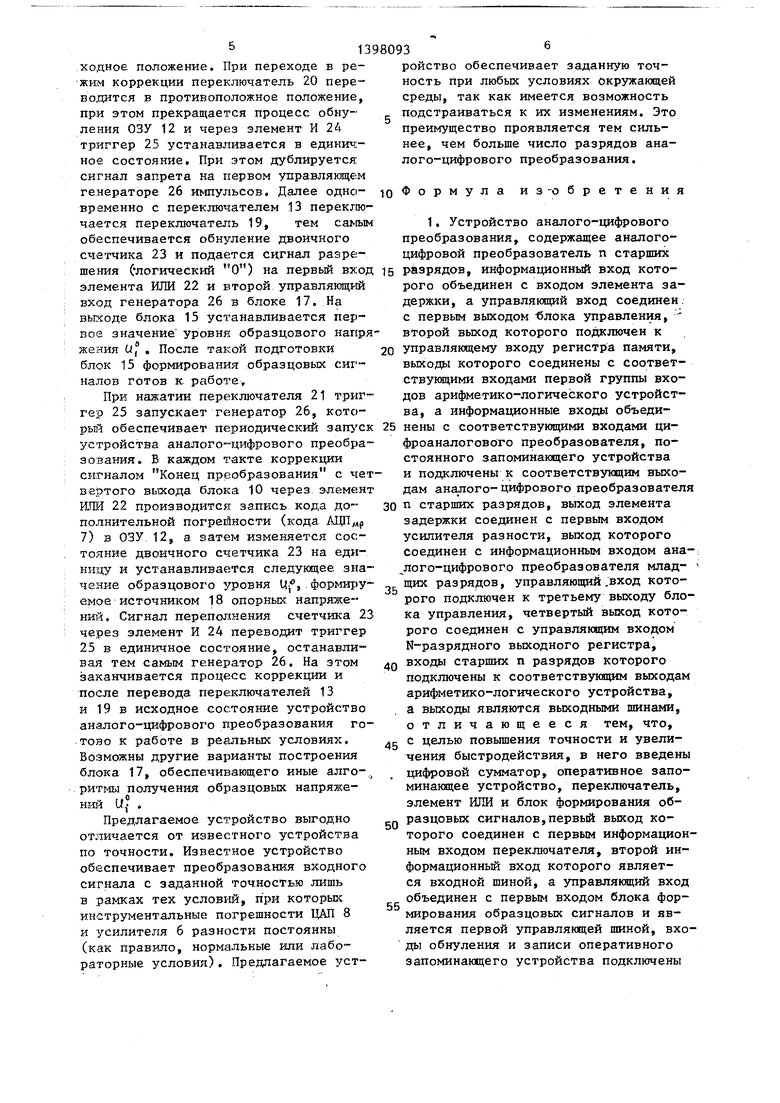

АЛУ 3 выполнено на элементе ИЛИ 27, элементе И 28 и цифровом сумматоре- вычитателе 29.,

Устройство работает в режиме кор- 1:1екцни нелине йности характеристики квантования и в режшме непосредственного преобразования входного сигнала U,. Б первом режиме участвуют все устройства во-зтором - все, за исключением блока 15 формирования образцовых сигналов, причем переключатель 13 устанавливается в положение И, при котором Ц подается на вход А1ДП 1 с:ч:гкалы Запись и Внутр. запуск с генератора 2.6 импульсов не формиру- гатся, а с помощью сигнала Обнулекч

+ 4 -1020 мВ, значения всех остальных уровней ДАЛ 8 определяются линей- 3D ной комбинацией разрядных уровней выполнен (смещение нуля усилителя 6 разности третьем считаем равным нулю).

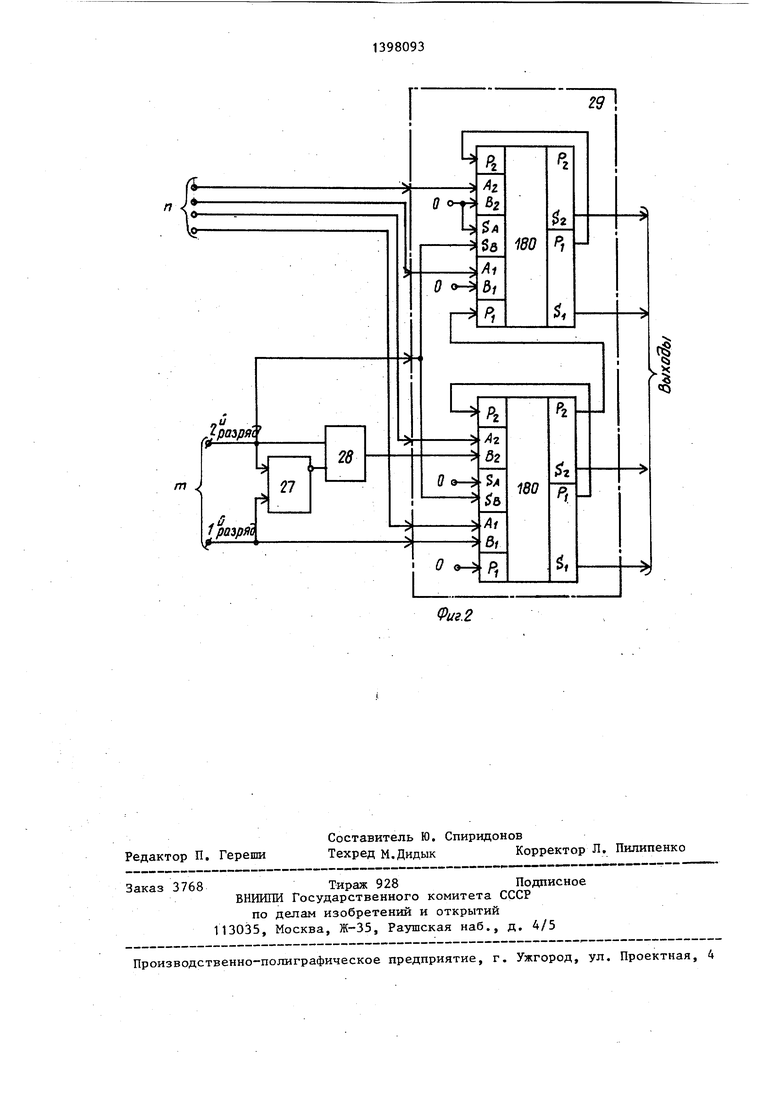

На этапе изготовления и настрой- ИЛК ки устройства, как и известного уст- gr ройства, инструментальные погрешности ДАЛ 8, присущие каждому выходному уровню, определяются экспериментально при нормальных условиях и записьшаются в цифровой форме с уче- jQ том 3Ha ka в ячейки ПЗУ 9. Адресом

каждой ячейки ПЗУ 9 является соответствующий код АЦП jp 1 (табл. 1 сос45

50

55

тавлена для положительного входного сигнала U).

Пусть y 640 мВ. После стробиро- вания АДП 1 сформируется код +101,, который преобразуется с помощью ЦАП 8 в компенсирующее напряжение, равное , 125 + 508 633 мВ. Разностный сигнал Uj, 640 - 633 7 мВ, установившийся на выходе усилителя 6 разности, после стробирова- ния 7 преобразуется в код +0000111 (+7 мВ). По коду +101 из ячейки ПЗУ 9 с этим адресом производится выборка кода основной погрешности (см. табл. О, равного - 111 (-7 мВ), который складывается в циние12.

обнуляется содержимое ячеек ОЗУ

Рассмотрим работу устройства в режиме непосредственного преобразования входного сигнала на конкретном примере. Допустим, что число разрядов всего устройства, включая знаковый разряд, , число разрядов АЦП. 1

п 4, 7 N - п + m 8(m 1, где m - число разрядов коррекции, см. известное устройство), а диапазон U (-1,024В) - (+1,024В). Так же, как и в известном устройстве,

здесь в качестве узла 8 используется грубый быстродействующий интегральный ЦАП (к примеру 1118 ПА1). Инструментальная погрешность такого ЦАП значительна и в несколько раз превышает требования, предъявляемые к узлу 8 в составе устройства аналого-цифрового преобразования,

Допустим, что значения разрядных уровней ЦАП 8 с учетом их инструментальных погрешностей равны: U, 128- 3 125 мВ; а 256 + 2 258 мВ; t ns 512 - 4 508 мВ; и„ -1024 +

кч

тавлена для положительного входного сигнала U).

Пусть y 640 мВ. После стробиро- вания АДП 1 сформируется код +101,, который преобразуется с помощью ЦАП 8 в компенсирующее напряжение, равное , 125 + 508 633 мВ. Разностный сигнал Uj, 640 - 633 7 мВ, установившийся на выходе усилителя 6 разности, после стробирова- ния 7 преобразуется в код +0000111 (+7 мВ). По коду +101 из ячейки ПЗУ 9 с этим адресом производится выборка кода основной погрешности (см. табл. О, равного - 111 (-7 мВ), который складывается в цифровом сумматоре 11 с кодом А1Щд,р 7: 111 + 0000111 -fOOOOOO. При это выходной код всего устройства соответствует входному сигналу 640 мВ, т.е. +101000000.

Однако, при работе устройства (и известного устройства) в реальных условиях (отличных от нормальных) появляется дополнительная составляющая инструментальной погрешности ЦАП 8 и усилителя 6 разности. Поэтому коррекция с помощью ПЗУ 9 теряет эффективность, Тое. не полная компенсация погрешности и в резуль- тате значительно (в несколько раз) возрастает общая погрешность аналого-цифрового преобразования.

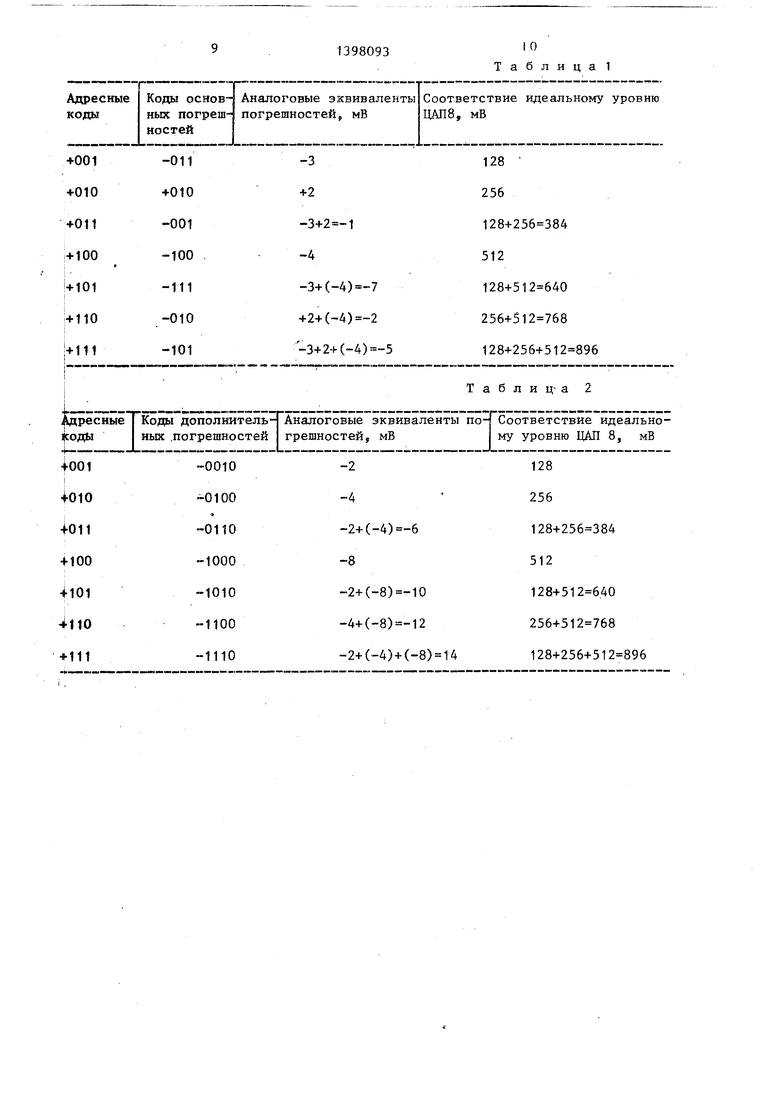

Для коррекции дополнительной составляющей инструментальной погрешности в устройство введено ОЗУ 12, в ячейки которого в режиме коррекции нелинейности характеристики квантования заносятся коды этой погрешности, В рамках условий рассмотренного вьш1е примера можно допустить, что разрядные уровни ЦАП U ;

Lj, и U при наличии дополнительной погрешности изменились и стали равны: (J 125 - 2 123 мБ; U 258 - 4 254 мВ; L/ 508 - 8 - - 500 мВ; -1020 + 16 -1004 мВ (изменение исходного значения смещен нуля усилителя 6 разности положим равным нулю). В ячейках ОЗУ 12 при этом должны храниться коды дополнительной погрешности в соответствии с табл. 2.

При преобразовании входного сигнала U 640 мВ получаются соответственно коды: 1: +101; АЦП.

(соответствующие разност7: +0010001

ному сигналу -)(-( uL -(123 + 500) 17 мВ) ; код ПЗУ9: -111 (см. табл. 1) и код ОЗУ 12: -1010 (табл. 2), После сложения кодов 7 ПЗУ 9 и ОЗУ 12 в цифровом сумматоре 11 получим код младших разрядов +0010001-111-1010 +0000000, а полный код аналого-цифрового преобразования при этом равен +1010000000, что соответствует LJ| 640 мВ,

Определение и запись в ячейки ОЗУ 12 кодов дополнительной погрешности производятся в режиме коррекции нелинейности характеристики квантования. В этот режим устройство перводится установкой переключателя 13

0934

положение К. После этого с выхода блока 15 формирования образцовых сигналов на вход 1 поступа10

ВТ ступенчатое напряжение (значения образцовых уровней напряжения выбираются равными значениям уровней идеального ЦАП8, а их количество зависит от вида корректируемой погрешности и задается конструкцией блока 17j например, для коррекции

погрешности смещения нуля устройства необходимо всего лишь одно образцовое напряжение, равное нулю, для

коррекции дифференциальной нелиней- но.сти - большее количество уровней) .

Установка очередного уровня образцового напряжения сопровождается разовым запуском устройства аналогоцифрового преобразования (сигнал

Внутр. запуск), формированием кода на выходе цифрового сумматора 11, численно равного значению дополнительной погрешности, и записью его (сигнал запись) в.ячейку ОЗУ 12, адрес которой соответствует коду МЩср 1 в данном такте коррекции. При поступлении сигнала Конец преобр. счет- вертого выхода блока 10 управления

разрешается установление следующего уровня образцового напряжения. После формирования последнего образцового напряжения происходит остановка работы блока 15.

Пример , Считаем, что на вход

устройства подано не входное, а i-e значение образцового напряжения ({ 640 мВ, .тогда в условиях влияния дополнительной погрешности на выходе

цифрового сумматора 11 получим код, равньй сумме кодов АЦП/ир 7, ПЗУ 9 и ОЗУ 12 (код ОЗУ 12 равен нулю, так как предварительно вно обнуляется), т.е. +0010001-111+0 +0001010. Этот

код соответствует с противоположным знаком дополнительной погрешности 10 мВ ( табл. 2), инверсию знака кода +1010 погрешности можно производить, например, при вьшолнении операции сложения в рабочем режиме или

непосредственно при записи кода в

ОЗУ 12. Затем полученньй код погрешности (+1011) записьшается в ячейку ОЗУ 12 с адресом +101, что соответ- ствует коду АЦП ср 1.

Блок 15 формирования .образцовых сигналов работает следукхцим образом.

Переключатели 19-21 в узле 16 задания режимов устанавливаются в ис

ходное положение;. При переходе в ре- жи:м коррекции переключатель 20 пере- во,цится в противоположное положение, при этом прекращается процесс обнуления ОЗУ 12 и через элемент И 24 триггер 25 устанавливается в единич:- ное состояние. При этом дублируется сигнал запрета на первом управлякзщем генераторе 26 импульсов. Далее одновременно с переключателем 13 переключается переключ 1тель 19, тем самым обеспечивается обнуление двоичного счетчика 23 и подается сигнал разр&ройство обеспечивает заданную точность при любых условиях окружающей среды, так как имеется возможность подстраиваться к их изменениям. Это преимущество проявляется тем сильнее, чем больше число разрядов аналого-цифрового преобразования.

Юформула из-обретения

держки, а управляющий вход соединен, с первым выходом лока управления, второй выход которого подключен к 20 управляющему входу регистра памяти, выходы которого Соединены с соответ- ствукщими входами первой группы входов арифметико-логического устройства, а информационные входы объеди1. Устройство аналого-цифрового преобразования, содержащее аналого- цифровой преобразователь п старших

щения ( логический О) на первый вход 15 разрядов, информационный вход кото- элемента ИЛИ 22 и второй управляющей рого объединен с входом элемента за- вход генератора 26 в блоке 17. На выходе блока 15 устанавливается первое значение уровня образцового напряжения U, После такой подготовки блок 15 формирования образцовых сигналов готов к. р 1ботеу

При нажатии переключателя 21 триггер 25 запускает генератор 26, кото- рьй обеспечивает периодический защ ск 25 нены с соответствующими входами ци- устройства аналого-цифрового преобра- фроаналоговбго преобразователя, постоянного запоминающего устройства и подключены к соответствующим выходам аналого- цифрового преобразователя 30 п старших разрядов, выход элемента задержки соединен с первым входом усилителя разности, выход которого соединен с информационным входом ана; лого-цифрового преобразователя млад-

чение образцового уровня U, формиру- 35 ™ Разрядов, управляющий .вход кото- емое источником 18 опорных напряже-

НИИ, Сигнал переполнения счетчшса 23 через элемент И 24 переводит триггер 25 в единичное состояние, останавли40

зования. В каждом такте коррекции сигналом Конец преобразования с четвертого выхода блока 10 через элемент ИЛИ 22 производится запись кода дополнительной погрейности (кода АЦП;л() 7) в ОЗУ 12, а затем изменяется состояние двоичного счетчика 23 на единицу и устанавливается следующее знавая тем самым генератор 26. На этом заканчивается процесс коррекции и

после перевода переключателей 13 и 19 в исходное состояние устройство аналого-цифрового гфеобразования готово к работе в реальных условиях. Возможны другие варианты построения блока 17, обеспечивающего иные алго-, получения образцовых напряжений U,- .

Предлагаемое устройство выгодно отличается от известного устройства по точности. Известное устройство обеспечивает преобразования входного сигнала с заданной точностью лишь в рамках тех условий, при которьос инструментальные погрешности ЦАП 8 и усилителя 6 разности постоянны (как правило, нормальные или лабораторные условия) . Предлагаемое уст45

50

55

рого подключен к третьему выходу блока управления, четвертый выход которого соединен с управляющим входом N-разрядного выходного регистра, входы старших п разрядов которого подключены к соответствующим выходам арифметико-логического устройства, а выходы являются выходными шинами, отличающееся тем, что, с целью повьш1ения точности и увеличения быстродействия, в него введены цифровой сумматор, оперативное запоминающее устройство, переключатель, элемент ИЛИ и блок формирования образцовых сигналов,первьй выход которого соединен с первым информационным входом переключателя, второй информационный вход которого является входной шиной, а управляющий вход объединен с первым входом блока формирования образцовых сигналов и является первой управляющей шиной, входы обнуления и записи оперативного запоминающего устройства подключены

ройство обеспечивает заданную точность при любых условиях окружающей среды, так как имеется возможность подстраиваться к их изменениям. Это преимущество проявляется тем сильнее, чем больше число разрядов аналого-цифрового преобразования.

формула из-обретения

держки, а управляющий вход соединен, с первым выходом лока управления, второй выход которого подключен к управляющему входу регистра памяти, выходы которого Соединены с соответ- ствукщими входами первой группы входов арифметико-логического устройства, а информационные входы объедиразрядов, информационный вход кото- рого объединен с входом элемента за-

нены с соответствующими входами ци- фроаналоговбго преобразователя, постоянного запоминающего устройства и подключены к соответствующим выходам аналого- цифрового преобразователя п старших разрядов, выход элемента задержки соединен с первым входом усилителя разности, выход которого соединен с информационным входом аналого-цифрового преобразователя млад-

5 ™ Разрядов, управляющий .вход кото-

0

5

0

5

рого подключен к третьему выходу блока управления, четвертый выход которого соединен с управляющим входом N-разрядного выходного регистра, входы старших п разрядов которого подключены к соответствующим выходам арифметико-логического устройства, а выходы являются выходными шинами, отличающееся тем, что, с целью повьш1ения точности и увеличения быстродействия, в него введены цифровой сумматор, оперативное запоминающее устройство, переключатель, элемент ИЛИ и блок формирования образцовых сигналов,первьй выход которого соединен с первым информационным входом переключателя, второй информационный вход которого является входной шиной, а управляющий вход объединен с первым входом блока формирования образцовых сигналов и является первой управляющей шиной, входы обнуления и записи оперативного запоминающего устройства подключены

соответственно к второму и третьему выходам блока формирования образцовых сигналов, второй и третий входы - которого являются соответственно второй и третьей управляющими шинами, а четвертый вход соединен с четвертым выходом блока управления, вход которого подключен к выходу элемента ИЛИ, первый вход которого соеди- йен с четвертым выходом блока формирования образцовЬк сигналов, а второй вход яйляется шиной Внешний запуск, входы N - п младших разрядов выходного Ы-раз15ядного регистра объе- динены с первыми информационными входами оперативного запоминающего устройства и подключены к соответ- ствукнцим N-n выходам младших разрядов цифрового сумматора, m входов второй группы входов арифметико-логического устройства объединены с соответствующими вторыми информационными входами оперативного запоминающего устройства и подключены к соответ- ствующим выходам m старших разрядов цифрового сумматора, первые N-n+m входов которого подключены к соответствующим выходам аналого-цифрового преобразователя младших разрядов, вторые входы соединены с соответствующими выходами постоянного запоминающего устройства, а третьи входы подключены к соответствующим выходам

выход источника опорного напряжения, входы которого соединены с соответствующими информационными выходами счетчика импульсов, вход обнуления которого объединен с первым управляющим входом генератора импульсов, первым входом элемента ИЛИ и подключен к выходу первого переключателя, первьй и второй входы которого объединены соответственно с первыми и вторыми входами второго и третьего переключателей и являются соответственно шинами логического нуля и единицы, выход второго ключа соединен с первым входом элемента И и является вторым выходом блока, третьим выходом которого является выход элемента ИЛИ, второй вход которого объединен со счетным входом счетчика импульсов и является четвертым входом блока, выход переполнения счетчика импульсов соединен с вторым входом элемента И, выход которого подключен к входу установки в 1 триггера, прямой выход которого соеди- нен с вторым управляющим входом генератора, а вход установки в О подключен к выходу третьего переключателя, выход генератора является четвертым выходом блока.

3, Устройство по п, 1, отличающееся тем, что арифметико- логическое устройство вьшолнено на

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2013863C1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1319279A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Многоточечный цифровой термометр | 1985 |

|

SU1268972A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1667246A1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2326494C1 |

Изобретение относится к электроизмерительной технике и может быть J /x , 0,, , Л использовано при построении точных быстродействующих аналого-цифровых преобразователей, Б устройство, содержащее АЦПср 1, регистр 2.памяти,. АДУ3, выходной регистр 4, элемент 5 задержки, усилитель 6 разности5 АЦПд;, 7, ЦАП 8, ПЗУ 9, блок 10 управления с, целью повьшения точности и быстродействия введены цифровой сумматор 11, ОЗУ 12, переключатель 13,.элемент ИЛИ 14 и блок 15 формирования образцовых сигналов. Повьшение точности достигается коррекцией дополнительной погрешности преобразования с введением поправки в цифровом виде, период дискретизации сокращается- благодаря исключению ряда узлов, следовательно, и задержек, вносимых ими. в процессе преобразования. Функциональные возможности расширяются за счет введения узлов, обеспечивающих режим самокоррекции устройства, 2 з,п, ф-лы, 2 шт., 2 табл. я о со 00

оперативного запоминающего устройства, элементе И, элементе ИЛИ и цифровом

адресные входы которого подключены к соответствующим выходам аналого-цифрового преобразователя п старших разрядов, второй вход усилителя разности соединен с выходом цифроанало- гового преобразователя, выход переключателя соединен с входом линии задержки.

2, Устройство по п. 1, отличающееся тем, что блок формирования образцовых сигналов вьшолнен на источнике опорного напряжения, первом, втором и третьем переключателях, элементе ИЛИ, счетчике импульсов, элементе И, триггере и генераторе импульсов, выход которого является четвертым выходом блока, первым, вторым и третьим входами которого являются соответственно управляющие входы первого, второго и третьего переключателей, а первым выходом 40

45

50

55

cyNj iaTope-вычитателе, первые информационные входы которого являются соответствующими входами первой груп пы входов арифметико-логического уст ройства, вход первого разряда вторы информационных входов цифрового сум матора-вычитателя объединен с первы входом элемента ИЛ№ и является перв входом второй группы входов арифмет ко-логического устройства, вход вто рого разряда вторых информационных входов цифрового сумматора-вычитатё ля соединен с выходом элемента И, первьй вход которого объединен с вт рым входом элемента ИЛИ, с управляю щим входом цифрового сумматора-вычи теля и является входом второго разр да второй группы входов арифметико- логического устройства, выходами ко торого являются соответствующие вых ды цифрового сумматора-вычитателя.

элементе И, элементе ИЛИ и цифровом

cyNj iaTope-вычитателе, первые инфорационные входы которого являются соответствующими входами первой группы входов арифметико-логического устройства, вход первого разряда вторых информационных входов цифрового сум- матора-вычитателя объединен с первым входом элемента ИЛ№ и является первым входом второй группы входов арифметико-логического устройства, вход второго разряда вторых информационных входов цифрового сумматора-вычитатё- ля соединен с выходом элемента И, первьй вход которого объединен с вторым входом элемента ИЛИ, с управляющим входом цифрового сумматора-вычита- теля и является входом второго разряда второй группы входов арифметико- логического устройства, выходами которого являются соответствующие выходы цифрового сумматора-вычитателя.

;Таблиц а2

Адресные Коды дополнитель-ГАналоговые эквиваленты по-ГСоответствие идеально- 1|содЫ I ных .погрешностей грешностей, мВму уровню ЦАП 8, мВ

128

I-001 4010

4-011

4100 4101 4110 «111

-0010 -0100

4

0110 -1000 -1010 -1100 -1110

-2 -4 -2+(-4)-6

О

-2+(-8)-10 -4+(-8) -12 -2+(-4)+(-8)14

256

128+256 384

512

128+512 640

256+512 768

128+256+512 896

Таблица 1

256

128+256 384

512

128+512 640

256+512 768

128+256+512 896

| Шляндин В.М | |||

| Цифровые измерительные устройства | |||

| - М.: Высшая школа, 1981, с | |||

| Рельсовый башмак | 1921 |

|

SU166A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Грешищев Ю.М., Гудинов А.Г | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Проблемы создания преобразователей формы информации | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| - Киев: Наукова думка, 1984, с | |||

| Способ получения бензидиновых оснований | 1921 |

|

SU116A1 |

Авторы

Даты

1988-05-23—Публикация

1986-05-11—Подача