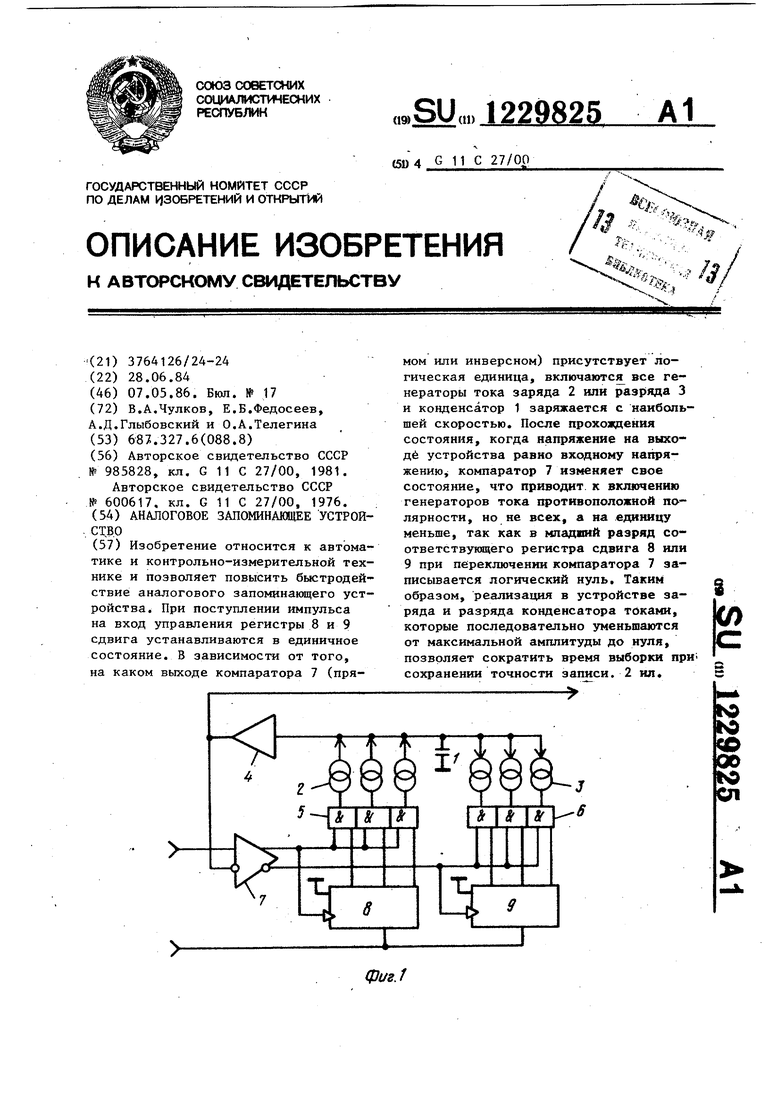

Изобретение относится к области автоматики и контрольно-измерительной техники и может быть использовано для запоминания выборочных значений напряжения аналогового сигналао

Целью изобретения является повы- шение быстродействия аналогового запоминающего устройства.

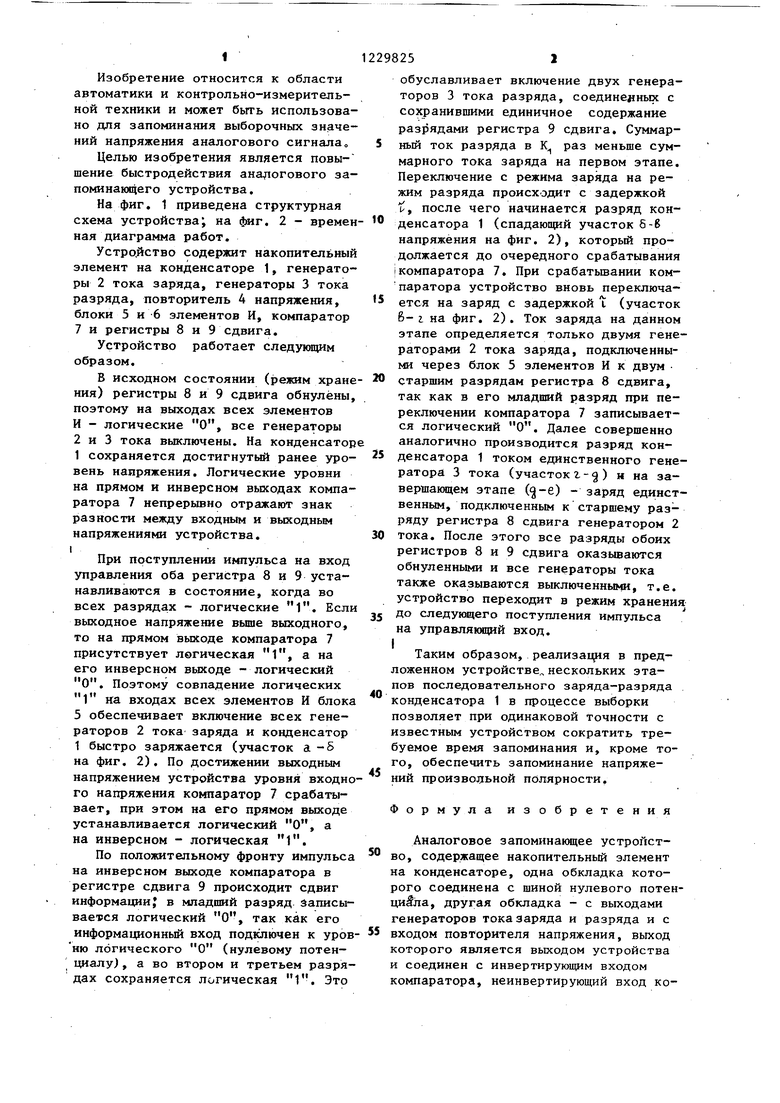

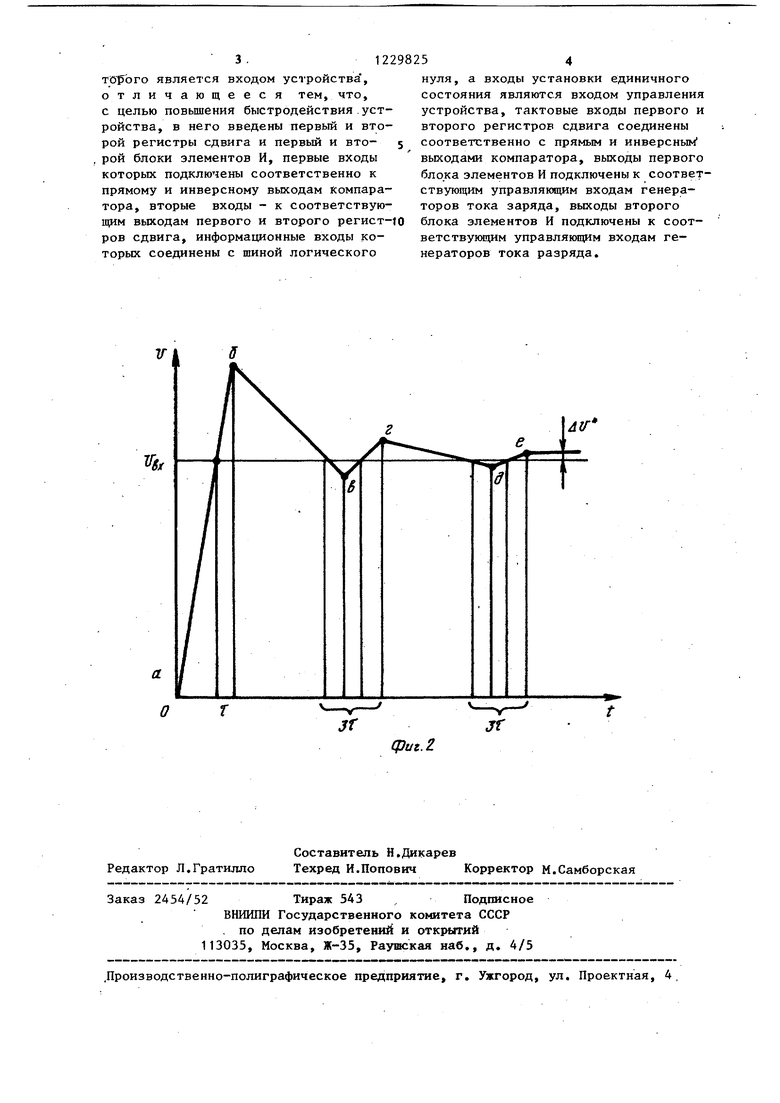

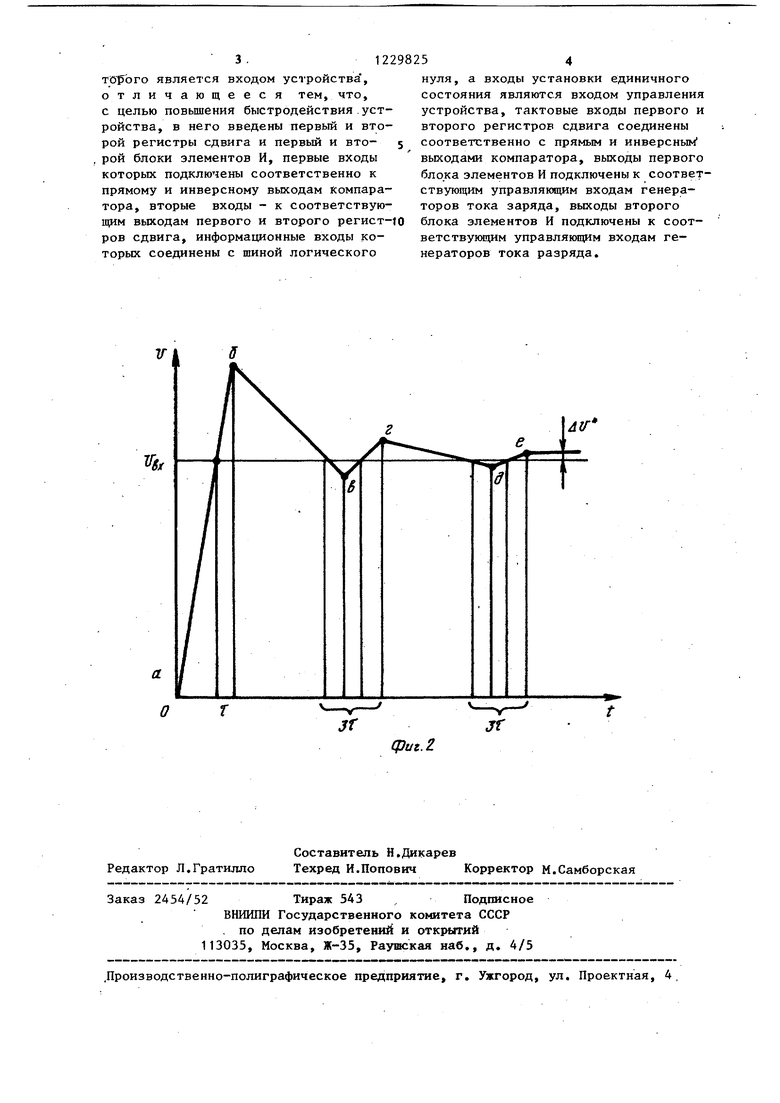

На фиг. 1 приведена структурная схема устройства i на г, 2 - времен ная диаграмма работ.

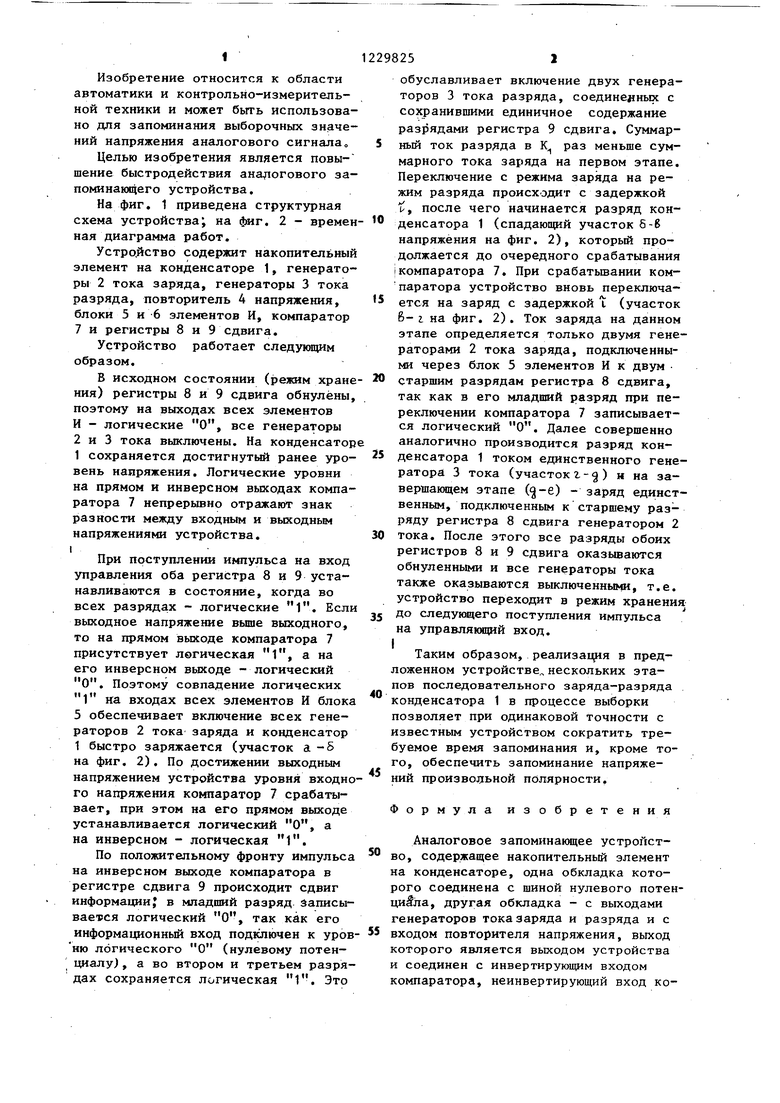

Устройство содержит накопительный элемент на конденсаторе 1, генераторы 2 тока заряда, генераторы 3 тока разряда, повторитель 4 напряжения, блоки 5 и 6 элементов И, компаратор 7 и регистры 8 и 9 сдвига.

Устройство работает следукяцим образом.

В исходном состоянии (режим хране ния) регистры 8 и 9 сдвига обнулены, поэтому на выходах всех элементов И - логические О, все генераторы 2 и 3 тока выключены. На конденсатор 1 сохраняется достигнутый ранее уро- вень напряжения. Логические уровни на прямом и инверсном выходах компаратора 7 непрерывно отражаня- знак разности между входным и выходным напряжениями устройства.

1

При поступлении импульса на вход

управления оба регистра 8 и 9 устанавливаются в состояние, когда во

1. Если

всех разрядах - логические выходное напряжение выше выходного, то на прямом выходе компаратора 7 присутствует логическая 1, а на его инверсном выходе - логический О. Поэтому совпадение логических 1 на входах всех элементов И блока 5 обеспечивает включение всех генераторов 2 тока заряда и конденсатор 1 быстро заряжается (участок а -5 на фиг. 2). По достижении выходным напряжением устройства уровня входного напряжения компаратор 7 срабатывает, при этом на его прямом выходе устанавливается логический О, а на инверсном - логическая 1.

По положительному фронту импульса на инверсном выходе компаратора в регистре сдвига 9 происходит сдвиг информации; в младший разряд записывается логический О, так как его информационный вход подключен к уров ню логического О (нулевому потенциалу) , а во втором и третьем разрядах сохраняется логическая 1. Это

5

0

5

0

5

обуславливает включение двух генераторов 3 тока разряда, соединенных с сохранившими единичное содержание разрядами регистра 9 сдвига. Суммарный ток разряда в К раз меньше суммарного тока заряда на первом этапе. Переключение с режима заряда на режим разряда происходит с задержкой , после чего начинается разряд конденсатора 1 (спадающий участок 6-6 напряжения на фиг. 2), который продолжается до очередного срабатывания iкомпаратора 7. При срабатывании ком- паратора устройство вновь переключается на заряд с задержкой t (участок 6-г на фиг. 2). Ток заряда на данном этапе определяется только двумя генераторами 2 тока заряда, подключенными через блок 5 элементов И к двум старшим разрядам регистра 8 сдвига, так как в его младший разряд при переключении компаратора 7 записывается логический О. Далее совершенно аналогично производится разряд конденсатора 1 током единственного генератора 3 тока (участок г-) и на завершающем этапе (-е) - заряд единственным, подключенным к старшему разряду регистра 8 сдвига генератором 2 тока. После этого все разряды обоих регистров 8 и 9 сдвига оказываются обнуленными и все генераторы тока также оказываются выключенными, т.е. устройство переходит в режим хранения до следунщего поступления импульса на управляющий вход.

Таким образом, реализащ1я в предложенном устройстве нескольких этапов последовательного заряда-разряда конденсатора 1 в процессе выборки позволяет при одинаковой точности с известным устройством сократить требуемое время запоминания и, кроме того, обеспечить запоминание напряжений произвольной полярности.

Формула изобретения

Аналоговое запоминающее устройство, содержащее накопительный элемент на конденсаторе, одна обкладка которого соединена с шиной нулевого потен- ци5ла, другая обкладка - с выходами генераторов тока заряда и разряда и с входом повторителя напряжения, выход которого является выходом устройства и соединен с инвертирующим входом компаратора, неинвертирующий вход ко3,12

T0pbro является входом устройства, отличающееся тем, что, с целью повышения быстродействия.устройства, в него введены первый и второй регистры сдвига и первый и вто- рой блоки элементов И, первые входы которых подключены соответственно к прямому и инверсному выходам компаратора, вторые входы - к соответствующим выходам первого и второго регистров сдвига, информационные входы которых соединены с шиной логического

нуля, а входы установки единичного состояния являются входом управления устройства, тактовые входы первого и второго регистров сдвига соединены соответственно с прямым и инверсным выходами компаратора, выходы первого блока элементов И подключены к соответствующим управляющим входам генераторов тока заряда, выходы второго блока элементов И подключены к соответствующим управляющим входам генераторов тока разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измерительный преобразователь для тензорезисторных весоизмерительных устройств | 1990 |

|

SU1830463A1 |

| Устройство для управления группой N статических преобразователей частоты,включенных параллельно по входу и выходу | 1986 |

|

SU1388973A1 |

| ИНТЕНСИМЕТР | 1995 |

|

RU2146061C1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1117835A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1200421A1 |

| Сенсорный переключатель | 1988 |

|

SU1684923A1 |

| Способ измерения положения или размеров объектов | 1987 |

|

SU1603192A1 |

| УРАВНОВЕШИВАЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1995 |

|

RU2101859C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Устройство слежения за дорожкой дискового носителя информации | 1987 |

|

SU1614031A1 |

Изобретение относится к автоматике и контрольно-измерительной технике и позволяет повысить быстродействие аналогового запоминающего устройства. При поступлении импульса на вход управления регистры 8 и сдвига устанавливаются в единичное состояние. В зависимости от того, на каком выходе компаратора 7 (прямом или инверсном) присутствует логическая единица, включаются все генераторы тока заряда 2 или разряда 3 и конденсатор 1 заряжается с наибольшей скоростью. После прохождения состояния, когда напряжение на выходе устройства равно входному напря- жению компаратор 7 изменяет свое состояние, что приводит, к включению генераторов тока противоположной полярности, но не всех, а на единицу меньше, так как в младший разряд со- ответствукицего регистра сдвига В или 9 при переключении компаратора 7 записывается логический нуль. Таким образом, реализация в устройстве заряда и разряда конденсатора токами, которые последовательно уменьшаются от максимальной амплитуды до нуля, позволяет сократить время выборки прИ сохранении точности записи. 2 ил. фиг.1

V

dlf

Редактор Л.Гратилло

Составитель Н.Дикарев

Техред И.Попович Корректор М.Самборская

Заказ 2454/52 Тираж 543 , Подписное ВНИИПИ Государственного комитета СССР . по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

(flut.Z

| Аналоговое запоминающее устройство | 1981 |

|

SU985828A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аналоговое запоминающее устройство | 1976 |

|

SU600617A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-05-07—Публикация

1984-06-28—Подача