Изобретение относится к вычислительной технике и может быть использовано для обнаружения и исправления ошибок при передаче данных в ЭВМ.

Цель изобретения - повышение быстродействия устройства.

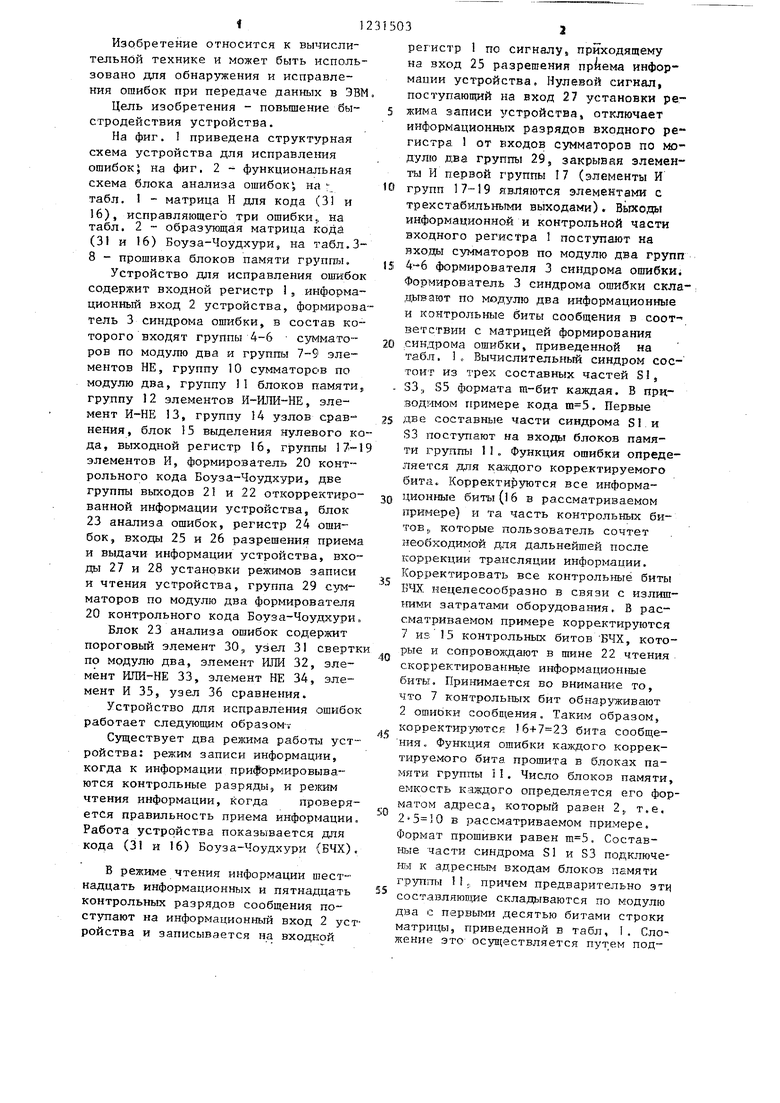

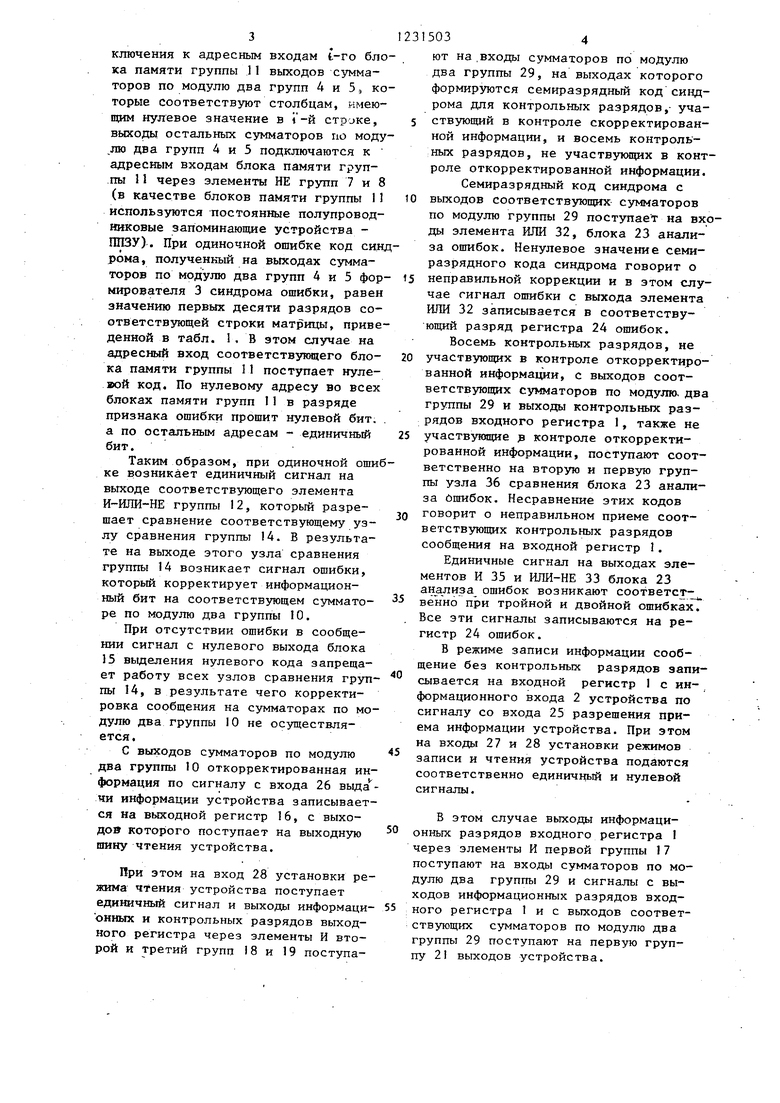

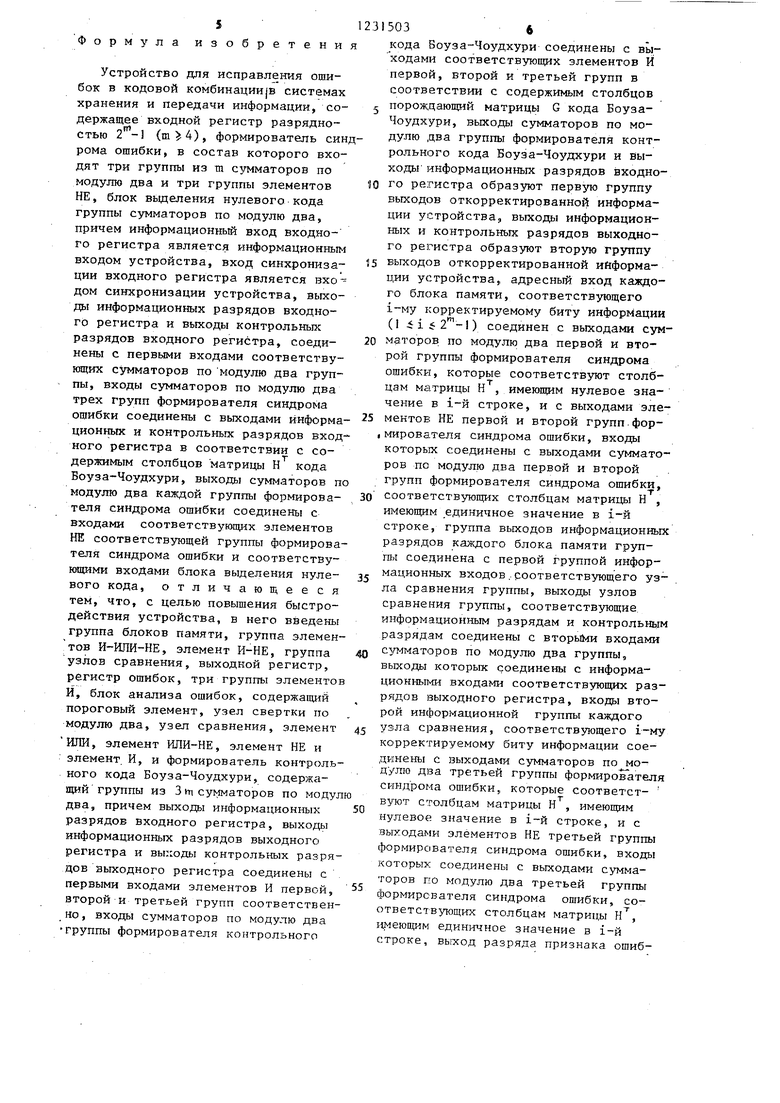

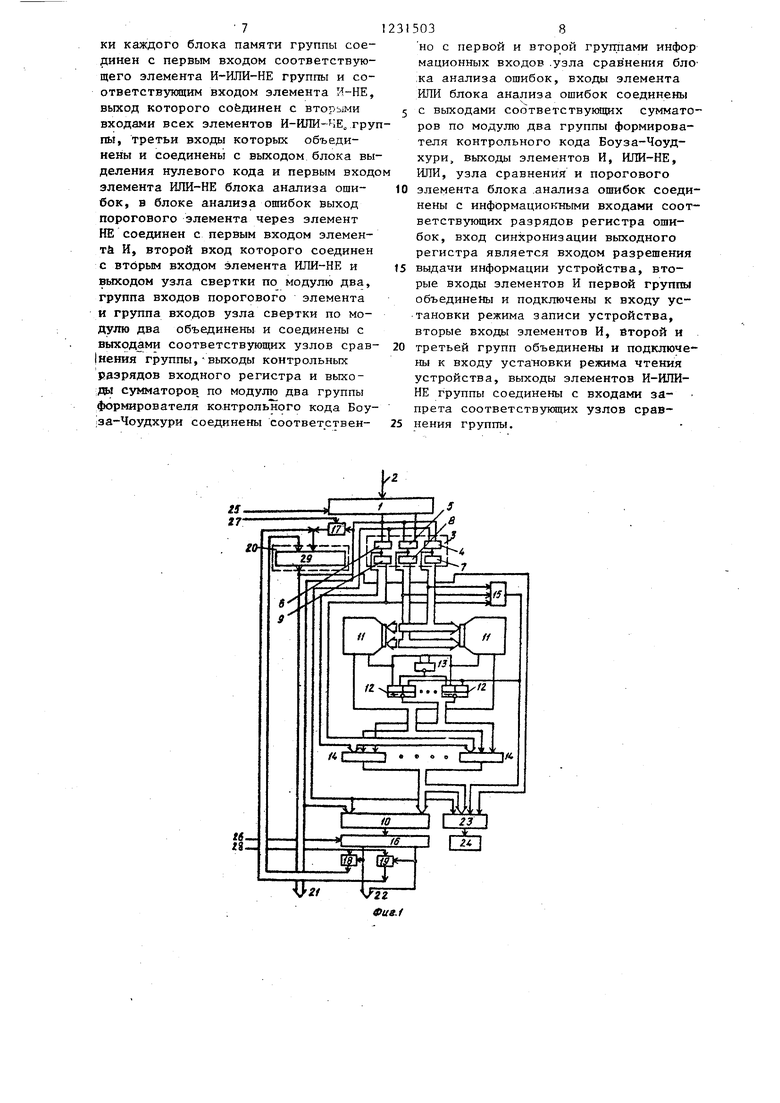

На фиг. I приведена структурная схема устройства для исправления ошибок; на фиг, 2 - функциональная схема блока анализа ошибок , на г,. табл. 1 - матрица Н для кода (3) и 16), исправляющего три ошибки,, на табл. 2 - образующая матрица кода (31 и 16) Боуза-Чоудхури, на табл.З- 8 - прошивка блоков памяти группы.

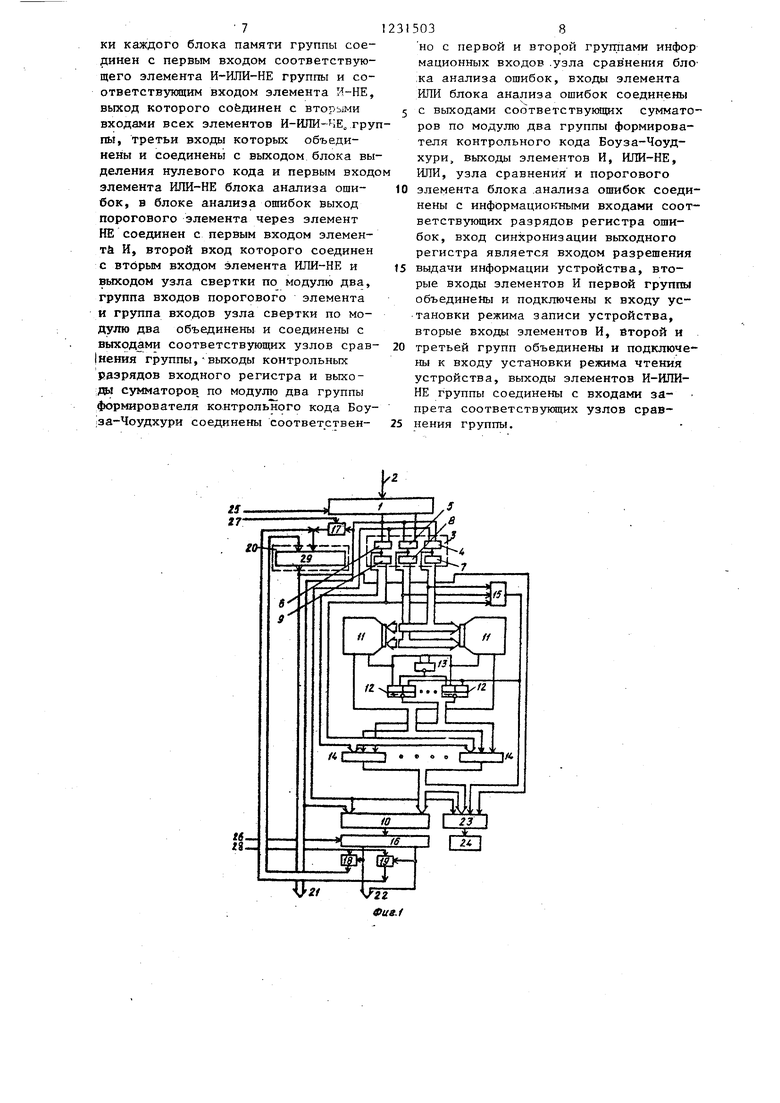

Устройство д:1я исправления ошибок содержит входной регистр 1, информа- ционньй вход 2 устройства, формирователь 3 синдрома ошибки, в состав которого входят группы 4-6 сумматоров по модулю два и группы 7-9 элементов НЕ, группу 10 сумматоров по модулю два, группу П блоков памяти, группу 12 элементов И-ИЛИ-НЕ, элемент И-НЕ 13, группу 14 узлов сравнения, блок 15 выделения мулевого кода, выходной регистр 16, группы 17-19 элементов И, формирователь 20 контрольного кода Боуза-Чоудхури, две

25 две составные части синдрома S1 и S3 поступают на входы блоков памяти группь 1 ,, Функция ошибки опред ляется дхЕЯ калодого корректируемого бита. Корректируются все информа.15

40

группы выходов 21 и 22 откорректиро- о Ционные биты (16 в рассматриваемом ванной информации устройства, блок 23 анализа ошибок, регистр 24 ошибок, входы 25 и 26 разрешения приема и выдачи информации устройства, входы 27 и 28 установки режимов записи и чтения устройства, группа 29 сумматоров по модулю два формирователя 20 контрольного кода Боуза-Чоудхури,

Блок 23 анализа ошибок содержит пороговый элемент 30, узел 31 свертки по модулю два, элемент ИЛИ 32, элемент ИЛИ-НЕ 33, элемент НЕ 34, элемент И 35, узел 36 сравнения.

Устройство для исправления ошибок работает следующим образом-т

Существует два режима работ ; устройства: режим записи информации, когда к информации приформировыва- ются контрольные разряды, и резким чтения информации, когда проверяется правильность приема информации. Работа устройства показывается для кода (31 и 16) Боуза-Чоудхури (БЧХ).

45

50

примере) и та часть контрольных би тов,, которые пользователь сочтет необходимой для дальнейшей после коррекции трансляции информации. Корректировать все контрольные бит БЧХ нецелесообразно в связи с изли tmwH затратами оборудования, В рас сматриваемом примере корректируютс 7 из 15 контрольных битов БЧХ, кот рые и сопровождают в шине 22 чтени скорректированньш информацион 1ые биты. Принимается во внимание то, что 7 контрольных бит обнаруживают 2 ошибки сообщения. Таким образом, корректир-уются бита сообще ния. Функция ошибки каждого коррек тируемого бита прошита в блоках па мяти группы 1I. Число блоков памят емкость каждого определяется его ф матом адреса который равен 2 т.е в рассматриваемом примере. Формат прошивки равен . Составные -части синдрома S1 и S3 подключ на к адресньм входам блоков памяти группы 1 I;: предварительно э составляюпще складе ваются по модул два с первыми десятью битами строк матрицы, приведенной в табл, 1. Сл жение это осуществляется путем под

В режиме чтения информации шестнадцать информационных и пятнадцать контрольных разрядов сообщения поступают на информационный вход 2 устройства и записывается на входной

15032

регистр 1 по сигналу, приходящему на вход 25 разрешения приема информации устройства. Нулевой сигнаЛ| поступающий на вход 27 установки ре5 жима записи устройства, отключает информационных разрядов входного ре гистра 1 от входов сумматоров по модулю два группы 29, закрывая элементы И первой группы 17 (элементы И

10 групп 17-19 являются элементами с трехстабильными выходами). Выходы информационной и контрольной части входного регистра 1 поступают на входа сзп- маторов по модулю два групп

5 4-6 формирователя 3 синдрома ошибки. Формирователь 3 синдрома ошибки скла-: дывают по модулю два информационные и контрольные биты сообщения в соответствии с матрицей форг гарования

20 синдрома ошибки, приведенной на

табл. 1. Вычислительный синдром сое- тоит из трех составных частей S, . 33,, S5 формата т-бит каждая. В прн- ВОДГ-1МОМ примере кода . Первые

25 две составные части синдрома S1 и S3 поступают на входы блоков памяти группь 1 ,, Функция ошибки определяется дхЕЯ калодого корректируемого бита. Корректируются все информа о Ционные биты (16 в рассматриваемом

5

0

о Ционные биты (16 в рассматриваемом

5

0

примере) и та часть контрольных битов,, которые пользователь сочтет необходимой для дальнейшей после коррекции трансляции информации. Корректировать все контрольные биты БЧХ нецелесообразно в связи с излиш- tmwH затратами оборудования, В рассматриваемом примере корректируются 7 из 15 контрольных битов БЧХ, которые и сопровождают в шине 22 чтения скорректированньш информацион 1ые биты. Принимается во внимание то, что 7 контрольных бит обнаруживают 2 ошибки сообщения. Таким образом, корректир-уются бита сообще- ния. Функция ошибки каждого корректируемого бита прошита в блоках памяти группы 1I. Число блоков памяти, емкость каждого определяется его форматом адреса который равен 2 т.е. в рассматриваемом примере. Формат прошивки равен . Составные -части синдрома S1 и S3 подключена к адресньм входам блоков памяти группы 1 I;: предварительно этц составляюпще складе ваются по модулю два с первыми десятью битами строки матрицы, приведенной в табл, 1. Сложение это осуществляется путем подключения к адресным входам t-ro блока памяти группы 11 выходов сумматоров по модулю два групп 4 и 5, которые соответствуют столбцам, имеющим нулевое значение в 1 -й строке, выходы остальных сумматоров по моду лю два групп 4 и 5 подключаются к адресным входам блока памяти группы 1I через элементы НЕ групп 7 и 8 (в качестве блоков памяти группы 1 используются постоянные полупроводниковые запоминающие устройства - ППЗУ). При одиночной ошибке код син рома, полученный на выходах сумматоров по модулю два групп 4 и 5 формирователя 3 синдрома ошибки, равен значению первых десяти разрядов соответствующей строки матрицы, приведенной в табл. 1. В этом случае на адресный вход соответствзтощего блока памяти группы I1 поступает нулевой код. По нулевому адресу во всех блоках памяти групп I1 в разряде признака ошибки прошит нулевой бит. а по остальным адресам - единичный бит.

Таким образом, при одиночной ошике возникает единичный сигнал на вьтходе соответствующего элемента И-ИЛИ-НЕ группы 12, который разрешает сравнение соответствующему узлу сравнения группы 14. В результате на выходе этого узла сравнения группы 14 возникает сигнал ошибки, который корректирует информационный бит на соответствующем сумматоре по модулю два группы 10.

При отсутствии ошибки в сообщении сигнал с нулевого выхода блока 15 выдешения нулевого кода запрещает работу всех узлов сравнения группы 14, в результате чего корректировка сообщения на сумматорах по модулю два группы 10 не осуществляется.

С выходов сумматоров по модулю два группы 10 откорректированная информация по сигналу с входа 26 выда чи информации устройства записывается на выходной регистр 16, с выходов KOTOpioro поступает на выходную шику чтения устройства.

При этом на вход 28 установки режима чтения устройства поступает единичный сигнал и выходы информационных и контрольных разрядов выходного регистра через элементы И второй и третий групп 18 и 19 поступа2315034

ют на.входы сумматоров по модулю два группы 29, на выходах которого формируются семиразрядный код синдрома для контрольных разрядов,- уча- 5 ствующий в контроле скорректированной информации, и восемь контрольных разрядов, не участвующих в контроле откорректированной информации.

Семиразрядный код синдрома с 10 выходов соответствующих сумматоров по модулю группы 29 поступает на входы элемента ИЛИ 32, блока 23 анализа ошибок. Ненулевое значение семиразрядного кода синдрома говорит о

15 неправильной коррекции и в этом случае сигнал ошибки с выхода элемента ИЛИ 32 записывается в соответствующий разряд регистра 24 ошибок. Восемь контрольных разрядов, не

20 участвующих в контроле откорректированной информации, с выходов соответствующих сумматоров по модулю, два группы 29 и выходы контрольных разрядов входного регистра 1, также не

25 участвукнцие в контроле откорректированной информации, поступают соответственно на вторую и первую группы узла 36 сравнения блока 23 анализа Ошибок. Несравнение этих кодов

30 говорит о неправильном приеме соответствующих контрольных разрядов сообщения на входной регистр 1.

Единичные сигнал на выходах элементов И 35 и ИЛИ-НЕ 33 блока 23 анализа ошибок возникают соответст3-5 венно при тройной и двойной ошибках. Все эти сигналы записываются на регистр 24 ошибок.

В режиме записи информации сообщение без контрольных разрядов записывается на входной регистр 1 с информационного входа 2 устройства по сигналу со входа 25 разрешения приема информации устройства. При этом на входы 27 и 28 установки режимов записи и чтения устройства подаются соответственно единичный и нулевой сигналы.

0

5

В этом случае выходы информаци- онных разрядов входного регистра 1 через элементы И первой группы 17 поступают на входы сумматоров по модулю два группы 29 и сигналы с выходов информационных разрядов вход- кого регистра 1 и с выходов соответствующих сумматоров по модулю два группы 29 поступают на первую группу 21 выходов устройства.

5

Формула изобретения

Устройство для исправления ошибок в кодовой комбинации)в системах хранения и передачи информации, со- держащее входной регистр разрядностью (), формирователь синдрома ошибки, в состав которого входят три группы из та сумматоров по модулю два и три группы элементов НЕ, блок выделения нулевого кода группы сумматоров по модулю два, причем информационный вход входного регистра является информационным входом устройства, вход синхрониза- ции входного регистра является вхо дом синхронизации устройства, выходы информационнь1х разрядов входного регистра и выходы контрольньк разрядов входного регистра, соеди- нены с первыми входами соответству- клцих сумматоров по модулю два группы, входы сумматоров по модулю два трех групп формирователя синдрома ошибки соединены с выходами информа- ционных и контрольных разрядов входного регистра в соответствии с содержимым столбцов матрицы Н кода Воуза-Чоудхури, выходы сумматоров по модулю два каждой группы формирова- теля синдрома ошибки соединены с входами соответствующих элементов НЕ соответствующей группы формирователя синдрома ошибки и соответствующими входами блока выделения нуле- вого кода, отличающее ся тем, что, с целью повышения быстродействия устройства, в него введены группа блоков памяти, группа элемен- тов И-Ш1И-НЕ, элемент И-НЕ, группа узлов сравнения, выходкой регистр, регистр ошибок, три группы элементов И, блок анализа ошибок, содержаний пороговый элемент, узел свертки по модулю два, узел сравнения, элемент

ИЛИ, элемент ИЛИ-НЕ, элемент НЕ и элемент И, и формирователь контрольного кода Боуза-Чоудхури, содержащий группы из 3т сумматоров по модул два, причем выходы информационных разрядов входного регистра, выходы информационньгх разрядов выходного регистра и выходы контрольных разрядов выходного регистра соединены с первыми входами элементов И первой, второй и третьей групп соответственно, входы сумматоров по модулю два

труппы формирователя контрольного

5036

кода Боуза-Чоудхури соединены с выходами соответствующих элементов И первой, второй и третьей групп в соответствии с содержимым столбцов порожцающий матрицы G кода Боуза- Чоудхури, выходы сумматоров по модулю два группы формирователя контрольного кода Боуза-Чоудхури и выходы информационньгх разрядов входного регистра образуют первую группу выходов откорректированной информации устройства, выходы информационных и контрольных разрядов выходного регистра образуют вторую группу выходов откорректированной ийформа- ции устройства, адресный вход каждого блока памяти, соответствующего i-му корректируемому биту информации (I i i f- 2 -1) соединен с выходами сумматоров по модулю два первой и второй группы формирователя синдрома ошибки, которые соответствуют столбцам матрицы Н , имеющим нулевое значение в 1-й строке, и с выходами эле ментоЕ НЕ первой и второй групп.фор1 мирователя синдрома ошибки, входы которксх соединены с выходами сумматоров ПС модулю два первой и второй групп формирователя синдрома ошибки, соответствующих столбцам матрицы Н , и)у1еющим единичное значение в i-й строке, группа выходов информационньг разрядов каждого блока памяти груп- шя соединена с первой группой информационньгх входов ..соответствующего узла сравнения группы, выходы узлов сравнения группы, соответствующие информационным разрядам и контрольны разрядам соединены с вторыми входами сумматоров по модулю два группы, выходы которых соединены с ннформа- ционньп Ш входами соответствующих разрядов выходного регистра, входа второй ишЬормационной группы каждого узла сравнения, соответствующего i-м корректируемому биту информации соединены с выходами сумматоров по модулю два третьей группы формировател синд рома ошибки, которые соответст- вуют столбцам матрицы Н , имеющим нулевое значение в i-й строке, и с выходами элементов НЕ третьей группы формирователя синдрома ошибки, входы которых соединены с выходами сумматоров по модулю два третьей группы формирователя синдрома ошибки, соответствующих столбцам матрицы Н , даеющим единичное значение в i-й строке, выход разряда признака сшиб 7

ки каждого блока памяти группы соединен с первым входом соответствующего элемента И-ИПИ-НЕ группы и со- ответствунлцим входом элемента И-НЕ, выход которого соединен с вторыми входами всех элементов И-ИЛИ-ЧЕ групы, третьи входы которых объединены и соединены с выходом блока выделения нулевого кода и первым вход элемента ИПИ-НЕ блока анализа оши- бок, в блоке анализа ошибок выход порогового элемента через элемент НЕ соединен с первым входом элемен- т& И, второй вход которого соединен с вторым входом элемента ИЛИ-НЕ и выходом узла свертки по модулю два, группа входов порогового элемента и группа входов узла свертки по модулю два объединены и соединены с выходами соответствующих узлов срав- Iнения группы,выходы контрольных разрядов входного регистра и выхода сумматоров по модулю два группы формирователя ко.нтроль ного кода Боу- ;За-Чоудхури соединены соответствен-

5038

но с первой и BTopofi грудпамн инфор мационных входов .узла срав нения блО .ка анализа ошибок, входы элемента юта блока анализа ошибок соединены с выходами соответствукяцих сумматоров по модулю два группы формирователя контрольного кода Боуза-Чоуд- хури, выходы элементов И, ИЛИ-НЕ, ИЛИ, узла сравнения и порогового элемента блока .анализа ошибок соединены с информациокными входами соответствующих разрядов регистра ошибок, вход синхронизации выходного регистра является входом разрешения выдачи информации устройства, вторые входы элементов И первой группы объединены и подключены к входу установки режима записи устройства, вторые входы элементов И, второй и третьей групп объединены и подключены к входу установки режима чтения устройства, выходы элементов И-ИПИ- НЕ группы соединены с входами запрета соответствующих узлов сравнения группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ РЕКОНФИГУРИРУЕМЫЙ КОДЕР БЧХ КОДОВ | 2015 |

|

RU2591474C1 |

| Устройство для декодирования кодов Боуза-Чоудхури-Хоквингема | 1982 |

|

SU1168946A1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ С МЯГКИМИ РЕШЕНИЯМИ ДЛЯ ДВУХСТУПЕНЧАТОГО КАСКАДНОГО КОДА | 2012 |

|

RU2485683C1 |

| Устройство для исправления двухкратных ошибок в блоках передачи и хранения информации | 1983 |

|

SU1173417A1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ С ЖЕСТКИМИ И МЯГКИМИ РЕШЕНИЯМИ ДЛЯ ДВУХСТУПЕНЧАТОГО КАСКАДНОГО КОДА И МОДУЛЯЦИИ ПО ТИПУ СТЫКА С1-ФЛ | 2024 |

|

RU2834891C1 |

| Декодер кода Боуза-Чоудхури-Хоквингема с каноническим декодером Хэмминга | 2018 |

|

RU2704499C1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2259638C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

Изобретение относится к области вычислительной техники. Целью изобретения является повьппение быстродействия устройства. Устройство содержит входной регистр, формирователь синдрома ошибки, группу cyj jaTOpoB по модулю два, группу блоков памяти, группу элементов И- Ш1И-НЕ, элемент И-НЕ, группу узлов сравнения, дешифратор, выходной регистр, три группы элементов И, формирователь контрольного кода Боуза- Чоудхури, блок анализа ошибок, регистр ошибок. Повьшение производи- тельности устройства достигается за счет использования группы блоков памяти, которые по синдрому ошибки, индивидуальному для каждого бита информации, формируют константу коррекции, которая и осуществляет коррекцию принятой информации. Имеет- ся возможность проверить правильность коррекции информации с помощью формирователя контрольного кода Боуза-Чоудхури- На вход этого формирователя поступает откорректированная информация с выходного регистра, а выходные сигналы формирователя контрольного кода Боуза-Чоудхури анализируются блоком анализа оптбок. Нулевое значение выходных сигналов говорит о правильности коррекции. Имеется возможность приформировы- вать к информационному слову, поступающему на входной регистр, контрольные разряды с помощью формирователя контрольного кода Боуза-Чоудхури . 2 ил. 8 табл,I с (Л СП О со

Г2г

Фиг.1

| Патент США № 4030067, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| СПОСОБ ПОЛУЧЕНИЯ СПИРТА | 1995 |

|

RU2093238C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-15—Публикация

1984-04-21—Подача