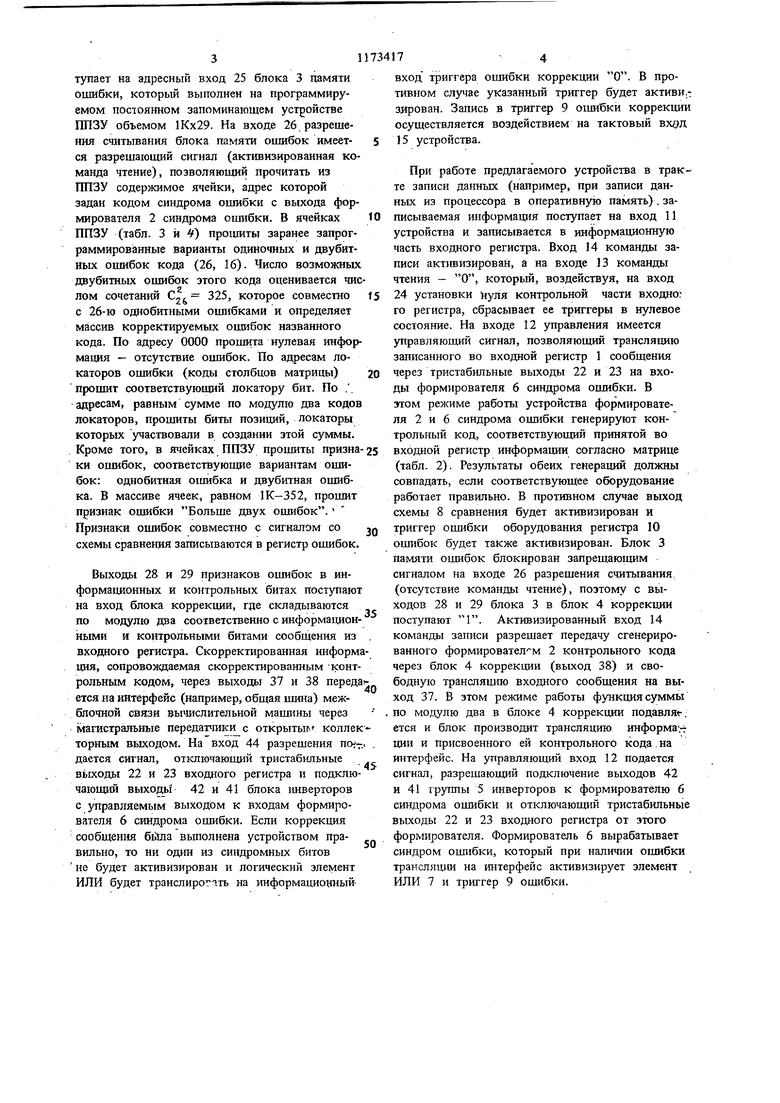

Изобретение относится к вычислительной ; технике и может быть использовано для исправ ления двукратных ошибок в блоках хранения информации и трактах приемо-передачи дискретных данных, например, при считывании данных из оперативной памдти в процессор вы числительной машины или записи даннях из процессора в оперативную память. ЦеЛь изобретения - повышение быстродей ствия устройства и достоверности передачи ,, ранных. - На чертеже представлена блок-схема предлагаемого устройства. Устройство содержит входной регистр. 1, первый формирователь 2 синдрома ошибки, блок 3 памяти ошибок, блок 4 коррекции, группу 5 инверторов с управляемым выходом, второй формироватеть 6 синдрома ошибки, элемент ИЛИ 7, схему 8 сравнения, триггер 9 ошибки коррекции, регистр 10 ошибок, вход 11 сообшения, вход 12 управления, вход 13 команды чтения, вход 14 команды записи и тактовый вход 15 устройства. На первую группу 16 информационных входов входного регистра 1 поступает контрольная часть сообшения, а на вторую группу 17 - информациош1ая часть. Блок коррекции разделен на две части: контрольную 18 и информационную 19. Входной регистр состоит из D-триггеров с прямыми и тристабильными выходами. При этом выходы 20 и 21 входного регистра образованы прямыми выходами триггеров, а выходы 22 и 23 - их тристабильными выходами, вход 24 установки нуля контрольной части входного регистра соединен с входом команды чтения. Блок 3 памяти ошибок может быть вьшолнен например, на ППЗУ и имеет адресный вход 25 вход 26 разрешения считывания, выход 27 признаков ошибок, выходы 28 и 29 признаков. ошибок контрольной и информационной части соо.бшения. Блок 4 коррекции имеет следующие входы: признаков команд 30 и чтения 31, информационных 32 и контрольных 33 ра рядов входного регистра, признака информационной 34 и контрольной 35 ошибок и синдромного кода 36 . Выходы блока коррекции сгруппированы в две группы, составляюшие интерфейс межблочной связи вычислительной машины, и являются соответственно группами информационных 37 и контрольных 38 выходов устройства. Входы грутшы . инверторов с у равляемыми выходами подразделяются на кон трольные 39 и информационные 40. Указанная группа имеет соответствующие входам тристабильные управляемые выхош) 41 и 42, вход 43 разрешения, соединенный с управляющим входом устройства и входом 44 разрешения триста1172 бильных выходов входного регистра. Выходы . регистра ошибок и триггера ошибки коррекции составляют соответственно идентификационный выход 45 ошибки устройств и выход 46 ошибки коррекции устройства. В основу построения формирователей 2 и 6 синдрома ошибки положена матрица, состоящая из элементов, реализующих функцию ИСКЛЮЧАЮЩЕЕ ИЛИ. Блок 4 коррекции реализует на своих выходах следующие логические функции : ,- - . .«. BD. D. (5; vw-)v ED.D. R -, 8С. 5,,-W IE с. Cj R V с. ECj V/ , где ВО;-функция на i-й информационной выходной шине устройства; ВС- функция на j-и контрольной выход.-., ной шине устройства; D - информационный бит сообщения; С - контрольный бит сообщения; ED{- ошибка информационного бита сообщения:ошибка контрольного биты сообщения;Sj - j-й разряд синдромного кода; R - команда чтения; W - команда записи. При отсутствии команд чтения или записи jnoK .коорекции отключается от интерфейса. Управляющие сигналы на входах 12-15 устройства формируются устройством, входящим в состав ЭВМ, использующим предлагаемое устройство для исправления Двукратных ошибок. Устройство работает следующим образом. Передаваемое шгформационное сообщение, например 16 бит, с сопровождающим его контрольнь1М кодом, например 10 бит, поступает на вход 11 сообщения устройства и записьшается во входной регистр. На входе 44 разрешения имеется сигнал, разрешающий трансляцию записанной информации через тристабильные выходы 22 и 23 на входы формирователя 6 синдрома ошибки. С прямых выходов входного регистра записанное сообщение поступает на формирователь 2, а с тристабильных выходов - на формирователь 6 синдрома ошибки. Оба формирователя складывают по модулю два информационные и контрольные биты сообщения в соответствии с Штрицей формирования синдрома ошибки {табл. 1). ВьГчисленные синдромы ошибки с выходов обоих формирователей сравнивают ся на схеме 8 сравнения. Результат сравнения поступает на второй информационный вход регистра ошибок. Код синдрома ошибки с выхода формирователя 2 синдрома ошибки поступает на адресный вход 25 блока 3 памяти ошибки, который выполнен на программируемом постоянном запоминающем устройстве ППЗУ объемом 1Кх29. На входе 26 разрешения считьгеания блока памяти ошибок имеется разрешающий сигнал (активизированная команда чтение), позволяющий прочитать из ППЗУ содержимое ячейки, адрес которой задан кодом синдрома ошибки с выхода формирователя 2 синдрома ошибки. В ячейках ППЗУ (табл. 3 и 4) прошиты заранее запрограммированные варианты одиночных и двубитных ошибок кода (26, 16). Число возможных двубитных ошибок этого кода оценивается чис лом сочетаний Cj 325, которое совместно с 26-ю однобитными ошибками и определяет массив корректируемых ошибок названного кода. По адресу 0000 прошита нулевая информация - отсутствие ошибок. По адресам локаторов ошибки (коды столбцов матрицы) прошит соответствующий локатору бит. По .. адресам, равным сумме по модулю два кодов локаторов, прошиты биты позиций, локаторы которых участвовали в создании этой суммы. Кроме того, в ячейках ППЗУ прошиты призна ки ошибок, соответствующие вариа11там ошибок: однобитная оишбка и двубитная ошибка. В массиве ячеек, равном К-352, прошит признак ошибки Больше двух ошибок. Признаки ошибок совместно с сигналом со схемы сравнения записываются в регистр ошибок. Выходы 28 и 29 признаков ошибок в информационных и контрольных битах поступают на вход блока коррекции, где складываются по модулю два соответственно с информационными и контрольными битами сообщения из входного регистра. Скорректированная информ ция, сопровоходаемая скорректированным -контрольным кодом, через выходат 37 и 38 переда ется на интерфейс (например, общая шина) межблочной связи вычислительной машины через магистральные передатчики с открытым коллек торным выходом. На вход 44 разрешения по;дается сигнал, отключающий тристабильные вькходы 22 и 23 входного регистра и подключающий выходь 42 и 41 блока 1шверторов с управляемым выходом к входам формирователя 6 синдрома ошибки. Если коррекция сообщен11Я бьШа вьшолнена устройством правильно, то ни ОД1Ш из синдромных битов не будет активизирован и логический элемент ИЛИ будет транслирог1ть на информационный117-4 вход триггера ошибки коррекции О. В противном случае указанный триггер будет активизирован. Запись в триггер 9 ошиВки коррекции осуществляется воздействием на тактовый вход 15 устройства. При работе предлагаемого устройства в трак-те записи данных (например, при записи данных из процессора в оперативную память). записываемая информация поступает на вход 11 устройства и записывается в информационную часть входного регистра. Вход 14 команды записи акт1шизирован, а на входе 13 команды чтения - О, который, воздействуя, на вход 24 установки нуля контрольной части вxoднo го регистра, сбрасывает ее триггеры в нулевое состояние. На входе 12 управления имеется управляющий сигнал, позволяющий трансляцию записанного во входной регистр 1 сообщения через тристабильные выходы 22 и 23 на входы формирователя 6 синдрома ошибки. В этом режиме работы устройства формирователя 2 и 6 синдрома ошибки генерируют контрольный код, соответствующий принятой во входной регистр информации согласно матрице (табл. 2). Результаты обеих генераций должны совпадать, если соответствующее оборудование работает правильно. В противном случае выход схемы 8 сравнения будет активизирован и триггер ошибки оборудования регистра Ю ошибок будет также активизирован. Блок 3 памяти ошибок блокирован запрешающим сигналом на входе 26 разрешения считывания (отсутствие команды чтение), поэтому с выходов 28 и 29 блока 3 в блок 4 коррекций поступают 1. Активизированный вход 14 команды записи разрещает передачу сгенерированного формирователем 2 контрольного кода через блок 4 коррекции (выход 38) и свободную трансляцию входного сообщения на выход 37. В этом режиме работы функция суммы по модулю два в блоке 4 коррекции подавляв: ется и блок производит трансляцию информа;-;ции и присвоенного ей контрольного кода.на интерфейс. На управляющий вход 12 подается сигнал, разрешающий подключение выходов 42 и 41 группы 5 инверторов к формирователю 6 синдрома ошибки и отключаюший тристабильные выходы 22 и 23 входного регистра от этого формирователя. Формирователь 6 вырабатывает синдром ошибки, который при наличии ошибки транслящш на интерфейс активизирует элемент ИЛИ 7 и триггер 9 ошибки.

/2 /J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

| Устройство для исправления ошибок в системах хранения и передачи информации в кодовой комбинации | 1984 |

|

SU1231503A1 |

| Устройство для исправления двух ошибок в кодовой комбинации с самоконтролем в системах контроля и передачи информации | 1984 |

|

SU1239721A1 |

| Устройство для записи и воспроизведения информации из блоков оперативной памяти с коррекцией ошибки | 1977 |

|

SU974410A1 |

| Устройство для контроля оперативной памяти | 1978 |

|

SU752502A1 |

| Корректор ошибок | 1989 |

|

SU1810909A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1751762A1 |

| Устройство для обнаружения и коррекции ошибок | 1990 |

|

SU1783583A1 |

| Устройство для контроля и коррекции информации | 1980 |

|

SU940160A1 |

УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ .ДВУКРАТНЫХ; ОШИБОК в БЛОКАХ ПЕРЕДАЧИ и ХРАНЕНИЯ ИНФОРМАЦИИ, содержащее входной регистр, первый к второй формиг рователи синдрома ошибки, схему сравнения, регистр ошибок, причем группа информационных и группа контрольных входов устройства соединены соответственно с группой инфоркачг. ционных и группой контрольных разрядов входрюго регистра, группы выходов информационных и контрольных разрядов входного регистра соединены с входами первого формирователя синдрома ошибки, отличающееся тем, что, с целью повышения быстродействия и достоверности передачи данных, в устройство введены блок памяти ошибок, блок коррекции, группа инверторов с управляемым выходом, элемент ИЛИ и триг- гер ошибки коррекции, причем выход первого формирователя синдрома ошибки соединен с первым входом схемы сравнения, входом контрольного кода блока коррекции и адресным входом блока памяти ошибок, выходы признаков ошибок, ошибок контрольной части сообщения, ошибок информационной части сообщения блока памяти ошибок соединены соответственно с первым информационным входом регистра ошибок, входом признака информационной ошибки и входом признака контрольной ошибки, вход команда чтения устройства соединен с входом разрешения считывания блока памяти ошибок, входом установки нуля контрольной части входного регистра и входом признака команды чтения блока коррекции, группы выходов информационных и контрольных разрядов входного регистра соединены соответственно с группами информационных и контрольных входов блока коррекции, вход команды записи устройства соединен с входом признака команды записи блока коррекции, группы информационных и контрольных выходов которого соединены с входами соответствующих злементов группы инверторов с управляемым выходом и являются соответственно группами информациi онных и контрольных выходов устройства, (Л выхода группь инверторов с управляемыми выходами соединены с информационными и f контрольными входами второго формирователя синдрома ошибки, группь управляемых выходов информациошп х и контрольных разрядов входного регистра соединены с группами информационных и контрольных входов второ го формирователя синдрома ошибки, выход со 4 которого соединен с вторым входом схемы сравнения и через элемент ИЛИ с информационным входом триггера ошибки коррекции, выход схемы сравнения соединен с вторым информационным входом регистра ошибок, . которого является идентификационным выходом сигнала ошибки устройства, тактовый вход устройства соединен;; с входом синхронизации триггера ошибки коррекции, выход которого является выходом сигнала ошибки коррекции устройства, управляющий вход устройства соединен с входом управления выходами входного регистра и управляющим вхо- дом группы инверторов с управляемым выходом.

| Патент США N 4030067, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Computer Design, v | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Способ получения морфия из опия | 1922 |

|

SU127A1 |

Авторы

Даты

1985-08-15—Публикация

1983-05-27—Подача