ответственно с вторым входом элемента ИЛИ и вторым входом записи регистра контрольной метки, выкод переполнения второго счетчика времв ни соединен с инверсным входом элемента ИЛИ, ьыход которого соединен

1I76336

с входом .блока индикации, выход переполнения первого счетчика соединен с вторыми входами второго и четвертого элементов И и инверсным -входом третьего элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

| Устройство для контроля выполнения программ | 1985 |

|

SU1307460A1 |

| Устройство для контроля параллельной вычислительной системы | 1987 |

|

SU1451697A1 |

| Устройство управления с контролем переходов | 1983 |

|

SU1103238A1 |

| Устройство для отладки программ | 1985 |

|

SU1348840A1 |

| Микропрограммное устройство управления с контролем переходов | 1980 |

|

SU966694A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1617442A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

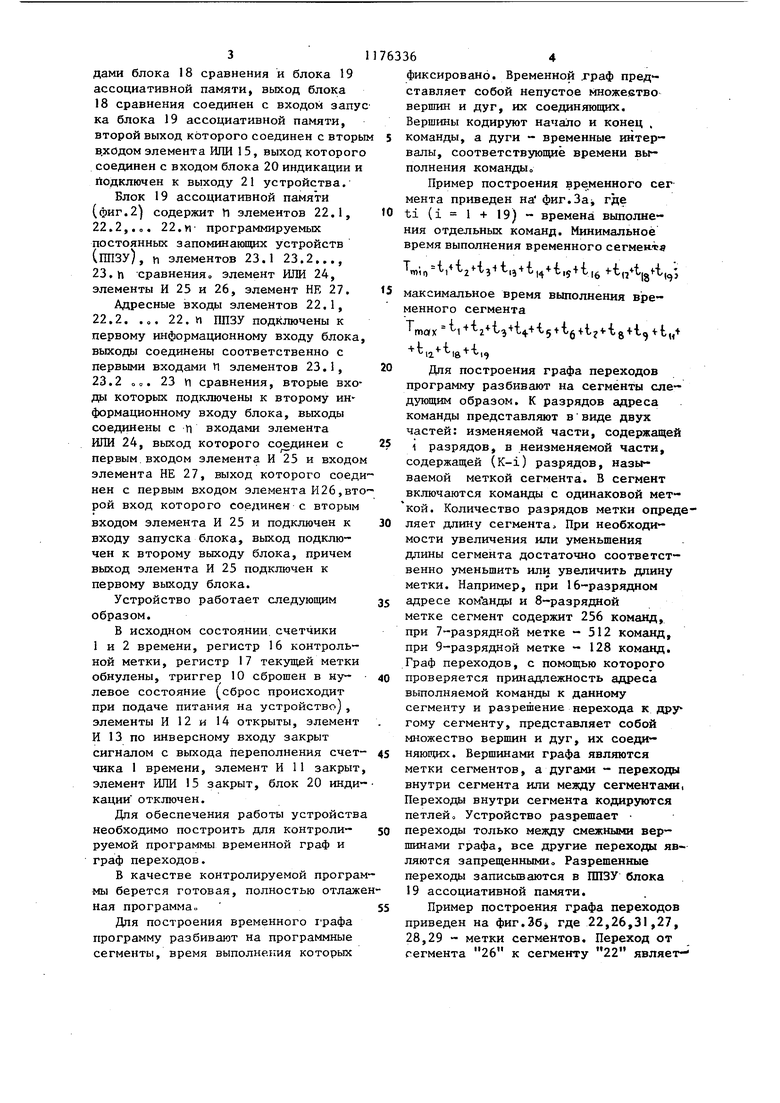

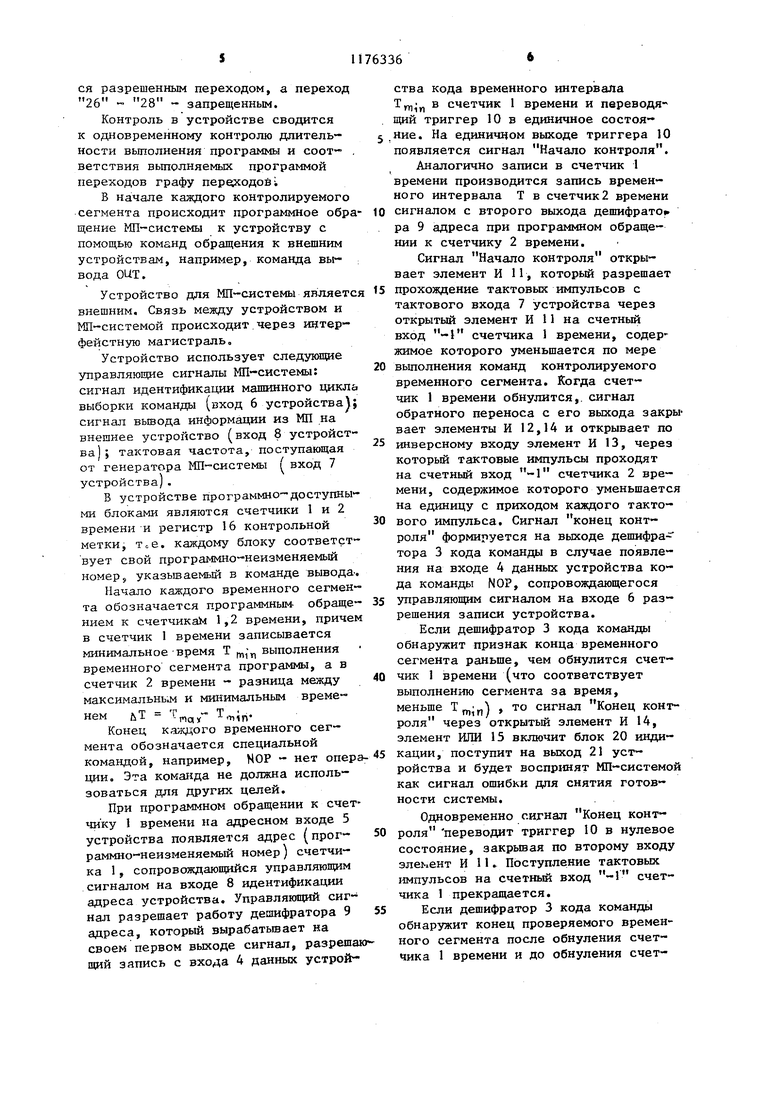

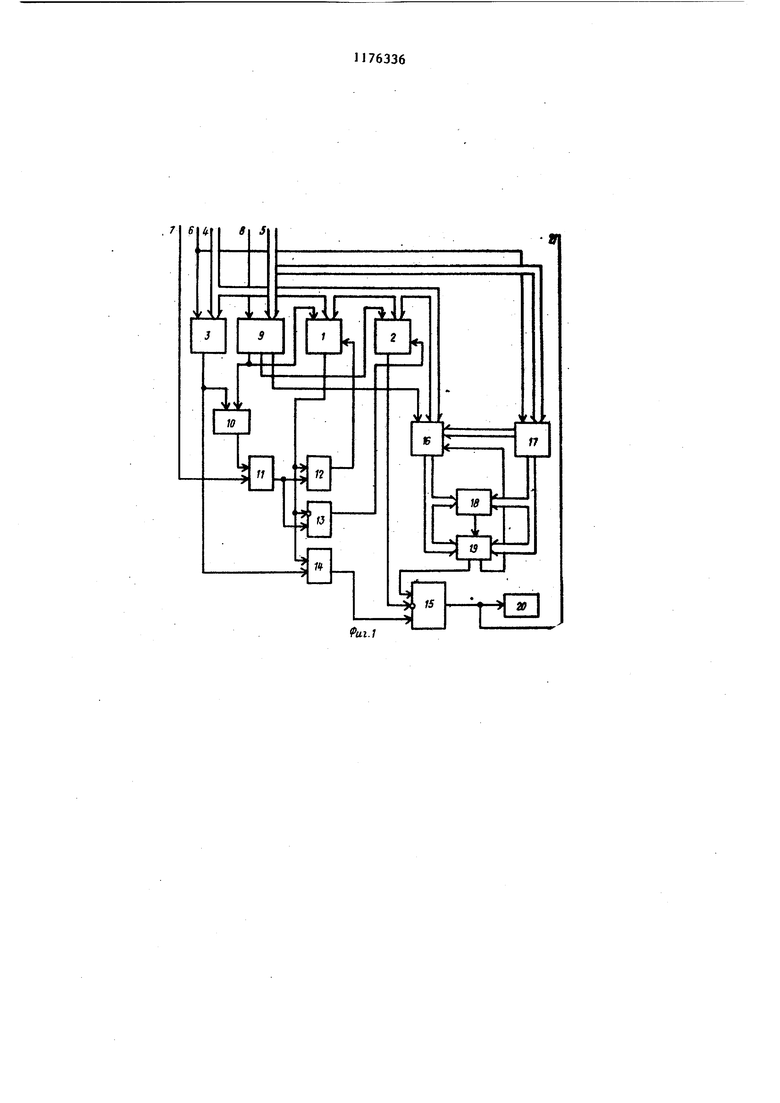

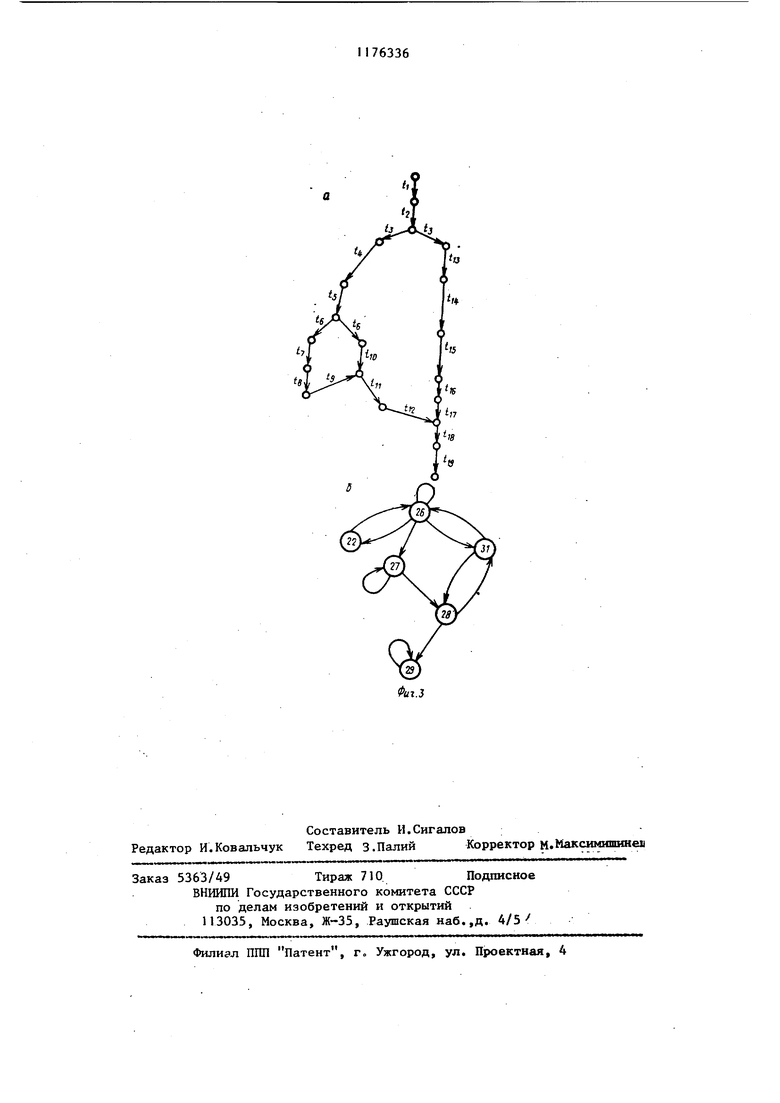

Изобретение относится к вычисли тельной технике, предназначено для программно-уплотняемого контроля правильности выполнения рабочей пр раммы в цифровых управляющих и . информационных системах реального времени и может быть использовано для контроля хода выполнения программ в микропроцессорньк АСУо Цель изобретения - повьшение достоверности контроля выполнения программы за счет одновременного программно-уплотняемого контроля времени выполнения программы и нап равления переходов между сегментам программного графа. На фиг,1 представлена структурная электрическая схема предлагаемого устройства; на фиг.2 - пример выполнения структурной электрическ схемы блока ассоциативной памяти; на фиг.З - пример построения временного графа и графа переходов программы. Устройство (фиг.1) содержит сче чики 1 и 2 времени, дешифратор 3 к да команды, вход 4 данных устройства, адресный вход 5 устройства, вход 6 разрешения записи устройства, тактовый вход 7 устройства, вход 8 идентификации адреса устройства, дешифратор 9 адреса триггер 10, элементы И Л - 14, элемент ИЛИ 15, регистр 16 контроль ной метки, регистр 17 текущей метки , блок 18 сравнения, блок 19 ассо циативной памяти, блок 20 индикации выход 21 устройства. Информационные входы счетчиков и 2 времени, регистра 16 контрольной метки объединены с информационным входом дешифратора 3 кода коман ды и подключены к входу 4 данных устройства, вход разрешения дешифрз ции дешифратора 3 кода команды соединен с входом записи регистра 17 текущей метки и подключен к входу 6 разрешения записи устройства, выход соединен с входом установки в О триггера 10 и первым входом элемента И 14, тактовый вход дешифратора 9 адреса подключен к входу 8 идентификации адреса устройства, информационный вход соединен с информационным входом регистра 17 текущей метки и подключен к адресному входу 5 устройства, первый выход соединен с входом записи счетчика 1 времени и входом установки в 1 триггера 10, второй выход соединен с входом записи счетчика 2 времени, третий - с первым входом записи регистра 16 контрольной метки, первый вход элемента И 11 подключен к тактовому входу 7 устройства, второй вход соединен с выходом триггера 10, а выход соедииен с первыми входами элементов И 12 и 13, вторые входы элементов И 12 - 14 подключены к выходу переполнения счетчика 1 времени, а выходы - соответственно к счетным входам счетчиков 1 и 2 времени и первому входу элемента ИЛИ 15, к инверсному входу которого подключен выход переполнения счетчика 2 времени Второй информационный вход регистра 16 контрольной метки соединен с первым информационным выходом регистра 17 текущей метки, второй вход записи соединен с первым выходом блока 19 ассоциативной памяти, второй информационный вход которого соединеи с вторым информационным входом блока 18 сравнения и со вторым информационным выходом регистра 17 текущей метки, информационный выход регистра 16 контрольной метки соединен с первыми информационными вхо3дами блока 18 сравнения и блока 19 ассоциативной памяти, выход блока 18 сравнения соединен с входом запу ка блока 19 ассоциативной памяти, второй выход которого соединен с втор в.ходом элемента ИЛИ 15, выход которог соединен с входом блока 20 индикации йодключен к выходу 21 устройства. Блок 19 ассоциативной памяти (фиг.2) содержит П элементов 22.1, 22.2,.,« 22.и- программируемых постоянных запоминающих устройств (ППЗУ), Y элементов 23.1 23.2..., 23.h сравнения элемент ИЛИ 24, элементы И 25 и 26, элемент НЕ 27. Адресные входы элементов 22.1, 22.2. .0. 22. и ППЗУ подключены к первому информационному входу блока выходы соединены соответственно с первыми входами И элементов 23.1, 23.2 00. 23 и сравнения, вторые вхо ды которых подключены к второму ин формационному входу блока, выходы соединены с п входами элемента ИЛИ 24, выход которого соединен с первым.входом элемента И 25 и входо элемента НЕ 27, выход которого соед нен с первым входом элемента И26,вт рой вход которого соединен с вторым входом элемента И 25 и подключен к входу запуска блока, выход подключен к второму выходу блока, причем выход элемента И 25 подключен к первому выходу блока. Устройство работает следующим образом. В исходном состоянии, счетчики 1 и 2 времени, регистр 16 контрольной метки, регистр 17 текущей метки обнулены, триггер 10 сброшен в нулевое состояние (сброс происходит при подаче питания на устройство), элементы И 12 и 14 открыты, элемен И 13 по инверсному входу закрыт сигналом с выхода переполнения сче чика 1 времени, элемент И 11 закры элемент ИЛИ 15 закрыт, блок 20 инд кации отключен. Дпя обеспечения работы устройст необходимо построить для контролируемой программы временной граф и граф переходов. В качестве контролируемой прогр мы берется готовая, полностью отлаж ная программао Для построения временного храфа программу разбивают на программные сегменты, время выполнения которых 64 фиксировано. Временной граф представляет собой непустое множевтво вершин и дуг, их соединяющих. Вершины кодируют начало и конец . команды, а дуги - временные интервалы, соответствующие времени выполнения команды Пример построения временного сег мента приведен на фиг.За где ti (i 1 + 19) - времена выполнения отдельных команд. Минимальное время выполнения временного cerMeHLTe Tm;n.,j+l,+i,,y+t,Vt...ft, максимальное время выполнения временного сегмента Tmax (, t,,gti,, Для построения графа переходов программу разбивают на сегменты следукщим образом. К разрядов адреса команды представляют ввиде двух частей: изменяемой части, содержащей 1 разрядов, в неизменяемой части, содержащей (К-i) разрядов, называемой меткой сегмента. В сегмент включаются команды с одинаковой меткой. Количество разрядов метки определяет длину сегмента При необходимости увеличения или уменьшения длины сегмента достаточно соответственно уменьшить или увеличить длину метки. Например, при 16-разрядиом адресе команды и 8-разрядной метке сегмент содержит 256 команд, при 7 разрядной метке - 512 команд, при 9-разрядной метке - 128 команд. Граф переходов, с помощью которого проверяется принадлежность адреса выполняемой команды к данному сегменту и разрешение перехода к дру гому сегменту, представляет собой множество вершин и дуг, их соеди- няющих. Вершинами графа являются метки сегментов, а дугами - переходы внутри сегмента или между сегментами, Переходы внутри сегмента кодируются петлейо Устройство разрешает переходы только между смежными вершинами графа, все другие переходы являются запрещенными. Разрешенные переходы записьюаются в ППЗУ блока 19 ассоциативной памяти. Пример построения графа переходов приведен на фиг.Зб где 22,26,31,27, 28,29 - метки сегментов. Переход от сегмента 26 к сегменту 22 являет ся разрешенным переходом, а переход ttocll ООПг (Ч /о Z - запрещенным. Контроль в устройстве сводится к одновременному контролю длительности вьтолнения программы и соответствия вьтолняемых программой переходов графу перегсодов1 В Начале каждого контролируемого сегмента происходит программное обр щение МП-системы к устройству с помощью команд обращения к внешним устройствам, например, команда вывода OUT. Устройство для МП-системы являетс внешним. Связь между устройством и МП-системой происходит.через ицтер- фейстную магистраль. Устройство использует следующие управляющие сигналы МП-системы: сигнал идентификации машинного цикл выборки команды (вход 6 устройства сигнал вьшода информации из МП на внешнее устройство (вход 8 устройства) ; тактовая частота, поступающая от генератора МП-системы { вход 7 устройства). В устройстве программно-доступны ми блоками являются счетчики 1 и 2 времени и регистр 16 контрольной метки, . каждому блоку соответст вует свой программно-неизменяемый номер,, указываемый в команде вывода Начало каждого временного сегмен та обозначается программным- обраще кием к счетчика 4 1,2 времени, приче в счетчик 1 времени записывается минимальное время Т - выполнения временного сегмента программы, а в счетчик 2 времени - разница между максимальньм и минимальным временем й,Т Т,-. Конец каждого временного сегмента обозначается специальной командой, например, NOP - нет опер ции. Эта команда не должна использоваться для других целей. При программном обращении к счет чику 1 времени на адресном входе 5 устройства появляется адрес (программно-неизменяемый номер) счетчика 1, сопровождающийся управляющим сигналом на входе 8 идентификации адреса устройства. Управляняций сигнал разрешает работу дешифратора 9 адреса, который вырабатьшает на своем первом выходе сигнал, разреша щий запись с входа 4 данных устройства кода временного интервала в счетчик 1 времени и переводящий триггер 10 в единичное состояние. На единичном выходе триггера 10 появляется сигнал Начало контроля. Аналогично записи в счетчик 1 времени производится запись временного интервала Т в счетчик 2 времени сигналом с второго выхода дешифрато. ра 9 адреса при программном обращении к счетчику 2 времени. Сигнал Начало контроля открывает элемент И 11, который разрешает прохождение тактовых импульсов с тактового входа 7 устройства через открытый элемент И 11 на счетный вход -1 счетчика 1 времени, содер жимое которого уменьшается по мере вьтолнения команд контролируемого временного сегмента. Когда счетчик 1 времени обнулится,. сигнал обратного переноса с его выхода закрывает элементы И 12,14 и открывает по инверсному входу элемент И 13, через который тактовые импульсы проходят на счетный вход -1 счетчика 2 времени, содержимое которого уменьшается на единицу с приходом каждого тактового импульса. Сигнал конец контроля формируется на выходе дешифратора 3 кода команды в случае появления на входе 4 данных устройства кода команды NOP, сопровождающегося управляющим сигналом на входе 6 разрешения записи устройства. Если дешифратор 3 кода команды обнаружит признак конца временного сегмента раньше, чем обнулится счетчик 1 времени (что соответствует выполнению сегмента за время, меньше , то сигнал Конец контроля через открытый элемент И 14, элемент ШШ 15 включит блок 20 индикации, поступит на выход 21 устройства и будет воспр1шят МП-системой как сигнал ошибки для снятия готовности системы. Одновременно сигнал Конец контроля переводит триггер 10 в нулевое состояние, закрьшая по второму входу элеьент И 1 К Поступление тактовых импульсов на счетный вход - счетчика 1 прекращается. Если дешифратор 3 кода команды обнаружит конец проверяемого временного сегмента после обнуления счетчика 1 времени и до обнуления счетчика 2 времени (что соответствует выполнению сегмента за время Т; (,- Т,пах). то сигнал Конец контроля.переводит в нулевое состояние триггер 10, закрьгаает элемент И 11 и прекращает поступление тактовых импульсов на счетчик 2 времени Так как в этот момент элемент И 14 закрыт, то сигнал Конец контроля не проходит на выход 21 устройства и блок 20 индикации.

Если счетчик 2 времени обнулится до появления команды НОР (что соответствует выполнению программного сегмента за время, большее Т,), то сигнал обратного переноса с выход счетчика 2 времени через инверюный вход элемента ИЛИ 15 включит блок 20 индикации, поступит на выход 21 устройства и будет, воспринят МП-системо как сигнал ошибки для снятия готовности системы.

Одновременно с контролем времени выполнения программ в устройстве осу ществляется контроль соответствия выполняемых программой переходов графу переходов,

В регистр 16 контрольной.метки программой записьшается контрольная метка только один раз в начале контроля. В дальнейшем в процессе контроля смена метки происходит аппаратным путем. Запись контрольной метки в регистр 16 контрольной метки в начале контроля происходит следующим образом.

При программном обращении к регистру 16 контрольной метки на адресном входе 5 появляется номер регистра 16, который расшифровывается дешифратором 9 адреса На третьем выходе дешифратора 9 адреса появляется сигнал, разрешающий запись кода метки с входа 4 данных в регистр 16 контрольной меткио

В регистр 17 текущей метки записывается текущая метка следующим образом. В каждом цикле выборки команды на адресном входе 5 появляется адрес выполняемой команды, принадлежащей контролируемому сегменту графа переходов (т.е. текущая метка) на входе 6 разрешения записи устройства - сигнал, идентифицирующий цикл выборки команды, который разрешает запись текущей метки в регистр 17 текущей метки.

С информационного выхода регистра 16 контрольной метки и с второго информационного выхода регистра 17 текущей метки коды меток поступают соответственно на первый и второй информационные входы блока 18 сравнения, где коды сравниваются. Пока текущая метка принадлежат проверяемому сегменту,, при правильном выполнении программы коды меток должны совпадать.

Несовпадение меток может произойти при наличии в сегменте команды, передающей управление другому сегменту в соответствии с графом переходов; при попытке программы выполнить запрещенный переход, что обусловлено наличием неисправности в МП-системе,

При несовпадении меток на выходе блока 18 сравнения появляется сигнал, поступающий на управляющий вход блока 19 ассоциативной памяти.

Одновременно на первый и второй информационные входы блока 19 ассоциативной памяти поступают те же коды контрольной и текущей меток. Блок 19 ассоциативной памяти проверяет, является ли текущая метка разрешенной графом переходов. Если текущая метка разрешена, на первом выходе блока появляется сигнал Смена метки, в противном случае на втором выходе появляется сигнал Ошибка.

Сигнал Смена метки поступает . на второй вход записи регистра 16 контрольной метки, разрешая перезапись кода текущей метки из регистра 17 текущей метки. Таким образом происходит смена контрольной метки аппаратным путем.Следующие текущие метки аналогично сравниваются с новой контрольной меткой.

В случае запрещенного перехода сигнал Ошибка поступает.на второй вход элемента ИЛИ 15, включает блок 20 индикации и поступает на вьрсод 2 устройства для снятия готовности МП-системы.

Блок 19 ассоциативной памяти работает следующим образом.

Одновременно коды контрольной и текущей меток поступают соответственно на первый ij второй информационные входы блока. Код контрольной метки является адресом, для п элементов 22.1, 22.2 ... 22.n ППЗУ, в ячейках которых по afoMy адресу хранится n меток, переходы в Кото рые из контрольной метки разрешены графом переходов. Из П элементов

Если текущая метка совпадает с меткой, разрешенной графом переходов, то на выходе элемента 23, i сравнения появится сигнал, поступающий Hai -и вход элемента ИЛИ 24, с выхода, которого сигнал проходит через элемент И 25, открытый по второму входу сигналом с входа запуска блока на первый выход блока как сигнал разрешения смены метки Если текущая метка не сравнивалась ни с одной из и меток (что означает попытку программы выполнить запрещенный переход, то сигнал об ошибке с выхода элемента ИЛИ 24 через элемент НЕ 27, элемент И 26 проходит на второй выход блока.

Таким образом, устройство вьщает сигнал ошибки, если измеренное время выполнения программы меньше расчетного; измеренное время выполнения

программы больше расчетногб, а также при попытке программы выполнить запрещенный переход.

Устройство значительно повьш1ает достоверность контроля правильнюсти выполнения программ, что имеет важное значение в управлякнцих вычислительных системах, работающих.в реальном времени.

Дополнительным преимуществом предлагаемого изобретения является применение его в любых синхронных вычислительных системах с одним потоком информации и с постоянными программами.

Предлагаемое устройство для контроля выполнения программы выгодно отличается от прототипа, так как использование новых элементов; регистра контрольной метки, регистра текущей метки, блока сравнения, дешифратора адреса, триггера, дешифратора кода команды и блока ассоциативной памяти обеспечило одновременный контроль выполнения программы по времени в соответствии с временным графом и контроль направления переходов в соответствии с графом переходов, а это, в свою очередь,исключило возможность вьщачи несанкционировангных команд системой управления на объект при сбоях в аппаратуре.

f

Ш

Xj

1

27

r

i

Фиг.1

| Устройство для контроля времени выполнения программ | 1972 |

|

SU439813A1 |

| R.W.Marczynski, e.t.s | |||

| А method for detection of microcomputer malfunctions | |||

| Prace Instytut Podstaw Informatyki, PAN, Warsaw,1978, ..№ 308, p.12, Fig.ll, | |||

Авторы

Даты

1985-08-30—Публикация

1984-03-11—Подача