Изобретение относится к импульсной технике и может быть использовано в системах электрических испытаний изделий радиоэлектроники, а также в системах автоматики и передачи данных.

Целью изобретения является расширение функциональных возможностей за счет генерации как однородного, так и неоднородного имнульсног О процесса пачечного типа, с возможностью управления в широком дианазоне длительностями генерируемых импу„1ьсов и науз между ними, количеством импульсов в пачке, длительностями пауз между пачками.

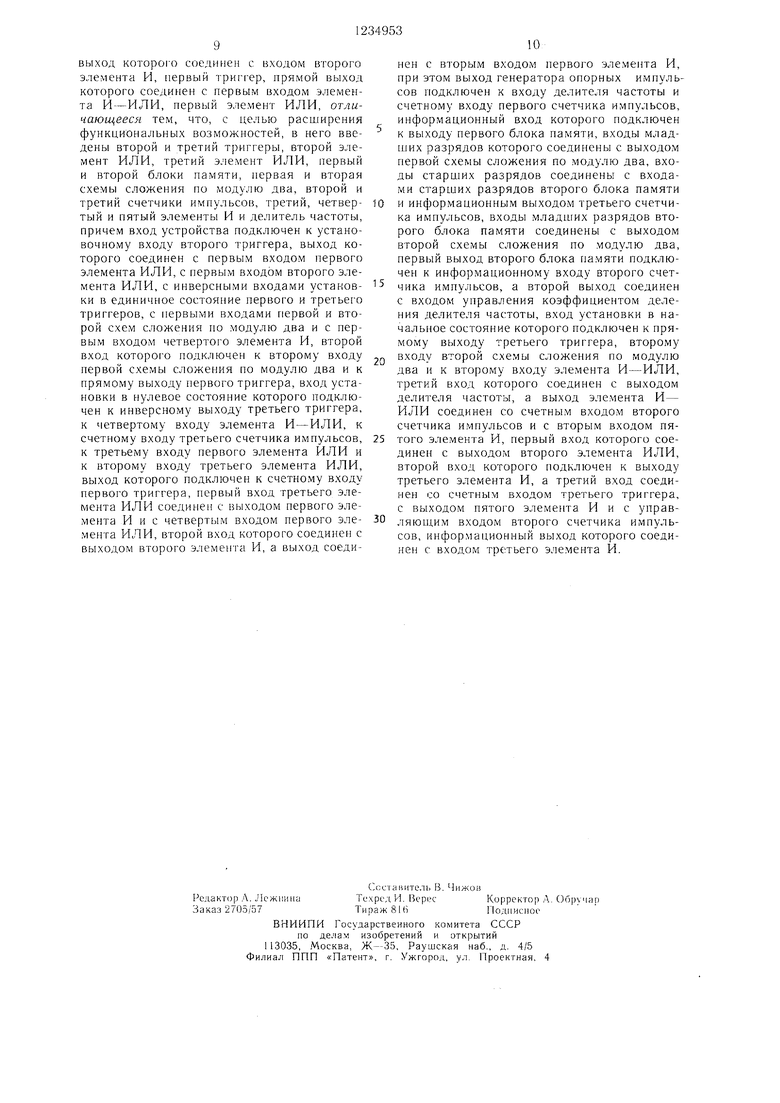

На чертеже представлена функциональная схема устройства для генерации пачек импульсов.

Устройство содержит |-енератор 1 опорных импульсов, первый элемент И 2, первый счетчик 3, второй элемент И 4, первый триггер 5, элемент И - ИЛИ 6, первый элемент ИЛИ 7, второй триггер 8, второй элемент ИЛИ 9, первый блок 10 памяти, первую схему 11 сложения но модулю два, второй блок 12 памяти, второй счетчик 13, третий элемент И 14, третий триггер 15, четвертый 16 и пятый 17 элементы И, вторую схему 18 сложения но модулю два, делитель 19 частоты, третий счетчик 20 и третий элемент ИЛИ 21. Выход генератора 1 опорных импульсов соединен с входом делителя 19 частоты, счетным входом счетчика 3 и первым входом элемента И 2, второй вход которого соединен с выходом эле.аден- та ИЛИ 7, а выход - с входом управления счетчика 3, первым входом элемеп- та ИЛИ 21 и четвертым входом элемеп- та ИЛИ 7. Информационный вход счетчика 3 соединен с выходом блока 10 памяти, а выход --- с входом элемента И 4. Вход установки единичного состояния триггера 5 соединен с прямым выходом триггера 8, входом устаповки едпничпого состояния триггера 15, первыми входами элементов ИЛИ 7 и 9, первыми входами схем 11 и 18 сложения по модулю два и вторым входом элемента И 16, а выход --- с вторым входо.м схемы П сложения по модулю два, первым входом элемента И Hi и юрвым входом элемента И-ИЛИ 6. Выход элемента И 4 соединен с вторым входом элемента ИЛИ 7. Вход триггера 8 является входом устройства. Входы старших разрядов адреса блоков И) и 12 памяти соединены с информационным выходом счетчика 20, входы .члад- Hiero разряда адреса - с выходами соот- ветствешю схем 11 и 18 сложения но модулю два. Выход делителя 19 частоты соединен с третьим входом э. емепта И--ИЛИ 6, второй вход которого соединен с п)ямым выходом триггера 15, вто,рым входом схемы 18 сложения по модулю два и входом установки начального состояния делителя 19 частоты, четвертый вход - с обратным выходо.м триггера 15, а выход -- с счетным входом

счетчика 13 и вторым входо.м элемента И 17, нервый вход которого соединен с выходом элемента ИЛИ 9, а выход - с входо.м управления счетчика 13, счетным входом триггера 15 и третьим входом элемента ИЛИ 9. Информационный выход счетчика 13 соеди- lieH с входом элемента И 14, выход которого соединен с вторым входом элемента ИЛИ 9, информационный вход - с нервым выходом блока 12 памяти, второй выход которого соединен с входом управления коэффициентом деления делителя 19 частоты. Счетный вход триггера 5 соединен с выходом элемента ИЛИ 21, вход установки ну- .левого состояния - с инверсным выходом 1 риггера 15 и вторым входом элемента ИЛИ 21. Третий вход элемента ИЛИ 7 соединен со счетны.м входом счетчика 20 и обратным выходом триггера 15. Вход эле.мен- та И 14 соединен с информационным выходом счетчика 13, а выход - с вторым входом

элемента ИЛИ 9. Выход элемента И 16 является выходом устройства.

Функционирование .устройства нредстав- ляет собой последовательность новторяющих- ся циклов генерации пачек и пауз между пачками, нричем для каждого нового цик- ла задаются свои нараметры: длительности нмнульсов и науз между ними в пачке, количество импульсов в пачке, длительность паузы между данной начкой и следуюндей. Генератор 1 опорных импульсов генерирует последовательность тактовых импульсов устройства и может быть реализован на микросхеме 155АГЗ.

При наличии уровня логического нуля на входе унрав.чения счетчика 3 последний но каждому тактовому импульсу, ностуг аюп.1ему на его счетный вход, увеличивает свое состояние на единицу, нри наличии уровня логической единицы на этом входе в счетчик 3 заносится код, ноступаюший на его информационный вход. Иодобные счетчики имеются в интегральном исполнении, например, 155ИЕ7. Аналогично цЬу ч иионирует и реализуется счетчик 13. Для построения счет- ч Ака 20 также можно ис 1ол;13овать микросхему 155ИЕ7.

Три1 геры 5 и 15 -- счетшле, триггер 8 --

RS-типа. .. 1,ля построения триггеров 5, 8 и 15 можно использовать микросхемы 155ТМ2. Для иостроения блоков 10 и 12 намя- ти можно использоватьмикросхемы

1802ИР1. Ири отсутствии пеобходимости управления параметра.ми 1ачечного неоднородного н.мпульсного процесса в качестве блоков памяти можно использовать ИЗУ, например микросхему 556РТ5.

Первая и вторая схемы 11 и 18 сложения но модулю два могут строиться

на микросхеме .

У элемента И-ИЛИ 6 функцией И объединен нервый вход с вторым, а третий - с четвертым. Первые входы элементов ИЛИ 7

и 9 - инверсные, остальные входы и выходы - прямые.

Делитель 19 частоты предназначен для деления частоты тактовых импульсов во время формирования паузы между пачками импульсов. Используется управляемый делитель частоты, коэффициент деления которого может изменяться в широком диапазоне в соответствии с широким диапазоном изменения длительностей пауз между пачками. В случае значительного превышения длительностью паузы между пачками длительности импульсов в пачке и пауз между ними для формирования длительностей пауз между пачками требуется частота, которая значительно меньше тактовой частоты, в этом случае коэффициент деления делителя частоты должен быть большим. В то же время при малых длительностях пауз между пачками требуется высокая точность их формирования, что требует высокой частоты импульсной последовательности, используе- мой для этой цели, и коэффициент деления делителя 19 частоты в этом случае должен быть небольшим. Делитель 19 частоты реализован на счетчике, например 155ИЕ7, счетный вход которого является первым входом делителя частоты, а поразрядные выходы соединены с входами коммутатора, например 155КП5. На У-входы коммутатора поступает код управления коэффициентом деления, выход коммутатора является выходом делителя частоты. Вход установки нулевого состояния счетчика является более приоритетным по сравнению со счетным входом, и при наличии единичного сигнала на этом входе (вход установки начального состояния делителя частоты) счетчик сохраняет нулевое состояние и импульсы на выход делителя частоты не поступают. При отсутствии сигнала на входе установки начального состояния делителя 19 частоты счетчик делителя частоты осушествляет циклическое суммирование тактовых импульсов, один из выходов этого счетчика согласно коду управления коэф- фициентом деления делителя частоты через коммутатор подключается к выходу делителя частоты. Коэффициент деления такого делителя частоты где М - код управления коэффициентом деления.

Началу работы устройства предшествует режим настройки, включающий в себя запись в блоки 10 и 12 памяти кодов параметров генерируемого импульсного процесса. В первый блок 10 памяти по четным адресам записываются обратные коды длительностей пауз между импульсами, по нечетным - обратные коды длительностей импульсов. Во второй блок 12 памяти записываются параметры пачек: по четным адресам - обратные коды длительностей пауз между пачками и коды управления коэффициентом деления делителя 19 частоты, по нечетным - обратные коды количества импульсов в пачках.

5

0 5 0

5

0 5

0

Всего в блоки 10 и 12 памяти записывается N/2 наборов указанных параметров, где N - объем каждого из блоков памяти.

При использовании в качестве блоков памяти ПЗУ этап записи параметров процесса в блоки памяти исключается.

В исходном состоянии триггер 8 находится в нулевом состоянии, нулевой уровень с его прямого выхода поступает на инверсные вхо- дь установки единичного состояния триггеров 5 и 15, удерживая их в единичном состоянии. Третий счетчик 20 находится в некотором i-M состоянии (), а в счетчики 3 и 13 заносятся обратные коды соответственно длительности импульсов и количества импульсов в пачке i-ro набора параметров, считанные из блоков 10 и 12 памяти по нечетным адресам, старшие разряды которых представляют собой код i-ro состояния счетчика 20, а младшие разряды сформированы на выходах соответственно схем 11 и 18 сложения по модулю два. Запись кода в счетчик 3 осуществляется импульсами с выхода элемента И 2, на первый вход которого поступают импульсы с выхода генератора I опорных импульсов, на второй - уровень единицы с выхода элемента ИЛИ 7, открытого по первому инверсному входу нулевым уровнем с прямого выхода триггера 8. Так как вход управления счетчика 3 является более приоритетным по сравнению со счетныу входом, в момент записи кода прибавления L-ДИНИЦЫ к этому коду не происходит. В счетчик 13 запись кода осуществляется единичным уровнем с выхода элемента И 17, на первый вход которого поступает уровень единицы с выхода элемента И-ИЛИ 6, открытого по первому и второ- .му входам единичными уровнями прямых выходов триггеров 5 и 15, на второй вход - единичный уровень с выхода элемента ИЛИ 9, открытого по первому инверсному входу уровнем нуля, поступающим с прямого выхода триггера 8.

Функционирование устройства начинается по сигналу начала генерации, поступающему на вход устройства и устанавливающему триггер 8 в единичное состояние. Единичный уровень с выхода триггера 8 поступает на инверсный вход первого элемента ИЛИ 7, на выходе которого формируется уровень нуля, закрывающий по второму входу элемент И 2. Нулевой уровень, поступающий с выхода элемента И 2 на вход управления счетчика 3, разрешает работу этого счетчика в режиме счета, и счетчик начинает последовательно увеличивать свое состояние по каждому импульсу, поступающему на его счетный вход с выхода генератора 1 опорных импульсов. При этом единичное состояние триггера 5 через открытый единичным уровнем с выхода триггера 8 элемент И 16 поступает на выход устройства, обусловливая формирование первого импульса первой генерируемой пачки. Кроме того, единичный уровень с выхода триггера 8 через элемент ИЛИ 9 и элемент

ИЛИ 17 разрешает работу счетчика 13 в счетном режиме, и этот счетчик увеличивает свое состояние на единицу в результате поступления на его счетный вход первого формируемого импульса, проходящего с выхода триггера 5 через элемент И-ИЛИ 6, открытый по второму входу уровнем логической единицы с прямого выхода триггера 15. При достижении единиц во всех разрядах счетчика 3 на выходе элемента И 4 формируется сигнал, который через элемент ИЛИ 7 поступает на вход элемента И 2, и по следующему тактовому импульсу с выхода генератора 1 опорных импульсов на его выходе формируется сигнал, по которому в счетчик 3 заносится обратный код длительности паузы i-ro набора параметров, считапный из блока 10 памяти по адресу, старщие разряды которого представляют собой код i-ro состояния счетчика 20, а младший, в данном случае нулевой, разряд сформирован на выходе схемы 11 сложения по модулю два, на первый и второй входы которой к этому моменту поступали единичные уровни с выходов соответственно триггеров 5 и 8. Кроме того, сигнал с выхода элемента И 2 через элемент ИЛИ 21 поступает на счетный вход триггера 5, устанавливая его в нулевое состояние и заканчивая формирование первого импульса заданной длительности в первой генерируемой пачке. В результате записи в счетчик 3 нового кода сигнал с выхода элемента И 4 снимается, однако единичный уровень на выходе элемента ИЛИ 7 поддерживается в течение длительности тактового импульса, поступающего на его четвертый вход с выхода элемента И 2. Элемент И 2, выход которого соединен с входом элемента ИЛИ 7, и элемент ИЛИ 7, выход которого соединен с входом элемента И 2, представляют собой одноступенчатый асинхронный RS-триггер, причем первый, второй и третий входы элемента ИЛИ 7 являются объединенным функцией ИЛИ S-входом, первый вход элемента И 2 - инверсным R-входом, а выход элемента И 2 - обратным выходом триггера. Такая организация необходима для надежной записи в счетчик 3 очередного кода, а также для блокировки счета этого счетчика во время занесения кода, что обеспечивается приоритетностью его входа управления по сравнению со счетным входом. По окончании длительности тактового импульса, осуществляющего через элемент И 2 запись в счетчик 3 обратного кода длительности паузы, сигнал с четвертого входа элемента ИЛИ 7 снимается, и разрешается дальнейшее функционирование счетчика 3 в режиме счета.

Начинается формирование первой паузы между импульсами в пачке, при этом счетчик 3 по каждому тактовому импульсу, поступающему на его счетный вход, последовательно увеличивает свое состояние на единицу. По окончании формирования длительности паузы счетчик 3 снова достига

ет своего максимального состояния, на выходе элемента И 4 появляется сигнал, который, поступая через элемент ИЛИ 7 на второй вход элемента И 2, разрешает

по последующему тактовому импульсу запись в счетчик 3 кода длительности импульса i-ro набора параметров, считанного из блока 10 памяти по адресу, младщий разряд которого сформирован на выходе схемы 11 сложения по модулю два, на первый вход которой поступал единичный сигнал с выхода триггера 8, на второй - уровень нуля с выхода триггера 5. Сигнал с выхода элемента И 2 поступает через элемент ИЛИ 21 на счетный вход триггера 5

и устанавливает последний в единичное состояние, которое передается на выход устройства. Начинается формирование второго выходного импульса аналогично формированию первого. При этом счетчик 13 снова увеличивает свое состояние на единицу. Вза0 имодействие блоков 7, 2 и 3 при занесении кода импульса аналогично описанному.

Процесс генерации импульсов и пауз повторяется до тех пор, пока состояние счетчика 13 не станет максимальным. При достижении состоянием счетчика 13 его максимального значения на выходе элемента И 14 формируется сигнал, который через элемент ИЛИ 9 поступает на первый вход элемента И 17. Следующий импульс, геQ нерируемый устройством, проходит через элемент И-ИЛИ 6 и элемент И 17 на вход управления счетчиком 13, в результате чего в этот счетчик заносится обратный код длительности паузы между пачками для i-ro набора параметров, считанный из блока 12 памяти по адресу, старшие разряды которого представляют код 1-го состояния счетчика 20, а значение младшего разряда, в данном случае нулевое, сформировано на выходе схемы 18 сложения по модулю два, на входы которой поступали единичные уровни с пря0 мых выходов триггеров 8 и 15. Элемент ИЛИ 9 и элемент И 17 так же, как н аналогичные элементы И 2 и ИЛИ 7, представляют собой одноступенчатый асинхронный RS-триг- гер, обеспечивающий надежную запись очередного кода в счетчик 13 в течение длительности импульса, поступающего с выхода элемента И-ИЛИ 6, а также блокировку счета этого счетчика во время занесения кода. Кроме того, импульс с выхода элемента И 17 поступает на счетный вход триггера

0 15 и по его заднему фронту последний устанавливается в нулевое состояние. При этом элемент И-ИЛИ 6 закрывается по второму входу и открывается по четвертому; по положительному перепаду на обратном выходе триггера 15 в счетчик 20 прибавля5 ется единица, формируя код его i-|-l-ro состояния; единичный уровень с обратного выхода триггера 15 через элемент ИЛИ 7 открывает по второму входу элемент И 2.

С входа установки начального состояния делителя 19 частоты единичный сигнал снимается, и на выходе делителя частоты формируется последовательность импульсов с частотой где ff- частота последовательности тактовых импульсов, формируемых генератором 1.

В результате занесения в счетчик 13 нового кода сигнал на выходе элемента И 14 прерывается и счетчик снова работает в режиме счета. Теперь на его счетный вход поступают через открытый по четвертому входу элемент И-ИЛИ 6 импульсы с выхода делителя 19 частоты и начинается формирование длительности паузы между первой и второй пачками импульсов. В то же время импульсы с выхода генератора 1 проходят через открытый по второму входу элемент И 2 на вход управления счетчика 3, занося в него обратный код длительности импульса i-(- 1-го набора параметров, считанный из блока 10 памяти по адресу, сформированному из ко- да i+ 1-го состояния счетчика 20 и младшего разряда, значение которого сформировано на выходе схемы 11 сложения по модулю два из значения нулевого и единичного состояний соответственно триггеров 5 и 8. Вход установки нулевого состояния триггера 5 является более приоритетным по сравнению со счетным входом, и в течение времени формирования длительности паузы между пачками триггер 5 удерживается в нулевом состоянии единичным уровнем с обратного выхода триггера 15. При этом на счетном входе этого триггера присутствует уровень единицы, поступающий через элемент ИЛИ 21 с обратного выхода триггера 15.

В результате последовательного суммирования импульсов, поступающих на счетный вход счетчика 13, последний снова достигает своего максимального состояния, на выходе элемента И 14 формируется сигнал, который открывает через элемент ИЛИ 9 элемент И 17 по второму входу, и следующий импульс с выхода делителя 19 частоты проходит через элемент И-ИЛИ 6 и элемент И 17 на вход управления счетчика 13, заносит в этот счетчик обратный код количества импульсов в пачке импульсов для i+ 1-го набора параметров, а по заднему фронту этого импульса триггер 15 устанавливается в единичное состояние, заканчивая формирование паузы между первой и второй пачками импульсов.

Длительность сформированной паузы

Т,., {fr/2« . К„„

где Knj - код длительности паузы между пачками для i-ro набора параметров. Ири этом единичный сигнал с входа установки нулевого состояния триггера 5 снимается, отрицательный перепад на его счетном входе воспринимается как задний фронт импульса длительностью Т„,, н первый триггер 5 уста- навливается в eдинич ioe состояние.

Вследствие установки единичного состояния триггера 15 элемент И-ИЛИ 6 снова

5

5

0

0

5

5

закрывается по четвертому входу и открывается по второму,элемент И 2 через элемент ИЛИ 7 закрывается по второму входу, счетчик 3 начинает работу в режиме счета, начиная формирование первого импульса второй пачки. Функционирование блоков устройства при генерации второй пачки аналогично их работе при генерации первой пачки. Параметры пачки определяются новым i-|- 1-ым состоянием счетчика 20.

Процесс генерации пачек импульсов и пауз между пачками циклически повторяется. При этом по окончании формирования каждой пачкн счетчик 20 увеличивает свое состояние на единицу, подготавливая переход к новому набору параметров для следующей пачки. Циклически изменяя свое состояние, этот счетчик обеспечивает считывание всех наборов параметров пачек из блоков памяти.

Таким образом, при генерации каждой новой пачки осуществляется переход к новым параметрам - длительности импульсов, пауз между импульсами, количеству импульсов в пачке, длительности паузы между данной пачкой и следующей, что обусловливает неоднородность формируемого импульсного процесса пачечного типа.

Заканчивается процесс генерации пачек при поступлении на вход устройства сигнала окончания генерации, который устанавливает триггер 8 в нулевое состояние. При этом триггеры 5 и 15 устанавливаются в еди- щгчное состояние, элемент И 1 б закрывается но первому входу, н состояние триггера 5 на выход устройства не поступает.

Если заблокировать прибавление единицы в счетчик 20 в конце генерации каждой пачки, то генерируемый импульсный процесс будет однородным. Однородность процесса можно также обеспечить за счет настройки устройства путем записи в блоки памяти одинаковых наб оров параметров по всем парам адресов.

Данное устройство может осуществлять также программный режим работы, если по окончании генерации очередной пачки в третий счетчик принудительно заносить состояние согласно некоторой программе.

Если задавать длительности пауз между пачками, равные длительностям пауз между импульсами в пачках, устройство будет вы- функцл.ч генератора последовательности импульсов с yпpaвляeмы.н1 параметрами.

55

50

Форму.а изобретения

Устройство для генерации пачек импульсов, содержащее генератор опорных нм- ny. ibcoB, выход которого подключен к первому входу первого элемента И, выход KOTOpoi o подключен к входу управления первого счетчика импульсов, информационный

9

выход KOTOpoi O соединен с входом ЕП орого элемента И, первый тригсер, прямой выход которого соединен с первым входом элемента И - ИЛИ, первый элемент ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей, в него нее- дены второй и третий триггеры, второй элемент ИЛИ, третий элемент ИЛИ, первый и второй блоки памяти, первая и вторая схемы сложения по модулю два, второй и третий счетчики импульсов, третий, четвер- тый и пятый элементы И и делитель частоты, причем вход устройства подключен к установочному входу второго триггера, выход которого соединен с первым входом первого элемента ИЛИ, с первым входом второго элемента ИЛИ, с инверсными входами уставов- ки в единичное состояние первого и третьего триггеров, с первыми входами первой и второй схем сложения но модулю два и с первым входом четвертого элемента И, второй вход которого подключен к второму входу первой схемы сложения по модулю два и к прямому выходу первого триггера, вход установки в нулевое состояние которого подключен к инверсному выходу третьего триггера, к четвертому входу элемента И-ИЛИ, к счетному входу третьего счетчика импульсов, к третьему входу первого элемента ИЛИ и к второму входу третьего элемента ИЛИ, выход которого подключен к счетному входу первого триггера, первый вход третьего элемента ИЛИ соединен с выходом первого элемента И и с четвертым входом первого эле- мента ИЛИ, второй вход которого соединен с выходом второго элемента И, а выход соеди

5 5 0

10

нен с вторым входом первого элемента И, при этом выход генератора опорных импульсов подключен к входу делителя частоты и счетному входу первого счетчика импульсов, информационный вход которого подключен к выходу первого блока памяти, входы младших разрядов которого соединены с выходом первой схемы сложения по модулю два, входы старших разрядов соединены с входами стар1пих разрядов второго блока памяти и информационным выходом третьего счетчика импульсов, входы младших разрядов второго блока памяти соединены с выходом второй схемы сложения по модулю два, первый выход второго блока памяти подключен к информационному входу второго счетчика импульсов, а второй выход соединен с входом управления коэффициентом деления делителя частоты, вход установки в начальное состояние которого подключен к прямому выходу третьего триггера, второму входу второй схемы сложения по модулю два и к второму входу элемента И - ИЛИ, третий вход которого соединен с выходом делителя частоты, а выход элемента И- ИЛИ соединен со счетным входо.м второго счетчика импульсов и с вторым входом пятого элемента И, первый вход которого соединен с выходом второго элемента ИЛИ, второй вход которого подключен к выходу третьего элемента И, а третий вход соединен со счетным входом третьего триггера, с выходом пятого элемента И и с управ- ляюп1.им входом второго счетчика импульсов, информационный выход которого соединен с входом третьего элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель частоты заполнения радиоимпульсов | 1982 |

|

SU1161892A1 |

| Генератор случайного процесса | 1986 |

|

SU1427365A1 |

| Стохастический преобразователь | 1981 |

|

SU1056191A1 |

| Устройство задержки импульсов | 1981 |

|

SU1019611A1 |

| Генератор случайного процесса | 1986 |

|

SU1436113A1 |

| Генератор случайного процесса | 1986 |

|

SU1429113A1 |

| Генератор нестационарного случайного импульсного процесса | 1987 |

|

SU1587501A1 |

| Генератор случайных процессов | 1981 |

|

SU985786A1 |

| Генератор случайного процесса | 1986 |

|

SU1432515A1 |

| Генератор серий импульсов | 1979 |

|

SU864514A1 |

Изобретение может использоваться в системах электрических испытаний изделий радиоэлектроники, а также в системах автоматики и передачи данных. Цель изобретения - расширение функциональных возможностей - достигается путем генерации как однородного, так и неоднородного импульсного процесса при генерировании пачек импульсов с возможностью управления в широком диапазоне длительностями генерируемых и.мпульсов и пауз между ними, а также количеством импульсов в пачке и длительностями пауз между пачками. Устройство содержит генератор I опорных импульсов, эле.менты И 2, 4, 14, I6 и 17, триггеры 5, 8 и 15, счетчики 3, 13 и 20, элемент И - ИЛИ 6, элементы ИЛИ 7, 9 и 21, блоки памяти 10 и 12, схемы сложения по модулю два И и 18, делитель 19 частоты. В устройстве предусматривается запрограммированный режим работы, если по окончании генерации очередной пачки в третий счетчик принудительно заносить состояние согласно некоторой программе. I ил. в (Л ю со со ел ОО

| Устройство для генерации пачек импульсов | 1981 |

|

SU982186A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-05-30—Публикация

1984-08-13—Подача