Изобретезше относи гс;- i; -.ы гмсли- тельной технике и может быть нслюпъ- зовано при построении имитац;ион 1о-мо- депирующей аппаратуры для ремиепия за- дач оптимизации структурно сложных систем испытаний изделий на ударные, электрические и другие воздействия,,

Цель изобретения - . поиыщещхе ности генератора.

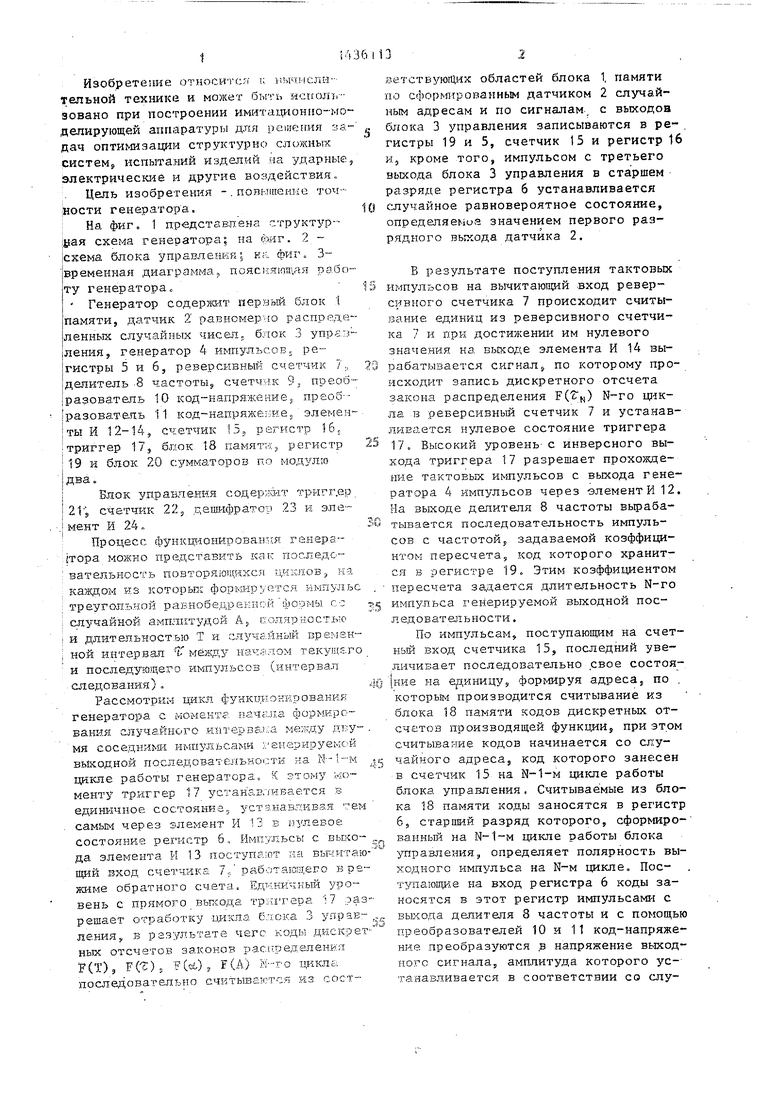

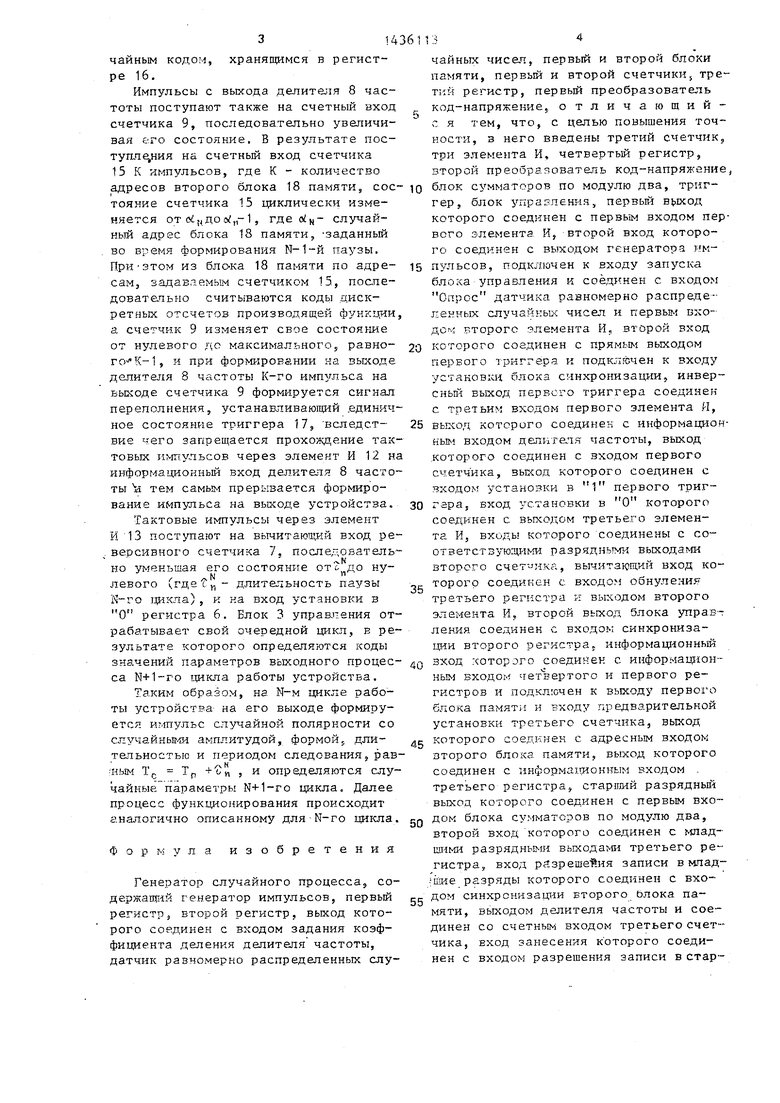

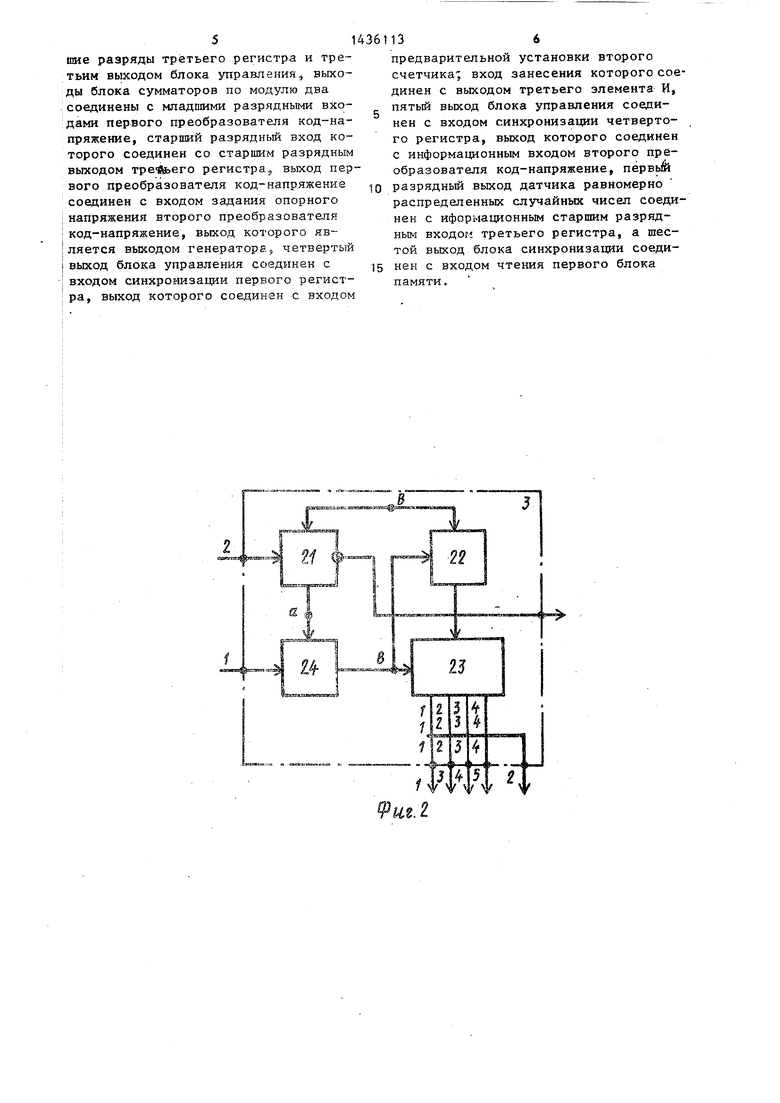

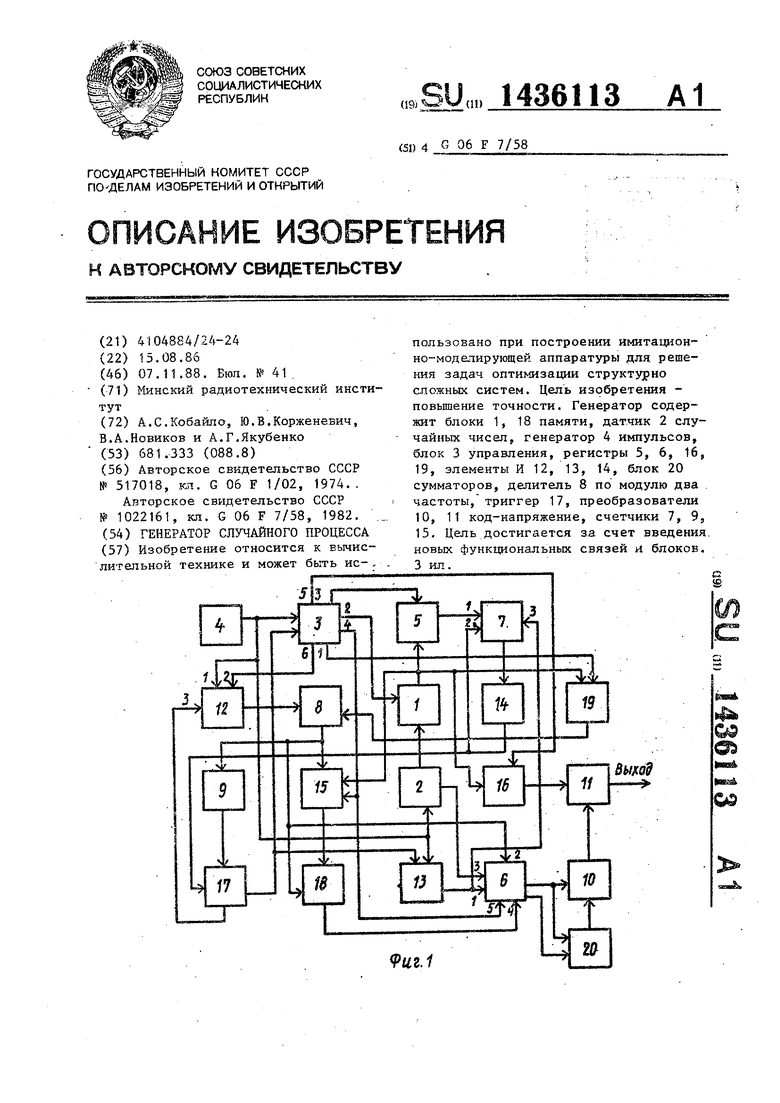

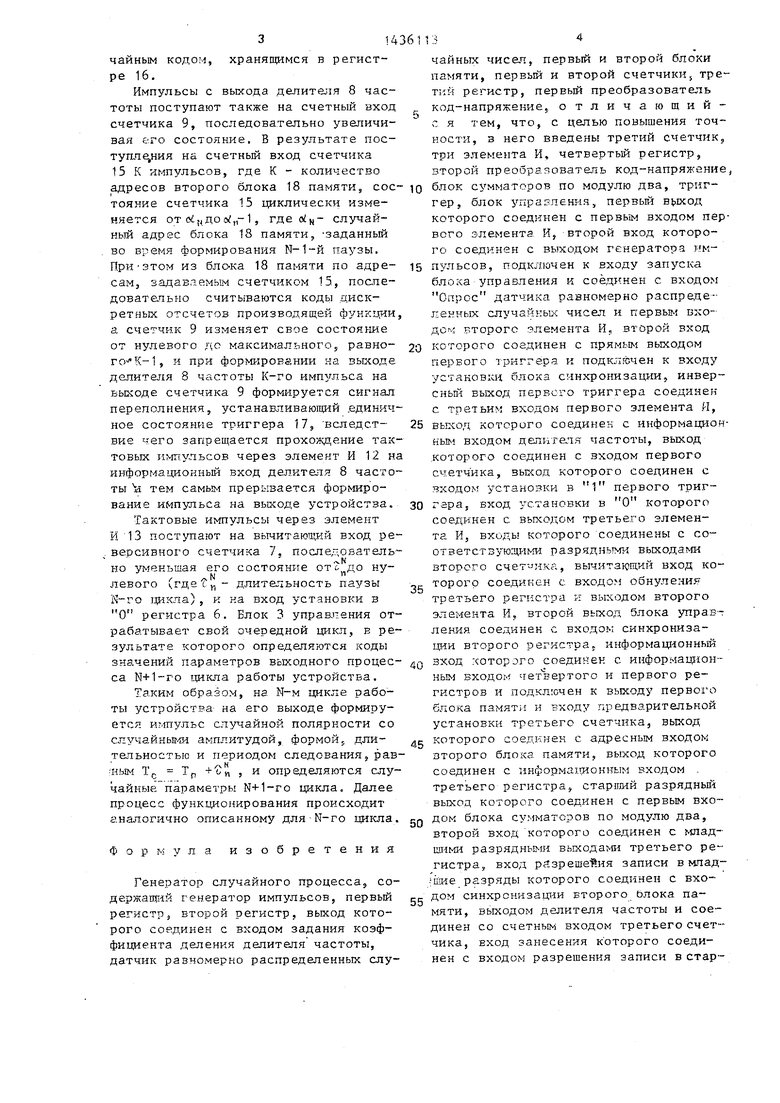

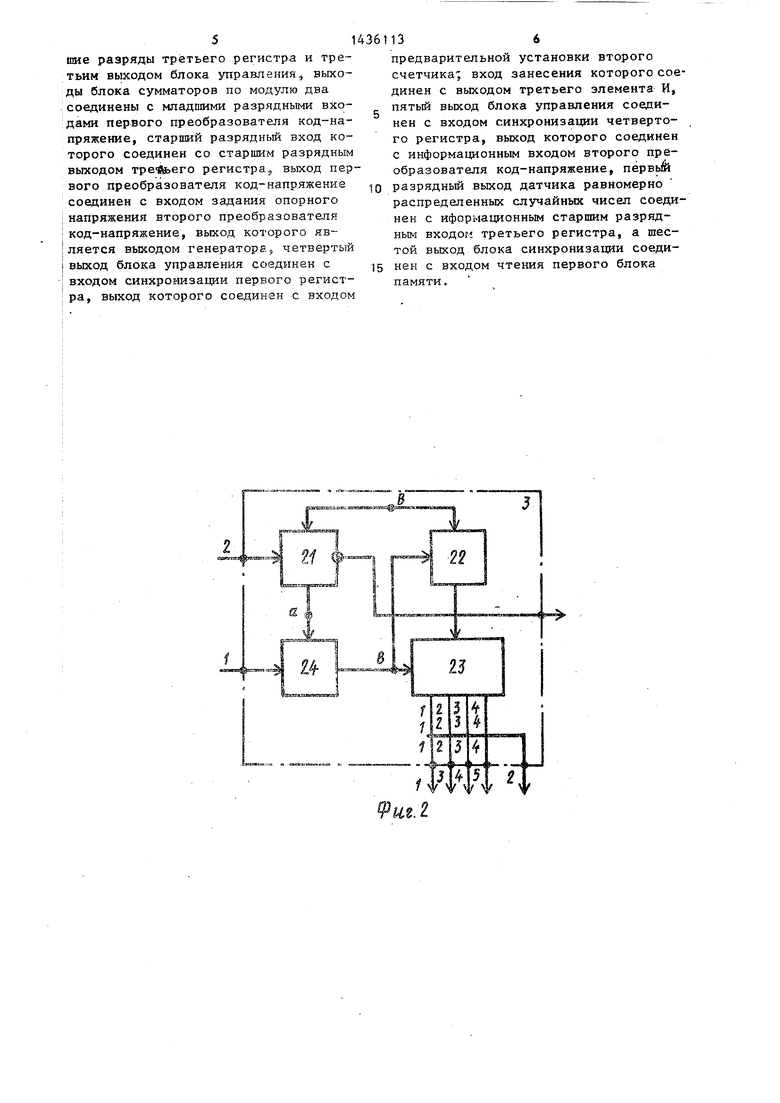

На фиг. 1 представлена структур- 1уая схема генератора; на Фиг. 2 - |сзгема блока управленкя; к;;, фиг, 3-- шременная диаграмма., поясияюш.дя работу генератора

Генератор содерлшт первьй блок памяти, датчик 2 равномерно распреде- |ленных случайных чисел, блок 3 упраз|ления, генератор 4 импульсов,, ре- {гистры 5 и б, реверсивный счетчик 7,, |делитель-8 4acTOTbij счетчик 9, преоб- |разоватепь 10 код-напряжение иреоб- {разоватеяь 11 код-напряжениеj элемен- I ты И 12-14, счетчик 15, регистр iGj I триггер 17, блок 18 памяп-:;, регистр I 19 и блок 20 сумматоров по модул:о два.

Блок угфавлення содернмт тригг.ер 21 s счетчик 22 э дешифратор 23 и элемент И 24„

Процесс функционирован-ш генера- тора можно представить как последекаждом из которьк формируется треугольной равнобедрекной формы со случайной амплитудой А, 1:;олярнос Г:ью и длительностью Т и случайный Бре.ен-- ной интерв.ал ч между нз.ч. текущг.го и последующего импульсов (интервал- следования) ,

Рассмотрим цикл ФУНКЦИОНЕРованкя генератора с моментг начала формирования случайного интервал..:а ме;5-ду дву- мя соседними и rayльcaми генерируемой выходной последоватео гьно1:.ти на. N--1--M цикле работы генератора, К этому моменту триггер 17 устан ав, 1ИБается з единичное состояние; устанавливая тем самым через элемент И 13 в нулевое состояние регистр 6, Импульсы с вько- да элемента И 13 поступашт на вычитаю щнй зход счетчика 7,/ рабатаю)-дего в режиме обратного счета. Единичный уровень с прямого вьщода триггера 17 оаз решает отработку ЦИКла блока 3 управ- ления,, в результате чего коды дискрет ньк отсчетов законов расг.ределения (Т), РСб). (oi,), F(A) й-ro дикла последовательно считываются из состветствующих областей блока 1, памяти по cs pophfflpoBaHHbiM датчиком 2 случай- ным адресам и по сигналам., с выходов блока 3 управления записываются в ре- гистры 19 и 5, счетчик 15 и регистр 1 и, кроме того, импульсом с третьего выхода блока 3 управления в старшем разряде регистра 6 устанавливается с:лучайное равновероятное состояние, определяеыиа значением первого разрядного выхода датчика 2.

В результате поступления тактовых импзшьсов на вычитающий вход реверсивного счетчика 7 происходит считывание единиц из реверсивного счетчика 7 и при достижении им нулевого значения на выходе элемента И 14 вырабатывается сигнаЛр по которому происходит запись дискретного отсчета закона распределения ) ip-iK- ла в реверсивный счетчик 7 и устанавливается нулевое состояние триггера 17. Высокий уровень с инверсного выхода триггера 17 разрешает прохождение тактовых импульсов с выхода генератора 4 импульсов через элемент И 12. На выходе делителя 8 частоты вьфаба- тывается последовательность импульсов с частотой задаваемой коэффици- нтом пересчета, код которого хранится в регистре 19 Этим коэффициентом пересчета задается длительность N-ro импульса генерируемой выходной последовательности „

По импульсам, поступающим на счет- НЬ1Й вход счетчика 15, последний увеличивает последовательно свое состоя- ние на ер,иницу,, формируя адреса, по . которым производится считывание кз блока 18 памяти кодов дискретных отсчетов производящей функции, при этом считывание кодов начинается со сп:у- чайного адреса, код которого занесен в счетчик 15 на цикле работы блока управления. Считываемые из блока 18 памяти коды заносятся в регистр 6, старший разряд которого, сформированный на N-1-м цикле работы блока управления,, определяет полярность выходного импульса на N-M цикле,, Пос- тупающи.е на вход регистра 6 коды заносятся в этот регистр импульсами с вьЕсода делителя 8 частоты и с помощью преобразователей 10 и 11 код-напряжение преобразуются ,в напряжение выходного сигнала, амплитуда которого устанавливается в соответствии со слу314361

чайным кодом, хранящимся в регистре 16.

Импульсы с выхода делителя 8 частоты поступают также на счетный вход счетчика 9, последовательно увеличивая его состояние, В результате пос на счетный вход счетчика 15 К импульсов, где К - количество адресов второго блока 18 памяти, сое- Q тояние счетчика 15 циклически изменяется от oi;4 доэ/г,-1, где случайный адрес блока 18 памяти, -заданный

во время формирования N-1-й паузы. При ЭТОМ из бло-ка 18 памяти по адре- 15 сам, задаваемым счетчиком 15, поспе- доватепьно считьгваются коды дискретных отсчетов производящей функции, а счетчик 9 изменяет свое состояние от нулевого до максимальногоj равно- 20 , и при формировании на выходе делителя 8 частоты К-го импульса на выходе счетчика 9 формируется сигнал переполнения, устанавливающий .единичное состояние триггера 17, вследст- 25 вне чего загфещается прохождение тактовых импульсов через элемент И 12 на информа.ционньм вход делителя 8 частоты тем самьм прерывается формирование импульса на выходе устройства, зо

Тактовые импульсы через элемент И 13 поступают на вычитающий вход реверсивного счетчика 7, последовательно уменьшая его состояние нулевого (,- длительность паузы „ дакла) , и ка вход установки в О регистра 6. Блок 3 управления отрабатывает свой очередной цикл, в результате которого определяются коды значений параметров выходного продес- Q са N+1-го тщкла работы устройства.

Таким образом, на N-M цикле работы устройства на его выходе формируется импульс случайной полярности со случайныг4И амплитудой, формой дли- д тельностыо и периодом следования, рав- HbSM Tf. Тр + ьп , и определяются случайные параметры N+1-го цикла. Далее процесс функционирования происходит налогично описанному для-N-ro цикла.

50

Формула изобретения

Генератор случайного процесса, содержащий генератор импульсов, первый регистрэ второй регистр, выход которого соединен с входом задания коэффициента деления делителя частоты, датчик равномерно распределенных

5 0 5 о

Q

0

g

чайных чисел, первый и второй блоки памяти, первый и второй счетчики третий регистр, первый преобразователь код-напряжение отличающий- с я тем, что, с целью повышения точности, в него введены третий счетчик три элемента И, четвертьй регистр, второй преобразователь код-напряжение, блок сумматоров по модулю два, триггер, блок управления, первьм которого соединен с первым входом первого элемента. И, второй вход которого соединен с выходом генератора импульсов, подключен к входу запуска блоха управления и соединен с входом Опрос датчика равномерно распре,де- ленных случайкьк чисел и первым входом второго элемента И, второй вход которого соединен с прямым выходом первого триггера и подклгочен к входу установки блока синхронизации, инвер- сньш выход первого триггера соединен с третьим входом первого элемента Я, выход которого соединен с информационным, входом делителя частоты, выход .которого соединен с входом первого счетчика, вькод которого соединен с входом установки в 1 первого триг- гара, вход установки в О которого соединен с выходом третьег о элемента И, входы которого соединены с соответствующими разр.ядными вьгходами второго счет - нка, вычитающий вход которого соединен с входом обнуления третьего periiCTpa и выходом второго эле-мента И, второй выход блока управ- ления соединен с входом синхрониза- даи второго регистра информационный вход которого соединен с информационным входом чет вертого и первого регистров и подключен к выходу первох о блока памяти и входу предварительной установки третьего счгтчика, выход которого соединен с адресным входом второго блока памяти, выход которого соединен с информахшонным входом . третьего регистра, стармий разрядньй выход которого соединен с первым входом блока сумматоров по модулю два, второй вход которого соединен с младшими разрядными выходами третьего регистра, вход разрешения записи в млад- .1ше разряды которого соединен с входом синхронизации второго Ьлока памяти, выходом делителя частоты и соединен со счетным входом третьего счетчика, вход занесения которого соединен с входом разрешения записи в стар51

шие разряды третьего регистра и третьим выходом блока управления, выходы блока сумматоров по модулю два соединены с младшими разрядными входами первого преобразователя код-напряжение, старший разрядный вход которого соединен со старшим разрядным выходом Tpeiteero регистра,, выход первого преобразователя код-напряжение соединен с входом задания опорного I напряжения второго преобразователя i код-напряжение, выход которого яв- Iляется выходом генератора, четвертый I выход блока управления соединен с входом синхронизации первого регистра, выход которого соединен с входом

0

5

136

предварительной установки второго счетчика ; вход занесения которого соединен с выходом третьего элемента И, пятый выход блока управления соединен с входом синхронизации четвертого регистра, выход которого соединен с информационным входом второго преобразователя код-напряжение, первьЙ разрядный выход датчика равномерно распределенных случайных чисел соединен с ифорыационньм старшим разрядным входом третьего регистра, а шестой выход блока синхронизации соединен с входом чтения первого блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайного процесса | 1986 |

|

SU1432515A1 |

| Генератор случайного процесса | 1986 |

|

SU1429113A1 |

| Генератор случайного процесса | 1986 |

|

SU1427365A1 |

| Генератор случайного процесса | 1985 |

|

SU1739374A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Генератор случайного процесса | 1983 |

|

SU1113800A1 |

| Генератор случайного процесса | 1983 |

|

SU1100622A1 |

| Генератор случайного процесса (его варианты) | 1983 |

|

SU1125624A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Стохастический преобразователь | 1981 |

|

SU1056191A1 |

Изобретение относится к вычислительной технике и может быть ис-пользовано при построении имитацион- но-моделирующей аппаратуры для решения задач оптимизации структурно сложных систем. Цель изобретения - повышение точности. Генератор содержит блоки 1, 18 памяти, датчик 2 случайных чисел, генератор 4 импульсов, блок 3 управления, регистры 5, 6, 16, 19, элементы И 12, 13, 14, блок 20 сумматоров, делитель 8 по модулю два . частоты, триггер 17, преобразователи 10, 11 код-напряжение, счетчики 7, 9, 15. Цель достигается за счет введения, новых функциональных связей и блоков. 3 ил.

Bxodi .г.з

| Генератор случайного импульсного процесса | 1974 |

|

SU517018A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор случайного процесса | 1982 |

|

SU1022161A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-07—Публикация

1986-08-15—Подача