I

Изобретение относится к аппаратуре выделения геофизической информа ции, принимаемой на фоне помех,,сравнимых по амплитуде с полезным сигналом и может быть применено, например, в сейсморазведке при использова Нин слабых воздействий, возбуждаемых невзрывными источниками.

Цель Р13обретения - расширение функциональных возможностей и повышение помехоустойчивости.

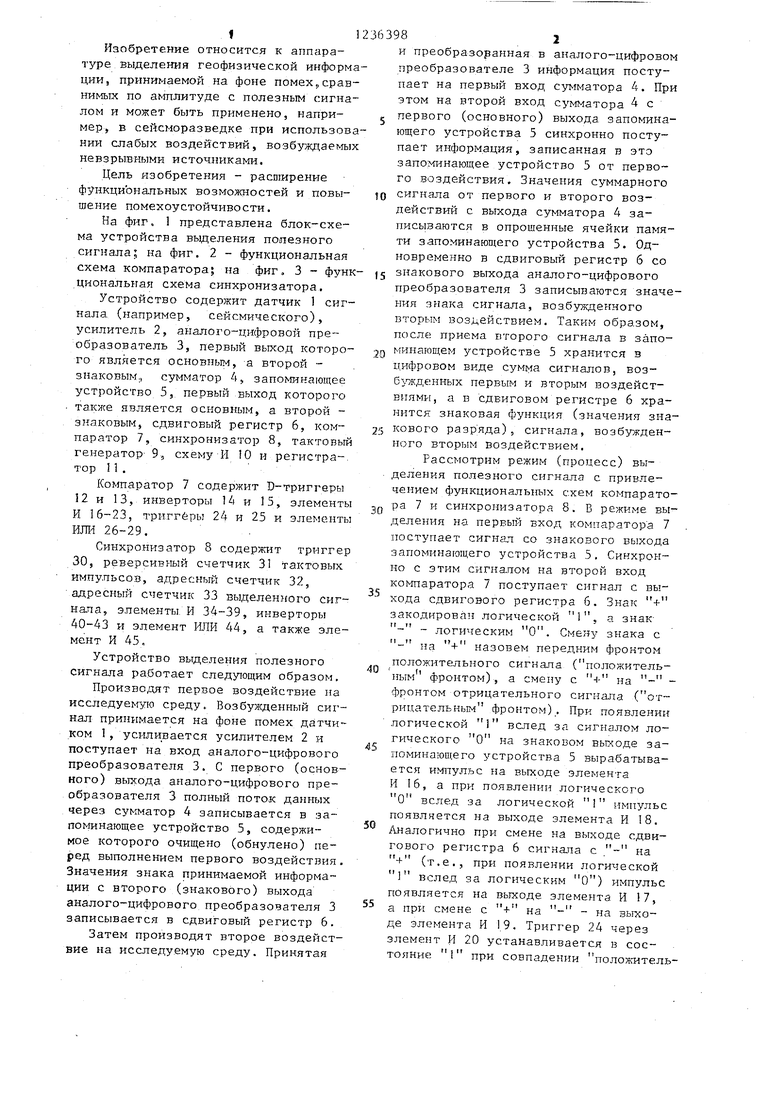

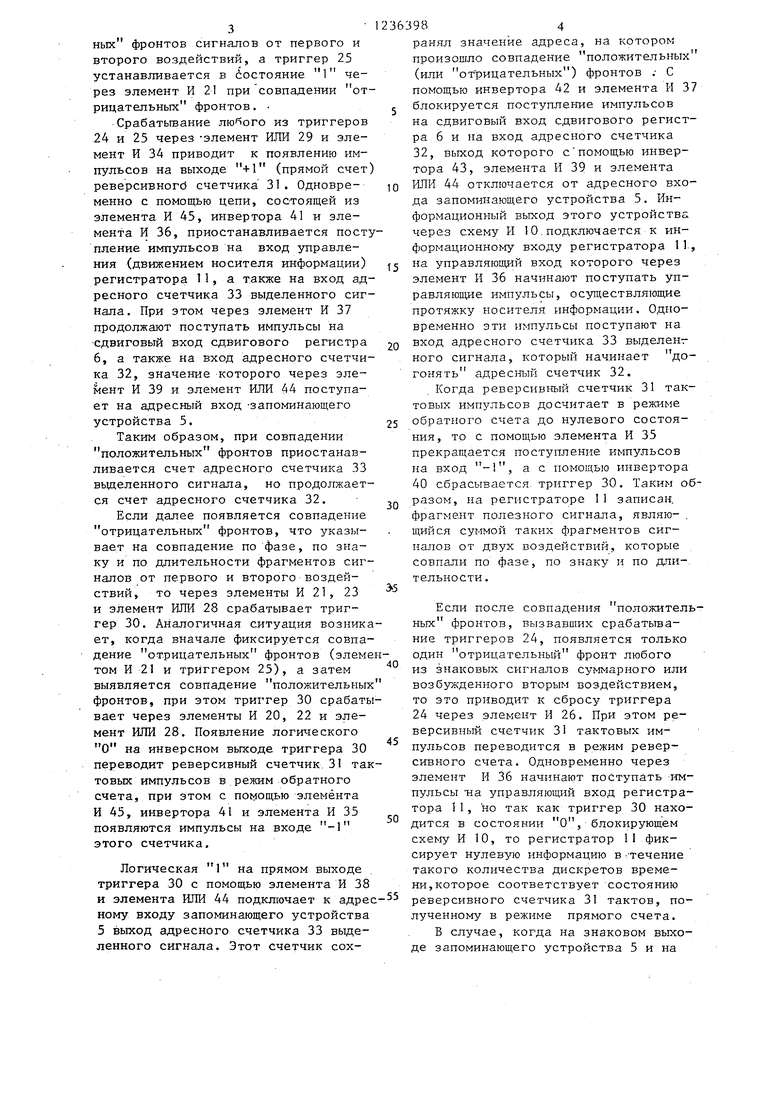

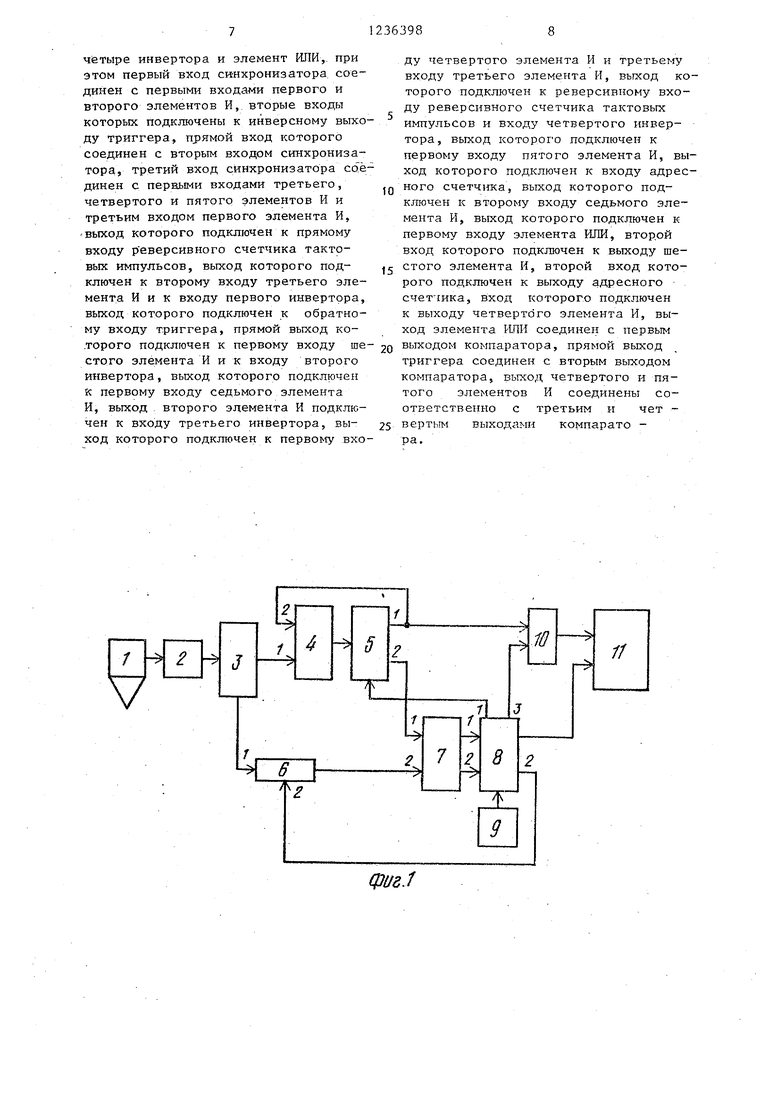

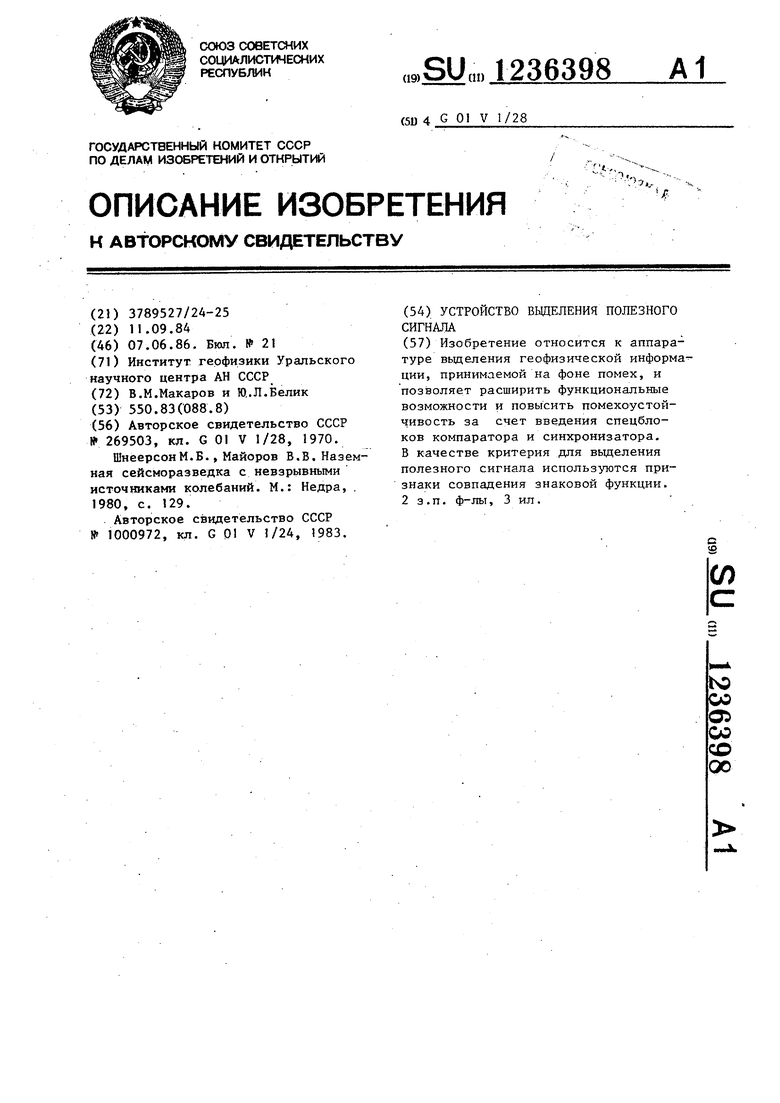

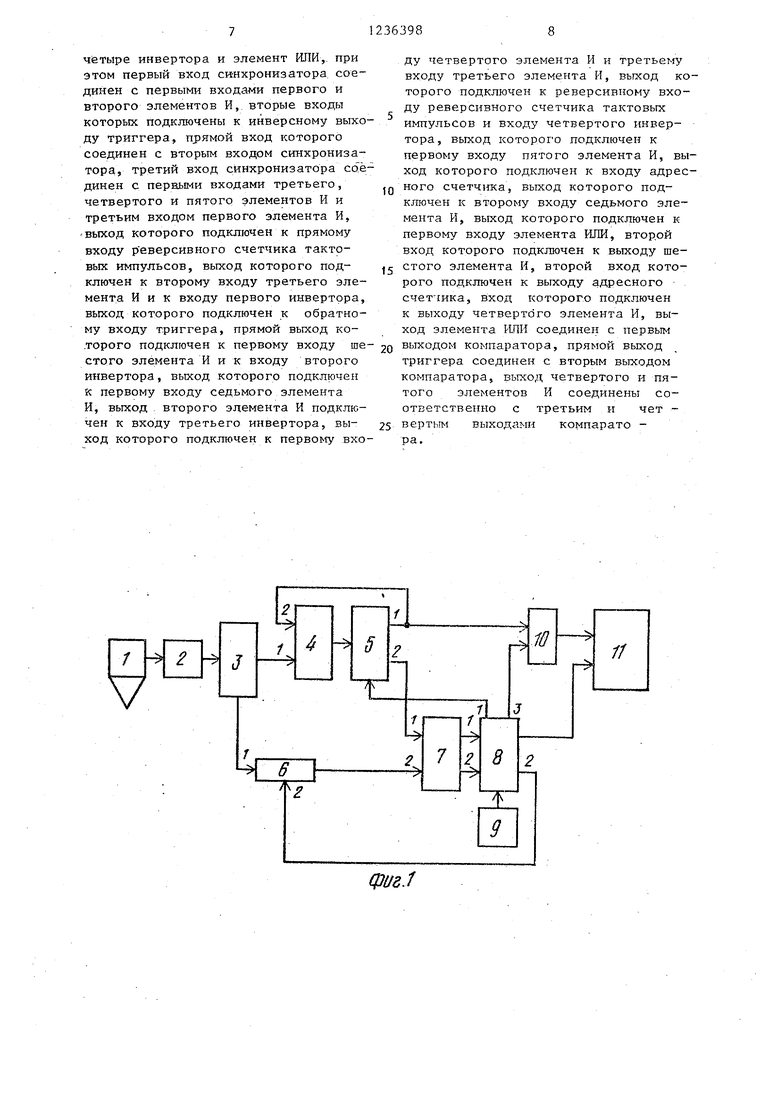

На фиг. 1 представлена блок-схема устройства выделения полезного сигнала; на фиг. 2 - функциональная схема компаратора; на фиг, 3 - функ циональная схема синхронизатора.

Устройство содержит датчик 1 сигнала (например, сейсмического), усилитель 2, аналого-цифровой преобразователь 3, первый выход которого является основньгм, а второй - знаковым., сумматор 4, запоминающее устройство 5, первый выход которого также является основным, а второй - знаковым, сдвиговый регистр 6, компаратор 7, синхронизатор 8, тактовый генератор 9, схему И 10 и регистра-, тор П .

Компаратор 7 содержит D-триггеры 12 и 13, инверторы 14 и 15, элементы И 16-23, триггеры 24 и 25 и элементы ИЛИ 26-29.

Синхронизатор 8 содержит триггер 30, реверсивный счетчик 31 тактовых импу.пьсов, адресный счетчик 32, адресный счетчик 33 выделенного сигнала, элементы. И 34-39, инверторы 40-43 и элемент ЮТИ 44, а также элемент И 45.

Устройство выделения полезного сигнала работает следуюпщм образом.

Производят первое воздействие на исследуемую среду. Возбужденный сигнал принимается на фоне помех датчиком 1, усиливается усилителем 2 и поступает на вход аналого-цифрового преобразователя 3. С первого (основного) выхода аналого-цифрового преобразователя 3 полный пото.к данных через сумматор 4 записывается в запоминающее устройство 5, содержимое которого очищено (обнулено) перед выполнеш-гем первого воздействия. Значения знака принимаемой информации с второго (знакового) выхода аналого-цифрового преобразователя 3 записывается в сдвиговый регистр 6.

Затем производят второе воздействие на исследуемую среду. Принятая

363982

и преобразованная в аналого-цифровом преобразователе 3 информация поступает на первый вход сумматора 4. При этом на второй вход сумматора 4 с

g первого (основного) выхода запоминающего устройства 5 синхронно поступает информация, записанная в это запоминающее устройство 5 от первого воздействия. Значения суммарного

IQ сигнала от первого и второго воздействий с выхода сумматора 4 записываются в опрошенные ячейки памяти запоминающего устройства 5. Одновременно в сдвиговый регистр б со (5 знакового выхода аналого-цифрового

преобразователя 3 записываются значения знака сигнала, возбуткденного вторым )зоздействием. Таким образом, после приема второго сигнала в запоy-j минающем устройстве 5 хранится в цифровом виде сумма сигналов, воз- б ткденных первым и вторым воздействиями, а в сдвиговом регистре 6 хранится: знаковая функция (значения зна2/5 кового разряда) 5 сигнала, возбужденного вторым воздействием.

Рассмотрим режим (процесс) выделения полезного сигнала с привлечением функциональных схем компаратора 7 и синхронизатора 8. В режиме выделения на первый вход компаратора 7 поступает сигнал со знакового выхода запоминающего устройства .5. Синхронно с этим сигналом на второй вход компаратора 7 поступает сигнал с вы- хода сдвигового регистра 6. Знак + закодирован логической 1, а знак - - логическим О. Смену знака с

30

- на + назовем передним фронтом положительного сигнала (положительным фронтом), а смену с ч- на - - фронтом отрицательного (отрицательным фронтом). При появлении логической i вслед за сигналом логического О на знаковом выходе запоминающего устройства 5 вырабатывается импульс на выходе элемента И 16, а при появлении логического О вслед за логической импульс появляется на выходе элемента И 18. / лалогично при смене на выходе сдвигового регистра 6 сигнала с - на + (т.е., при появлении логической 1 вслед за логическим О) импульс появляется на выходе элемента И 17, а при смене с + на - - на выходе элемента И 19. Триггер 24 через элемент И 20 устанавливается в состояние i при совпадении положитель3

ных фронтов сигналов от первого и второго воздействий, а триггер 25 устанавливается в состояние 1 через элемент И 21 при совпадении отрицательных фронтов,

Срабатывание из триггеров 24 и 25 через -элемент ИДИ 29 и элемент И 34 приводит к появлению импульсов на выходе +1 (прямой счет) реверсивногб счетчика 31. Одновременно с помощью цепи, состоящей из элемента И 45, инвертора 41 и элемента И 36, приостанавливается поступление импульсов на вход управления (движением носителя информации) регистратора 11, а также на вход адресного счетчика 33 выделенного сиг- Нала. При этом через элемент И 37 продолжают поступать импульсы на сдвиговый вход сдвигового регистра 6, а также на вход адресного счетчика 32, значение которого через элемент И 39 и элемент ИЛИ 44 поступает на адресный вход -запоминающего устройства 5.

Таким образом, при совпадении положительных фронтов приостанавливается счет адресного счетчика 33 выделенного сигнала, но продолжается счет адресного счетчика 32.

Если далее появляется совпадение отрицательных фронтов, что указывает на совпадение по фазе, по знаку и по длительности фрагментов сигналов от первого и второго воздействий, то через элементы И 21, 23 и элемент ИЛИ 28 срабатывает триггер 30. Аналогичная ситуация возникает, когда вначале фиксируется совпадение отрицательных фронтов (элеметом И 21 и триггером 25), а затем выявляется совпадение положительных фронтов, при этом триггер 30 срабатывает через элементы И 20, 22 и элемент ИЛИ 28. Появление логического О на инверсном выходе триггера 30 переводит реверсивный счетчик 31 тактовых импульсов в режим обратного счета, при этом с помощью элемента И 45, инвертора 41 и элемента И 35 появляются импульсы на входе -1 этого счетчика.

Логическая 1 на прямом выходе триггера 30 с помощью элемента И 38 и элемента ИЛИ 44 подключает к адресному входу запоминающего устройства 5 выход адресного счетчика 33 вьще- ленного сигнала. Этот счетчик сох363984

ранял значение адреса, на котором произошло совпадение положительных (или от рицательных) фронтов . С помощью инвертора 42 и элемента И 37 с блокируется поступление импульсов на сдвиговый вход сдвигового регистра 6 и на вход адресного счетчика 32, выход которого с помощью инвертора 43, элемента И 39 и элемента

10 ИЛИ 44 отключается от адресного входа запоминающего устройства 5. Информационный выход этого устройства через схему И 10.подключается к информационному входу регистратора 11,

12 на управляющий вход которого через элемент И 36 начинают поступать уп- равляюцц е импульсы, осутдествляющие протяжку носителя информации. Одновременно эти импульсы поступают на

Q вход адресного счетчика 33 выделенг ного сигнала, который начинает догонять адресшл счетчик 32.

Когда реверсивный счетчик 31 тактовых импульсов досчитает в реяшме

5 обратного счета до нулевого состояния, то с помощью элемента И 35 прекращается поступление импульсов на вход -1, а с помощью инвертора 40 сбрасывается, триггер 30. Таким обQ разом, на регистраторе 1 1 записан, фрагмент полезного сигнала, являющийся суммой таких фрагментов сигналов от двух воздействий, которые совпали по фазе, по знаку и по дли-.

тельности. б

Если после совпадения положительных фронтов, вызвавших срабатывание триггеров 24, появляется только один отрицательный фронт любого из знаковых сигналов сз ммарного или возбужденного вторым воздействием, то это приводит к сбросу триггера 24 через элемент И 26. При этом реверсивный счетчик 31 тактовых импульсов переводится в режим реверсивного счета. Одновременно через элемент И 36 начинают поступать I-TM- пульсы iia управляющий вход регистратора 11, но так как триггер 30 нахо- дится в состоянии О, блокирующем схему И 10, то регистратор II фиксирует нулевую информацию в течение такого количества дискретов времени, которое соответствует состоянию реверсивного счетчика 31 тактов, полученному в режиме прямого счета.

В случае, когда на знаковом выходе запоминающего устройства 5 и на

0

5

выходе сдвигового регистра 6 нет совпадений ни положительных, ни отрицательных фронтов сигналов, реверсивный счетчик 31 находится в состоянии О, при этом на регистраторе записывается нулевая информация синхронно с работой запоминающего устройства 5 и сдвигового регист- ра 6.

В результате опроса всех адресов запоминающего устройства 5 на регистраторе 11 фиксируется информация, представляющая собой принимаемый сигнал, из которого исключены поме- хи и выделены фрагменты, содержащие полезный сигнал с полным воспроизведением его формы, пои этом выделенный сигнал равен по величине сумме двух принятых. Далее производят новый цикл, состоящий из двух возбуждений и приемов сигналов. Сравнивая заре- гистррфованный результат этого цикла с результатом первого цикла, делают вывод о необходимости продол- жения наблйдений в данной точке профиля ,

Формула изобретения

. Устройство выделения полезного сигнала, содержащее последовательно соеднненгше сейсмодатчики, усилитель и аналого-цифровой преобразователь, а также запоминающее устройство,, тактовый генератор и ре- гистратор, отличающееся тем, что, с целью расщирения.функциональных возможностей и повышения помехоустойчивости, в него введены компаратор, синхронизатор, схема И, сдвиговый регистр и сумматор, первы вход которого подключен к первому выходу, аналого-цифрового преобразователя, второй вход - к первому выходу запомийающего устройства, связанному с первым входом.схемы И,а выход сумматора - к информационному входу запоминающего устройства, адресный вход которого подключен к первому выходу синхронизатора, второй выхрд запоминающего устройства - к первому входу компаратора, первый- и второй выходы которого соединены соответственно с первьм и вторым . входами синхронизатора, а второй вход компаратора - с выходом сдвигового регистра/ первый вход которого подключен к второму выходу ана

Q

5

0

5

0

лого-цифрово го преобразователя, а второй вход - к второму выходу синхронизатора, третий вход которого соединен с выходом тактового генератора, а третий выход - с вторым входом схемы И, выход которой подключен к первому )зходу регистратора, вход ,которого присоединен к четвертому выходу синхронизатора.

2.Устройство по п. I, отличающееся тем, что компара- т ор содержит два D-триггера, два инвертора, восемь элементов И, два триггера и четыре элемента lilffl, при этом входы компаратора соединены с входами соответствующих инверторов, D-триггеров и с первыми входами соответственно первого и второго элем.ен- тов И, вторые входы которых подключены к инверсным выходам соответст- вуюшлх D-триггеров, прямые выходы которых подключены к первым входам соответственно третьего и четвертого элементов И, вторые входы которых соединены с выходами соответственно первого и второго инверторов, выход первого элемента И подключен к первым входам первого элемента ИЛИ и пятого элемента И, вторые входы которых соединены с выходом второго элемента И, выход третьего элемента И подключен к первым входам второго элемента ИЖ и шестого элемента И, вторые входы которых соединены с выходом четвертого элемента И, выходы пятого и шестого элементов И подключены к первым входам соответственно седьмого и восьмого элементов И и к прямым входам соответствующих р-триг- Геров, обратные входы которых подключены к выходам соответственно первого и второго элементов ИЛИ, прямые выходы D-триггеров подключены к входам третьего элемента 1-ШИ и к вторым входам соответственно седьмого и восьмого элементов И, выходы которьпс подключены к входам четвертого элемента ИЛИ, выход третьего элемента

ИЛИ соединен с первым выходом компаратора., а выход четвертого элемента ИЛИ соединен с вторым выходом компаратора,,

3.Устройство по пп. I и 2, о т - л и ч а ю щ е е с я тем, что синхронизатор содержит триггер, реверсивный счетчик тактовых импульсов, адресный счетчик, адресный счетчик выделенного сигнала, семь элементов И

четыре инвертора и элемент ИЛИ, при этом первый вход синхронизатора соединен с первыми входами первого и второго элементов И, вторые входы которых подключены к инверсному выходу триггера, прямой вход которого соединен с вторым входом синхронизатора, третий вход синхронизатора соединен с первыми входами третьего, четвертого и пятого элементов И и третьим входом первого элемента И, -выход которого подключен к прямому входу реверсивного счетчика тактовых импульсов, выход которого подключен к второму входу третьего элемента И и к входу первого инвертора, выход которого подключен к обратному входу триггера, прямой выход ко- .торого подключен к первому входу шестого элемента И и к входу второго инвертора, выход которого подключен к первому входу седьмого элемента И, выход второго элемента И подключен к входу третьего инвертора, выход которого подключен к первому входу четвертого элемента И и третьему входу третьего элемента И, выход которого подключен к реверсивному входу реверсивного счетчика тактовых импульсов и входу четвертого инвертора, выход которого подключен к первому входу пятого элемента И, выход которого подключен к входу адресg ного счетчика, выход которого подключен к второму входу седьмого элемента И, выход которого подключен к первому входу элемента ИЛИ, второй вход которого подключен к выходу ше5 стого элемента И, второй вход которого подключен к выходу адресного счетчика, вход которого подключен к выходу четвертого элемента И, выход элемента ИЛИ соединен с первым

0 выходом компаратора, прямой выход триггера соединен с вторым выходом компаратора, выход четвертого и пятого элементов И соединены соответственно с третьим и чет 5 вертым выходами компарато - ра.

фид.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выделения сейсмических сигналов | 1982 |

|

SU1049781A1 |

| Цифровая сейсмическая станция | 1984 |

|

SU1188686A1 |

| Устройство для определения местоположения источника акустической эмиссии | 1987 |

|

SU1499224A1 |

| Устройство для регистрации и измерения сигналов акустической эмиссии | 1984 |

|

SU1180786A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для измерения интерферограмм | 1985 |

|

SU1295224A1 |

| Цифровой фильтр | 1988 |

|

SU1569957A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Квадратурный перемножитель | 1985 |

|

SU1300505A1 |

| Цифровой генератор гармонических сигналов | 1984 |

|

SU1211846A1 |

Изобретение относится к аппаратуре вьщеления геофизической информации, принимаемой на фоне помех, и позволяет расширить функциональные возможности и повысить помехоустойчивость за счет введения спецблоков компаратора и синхронизатора. В качестве критерия для вьщеления полезного сигнала используются признаки совпадения знаковой функции. 2 3.п. ф-лы, 3 ил.

Составитель Д.Заргарян Редактор Н.Тупица Техред М.Моргентал Корректор 0.Луговая

Заказ 3086/48 Тираж 728Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул..Проектная,4

| СПОСОБ НАКОПЛЕНИЯ СЕЙСМИЧЕСКИХ СИГНАЛОВ НА МАГНИТНОМ НОСИТЕЛЕ | 0 |

|

SU269503A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ШнеерсонМ.Б., Майоров В.В | |||

| Наземная сейсморазведка с невзрывными источниками колебаний | |||

| М.: Недра, | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Способ применения резонанс конденсатора, подключенного известным уже образом параллельно к обмотке трансформатора, дающего напряжение на анод генераторных ламп | 1922 |

|

SU129A1 |

| Цифровая многоканальная сейсмостанция | 1980 |

|

SU1000972A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-06-07—Публикация

1984-09-11—Подача