Изобретение относится к обработке сигналов и может быть использовано в технике связи.

Цель изобретения - устранение погрешности квадратурности.

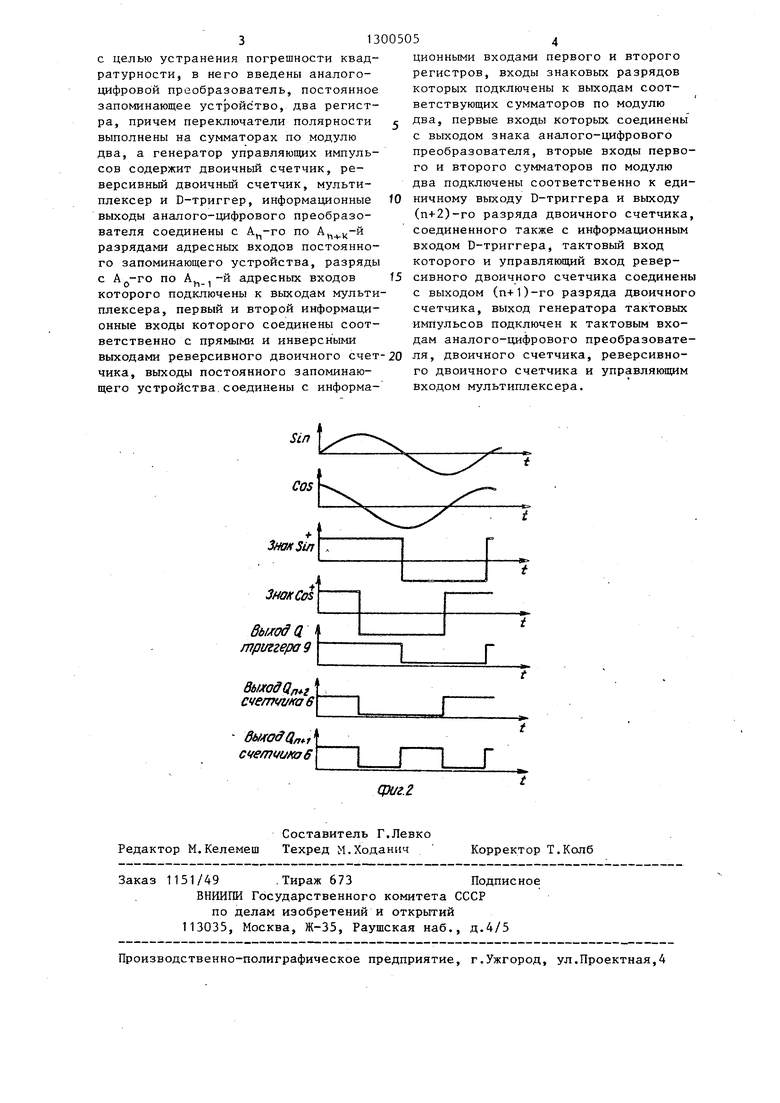

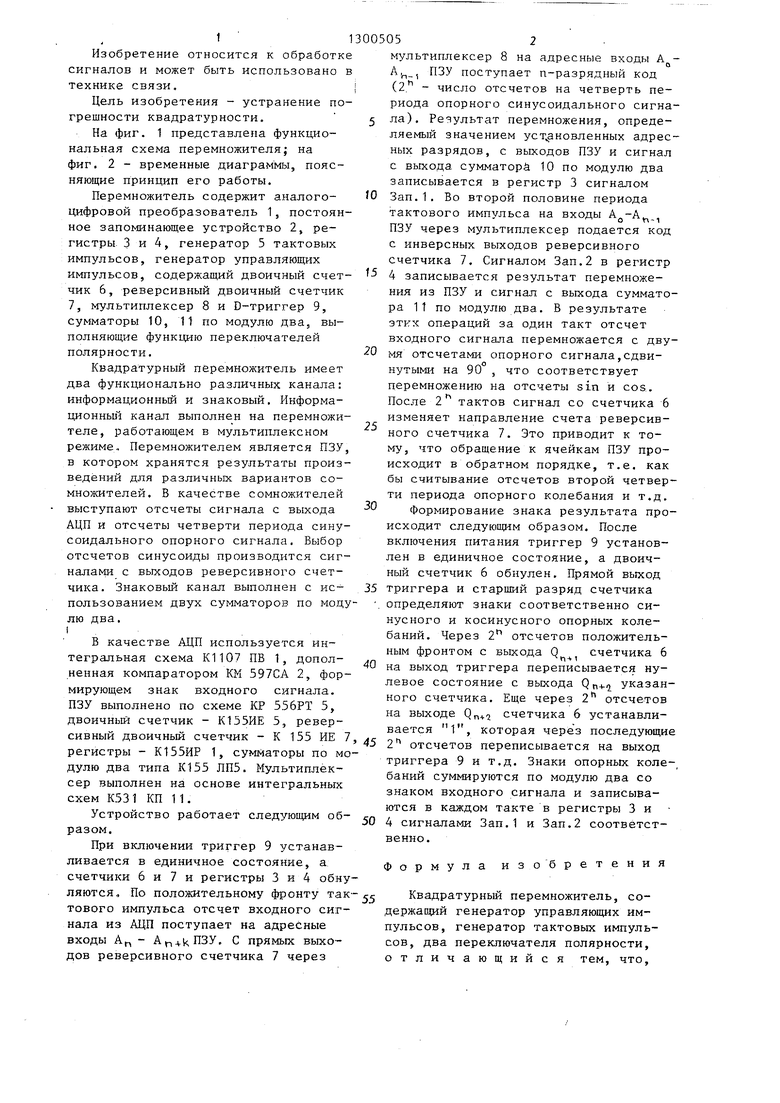

На фиг. 1 представлена функциональная схема перемножителя; на фиг. 2 - временные диаграммы, поясняющие принцип его работы.

Перемножитель содержит аналого- цифровой преобразователь 1, постоянное запоминающее устройство 2, регистры 3 и 4, генератор 5 тактовых импульсов, генератор управляющих импульсов, содержащий двоичный счетчик 6, реверсивный двоичный счетчик 7, мультиплексер 8 и D-триггер 9, сумматоры 10, II по модулю два, выполняющие функцию переключателей полярности.

Квадратурный перемножитель имеет два функционально различных канала: информационный и знаковый. Информа- ционньш канал выполне н на перемножителе, работающем в мультиплексном режиме. Перемножителем является ПЗУ, в котором хранятся результаты произведений для различных вариантов сомножителей. В качестве сомножителей выступают отсчеты сигнала с выхода АЦП и отсчеты четверти периода синусоидального опорного сигнала. Выбор отсчетов синусоиды производится сигналами с выходов реверсивного счетчика. Знаковый канал выполнен с ис- пользованием двух сумматоров по модулю два. I ,

В качестве АЦП используется интегральная схема K11G7 ПВ 1, дополненная компаратором КМ 597СА 2, формирующем знак входного сигнала. ПЗУ выполнено по схеме КР 556РТ 5, двоичный счетчик - К155ИЕ 5, реверсивный двоичный счетчик - К 155 ИЕ 7 регистры - К155ИР 1, сумматоры по модулю два типа К155 ЛП5. Мультиплексер выполнен на основе интегральных схем К531 КП 11.

Устройство работает следующим образом.

При включении триггер 9 устанавливается в единичное состояние, а счетчики 6 и 7 и регистры 3 и 4 обнуляются. По положительному фронту тактового импульса отсчет входного сигнала из АЦП поступает на адресные входы АГ, - ,,кПЗУ. С прямых выходов реверсивного счетчика 7 через

5

0

5

0

5

0

5

0

мультиплексер 8 на адресные входы А,, ПЗУ поступает п-разрядный код (2, - число отсчетов на четверть периода опорного синусоидального сигнала). Результат перемножения, определяемый значением уст ановленных адресных разрядов, с выходов ПЗУ и сигнал с выхода сумматорй 10 по модулю два записывается в регистр 3 сигналом Зап.1. Во второй половине периода тактового импульса на входы А„-А ,

О тЛ I

ПЗУ через мультиплексер подается код с инверсных выходов реверсивного счетчика 7. Сигналом Зап.2 в регистр 4 записывается результат перемножения из ПЗУ и сигнал с выхода сумматора 11 по модулю два. В результате ЭТР:Х операций за один такт отсчет входного сигнала перемножается с двумя отсчетами опорного сигнала,сдвинутыми на 90 , что соответствует перемножению на отсчеты sin и соа. После 2 тактов сигнал со счетчика 6 изменяет направление счета реверсивного счетчика 7. Это приводит к тому, что обращение к ячейкам ПЗУ происходит в обратном порядке, т.е. как бы считывание отсчетов второй четверти периода опорного колебания и т.д.

Формирование знака результата происходит следующим образом. После включения питания триггер 9 установлен в единичное состояние, а двоичный счетчик 6 обнулен. Прямой выход триггера и старший разряд счетчика определяют знаки соответственно синусного и косинусного опорных колебаний. Через 2 отсчетов положительным фронтом с выхода Q счетчика 6 на выход триггера переписывается нулевое состояние с выхода Qn-t-- указанного счетчика. Еще через 2 отсчетов на выходе счетчика 6 устанавливается 1, которая чере з последующие 2 отсчетов переписывается на выход триггера 9 и т.д. Знаки опорных коле-, баний суммируются по модулю два со знаком входного сигнала и записываются в каждом такте в регистры 3 и 4 сигналами Зап.1 и Зап.2 соответственно.

Формула

и

3 о б р е т е и и я

Квадратурный перемножитель, со- держаЕций генератор управляющих импульсов, генератор тактовых импульсов, два переключателя полярности, отличающийся тем, что.

с целью устранения погрешности квад- ратурности, в него введены аналого- цифровой преобразователь, постоянное запоминающее устройство, два регистра, причем переключатели полярности выполнены на сумматорах по модулю два, а генератор управляющих импульсов содержит двоичный счетчик, реверсивный двоичный счетчик, мульти- плексер и D-триггер, информационные выходы аналого-цифрового преобразователя соединены с

по А,-й

разрядами адресных входов постоянного запоминающего устройства, разряды с по А,-й адресных входов которого подключены к выходам мульти- плексера, первый и второй информационные входы которого соединены соответственно с прямыми и инверсными

выходами реверсивного двоичного счет-20 ля, двоичного счетчика, чика, выходы постоянного запоминающего устройства.соединены с информаго двоичного счетчика входом мультиплексера,

и

-20 ля, двоичного счетчика, 05054

ционными входами первого и второго регистров, входы знаковых разрядов которых подключены к выходам соответствующих сумматоров по модулю

г два, первые входы которых соединены с выходом знака аналого-цифрового преобразователя, вторые входы первого и второго сумматоров по модулю два подключены соответственно к еди10 яичному выходу D-триггера и выходу (п+2)-го разряда двоичного счетчика, соединенного также с информационным входом D-триггера, тактовый вход которого и управляющий вход ревер15 сивного двоичного счетчика соединены с выходом (п+1)-го разряда двоичного счетчика, выход генератора тактовых импульсов подключен к тактовым входам аналого-цифрового преобразоватереверсивно-управляющим

го двоичного счетчика входом мультиплексера,

и

л/,| Cos

к

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1830632A1 |

| Цифровой фильтр | 1988 |

|

SU1569957A1 |

| Адаптивный цифровой корректор | 1982 |

|

SU1083379A1 |

| Цифровое устройство фазовой синхронизации | 1985 |

|

SU1246395A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Умножитель частоты | 1986 |

|

SU1332316A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1984 |

|

SU1840075A1 |

Изобретение относится к обработке сигналов и может быть использовано в технике связи. Цель изобретения устранение погрешности квадратурнос- ти. Сущность заявляемого технического решения состоит в использовании аналого-цифрового преобразователя 1, постоянного запоминающего устройства 2, мультиплексора 8, регистров 3, 4 и сумматоров 10, 11 пл модулю два, которые образуют два функционально различных канала, чтд устраняет указанные недостатки. 2 ил. ifi 1сл m-ff GO О О сд о ел -4 ut.J

Редактор М.Келемеш

Составитель Г.Левко Техред М.Ходанич

Заказ 1151/49 .Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор Т.Колб

| Устройство для формирования квадратурных гармонических колебаний | 1975 |

|

SU752369A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Квадратурный перемножитёль для двухканального фильтра, Мин.М.В.Пар- ве Т.Э | |||

| - избирательные системы с обратной связью, г.Таганрог, 1983, № 5, с.127-129. | |||

Авторы

Даты

1987-03-30—Публикация

1985-11-21—Подача