§

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Многочастотный цифровой фильтр | 1987 |

|

SU1474827A1 |

| Многоканальный дискретно-аналоговый фильтр | 1987 |

|

SU1483607A1 |

| Цифровой приемник дельта-модулированных сигналов | 1989 |

|

SU1732499A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СУБОПТИМАЛЬНОГО РАЗМЕЩЕНИЯ И ЕГО ОЦЕНКИ | 2001 |

|

RU2193796C2 |

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Устройство для измерения нелинейных искажений | 1988 |

|

SU1707564A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ СТЕПЕНИ ЗАГРУЗКИ КАНАЛОВ В СИСТЕМАХ С ДРЕВОВИДНОЙ ТОПОЛОГИЧЕСКОЙ ОРГАНИЗАЦИЕЙ ПРИ НАПРАВЛЕННОЙ ПЕРЕДАЧЕ ИНФОРМАЦИИ | 2011 |

|

RU2451334C1 |

| УСТРОЙСТВО ДЛЯ РАЗЛИЧЕНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1984 |

|

SU1841016A1 |

| УСТРОЙСТВО ПОИСКА НИЖНЕЙ ОЦЕНКИ РАЗМЕЩЕНИЯ В МАТРИЧНЫХ СИСТЕМАХ ПРИ НАПРАВЛЕННОЙ ПЕРЕДАЧЕ ИНФОРМАЦИИ | 2009 |

|

RU2452005C2 |

Изобретение относится к технике цифровой обработки сигналов. Цель изобретения - повышение чувствительности путем уменьшения собственных шумов при отсутствии входного сигнала. Цифровой фильтр содержит АЦП 1, счетчик 2 адреса, сумматор 3, одновибраторы 4 и 5, тактовый г-р 6, нуль-орган 7, коммутаторы 8 и 16, регистр 9 сдвига, умножитель 10, блоки 11 и 12 памяти, детектор 13 совпадений, реверсивный счетчик 14 и D-триггер 15. Для уменьшения уровня собственных шумов фильтра при нулевых входных сигналах в данном фильтре обеспечивается устранение предельных циклов, обусловленных эффектом мертвой зоны. 5 ил.

СП

о

СО СО СП

Изобретение относится к технике цифровой обработки сигналов и может быть йспблЪЗОвано в автоматике, электро- и радиосвязи, измерительной технике и т.п. для цифровой рекурсивной фильтрации сигналов.

Целью изобретения является повышение чувствительности путем уменьшения собственных шумов при отсутст- JQ вин входного сигнала.

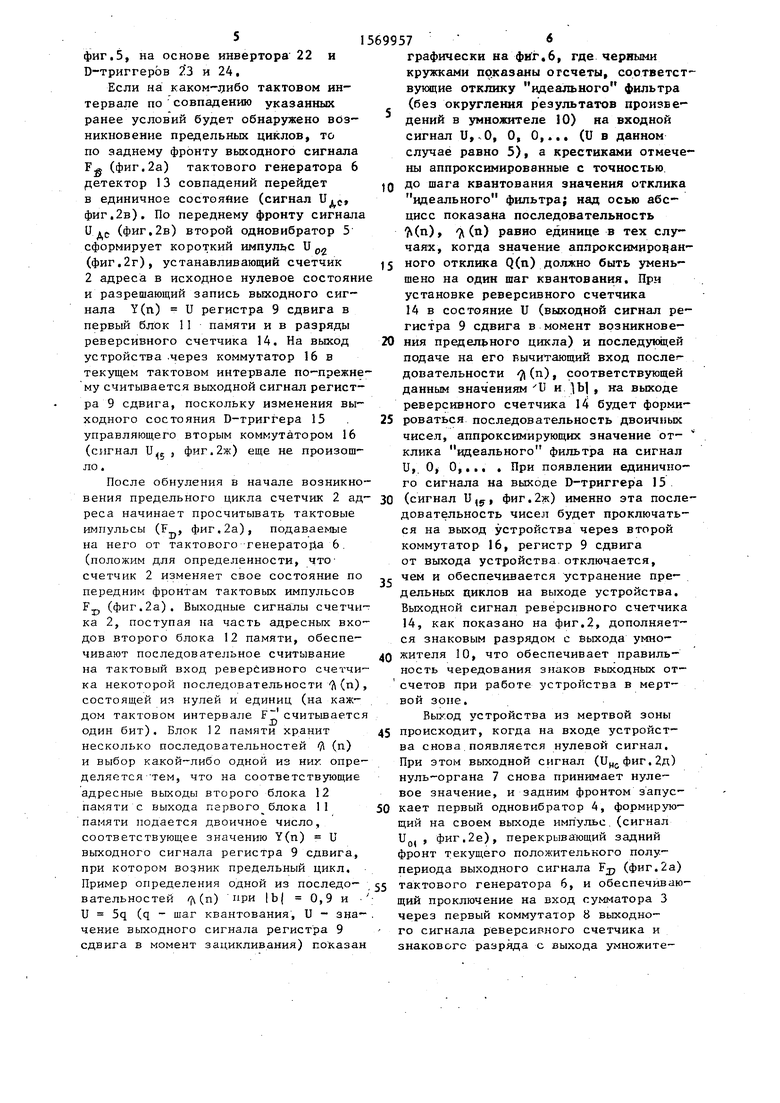

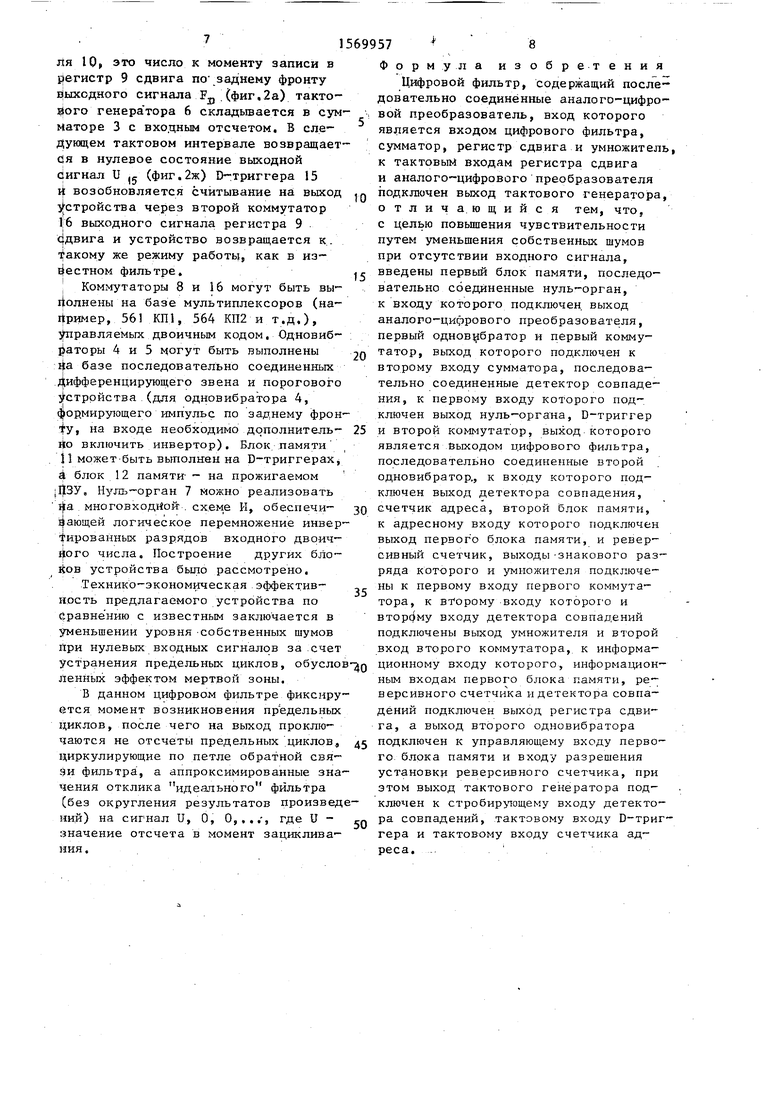

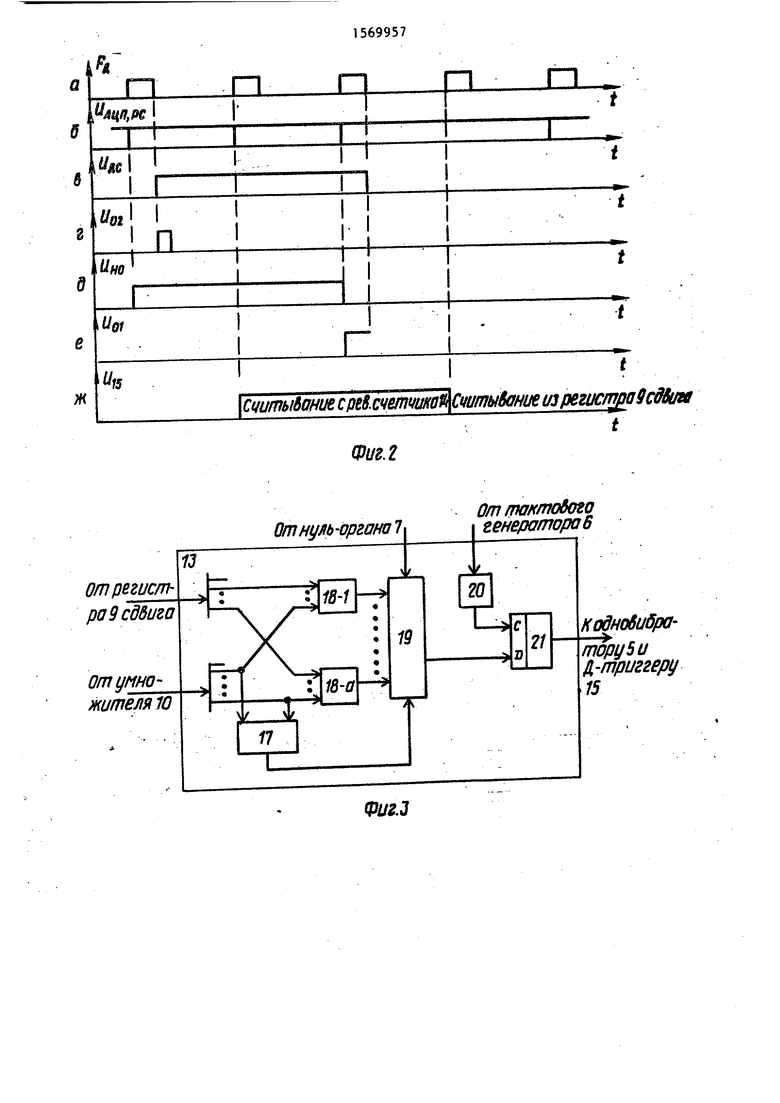

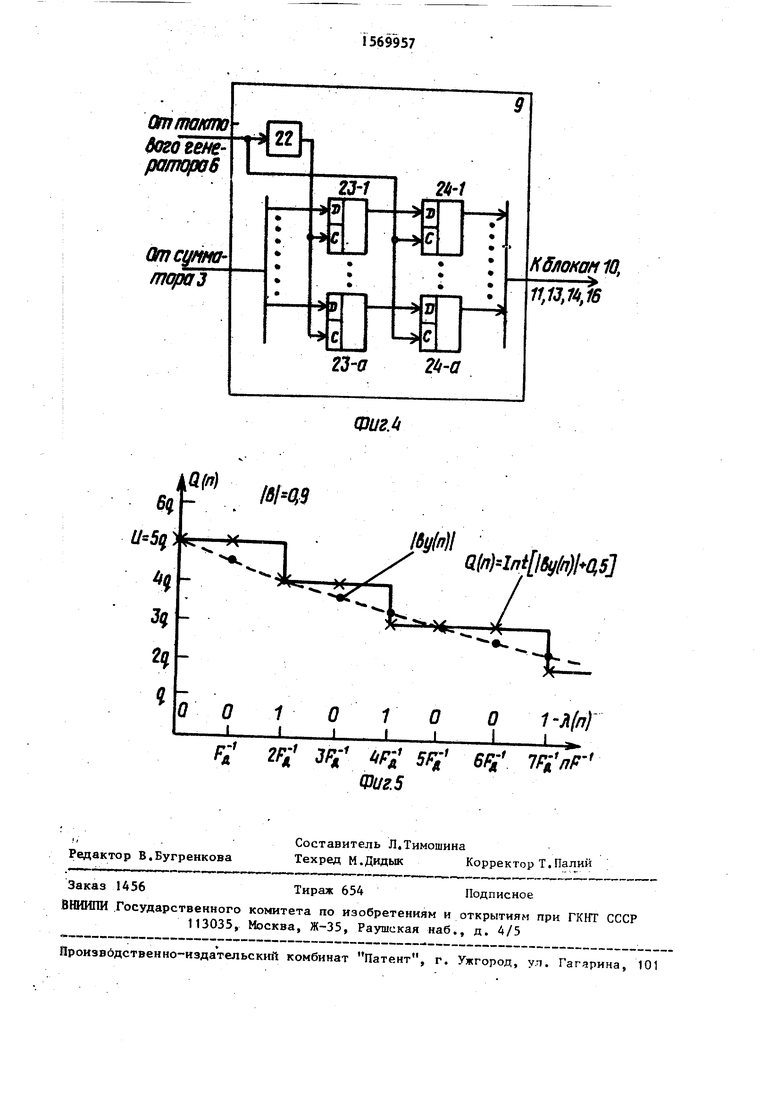

На фиг.1 приведена блок-схема предлагаемого устройства; на фиг.2 - временные диаграммы, поясняющие работу предлагаемого устройства; на 5 фиг.З - блок-схема, соответствующая одному из.возможных вариантов построения детектора совпадений; на фиг.4 - один из возможных вариантов построения регистра сдвига; на фиГ.5 - вре- 20 менные зависимости идеального и аппроксимированного отклика фильтра на одиночный ненулевой входной отсчет .

Цифровой фильтр содержит аналоге- 25 цифровой преобразователь (АЦП) I, счетчик 2 адреса, сумматор 3, первый 4 и второй 5 одновибраторы, тактовый генератор 6, нуль-орган 7, первый

выходной сигналы умножителя 10 равны Друг другу (по абсолютной величине) и отличны от нуля, при этом, если выполнено условие 1), логическая единица появляется на выходе детектора 13 совпадений, который может быть построен, например, как показано на фиг.4, на основе сумматоров 18 по модулю два с инверсией элемента И 19, элемента ИЛИ 17, инвертора 20 и D-триггера 21. При совпадении значений во всех разрядах (кроме знакового) входных сравниваемых чисел на выходах всех сумматоров 18 по модулю два с инверсией появится логическая единица, которая пройдет на вход элемента И 19 при условии, что от нуль-органа 7 поступает также логическая единица. Запрет срабатывания детектора 13 совпадений от нулевых сигналов осуществляется элементом ИЛИ 17. С помощью инвертора.20 и D-триггера 21 выходной сигнал элемента И 19 привязывается к задним фронтам выходного сигнала тактового генератора 6, при этом состояние детектора 13 совпадений не меняется за время выполнения текущего цикла

коммутатор 8, регистр,9 сдвига, умно- JQ операций (умножение на весовой коэфжитель 10, первый блок 11 памяти, второй блок 12 памяти, детектор 13 совпадений реверсивного счетчика 14, D-триггер 15, второй коммутатор 16.

Детектор 13 совпадений содержит элемент ИЛИ 17,-сумматоры 18 по мо- . дулю, элемент И 19, инвертор 20, В-тригг ер 21. Регистр 9 сдвига содержит инвертор 22, D-трнггеры 23 и 24.

Цифровой фильтр работает следующим образом.

Входной сигнал с помощью АЦП I дискретизируется с частотой FJ, (фиг.2а) и преобразуется в цифровую форму, после чего подается на рекурсивный фильтр первого порядка, построенный на сумматоре 3, регистре 9 сдвига и умножителе 10 и реализующий в Z-плоскости передаточную функцию H(Z) - (Z-b) , где b - весовой коэффициент умножителя 10. Моменты смены состояний на выходе АЦП 1 и регистра 9 сдвига показаны на фиг.26. Определение момента начала предельных циклов производится по совпадению двух

35

40

45

50

55

цииент b и суммирование).

При отсутствии предельных циклов сигналы на выходе детектора 13 совпадений, D-триггера 15, нуль-органа 7 и первого одновибратора 4 равны нулю и первый коммутатор 8 проключает на вход сумматора выходной сигнал умнот жителя 10, а второй коммутатор 16 проключает на выход всего устройства выходной сигнал регистра 9 сдвига.

8этом случае очевидно, что работа устройства происходит так же, как и в известном устройстве. Моменты

дискретизации сигнала в АЦП 1 и считывания отсчетов из регистра 9 сдвига определяются положительными фронтами выходного сигнала F-p (фиг.2а) тактового генератора 6. Для того, чтобы к моменту записи очередного результата обработки в регистр 9 сдвига успели завершиться все переходные процессы (в умножителе 10, сумматоре 3 и т.д.) запись в регистр

9сдвига может производиться, например, по заднему фронту сигнала F (фиг.2а), а считывание на умножитель 10 - по .переднему. Такой регистр сдвига легко может быть построен, например, как показано на

следующих условий: 1) выходной сигнал АЦП 1 равен нулю, при этом на выходе нуль-органа 7 появляется логическая единица; 2) входной и

выходной сигналы умножителя 10 равны Друг другу (по абсолютной величине) и отличны от нуля, при этом, если выполнено условие 1), логическая единица появляется на выходе детектора 13 совпадений, который может быть построен, например, как показано на фиг.4, на основе сумматоров 18 по модулю два с инверсией элемента И 19, элемента ИЛИ 17, инвертора 20 и D-триггера 21. При совпадении значений во всех разрядах (кроме знакового) входных сравниваемых чисел на выходах всех сумматоров 18 по модулю два с инверсией появится логическая единица, которая пройдет на вход элемента И 19 при условии, что от нуль-органа 7 поступает также логическая единица. Запрет срабатывания детектора 13 совпадений от нулевых сигналов осуществляется элементом ИЛИ 17. С помощью инвертора.20 и D-триггера 21 выходной сигнал элемента И 19 привязывается к задним фронтам выходного сигнала тактового генератора 6, при этом состояни детектора 13 совпадений не меняется за время выполнения текущего цикла

Q операций (умножение на весовой коэф5

0

5

0

5

цииент b и суммирование).

При отсутствии предельных циклов сигналы на выходе детектора 13 совпадений, D-триггера 15, нуль-органа 7 и первого одновибратора 4 равны нулю и первый коммутатор 8 проключает на вход сумматора выходной сигнал умнот жителя 10, а второй коммутатор 16 проключает на выход всего устройства выходной сигнал регистра 9 сдвига.

8этом случае очевидно, что работа устройства происходит так же, как и в известном устройстве. Моменты

дискретизации сигнала в АЦП 1 и считывания отсчетов из регистра 9 сдвига определяются положительными фронтами выходного сигнала F-p (фиг.2а) тактового генератора 6. Для того, чтобы к моменту записи очередного результата обработки в регистр 9 сдвига успели завершиться все переходные процессы (в умножителе 10, сумматоре 3 и т.д.) запись в регистр

9сдвига может производиться, например, по заднему фронту сигнала F (фиг.2а), а считывание на умножитель 10 - по .переднему. Такой регистр сдвига легко может быть построен, например, как показано на

фиг.5, на основе инвертора 22 D-триггеров 3 и 24,

Если на каком-либо тактовом интервале по совпадению указанных ранее условий будет обнаружено возникновение предельных циклов, то по заднему фронту выходного сигнала Fg (фиг.2а) тактового генератора 6

детектор 13 совпадений перейдет в единичное состояние (сигнал U.c, фиг.2в). По переднему фронту сигнала U дс (фиг.2в) второй одновибратор 5 сформирует короткий импульс U 0 (фиг.2г), устанавливающий счетчик 2 адреса в исходное нулевое состояни и разрешающий запись выходного сигнала Y(n) U регистра 9 сдвига в первый блок 1I памяти и в разряды реверсивного счетчика 14. На выход устройства через коммутатор 16 в текущем тактовом интервале по-прежнему считывается выходной сигнал регистра 9 сдвига, поскольку изменения выходного состояния D-триггера 15 управляющего вторым коммутатором 16 (сигнал , фиг.2ж) еще не произошло.

После обнуления в начале возникновения предельного цикла счетчик 2 адреса начинает просчитывать тактовые импульсы (F , фиг,2а), подаваемые на него от тактового генератора 6 (положим для определенности, что счетчик 2 изменяет свое состояние по передним фронтам тактовых импульсов F.J., (фиг.2а). Выходные сигналы счетчика 2, поступая на часть адресных входов второго блока 12 памяти, обеспечивают последовательное считывание на тактовый вход реверсивного счетчика некоторой последовательности (п), состоящей из путей и единиц (на каждом тактовом интервале считывается один бит). Блок 12 памяти хранит несколько последовательностей fl (n) и выбор какой-либо одной из них определяется тем, что на соответствующие адресные выходы второго блока 12 памяти с выхода первого блока 11 памяти подается двоичное число, соответствующее значению Y(n) U выходного сигнала регистра 9 сдвига, при котором возник предельный цикл. Пример определения одной из последовательностей д(п) при |Ь| 0,9 и U 5q (q - шаг квантования, U - значение выходного сигнала регистра 9 сдвига в момент зацикливания) показан

10

15

25

569957

графически на фиг.6, где черными кружками показаны отсчеты, соответствующие отклику идеального фильтра (без округления результатов произведений в умножителе 10) на входной сигнал U, О, О, О,... (Us данном случае равно 5), а крестиками отмечены аппроксимированные с точностью до шага квантования значения отклика идеального фильтра; над осью абсцисс показана последовательность Мп), (п) равно единице в тех случаях, когда значение аплроксимиров,ан- ного отклика Q(n) должно быть уменьшено на один шаг квантования. При установке реверсивного счетчика 14 в состояние U (выходной сигнал регистра 9 сдвига в момент возникнове- 20 ния предельного цикла) и последующей подаче на его вычитающий вход послег- довательности (n) соответствующей данным значениям U и Ъ, на выходе реверсивного счетчика 14 будет формироваться последовательность двоичных чисел, аппроксимирующих значение от- v клика идеального фильтра на сигнал U, О, О,... . При появлении единичного сигнала на выходе D-триггера 15 (сигнал U,у, фиг.2ж) именно эта последовательность чисел будет проключать- ся на выход устройства через второй коммутатор 16, регистр 9 сдвига от выхода устройства отключается, чем и обеспечивается устранение предельных циклов на выходе устройства. Выходной сигнал реверсивного счетчика 14, как показано на фиг.2, дополняется знаковым разрядом с выхода умно- 40 жителя 10, что обеспечивает правильность чередования знаков выходных отсчетов при работе устройства в мертвой зоне.

Выход устройства из мертвой зоны происходит, когда на входе устройства снова появляется нулевой сигнал. При этом выходной сигнал (инофиг.2д) нуль-органа 7 снова принимает нулевое значение, и задним фронтом запускает первый одновибратор 4, формирующий на своем выходе импульс (сигнал

30

35

4S

50

U0) , фиг.2е), перекрывающий задний фронт текущего положительного полу- периода выходного сигнала F-р (фиг.2а) тактового генератора 6, и обеспечивающий проключение на вход сумматора 3 через первый коммутатор 8 выходного сигнала реверсивного счетчика и знакового разряда с выхода умножителя 10, это число к моменту записи в регистр 9 сдвига по заднему фронту выходного сигнала Fo (фиг.2а) тактового генератора 6 складывается в сумматоре 3 с входным отсчетом. В следующем тактовом интервале возвращается в нулевое состояние выходной сигнал U )5 (фнг.2ж) D-триггера 15 и возобновляется считывание на выход устройства через второй коммутатор 16 выходного сигнала регистра 9 сдвига и устройство возвращается к. такому же режиму работы, как в известном фильтре.

Коммутаторы 8 и 16 могут быть выполнены на базе мультиплексоров (например, 561 КП1, 564 КП2 и т.д.), управляемых двоичным кодом, Одновиб- раторы 4 и 5 могут быть выполнены на базе последовательно соединенных дифференцирующего звена и порогового устройства (для одновибратора 4, формирующего импульс по заднему фрон

ту, на входе необходимо дополнитель- 25 и второй коммутатор, выход которого

но включить инвертор). Блок памяти 11 может быть выполнен на D-триггерах, а блок I2 памяти - на прожигаемом ,ПЗУ, Нуль-орган 7 можно реализовать на многовходной- схеме 1-1, обеспечивающей логическое перемножение инвертированных разрядов входного двоичного числа. Построение других блоков устройства было рассмотрено.

Технико-экономическая эффективность предлагаемого устройства по сравнению с известным заключается в уменьшении уровня собственных шумов при нулевых входных сигналов за счет

устранения предельных циклов, обуслов- Q ционному входу которого, информацион- ленных эффектом мертвой зоны.ным входам первого блока памяти, реВ данном цифровом фильтре фиксируется момент возникновения предельных циклов, после чего на выход проклю- чаются не отсчеты предельных циклов, 45 циркулирующие по петле обратной связи фильтра, а аппроксимированные значения отклика идеального фильтра (без округления результатов произведений) на сигнал U, 0, 0,,.,-, где U - CQ значение отсчета ц момент зацикливания.

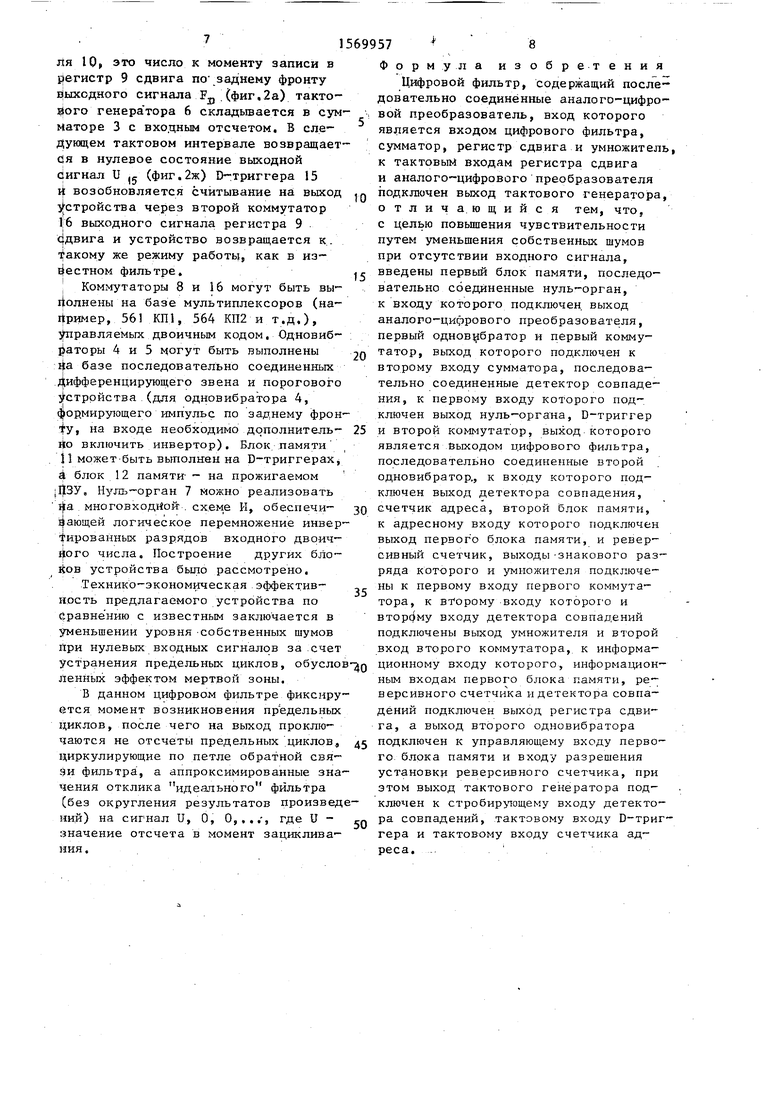

Формула изобретения

Цифровой фильтр, содержащий последовательно соединенные аналого-цифровой преобразователь, вход которого является входом цифрового фильтра, сумматор, регистр сдвига и умножитель, к тактовым входам регистра сдвига и аналого-цифрового преобразователя

подключен выход тактового генератора, отличающийся тем, что, с целью повышения чувствительности путем уменьшения собственных шумов при отсутствии входного сигнала,

c введены первый блок памяти, последовательно соединенные нуль-орган, к входу которого подключен выход аналого-цифрового преобраэоват еля, первый одновибратор и первый комму-

Q татор, пыход которого подключен к второму входу сумматора, последовательно соединенные детектор совпадения, к первому входу которого подключен выход нуль-органа, D-триггер

0

5

является Выходом цифрового фильтра, последовательно соединенные второй одновибратор., к входу которого подключен выход детектора совпадения, счетчик адреса, второй блок памяти, к адресному входу которого подключен выход первого блока памяти, и реверсивный счеччик, выходы знакового разряда которого и умножителя подключены к первому входу первого коммутатора, к второму входу которого и второму входу детектора совпадений подключены выход умножителя и второй вход второго коммутатора, к информа-

версивного счетчика и де гектора совпадений подключен выход регистра сдвига, а выход второго одновибратора подключен к управляющему входу первого блока памяти и входу разрешения установки реверсивного счетчика, при этом выход тактового генератора подключен к стробируыщему входу детектора совпадений, тактовому входу D-триггера и тактовому входу счетчика адреса.

Фиг.з

iQ()

Фиг. 4

| Введение в цифровую фильтрацию | |||

| /Под ред | |||

| Р.Богнера и А.Константини- диси | |||

| Пер | |||

| с англ, (под ред | |||

| Л.И.Филиппова).- М.: Мир, 1976, с.38. |

Авторы

Даты

1990-06-07—Публикация

1988-08-29—Подача