второго регистров группы соединены с разрядными входами соответственно первого и второго реверсивных счетчиков группы, узел задания геометрии области содержит блок памяти, группу сумматоров, группу регистров, группу умножителей на знак, сдвиговый регистр, счетчик и элемент НЕ-ИЛИ, причем вход и выход блока памяти соединены соответственно с первыми выходами и входами регистров группы, вторые выходы первого и второго регистров группы соединены с информационными входами соответственно первого и второго умножителей на знак группы, выходы первого и второго умножителей на знак группы соединены соответственно с первым и вторым входами первого сумматора группы, выход которого соединен с первым входом второго сумматора группы, второй выход третьего регистра группы соединен с вторым входом второго сумматора группы, первый выход кото рого соеди нен с вторые входом третьего регистра группы, а второй выход соединен с информационным входом сдв гового регистра и с прямым и инверсным входами элемента НЕ-ИЛИ, выход элемента НЕ-ИЛИ соединен со счетным входом счетчика, выход которого соединен с вторьм управляющим входом блока памяти, выход сдвигового регистра сое.чинен с входом третьего сумматора группы, узел формирования адреса, включающий блок регистров,, счетчик, счетчик-делитель, регистр, дешифратор, триггер, элемент И, элемент НЕ-И, элемент задержки, причем вход и выход счетчика соединены соответственно с первым и вторым адресными входами регистра, первый информационный вход которого соединен с выходом счетчика-делителя, а выход соединен с входом дешифратора, сигнальный выход дешифратора соединен с первым входом элемента И, а информационный выход соединен с информационным входом блока регистров, выход элемента НЕ-И соединен с вторым входом элемента И, выход которого соединен с единичным входом триггера выход триггера соединен с входом элемента задержки и управляющим входом блока регистров, выход элемента задержки соединен с нулевым входом триггера, и узел вычисления вероятностей перехода, включающий блок оперативной памяти, блок постоянной

памяти,-блок управления, содержащий элемент памяти, группу регистров, коммутатор, дешифратор,- группу триггеров и синхронизатор, первый выход которого соединен с входом синхронизации первого регистра группы, а второй выход соединен с входами синхронизации второго и третьего регистров группы и триггеров группы, выходы второго и третьего регистров группы соединены соответственно с первым и вторым информационными входами коммутатора, выход которого соединен с первым входом дешифратора, выход дешифратора соединен с входом первого регистра группы, выход которого соединен с входом элемента памяти, выход кодов команд которого соединен с вторым входом дешифратора, первьй управляющий выход элемента памяти соединен с .нулевым входом первого триггера группы, нулевой в:-.1ход которого соединен с первьм управляющим входом коммутатора, второй управляющий выход элемента памяти соединен с единичным входо - первого триггера -группы, третий и четвертый управляющие выходы элемента памяти соединены соответственно с нулевым и единичным входами второго триггера группы, выход которого соединен с вторым управляющим входом коммутатора,,и арифметико-логический блок, содержащий сумматор, и вторую группы коммутаторов, блок регистров, группу регистров и счетчик, причем информационный вход первого и первый информационный вход третьего коммутаторов первой группы соедиены с первым информационным входом первого регистра группы, - первого коммутатора первой группы соединен с. первым информационным входом второго коммутатора первой группы,

выход которого Соединен с первыми информационными входами сумматора и четвертого коммутатора первой группь и информационным входом первого оммутатора второй группы, выход третьего коммутатора первой группы соединен с вторым информационным ходом сумматора, информационный ыход которого соединен с вторым инормационным входом четвертого комутатора первой группы, выход четертого коммутатора первой группы оединен с первым входом блока реистров, с входом счетчика, с вторым информационным входом первого н ин формационмым входом второго регистров группы, выход блока регистров соединен с вторым информационным входом второго коммутатора первой группы и с информационным входом пер вого коммутатора второй группы, выход которого соединен с первым управ ляющим входом четвертого коммутатора первой группы, первый сигнальный выход сумматора соединен с первым сигнальным входом второго регистра группы, информационный выход которог соединен с вторым информационным входом третьего и первым информацион ным входом пятого коммутаторов первой группы, информационный выход пер вого регистра группы соединен с треты м информационным входом третье го и вторым информационным входом пятого коммутаторов первой группы, выход счетчика соединен с третьим информационным входом пятого коммутатора первой группы, сигнальный врркод первого регистра группы соединен с вторым сигнальным входом второго регистра группы, первый управляющий выход которого соединен с пер |Вым управляющим входом первого коммутатора второй группы, второй управляющий выход второго регистра гру пы соединен с BTOpi iM управляющим входом первого и первым управляющим входом третьего коммутаторов второй группы, выход третьего коммутатора второй группы соединен с первым управляющим входом второго регистра группы, третий управляющий выход которого соединен с первыми управляющими входами второго и четвертог коммутаторов второй группы, выход четвертого коммутатора второй групп соединен с вторым упраугяющим входом второго регистра группы, второй сигнальный выход сумматора соединен с третьим управляющим входом первог и вторым управляющим входом третьег коммутатора второй группы, третий сигнальный выход сумматора соединен с вторыми управляющими входами второго и четвертого коммутаторов второй группы, выход второго коммутатора второй группы соединен с вторы управляющим входом четвертого комму татора первой группы, первый, второ и третий управляющие входы блока оп ративной памяти узла вьмисления вероятностей перехода соединены соотвественно с вторым, третьим и четверTbw выходами синхронизатора блока управления узла вычисления вероятностей перехода, четвертый выход синхронизатора блока управления узла вычисления вероятностей перехода соединен с входом синхронизации блока постоянной памяти узла вычисления вероятностей перехода, выход управляющей информации элемента памяти блока управления узла вычисления вероятностей перехода соединен с входами управляющей информации коммутаторов первой и второй групп . су;- матора и блока регистров арифметико-логического блока узла вычисления вероятностей перехода, выход пятого коммутатора первой группы арифметико-логического блока узла вычисления вероятностей перехода соединен с входами адресной информации блоков оперативной и постоянной памяти узла вычисления вероятностей перехода и с входом адресной информации первого коммутатора первой группы арифметикологического блока узла вычисления вероятностей перехода, выход четвертого коммутатора первой группы арифметико-логического блока узла вычисления вероятностей перехода соединен с входами числовой информации блоков оперативной и постоянной памяти узла вычисления вероятностей перехода, выход блока оперативной памяти узла вычисления вероятностей перехода и выход управляющей информации блока постоянной памяти узла вычисления вероятностей перехода соединены с входом второго регистра группы блока управления узла вычисления вероятностей перехода, информационный выход блока постоянной памяти узла Е .иисления вероятностей перехода соединен с информационным входом блока оперативной памяти узла вычисления вероятностей перехода и с первым информационным входом первого регистра группы арифметико-логического блока, первый, второй и третий входы синхронизатора блока управления узла вычисления вероятностей перехода являются соответственно пусковым входом, входом сброса и входом останова устройства, первый вход синхронизатора блока управления узла вычисления вероятностей перехода соединен с пусковым входом датчика случайных чисел, выходы четвертого и пятого коммутаторов первой группы арифметико-логического блока узла вычисления вероятностей перехода сое динены с входами соответственно числовой и адресной информации датчика случайных чисел, с входами соответст венно числовой и адресной информации сумматоров группы блока формирования координат случайных точек обхода области, с входами соотве1ственно числовой и адресной информации сумматоров группы блока формирования координат случайных точек обхода области с входами соответственно числовой и адресной информации блока памяти, Счетчика и третьего сумматора группы блока задания геометрии области, с входами соответственно числовой и адресной информации счетчика, счетчика-делителя и блока регистров узла формирования адреса, единичный выход первого триггера группы блока управления узла вычисления вероятное тей перехода соединен с инверсным входом элемента НЕ-И узла формирования адреса, выход блока регистров узла формирования адреса соединен с первым входом третьего регистра группы блока управления узла вычисле ния вероятностей перехода выход триггера узла формирования адреса со-единен с входом синхронизации датчика случайных чисел, с тактовыми входами счетчика и сдвигового регист ра узла задания геометрии области и с вторым входом третьего регистра группы блока управления узла вычисления вероятностей перехода, управляющий выход датчика случайных чисел 38 соедине-н с управляющим входом блока памяти узла задания геометрии области, выход третьего сумматора группы узла задания геометрии области соединен с управляющими входами первого и второго регистров группы блока формирования координат случайных точек обхода области, с входом счетчика и с первьм адресным входом регистра узла формирования адреса, выходы первого и второго элементов НЕ-И группы блока формирования координат случайных точек обхода области соединены со знаковыми входами соответственно первого и второго умножителей на знак группы узла задания геометрии области, выход пятого элемента ИЛИ группы блока формирования координат случайных точек обхода области соединен с прямым входом элемента НЕ-И узла формирования адреса, первый информационный вход регистра узла формирования адреса является входом установки признака изменения вероятности перехода устройства, информационный выход датчика случайных чисел соединен с информационными входами сумматоров группы блока формирования координат случайных точек обхода области, выходы первого и второго реверсивных счетчиков группы блока формирования координат случайных точек обхода области соединены с входом кода координат вершин случайных траекторий первого коммутатора первой группы арифметико-логического блока узла вычисления вероятностей перехода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| Многофункциональный цифровой коррелометр | 1979 |

|

SU826361A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Устройство для моделирования стохастических объектов | 1988 |

|

SU1585803A1 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

| Устройство для обработки элементов сканерных изображений | 1983 |

|

SU1134945A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1160434A1 |

| Адаптивное вычислительное устройство | 1980 |

|

SU957214A1 |

ВЕРОЯТНОСТНОЕ УСТРОЙСТВО ДЛЯ РЕШЕНИЯ КРАЕВЫХ ЗАДАЧ, содержащее датчик случайных чисел, пусковой вход которого является пусковым входом устройства,блок формирования координат случайных точек обхода области, включающий группу сумматоров, узел задания геометрии области, отличающееся тем, что, с целью повыщения быстродействия и точности, блок формирования координат точек обхода области содержит группу реверсивных счетчиков, группу регистров, элемент И, группу элементов ИЛИ, группу элементов НЕ-И, первую и вторую группы элементов задержки, причем входы числовой информации сумматоров группы соединены с входами числовой информации регистров группы, входы адресной информации сумматоров группы соединены с входами адресной информации регистров группы, выход первого сумматора группы соединен с входом первого элемента задержки первой группы и первым входом элемента И, выход второго сумматора группы соединен с входом второго элемента задержки первой группы и вторым входом элемен-. та И, выходы третьего и четвертого сумматоров группы соединенп с входами соответственно первого и второго элементов задержки второй группы, выходы первого и второго элементов задержки первой группы соединены с первыми входами соответственно первого и второго элементов ИЛИ группы, выход элемента И соединен с вторыми входами первого и второго элемен- тов ИЛИ группы, выход первого элемента задержки второй группы соединен с первым входом четвертого элеменi та ИЛИ группы, с первым счетным входом первого реверсивного счетчи(л ка группы и прямьм входом первого элемента НЕ-И группы, выход второго элемента задержки второй группы сое динен с вторым входом четвертого элемента ИЛИ группы, с перлым счетным входом второго реверсивного счетчика группы и прямым входом второго элемента НЕ-И группы, выход пер вого элемента ИЛИ группы соединен с инверсным входом первого элемен30 та НЕ-И группы, с вторым счетным :о эс входом первого реверсивного счетчика группы и с первым входом третьего элемента ИЛИ группы, выход которого соединен с первым входом пятого элемента ИЛИ группы, выход второго элемента ИЛИ группы соединен с вторым входом третьего элемента ИЛИ группы, вторым счетным входом второго реверсивного счетчика группы и с инверсным входом второго элемента НЕ-И группы, выход четвертого элемента ИЛИ группы соединен с вторым входом пятого элемента ИЛИ группы, выходы первого и

Изобретение относится к вычислительной технике и предназначается как специализированное вычислительное устройство для решения уравнений математической физики, в частноети как приставка к универвальному вычислителю.

Известно устройство для решения задач математической физики, представляющее собой вероятностную ЭВМ для решения сеточных уравнений. Здесь на аналоговой части - потенциалоскопе - выполняется моделирование случайного блуждания. С помощью устройства регенерации из памяти на мишень потенциалоскопа наносится геометрия области Л .

Последнее снижает общее быстродействие устройства. Кроме того, в -память устройства вводятся координаты всех узлов, их граничные и начальные значения, вероятности переходов, что требует большого объема памяти, который растет при увеличении размеров области, также требует увеличения 3 1 разрядности регистров. При решении уравнений с переменными коэффициентами необходимо обращаться в память на каждом шаге, что также снижает общее быстродействие устройства. Наиболее близким к изобретению является гибрид(ый вероятностный ком плекс для решения краевых задач, который состоит из современной ЭЦВМ, способной работать в режиме прерывания и связанного с ней через устройство связи аналогового процессора. Основные функции последнего заключаются в хранения геометрии области в виде фотомаски, интегрирования систе мы стохастических дифференциальных уравнений для построения случайных траекторий, определении характерных моментов времени и текущих координат моделируемого процессора, а такхсе предварительной обработки полученных результатов, ЭЦВМ вьтолняет функции хранения и усреднения информации, вывод результатов и организацию обмена с аналоговым процессором zl . Недостатком известного устройства является ограниченное быстродействие определяемое спектром сигнала генератора шума, полосой пропускания и постоянной времени отклоняющей системы электронно-лучевой трубки, скоростью срабатывания элементов индикации положения луча. Кроме того, быстродействие устройства снижается за счет необходимости обращения в память при пересечении границы каждо подобласти и необходимости передачи больших массивов информации из аналоговой части в ЦВМ и обратно перед каждым временным шагом. Недостатком устройства является также невысокая точность, определяемая разрешающей способностью электронно-лучевой трубки, точностью изготовления маски и размером ячеек, на которые разбивается область. Последняя влияет на общее быстродействие устройства. Целью изобретения является повышение быстродействия и точности. Поставленная цель достигается тем что в устройстве,- содержащем датчик случайных чисел, пусковой вход которого является пусковым входом устройст ва блок формироБа ия координат случайных точек обхода обласчи, включаю щий группу сумматоров, узел задания геометрии области, блок формирования 8 координат точек обхода области содержит группу реверсивных счетчиков, группу регистров, элемент И, группу элементов ИЛИ, группу элементов НЕ-И, первую и вторую группы элементов задержки, причем входы числовой информации сумматоров группы соединены с входами числовой информации регистров группы, входы адресной информации сумматоров группы соединены с входами адресной информации регистров группы, выход первого сумматора группы соединен с входом первого элемента задержки первой группы и первым входом элемента И, выход второго сумматора группы соединен с входом второго элемента задержки первой группы и вторым входом элемента И, выходы третьего и четвертого сумматоров группы соединены с входами соответственно первого и второго элементов задержки второй группы, выходы первого и второго элементов задержки первой группы соединены с первыми входами соответственно первого и второго элементов ИЛИ группы, выход элемента И соединен с вторыми входами первого и второго элементов ИЛИ группы, выход первого элемента задержки второй группы соединен с первым входом четвертого элемента ИЛИ группы, с первым счетным входом первого реверсивного счетчика группы и прямым входом первого элемента НЕ-И группы, выход второго элемента задержки второй группы соединен с вторьм входом четвертого элемента ИЛИ группы, с первым счетным входом второго реверсивного счетчика группы и прямым входом второго элемента НЕ-И группы, выход первого элемента ИЛИ группы соединен с инверсным входом первого элемента НЕ-И группы, с вторым счетным входом первого реверсивного счетчика группы и с первым входом третьего элемента ИЛИ группы, выход которого соединен с первым входом пятого элемента ИЛИ группы, выход второго элемента Ш1И группы соединен с вторым входом третьего элемента ИЛИ группы, вторым счетным входом второго реверсивного счетчика группы и с инверсным входом второго элемента НЕ-И группы, выход четвертого элемента ИЛИ группы соединен с вторым входом пятого элемента ИЛИ группы, выходы первого и второго регистров группы соединены с разрядными входами соответственно первого и второго реверсивных счетчиков груп пы, узел задания геометрии области содержит блок памяти, группу суммато ров, группу регистров, группу умножи телей на знак, сдвиговый регистр, счетчик и элемент НЕ-КПП, причем вход и выход блока памяти соединены соответственно с первьиии выходами и входами регистров группы, вторые выходы первого и второго регистров гру пы соединены с информационными входами соответственно первого и второго умножителей на знак группы, выходы первого и второго умножителей на знак группы соединены соответственно с первым и вторым входами первого сумматора группы, выход которого сое динен с первым входом второго сумматора группы, второй выход третьего регистра группы соединен с вторым входом второго сумматора группы, пер вьй выход которого соединен с вторь входом третьего регистра группы, а второй выход соединен с информационным входом .сдвигового регистра и с прямым и инверсным входами элемента НЕ-ИЛИ, выход элемента сое динен со счетным входом счетчика, вы ход которого соединен с вторым управ ляющим входом блока памяти, выход сдвигового регистра соединен с входом третьего сумматора группы, узел формирования адреса, включающий блок регистров, счетчик, счетчик-делитель регистр, дешифратор, триггер, элемент И, элемент НЕ-И и элемент задер ки, причем вход и выход счетчика соединены соответственно с первым и вторым адерсными входами регистра, первый информационный вход которого соединен с выходом счетчика-делителя, а выход соединен с входом дешифратора, сигнальный выход дешифратора соединен с первым входом элемента И, а информационный вьгход соединен с информационным входом блока регистра выход элемента НЕ-И соединен с вторы входом элемента И, выход которого со динен с единичным входом триггера, выход триггера соединен с входом элемента задержки и управляющим входом блока регистров, выход элемента задержки соединен с нулевым входом триггера, и узел вычисления вероятностей перехода, включаклций блок опе ративной памяти, блок постоянной памяти, блок управления, содерх атий элемент памяти, группу регистров, коммутатор, дешифратор, группу триггеров и .синхронизатор, первый выход которого соединен с входом синхронизации первого регистра группы, а второй выход соединен с входами синхронизации второго и третьего регистров группы и триггеров группы, выходы второго и третьего регистров группы соединены соответственно с первым и вторым информационньп 1и входами коммутатора, выход которого соединен с первьм входом дешифратора, выход дешифратора соединен с входом первого регистра группы, выход которого соединен с входом элемента памяти, выход кодов команд которого соединен с вторым входом дешифратора, первый управляющий выход элемента.памяти соединен с нулевым входом первого триггера группы, нулевой выход которого соединен с первым управляющим входом коммутатора, второй управляющий выход элемента памяти соединен с единичным входом первого триггера группы, третий и четвертый управляющие выходы элемента памяти соединены соответственно с нулевым и единичным входами второго триггера группы, выход которого соединен с вторым управляющим входом ко мутатора, и арифметико-логический блок, содержащий сумматор, первую и вторую группы коммутаторов, блок регистров, группу регистров и счетчик, причем информационный вход первого и первый информационный вход третьего коммутатороа первой группы соединены с первым информационным входом первого регистра группы, выход первого коммутатора первой группы соединен с первым информационным входом второго коммутатора первой группы, выход которого сосдине с первыми информационными входами сумматора и четвертого коммутатора первой группы и с информационным входом первого коммутатора второй группы, В1..1ХОД третьего коммутатора первой группы соединен с вторым информационным входом сумматора, информационный выход которого соеде нен с вторым информационным входом четвертого коммутатора парной группы, выход четвертого коммутатора первой группь соединен с первым входом блока регистров, с входом счетчика, с вторым и 5формационным входом первого и информационным входом второго регистров группы, выход блока регистров соединен с вторым информационным входом второго коммутатора первой группы и с информационным входом первого коммутатора второй группы, выход которого соединен с первым управляющим входом четвертого коммутатора первой группы, первый сигнальный выход сумматора соединен .с первым сигнальным входом второго регистра группы, информационный выход которого соединен с вторым информационным входом третьего и первым информационным входом пятого коммутаторов первой группы, информационный выход первого регистра группы соединен.с третьим информационным входом третьего и вторым информационным входом пятого коммутаторов первой группы, выход счетчика соединен с третьим информационным входом пятого коммутатора первой группы, сигнальный выход первого регистра группы соединен с вторым сигнальным входом второго регистра группы, первый управляющий выход которого соединен с первым управляющим входом первого коммутатора второй группы, второй управляющий выход второго регистра группы соединен с вторым управляющим входом первого и первым управляющим входом третьего коммутаторов второй группы выход третьего коммутатора второй группы соединен с первым управляющим входом второго регистра группы, третий управляющий выход которого соединен с первыми управляющими входами второго и четвертого коммутаторов второй группы, выход четвертого коммутатора второй группы соединен с вторым управляющим входом второго регистра группы, BTopoii сигнальный выход сумматора соединен с третьим управляющим входом первого и вторым управляющим входом третьего коммутаторов второй группы, третий сигнальный выход сумматора соединен с вторыми управляющими входами второг и четвертого коммутаторов второй группы, выход второго коммутатора второй группы соединен Q вторым управляющим входом четвертого коммутатора первой группы, первый, второ и третий управляю1цие входы блока on ративной памяти узла.вычисления вероятностей перехода соединены соответственно с вторым, третьим и четвертными выходами синхронизатора блока управления узла вычисления верояткостей перехода, четвертый выход синхронизатора блока управления узла вычисления вероятностей перехода соединен с входом синхронизации блока постоянной памяти узла вычисления вероятностей перехода, выход управляющей информации элемента памяти блока управления узла вьгчисления вероятностей перехода соединен с входами управляющей информации коммутаторов первой и второй групп, сумматора и блока регистров арифметикологического блока узла вычисления вероятностей перехода, выход пятого коммутатора первой группы арифметикологического блока узла вычисления вероятностей перехода соединен с входами адресной информации блоков оперативной и постоянной памяти узла вычисления вероятностей перехода и с входом адресной информации первого ко мутатора первой группы арифметикологического блока узла вычисления вероятностей перехода, выход четвертого коммутатора первой группы арифметико-логического блока узла вычисления вероятностей перехода соединен с входами числовой и гформации блоков оперативной и постоянной памяти узла вычисления вероятностей перехода, выход, блока оперативной памяти узла вычисления вероятностей перехода и выход управляющей информации блока постоянной памяти узла вычисления вероятностей перехода соединены с входом второго регистра группы блока управления узла вычисления вероятностей перехода, информационный выход блока постоянной памяти узла вычисления вероятностей перехода соединен с информационным входом блока оперативной памяти узла вычисления вероятностей перехода и с первым информационным входом первого регистра группы арифметико-логического блока, первьш, второй и третий входы синхронизатора блока управления узла

вычисления вероятностей перехода являются соответственно пусковым входом, входом сброса и входом останова устройства, первый вход синхронизатора блока управления узла вычисления вероятностей перехода соединен с пусковым входом датчика случайных чисел, выходы четвертого и пятого коммутаторов первой группы арифмети9

ко-логического блока узла вычисления вероятностей перехода соединены с входами соответственно числовой и адресной информации датчика случайных чисел, с входами соответственно числовой и адресной информации сумматоров группы блока формирования координат случайных точок обхода области, с входами соответственно числовой и адресной информации блока памяти, счетчика и третьего сумматора группы узла задания геометрии области, с входами соответственно числовой и адресной информации счетчика, счетчика-делителя и блока регистра узла формирования адреса, единичный выход первого триггера группы блока управления узла вычисления вероятностей перехода соединен с инверсным входом элемента НЕ-И узла формирования адреса, выход блока регистров узла формирования адреса соединен с первым входом третьего регистра группы блока управления узла вычисления вероятностей перехода, выход триггера узла формирования адреса соединен с входом синхронизации датчика случайных чисел, с .тактовыми входами счетчика и сдвигового регистра узла задания геометрии области и с вторым входом третьего регистра группы блока управления узла вычисления вероятностей перекода, управляющий выход датчика случайных чисел соединен с управляющим входом блока памяти узла задания геометрии области, выход третьего сумматора группы узла задания геометрии области соединен с управляющими входами первого и второго регистров группы блока формирования координат (Случайных точек обхода области, с

входом счетчика и с первым адресным входом регистра узла формирования адреса, вькоды первого и второго эле ментов НЕ-И группы блока формировани координат случайных точек обхода области соединены со знаковыми входами соответственно первого и второго умножителей на знак группы узла заданця геометрии области, выход пятого элемента ИЛИ группы блока формирования координат случайных точек обхода области соединен с прямым входом элемента НЕ-И узла формирования адреса, первый информационный вход регистра узла формирования адреса является входом установки признака из83Й

10

менения вероятности перехода устройства, информационный выход датчика случайных чисел соединен с.информационными входами сумматоров группы блока формирования координат случайных точек обхода области, выходы первого и второго реверсивных счетчиков группы блока формирования координат случайных точек обхода области соединены с входом кода координат вершин случайных траекторий первого коммутатора первой группы арифметико-логического блока узла вычисления вероятностей перехода.

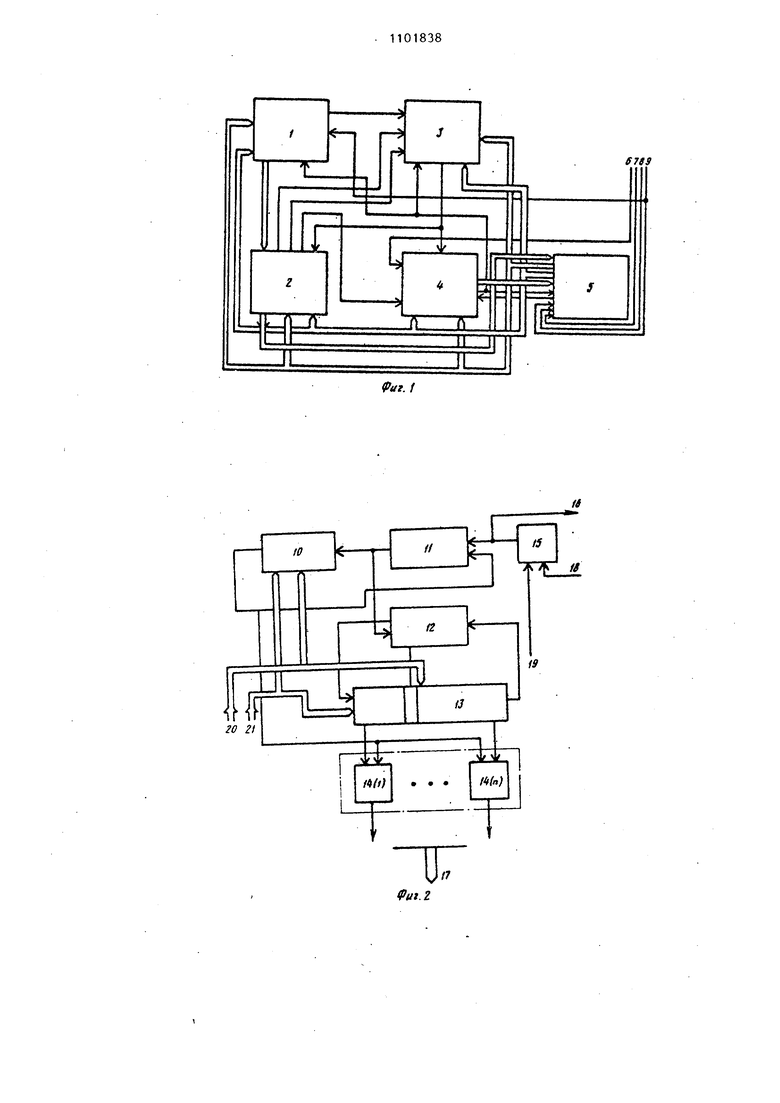

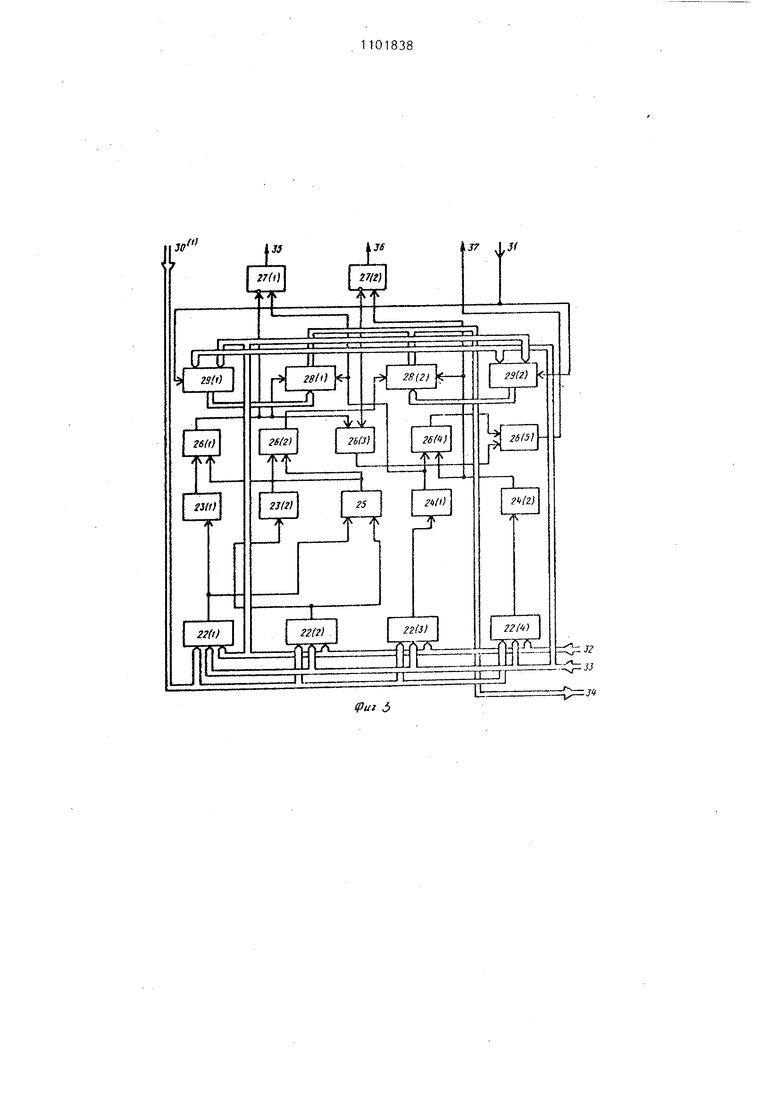

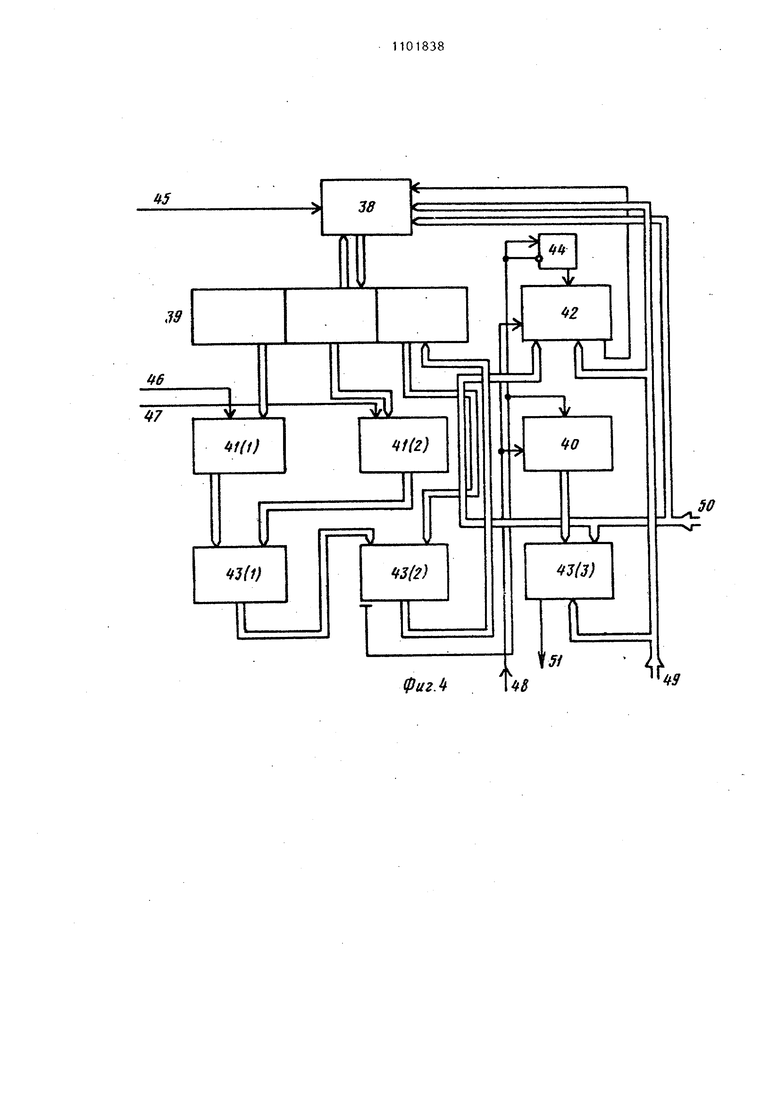

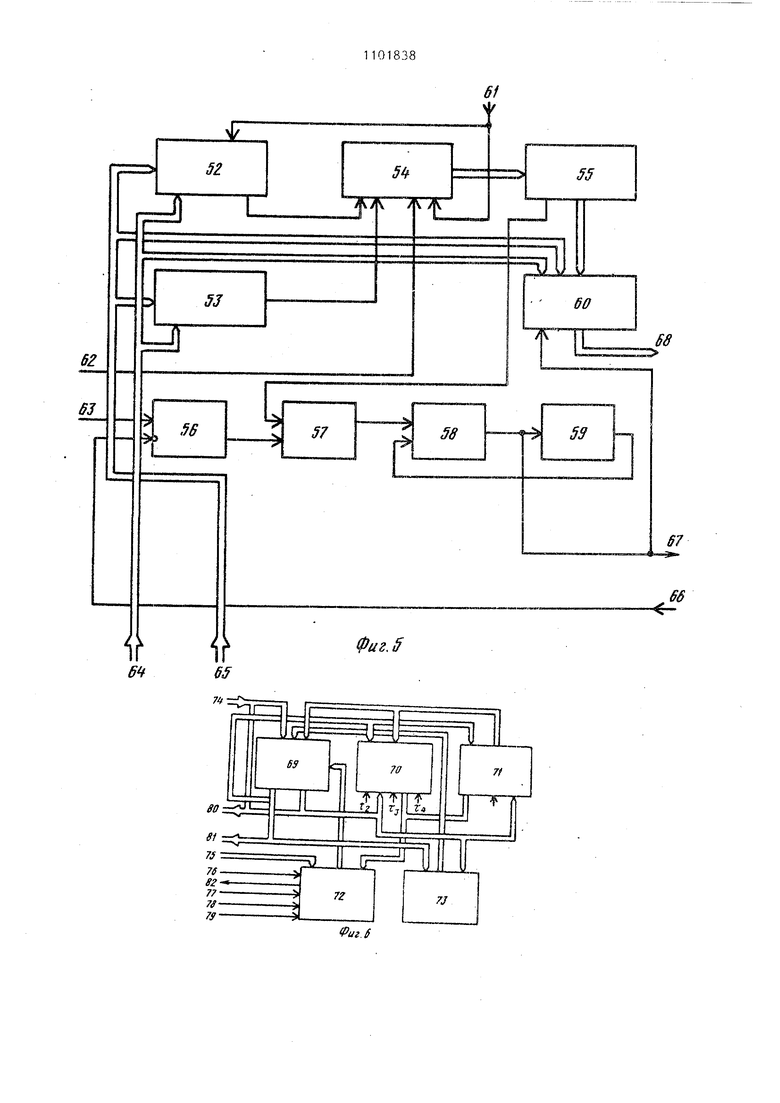

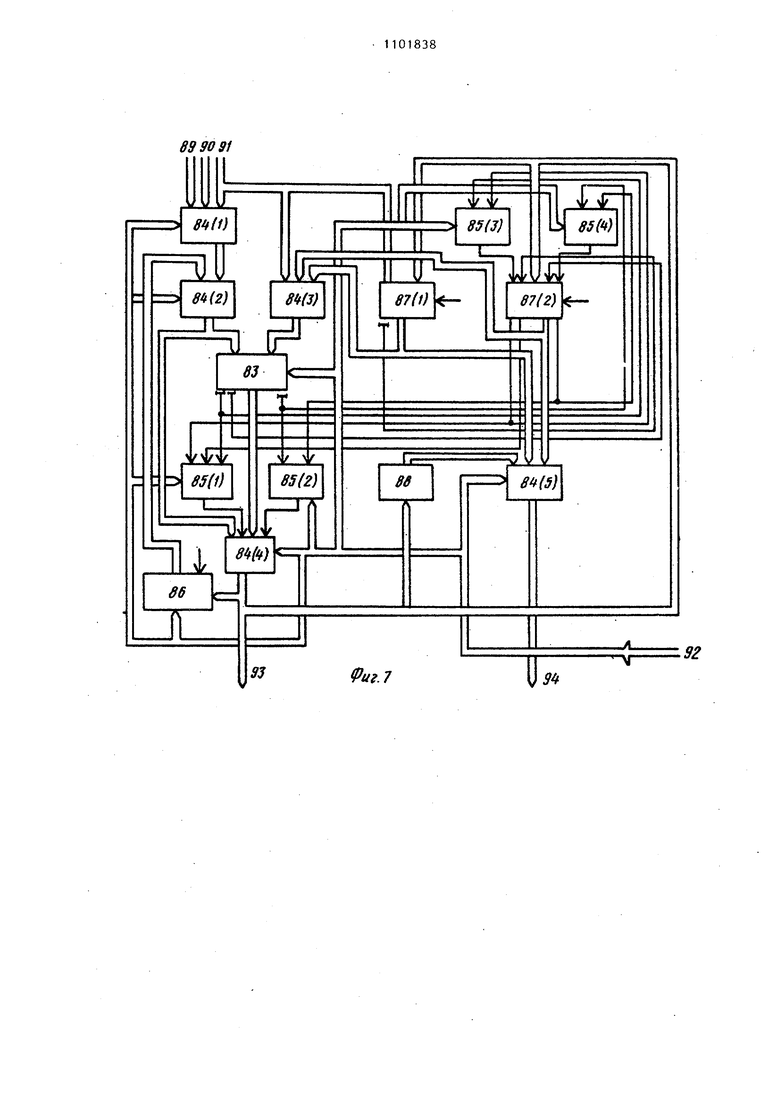

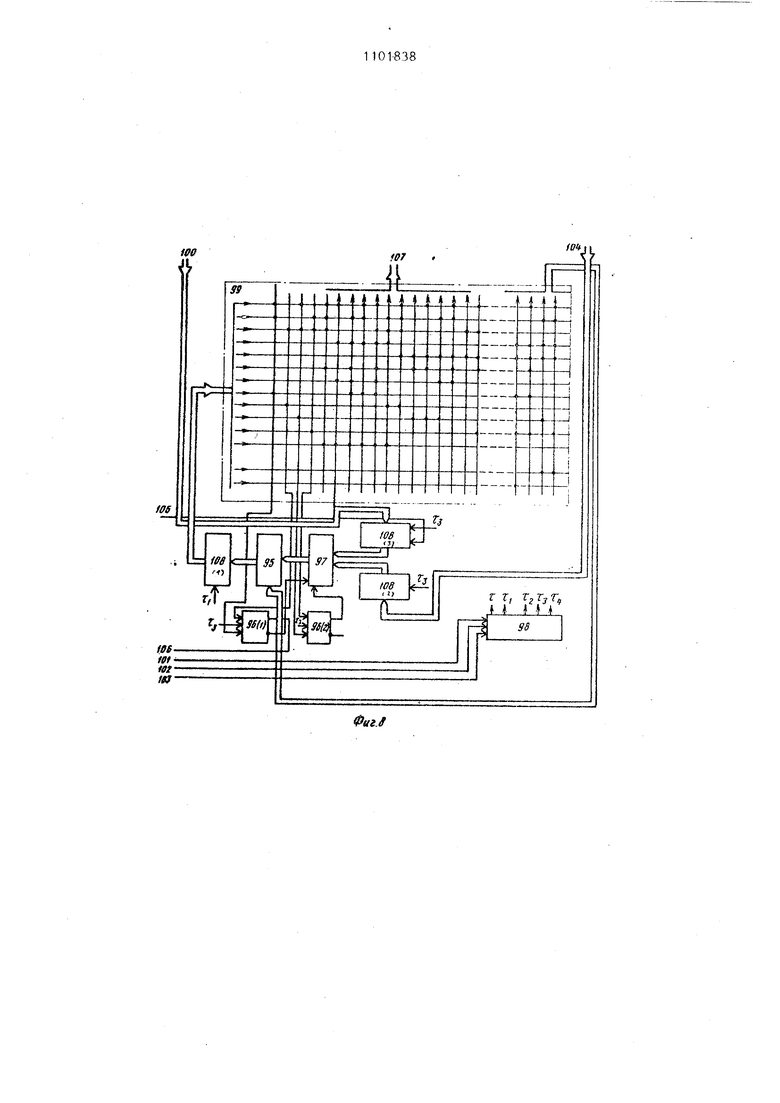

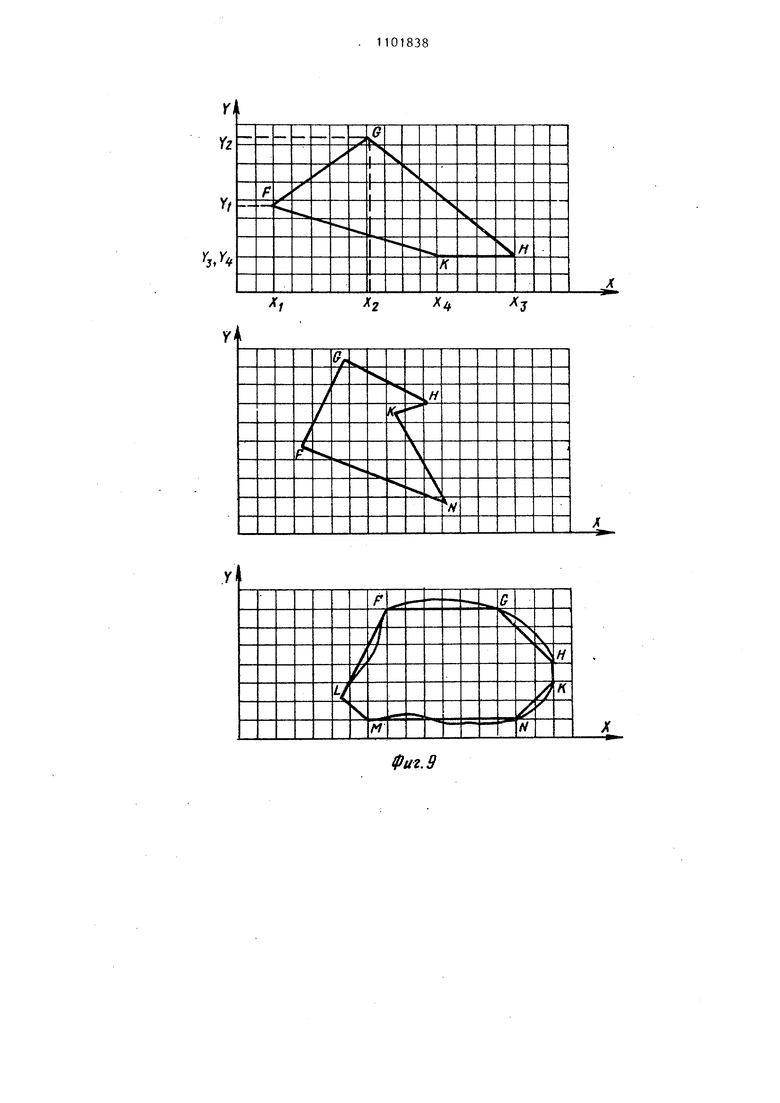

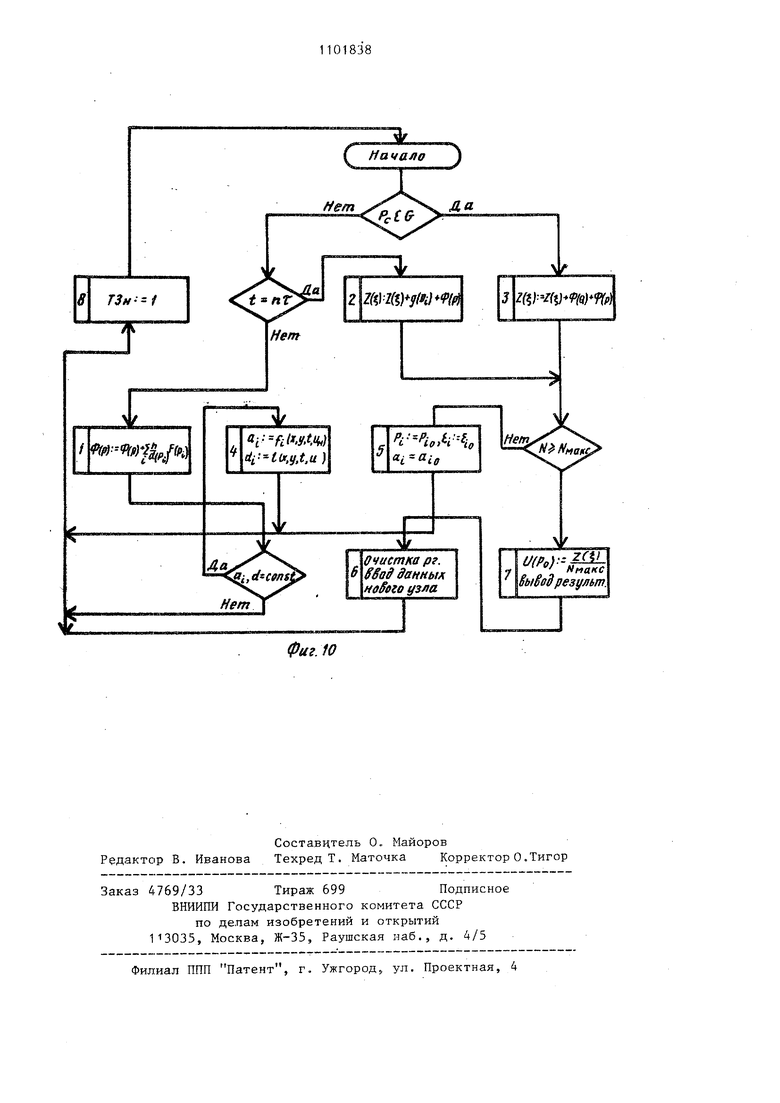

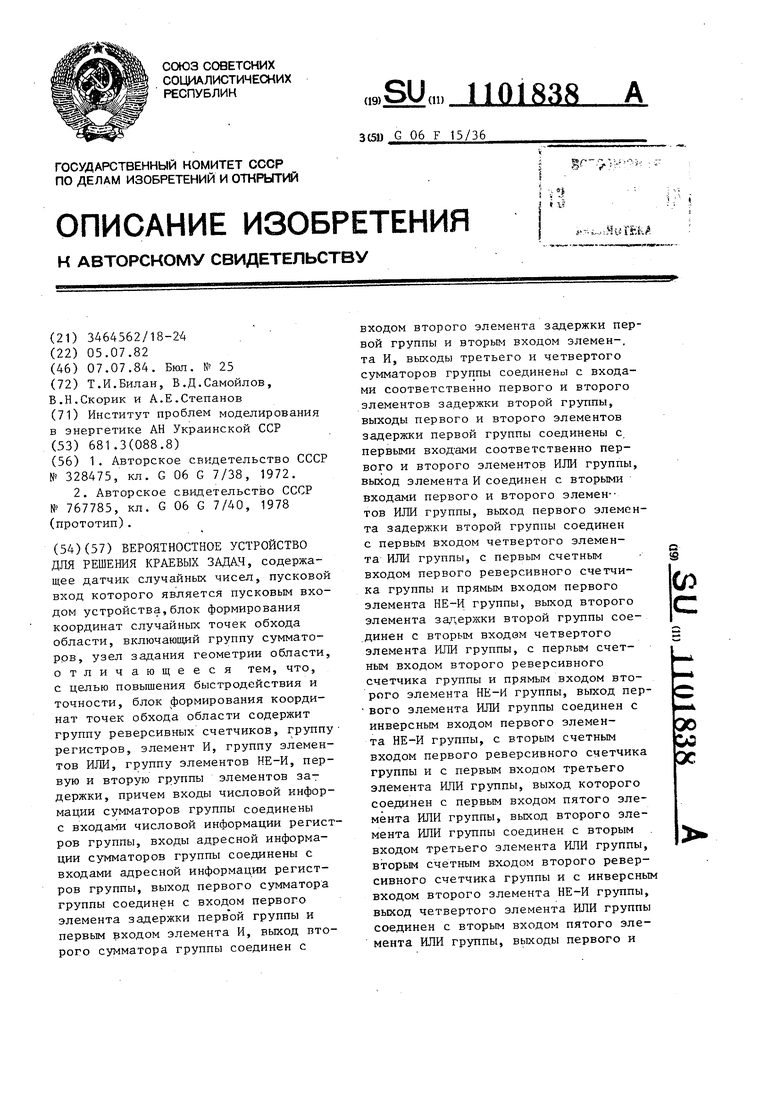

На фиг. 1 приведена блох-схема вероятностного устройства; на фиг, 2блок-схема возможной реализации датчика случайных чисел, на фиг. 3 блок-схема блока формирования координат случайных точек обхода областиj на фиг. 4 - блок-схема узла задания геометрии области; на фиг. 5 - блоксхема узла формирования адреса; на фиг. 6 - блок-схема узла вычисления вероятности перехода; на фиг. 7 блок-схема арифметико-логического блока узла вычисления вероятностей переходаJ на фиг. 8 - блок-схема блока управления узла вычисления вероятности перехода; на фиг. 9 - примеры задания геометрии области; на фиг. 10 - блок-схема алгоритма вероятностного решения краевых задач.

Вероятностное устройство содержит датчик 1 случайных чисел, блок 2 формирования координат случайных точек обхода области, узел 3 задания геометрии области, узел 4 формирования адреса, узел 5 вычисления вероятностей перехода, вход 6 установки признака изменения вероятности перехода, вход 7 останова, вход 8 сброса и пусковой вход 9.

Датчик 1 случайных чисел имеет счетчкк-делитель 10, генератор 11 тактовых импульсов, сумматор 12 по модулю два, сдвиговый регистр 13, группу 14 элементов И, элемент ИЛИ 15 .управляющий выход 16, информационный выход 17, пусковой вход 18, вход 19 синхронизации, вход 20 адресной информации и -ВХОД 2 1 числовой информации Блок 2 формирования координат случайных точек обхода области имеет группу 22 сумматоров, первую 23 и вторую 24 группы элементов задержки, элемент И 25, группу 3J eMeHтов ИЛИ 26, группу элементов НЕ-И 27

.

группу 28 реверсивныхсчетчиков, группу 29 регистров, информационный вход 30, вход 31 кода положения случайной точки, вход 32 числовой информации, вход 33 адресной информа11ИИ, выход 34 кода координат вершин случайных траекторий, выход 35 кодов приращений абсциссы, выход 36 кодов приращений ординаты и выход 37 останова.

Узел 3 задания геометрии области имеет блок 38 памяти, группу 39 регистров, сдвиговый регистр 40, группу 41 умножителей на знак, счетчик 42 группу 43 сумматоров, элемент НЕ- ИЛИ 44, управляющи вход 45, вход 46 кодов грмращений абсциссы, вход 47 кодов приращений ординаты, вход 48 синхронизации, вход 49 числовой информации, вход 50 адресной информации и выход 51 кода положения точки блуж,.т.ания .

Узел 4 формирования адреса имеет счетчик 52, счетчик-делитель 53, регистр 54, дещифратор 55, эле- . мент НЕ-ИЛИ 56, элемент И 57, триггер 58, элемент 59 задержки, блок 60 регистров, вход 61 кода положения случай}юй точки, вход 62 установки признака изменения вероятности перехода, вход 63 останова, вход 64 адресной информации, вход 65 числовой информации, управляющий вход 6 выход 67 синхронизации и -выход 68 кода команды..

Узел 5 вычисления вероятностей перехода имеет арифметико-логический блок 69, блок 70 оперативной памяти, блок 71 постоянной памяти, блок 72 управления, блок 73 индикации, вход 74 кода координат верщин случайных траекторий, вход 75 кода команды, вход 76 синхри.1зации, пусковой вход 77, вход 78 сброса, вход 79 останова, выход 80 адресной информации, выход 81 числовой информации и управляющий выход 82.

Арифметико-логический блок 69 узла 5 вычисления вероятностей перехода имеет сумматор 83, первую 84 и вторую 85 группы коммутаторов, блок 86 регистров, группу 87 регистров, счетчик 88, вход 89 кода координат верщин случайных траекторий, индикаторный вход 90, ииформационный вход 91 и вход 92 управляющей информации, выход 93 числовой информации и выход 94 адресной информации. .

Блок 72 управления узла 5 вычисления вероятностей перехода имеет дешифратор 95, группу 96 триггеров, коммутатор 97, синхронизатор 98, элемент 99 памяти, первьи 100, 101, четвертый 102, пятый 103, шестой 104, второй 105 входы, первый 106 и второй 107 выходы и груп-« пу 108 регистров.

Пусковой вход датчика 1 случайных чисел (фиг. 1) соединен с пусковым входом узла 5 вычисления вероятностей перехода и является пусковым входом 9 устройства. Вход останова и вход сброса узла 5 вычислений вероятностей перехода являются соответственно входом 7 останова и входом 8 сброса устройства. Выходы адресной и числовой информации узла 5 вычисления вероятностей перехода соединены с входами соответственно адресной и числовой информации узла 3 задания геометрии области, узла 4 формирования адреса, блока 2 формирования координат случайных точек обхода области, датчика 1 случайных чисел. Управляюцщй выход узла 5 вычисления вероятностей перехода соединен с управляюа(им входом узла 4 формирования адреса, выход кода команды которого соединен с входом кода команды узла 5 вычисления вероятностей перехода, а выход синхронизации соединен с входами синхронизации узла 5 вычисления вероятностей перехода, узла 3 задания геометр1 И области, датчика 1 случайных чисел. Управляющий выход датчика 1 случайных чисел соединен с управляющим входом узла 3 задания геометрир области, выход кода положения случайной точки которого соединен с гходам кода положения случайной точки узла 4 формирования адреса и блока 2 формирования координат случайных точек обхода области. Выходы кодов приращений абсциссы и ординаты блока 2 соединены с входами кодов приращений соответственно абсциссы и ординаты узла 3 заданий геометрии области, а выход останова соединен с входом останова узла 4 формирования адреса, вход установки признака изменения вероятности перехода которого является входом 6 установки признака изменения вероятности перехода устройства. Информационный выход датчика 1 случайных чисел соединен с информационным входом блока 2 13 формирования координат случайных то чек обхода области, выход кода коор динат вершин случайных траекторий которого соединен с входом кода коо динат вершин случайных траекторий узла 5 вычисления вероятностей пере хода. Первый и второй вход; : элемента ИЛИ 15 в датчике 1 случайных чисел (фиг. 2) являются соответственн пусковым входом 18 и входом 19 датчика 1, а выход является управляклцим выходом 16 датчика 1 и соединен с п вым входом генератора 11 тактовых импульсов, выход которого соединен с первым входом сумматора 12 по модулю два и входом счетчика-делителя 10. Выход счетчика-делителя 10 соединен с вторым входом генератора 11 тактовых импульсов и первыми входами элементов И группы 14, вторые входы которых соединены с выход ми разрядов сдвигового регистра 13, а выходы являются информационным выходом 17 датчика 1. Выход суммато ра 12 по модулю два соединен с входом сдвигового регистра 13, первый и второй выходы которого соединены соответственно с вторым и третьим входами сумматора 12 по модулю два. Входы адресной и числовой информаци счетчика-делителя 10 соединены с вх дами соответственно адресной и чис ловой информации сдвигового регистра 13 и являются входами соответственно адресной 20 и числовой 21 информации датчика 1. Устройство работает следующим образом. Инициирует работу устройства наличие пусковых сигналов (ах;од 9) и сброса (начальная установка вход 8). При этом в узле 5 выполняется программа, зашитая в блоке 71 постоянной памяти, заключающаяся в очистке регистров, сбросе в ноль триггеров и переводе узла 5 в режим ожидания. Параллельно с узлом 5 нач нает работу блок 3, в котором по пу ковому сигналу на входе 45 содер5Шмое основание блока 38 памяти (стековой памяти) переписывается в блок 39 регистров, а на следующем такте из него в умножители на знак группы 41 и второй сумматор группы 4 После этого узел 3 также приходит в режим ожидания. Начинается работа датчика 1 случайных чисел при посту 38 лении пускового сигнала на вход 18, который определяет через элемент ИЛИ 15 наличие единичного сигнала генератора 11 тактовых импульсов. Приход каждого импульса увеличивает содержимое счетчика-делителя 10 на единицу и обеспечивает сдвиг содержимого сдвигового регистра 13. Через, К тактов управляющий сигнал с выхода счетчика-делителя 10 останавливает генератор 11 тактовых импульсов и стробирует вывод содержимого СДВИГОВОГО регистра 13 через выход ;ые элементы И группы 14 на выход 17 датчика 1 случайных чисел. С появлением псевдослучайного двоичного числа на входе 30 блока 2 начинается его работа. В сумматорах группы 22 параллельно происходит вычитание псевдослучайного числа из значений вероятностей перехода, хранящихся : в сумматорах, выходами которых являются знаковые разряды. Знак минус мокет получиться только на одно.м из выходов, определяя тем самым направление случайного шага. При появлении единичных сигналов на первых входах реверсивных счетчиков их содержимое увеличивается на единицу, а на вторых - уменьшается на единицу. Полученные значения координат через выход 34 считываются узлом 5. На выходах приращений координат 35 и 36 единичный сигнал появится, если блуждающая точка перешла из одной точки в другую. При наличии единичного на входе 31, свидетельствующем о построении новой случайной траектории и с той же стартовой точк;, содержимое регистров группы 29 записывается соответственно в реверсивные счетчики группы 28. . С появлением кодов приращений на входах 46 и 47 возобновляется работа узла 3. Параллельно в умножителях ла знак группы 41 вычисляются произведения аДх и buy. В первом сумматоре группы 43 формируется приращение невязки АС аи X +Ьйу, которое во втором сумматоре группы 43 складывается с Tejvyu HM значением невязки. Код знаков сформируется на п тактов, где VI - число сторон многоугольника, аппроксимирующего границу Коды на входах 46 и 47 сохраняются в течение всех п тактов без изменения, пока не просчитываются все П значений невязки. 15. После каждого вычисления невязки содержимое счетчика 42 уменьшается на единицу. При обнулении счетчика на выходе последнего появи ся единичный сигнал, запрещаю ций за пись из блока 38 в блок 39, и содер жимое сдвигового регистра 40 переписывается в третий сумматор группы 43. Здесь происходит сравнение кода знаков с полным кодом условия пребывания внутри области. На вькоде 51 появляется нулевой код, если в результате случайного шага траектория не выходит за пределы границы области, и единичный - в противном случае. Если блуждающая точка остается внутри области, то процесс- подсчета невязок и анализа знаков повторяется при поступлении инициирующего сигнала на вход 45 при новых значениях .U X и U у на входах 46 . 4 При пересечении границы в блоке 38 восстанавливается значение не вязки EQ В стартовой точке, В обо их случаях восстанавливается значение счетчика 42 после обнуления. Сигнал с выхода 49 блока 3 задания геометрии области поступает на вход 61 блока 4 формирования адреса В зависимости от него содержимое счетчика 52 либо остается без изменения, либо увеличивается на единиц если граница пересечена. На вькоде счетчика 52 будет единичный сигнал, если N случайных -траекторий из начальной точки блуждания построено и нуль - в противном случае. После выполнения случайного шага содержимое счетчика-делителя 53 уменьшается на единицу. На выходе счетчика-делителя 53 будет единичны сигнал, если К шагов сделано и нуле вой - в противном случае. Если решается стационарное уравнение, то на выходе счетчика - делителя 53 по держивается постоянный нуль. На входе 62 будет постоянная единица, если коэффициенты решаемого уравнения переменные и постоянный нуль в противном случае. Таким образом, на регистр 54, а следовательно на вход дешифратора 55, поступают коды приведенные в таблице. В соответствии с таблицей на выходе дешифратора 55 формируется код адреса начала программы, записанной в памяти узла 5, который записывает 3816 ся в блок 60 регистров, В первом блоке 60 записан посгоянно код операции-обращения к блоку 71 постоянной памяти ,узла 5, инициирующий микропрогра)чму выборки команды из памяти. Содержимое блока 60 поступает на выход 68 блока 4 при наличии единичного сигнала на выходе триггера 58, который переводится в единичное состояние при наличии обращения к узлу 5 от блока 2, разрешении обращения от блока 5 (ноль на входе 66) при единичном сигнале на первом выходе дешифратора 55. Выход триггера 58 является также выходом 67 узла 4 . Он является сигналом, стробируквцим запись кода команды в узел 5 и возобновляет работу последнего. На следующем такте (через элемент 59 задержки) триггер 58 сбрасывается. Код команды по входу 105 блока 72 записывается в третий регистр группы 108 и 1Ерез коммутатор 97 (при единичном управляющем сигнале) с инверсного выхода первого триггера группы 96 поступает на дешифратор 95. Код команды преобразуется в код входных сигналов (кодов микрокоманд) блока 99 памяти, поступающих на вход последнего через первый регистр группы 108. В соответствии с входным сигналом на ряде вертикальных шин (в соответствии с прошивкой) появляются единичные сигналы (код микроопераций), определяющие работу элементов и узлов блока 69 и поступакщие на вход последнего с выхода 107. Адресная часть команд поступает в блок 69 через первый коммутатор первой группы 84. Первой микрокомандой каждой первой команды программы является микрокоманда начала программы, переводящей первый триггер группы 96 в единичное состояние, Единица на прямом выходе первого триггера 96 (выход 105) запрещает обращение к узлу 5 до конца программы, а нуль на инверсном выходе - прохождения кода команды с второго регистра группы 108 на вход дешифратора 95 через -коммутатор 97. Первый триггер группы 96 сбрасывается последней микрокомандой последней команды программы. Каждая команда начинается, с микрокоманды Начало команды (в первой команде программы она является второй). По этой микрокоманде второй триггер 17 группы 96 переводится в единичное состояние. Его прямой вход стробирует прохождение команды с третьего регистра группы 108 на вход дешифратора 95 через коммутатор 97. Код команды поступает в третий регистр группы 108 через вход 104 с блока 71 постоянной или 70 опера тошной памяти блока 5. Второй триггер группы 96 сбрасывается в конце каждой команды микрокомандой Конец команды. При вьтолнении команды код каждой следую щей микрокоманды формируется в бло-ке99 памяти автоматически. Появление единичных управпяюицлх сигналов Пуск, Сброс, Останов на входах 101-103 запускают блок 98 синхро низа1 ии, обеспечивающий выработку сигналов, тактирующих работу узла 5. Управляющие сигналы, поступающие на вход 92 блока 69, обеспечивают прохождение входных операндов на сум матор 83 через коммутаторы группы 84 регистров Г.уппы 87 через четвертый коммутатор группы 84, выполнение операций сдвига влево в первом и третьем коммутаторах группы 85 и впр во во втором и четвертом коммутаторах группы 85, хранение промежуточных результатов и использование их в качестве операндов в процессе счета в блоке 86 регистров, а также фор мирование и вьщачу адреса элементов датчика 1, блока 2 и узлов 3-5 при пересылке в них информации или а/дреса блока памяти, по которому записана следующая команда в соответствии с программой или числовая информация через пятый коммутатор группы 84, Во избежание ложного срабатывания в коде адреса содержатся (Зшажки, определяю1цие обращение к блоку 70 оперативной памяти, блоку 71 постоян

1001

10000 0100

20001

01 10

9 10

ООП 11100 1011 38 ной памяти или элеме))том л.атчика 1 , блока 2, узлов 3 и 4. (Ь.пажками являются соответственно коды 00, 01 или 11 в младших разрядах. 1-lcjin в младших разрядах код 11, то адресная информация запоминающими устройствами игнорирует. Вывод числовой информации осуществляется с В1 1хода сумматора 83, где она обрабатр тается или непосредственно с входов 89-91, минуя сумматор, через коммутаторы группы 84. Числовая информация может либо пересыпаться в соответствующие элементы блоков 14, либо выводиться на блок 73 индикации. По окончании работы узла 5, реализующего программы в соответствии с алгоритмом, приведенном на фиг. 10, возобновляется работа остальных узлов. Сигналом, ИНИЦ1Н1РУЮЩИМ работу датчика 1 случайн1)1Х чисел и узла 3, является единичный си1Л{;и1 с выхода триггера 58 ajjoKa 4 (выход 67) , поступающего на вход 19 датчика 1 случайных чисел. Таким обра.зом, по окончании выполнения программы (сброс первого триггера группы 96 в блоке 60 регистров узла 4) сформируется новый (или повторится предьщущ й) адрес в зависимости от кода в регистре 54 в соответствии с таблицей. Изложенная организация вычислительного процесса, реализованного в предложе} ном устройстве, отличается более высоким быстродействием и точностью по сравнению с известным устройством. Ожидаемый годовой экономический эффект от использования одного образца предложенного устройства при решении задач математической физики составляет около

-.32 -.33

-J

Фиг 6

899091

Yz

УЛ

//

N.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для РЕШЕНИЯ ЗАДАЧ МАТЕМАТИЧЕСКОЙ ФИЗИКИ | 0 |

|

SU328475A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вероятностное вычислительное устройство для решения трехмерных краевых задач | 1978 |

|

SU767785A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-07—Публикация

1982-07-05—Подача