Изобретение относится к радиотехнике и может йс ПОЛЬ з оват ься, напр и- мер, в различных измеритель.ных устройствах, в частности в устройствах ля измерения скорости вращения валов, 5

Целью изобретения является повышение точности умножения частоты.

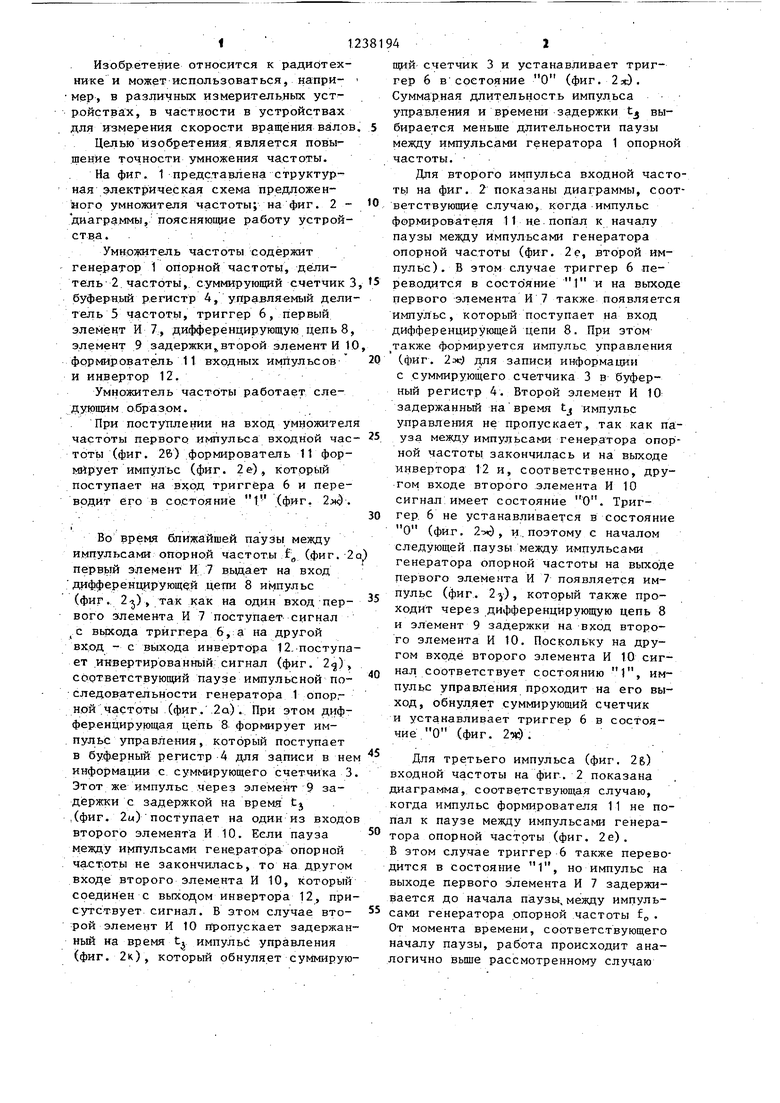

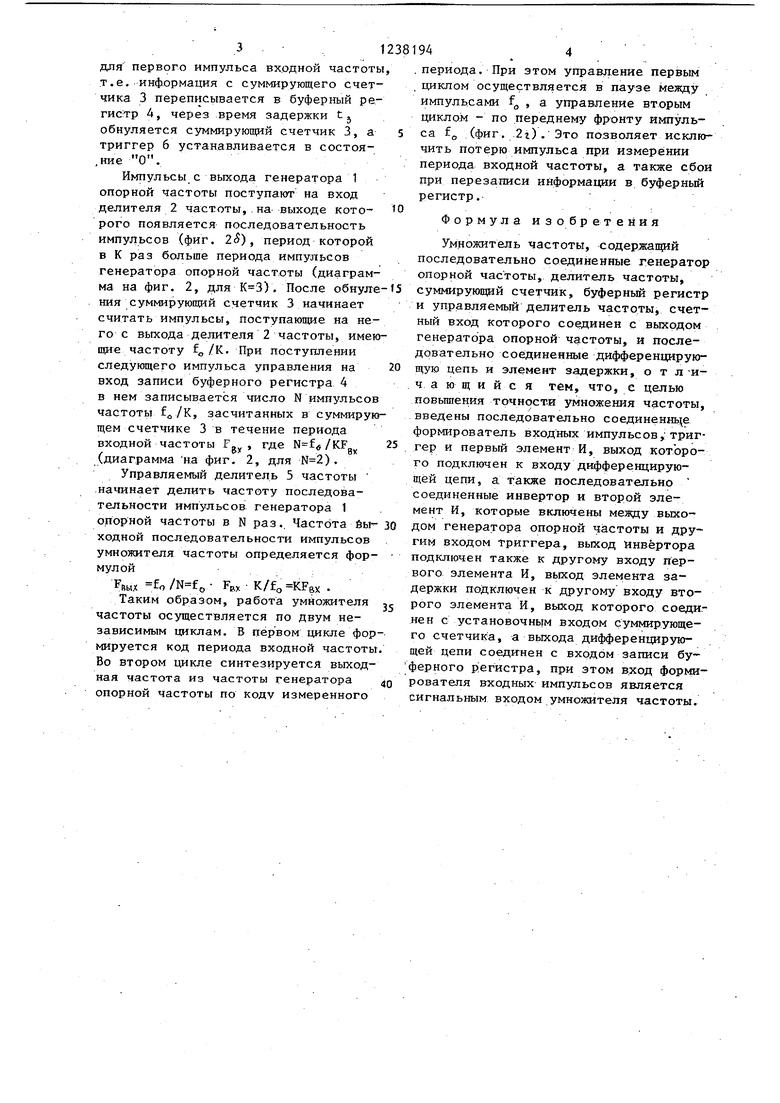

На фиг. 1 представлена структурная электрическая схема предложен- Ногр умножителя частоты; на фиг. 2 - О диаграммы, поясняющие работу устройства .

Умножитель частоты содержит генератор 1 опорной частоты, делитель 2. частоты,, суммирующий счетчик 3, 5 буферный регистр 4, управляемый делитель 5 частоты, триггер 6, первый элемент И 7, дифференцирующую цепь 8, элемент 9 задержки второй элемент И 10, Формирователь 11 входных импульсов 20 и инвертор 12.

Умножитель частоты работает следующим образом.

. При поступлении на вход умножителя частоты первого импульса входной час- 25 тоты (фиг. 26) формирователь 11 формирует импулъс (фиг. 2 е), котррьй поступает на вход триггера 6 и переводит его в состояние 1 (фиг. 2м,

. : ; / : . - . зо

I . ...., .

Во время ближайшей паузы между импульсами опорной частоты f (фиг. 2а) первый элемент И 7 выдает на вход

дифференцирующей цепи 8 импульс (фиг. 2), так как на один вход пер- вого элемента И 7 поступает сигнал

с вьрсода триггера 6, а на другой вход - с выхода инвертора 12.-поступа- ет инвертированный сигнал (фиг. 2.3), соответствующий паузе импульсной по- следовательности генератора 1 опор,- ной .частоты (фиг. .2а) . При этом дифференцирующая цепь 8 формирует импульс управления, который поступает в буферный регистр 4 для записи в нем информации с суммирующего счетчика 3. Этот же импульс .через элемент 9 задержки с задержкой на время tj ,(фиг. 2м) поступает на один из входов второго элемента И 10. Если пауза 50 между импульсами гене.ратора опорной част.Ъты не закончилась, то на другом входе второго элемента И 10, который соединен с вьгходом инвертора 12, присутствует сигнал. В этом случае вто- 55 рой элемент И 10 пропускает задержанный на время t импуЛьс управления (фиг. 2к), который обнуляет суммирующий счетчик 3 и устанавливает триггер 6 в состояние О (фиг. 2эс). Суммарная длительность импульса управления и времени задержки выбирается меньще длительности паузы между импульсами генератора 1 опорно частоты.

Для второго импульса входной частты на фи.г. 2 показаны диаграммы, сооветствующие случаю, когда импульс формирователя 11 не.попал к началу паузы между импульсами генератора опорной частоты (фит. 2е, второй импульс). В этом случае триггер 6 переводится в состояние 1 и на выход первого элемента И 7 также появляетс импульс, который поступает на вход дифференцирующей цепи 8. При этом также формируется импульс управления (фиг. 2з для записи информации с суммирующего счетчика 3 в буферный регистр 4. Второй элемент И 10 задержанный на время tj импульс управления не пропускает, так как пауза между импульсами генератора опорной частоты закончилась и на выходе инвертора 12 и, соответственно, другом входе второго элемента И 10 сигнал имеет состояние О. Триггер. 6 не устанавливается в состояние О (фиг. 2, и. поэтому с началом следующей паузы между импульсами генератора опорной частоты на выходе первого элемента И 7 появляется импульс (фиг. 2), который также проходит через дифференцирующую цепь В и элемент 9 задержки на вход второго элемента И 10. Поскольку на другом входе второго элемента И 10 сигнал соответствует состоянию 1, импульс управления проходит на его выход, обнул.яет суммирующий счетчик и устанавливает триггер 6 в состояние. О (фиг. .

Для третьего импульса (фиг. 2&) входной частоты на фиг. 2 показана диаграмма, соответствующая случаю, когда импульс формирователя 11 не попал к паузе между импульсами генератора опорной частоты (фиг. 2е). В этом случае триггер 6 также переводится в состояние 1, но импульс на выходе первого элемента И 7 задерживается до начала паузы,между импульсами генератора опорной частоты fj, . От момента времени, соответствующего началу паузы, раб ота происходит аналогично вьщге рассмотренному случаю

3 . . 1 для первого импульса входной частоты т.е. информация с суммирующего счетчика 3 переписывается в буферный ре- гис;тр 4, через время задержки tj обнуляется суммирующий счетчик 3, а триггер 6 устанавливается в состоя- ,ние О.

Импульсы с выхода генератора 1 опорной частоты поступают на вход делителя 2 частоты,.на выходе кото- рого появляется последовательность импульсов (фиг. 25), период которой в К раз больше периода импульсов генератора опорной частоты (диаграмма на фиг. 2, для ). После обнуле ния суммирующий счетчик 3 начинает считать импульсы, поступаюпще на него с выхода делителя 2 частоты, имеющие частоту „/.. При поступлении следующего импульса управления на вход записи буферного регистра 4 в нем записывается число N импульсов частоты fo/К, засчитанных в суммирующем счетчике 3 в течение периода входной частоты F,, , где N fe/KF

/

(диаграмма на фиг. 2, для ).

Управляемый делитель 5 частоты начинает делить частоту последовательности импульсов генератора 1 опорной частоты в N раз.. Частота бы- ходной последовательности импульсов умножителя Частоты определяется фор- мулой:

РВЫХ Fp, . Таким образом, работа умножителя частоты осуществляется по двум независимым циклам. В первом цикле формируется код периода входной частоты Во втором цикле синтезируется выходная частота из частоты генератора опорной частоты по коду измеренного

1944

. периода. При этом управление первым , циклом осуществля1ется в паузе между импульсами f, , а управление EITOPMM циклом - по переднему фронту импульса f-g (фиг. .2г). Это позволяет искпкг- чить потерю импульса при измерении периода входной частоты, а также сбои при перезаписи информации в буферный регистр.

Форм у л а изобретения

Умножитель частоты, содержащий последовательно соединенные генератор опорной частоты, делитель частоты, суммирующий счетчик, буферный регистр и управляемьй делитель частоты, счетный вход которого соединен с выходом генератора опорной частоты, и последовательно соединенные дифференцирующую цепь и элемент задержки, о т л -и- ч а ю щ и и с я тем, что, е целью повышения точности умножения частоты, введены последовательно соединеннь е формирователь входных импульсов,; триггер и первый элемент И, выход которого подключен к входу дифференцирующей цепи, а также последовательно соединенные инвертор и второй элемент И, которые включены между выходом генератора опорной частоты и другим входом Триггера, выход Инвертора подключен также к другому входу первого элемента И, выход элемента задержки подключен к другому входу второго элемента И, выход которого соеди.- нен с установочным входом суммирующего счетчика, а вьгхода дифференцирующей цепи соединен с входом записи бу- ферного регистра, при этом вход формирователя входных импульсов является сигнальным входом умножителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения и регулирования соотношения скоростей | 1985 |

|

SU1364993A1 |

| Устройство задержки импульсов | 1978 |

|

SU790205A1 |

| Устройство для измерения и регулирования соотношения скоростей | 1984 |

|

SU1224726A1 |

| УСТРОЙСТВО АКТИВНОЙ ЗАЩИТЫ И ОБЕСПЕЧЕНИЯ ТЕХНИЧЕСКОЙ ГОТОВНОСТИ ЭЛЕМЕНТОВ РАСПРЕДЕЛЕННОЙ ЛОКАЛЬНОЙ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ В УСЛОВИЯХ ВНЕШНИХ ДЕСТРУКТИВНЫХ ВОЗДЕЙСТВИЙ | 2006 |

|

RU2316810C2 |

| Умножитель частоты | 1988 |

|

SU1626315A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Умножитель частоты следования импульсов | 1983 |

|

SU1140220A1 |

| Анализатор параметрических отказов | 1986 |

|

SU1405075A1 |

| Устройство для измерения ускорений | 2022 |

|

RU2793846C1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

Изобретение относится к радиотехнике. Повышается точность умножения частоты. Работа умножителя частоты осуществляется по двум независимым циклам. В первом цикле формируется код периода входной частоты. Для этого импульсы с генератора Г опорной частоты поступают на делитель 2 частоты. Импульсы с его вьпсо- да поступают на суммирующй счетчик (СС) 3. При поступлении импульса управле тя на буферный .регистр 4, в него запишется информация (число N) с СС 3, соответствующая периоду входной .частоты. Управляющий сигнал для записи в буферный регистр 4 формируется во время паузы между импульсами опорной частоты с помощью формирователя 11 входных импульсов, триггера 6 элемента И 7, на который поступает сигнал паузы с инвертора 12, и дифференцирующей цепи 8. Сигнал для обнуления СС 3 и установления триггера 6 в состояние О формируется из управляющего сигнала дифференцирующей цепи В с помощью элемента 9 задержки и элемента И 10. Во втором цикле синтезируется выходная частота из частоты генератора 1 по коду измеренного периода. Это осуществляет управляемый делитель 3 частоты, на который поступает последовательность импульсов генератора 1 и код N с буферного регистра 4. 2 ил. ел СС 00 г/. со 4

| Умножитель частоты следования импульсов | 1982 |

|

SU1018190A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для умножения частотыСлЕдОВАНия иМпульСОВ | 1979 |

|

SU836756A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-06-15—Публикация

1984-11-10—Подача