(54) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1978 |

|

SU781832A1 |

| Умножитель частоты | 1978 |

|

SU765818A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2210102C1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для моделирования узлов коммутации сообщений | 1986 |

|

SU1354203A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Цифровой генератор гармонических функций | 1983 |

|

SU1224802A1 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для умножения частоты периодических сигналов.

Известен умножитель частоты, содержащий входной формирователь импульсов , генератор опорной частоты, счетчик, управляемый делитель частоты, дешифраторы, формирователь импульсов ввода, триггеры и элементы И и ИЛИ 1.

Известен также умножитель частоты, содержащий коммутаторы, генератор опорной частоты, блок упра вления, делитель частоты, счетчик,формирователи, регистры памяти, цифреуправд яемую линию задержки, элемент ИЛИ rf группы элементов И 2,

Недостатком известных устройств является пониженная точность умножения, обусловленная погрешностью .дискретиз/ации периода входного сигнала.

Наиболее близким к предлагаемому является умножитель частоты, содержащий блок синхронизации, подклю енный входом к шине ввода умножаемой частоты, первым выходом -iK управляющему входу регистра и к входу обнуления накапливающего сумматора.

а вторым йыходом - к первому входу элемента ИЛИ к к входу обнуления суммирующего счетчика, счетный вход которого соединен с выходом генератора опорной частоты, а выходы разрядов - с информационными входами регистра, подключенного выходами старших разрядов к установочным входам вычитающего счетчика, а выхо дами младших разрядов - к суммирующим входам старших и младших разрядов накапливающего сумматора, вход управления суммированием котоpcJro подключен к выходу переполнения вычитающего счетчика, второму входу элемента ИЛИ и к первому установочному входу триггера, соединенного вторым установочным входом с счетным входом вычитающего счетчика и с выходом мультиплексора, управляющие входы которого подключены к вЫходгил старших разрядов накапливающего сумматора, а информационные входы к выходам линии задержки, соединенной входом с выходом генератора опорной частоты, причем выход элемента ИЛИ подключен к входу управления установкой кода вычитающего счетчика,

а выход триггера соединен через

ЛИфференцирующий элемент с выхо. .ной шиной умножения частоты 3.

Недостатком устройства также является пониженная-точность умножения частоты,обусловленная погрешностью дискретизации периода входного сигнала.

Цель изобретения - повышение точности умножения частоты за счет уменьшения погрешности от дискретизации периода входного сигнала.

Эта цель достигается тем, что в умножитель частоты, содержащий блок синхронизации, подключенный входом к шине ввода умножаемой частоты, первым выходом - к управляющему входу первого регистра,и к входу обнуления накапливающего сумматора, а вторым выходом - к первому входу элемента ИЛИ и к входу обнуления суммирующего счетчика, счетный вход которого соединен с выходом генератора опорной частоты, а выходы разрядов - с информационными входами первого регистра, подключенного выходами старших разрядов к установочHbiM входам вычитающего счетчика, а выходами младших разрядов - к суммирующим входам старших разрядов накапливающего сумматора; вход управления суммированием которого подключен к выходу переполнения вычитающего счетчика, второму входу элемента ИЛИ и к первому установочному входутриггера. Соединенного вторым установочным входом с счетным входом вычитающего счетчика и с выходом мультиплексора, управляюие входы которого подключены к выходатд старших разрядов накапливающего сумматора, а информационные входы - к выходам линии задержки, соединенной входом с выходом генератора опорной частоты, причем выход элемента ИЛИ подключен к входу управления установкой кода вычитающего счетчика, а выход триггера соединен через дифференцирующий элеент с выходной шиной умножителя частЬты, дополнительно введены второй и третий регистры, шифраторы и группа элементов И, подключенных перЬыми входамик выходам первого ифратора, пторыми входами - к втоporiy выходу блока синхронизации, а выходами - к установочным входам старших разрядов накапливающего сумматора, соединенного суммирующими входами младших разрядов с выходами второго шифратора, причем выходы инии задержки подключены к информаЦИОННЫ1.1 входам второго регистра, соединенного выходами с входами первого шифратора и с,информационныи входами третьего регистра, а входы второго шифратора подключены к выходам второго и третьего регистов, соединенных управляющими входами с первым выходом блока синхронизации.

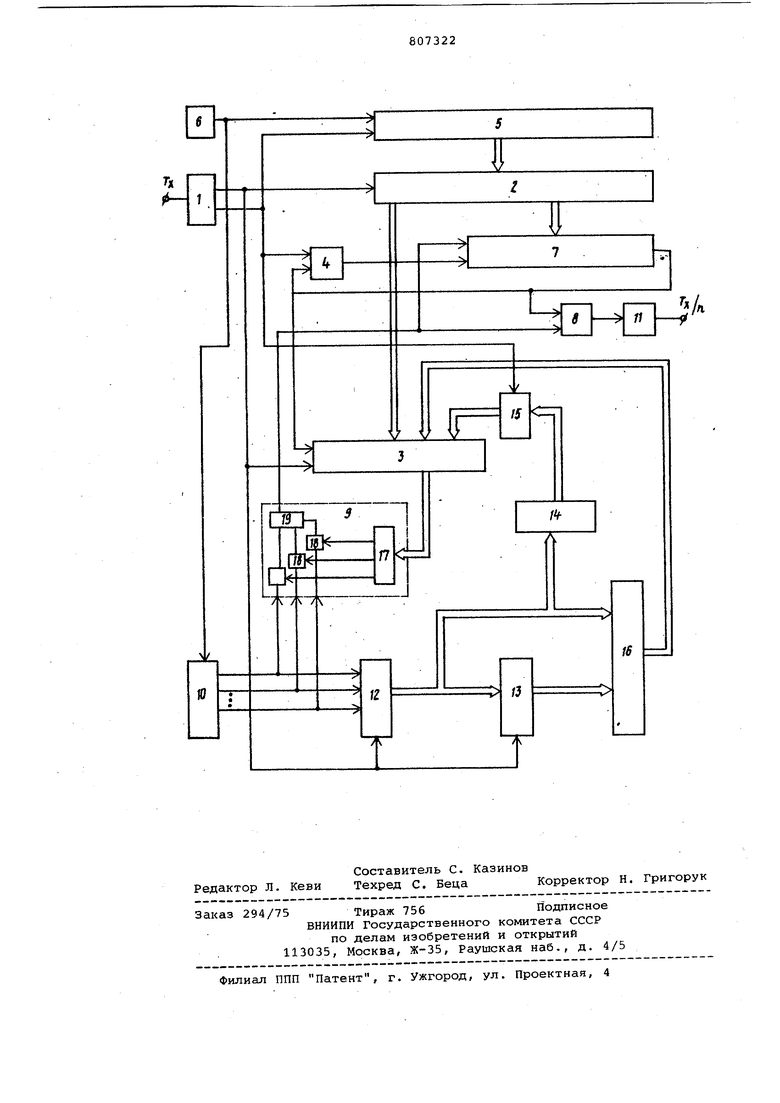

На чертеже изображена блок-схема умножителя частоты.

Умножитель частоты содержит блок f 1 синхронизации, подключенный входом к шине ввода умножаемой частоты, первым выходом - к управляющему входу первого регистра 2 и к входу обнуления накапливающего сумматора 3,

Q а вторым выходом - к первому входу элемента ИЛИ 4 и к входу обнуления суммирующего, счетчика 5. Счетный вход счетчика 5 соединен с выходом генератора 6 опорной частоту, а выходы разрядов - с информационными

5 входами регистра 2, Регистр 2 подключен выходами старших разрядов к установочным входам вычитающего счетчика 7, а выходами младших разрядов - к суммирующим входам старших разрядов накапливающего сумматора 3. Вход управления суммированием сумматора 3 подключен к выходу переключения вычитающего счетчика 7, второму входу элемента ИЛИ 4 и

5 к первому установочному входу триггера 8, соединенного вторым установочным входом с счетным входом вычитающего счетчика 7 и с выходом мультиплексора 9. Управляющие входы

мультиплексора 9 подключены к выходам старших разрядов сумматора 3, а информационные входы - к выходам линии 10 задержки. Линия 10 задержки соединена входом с выходом генератора б опорной частоты. Выход элемента ИЛИ 4 подключен к входу управления установкой кода счетчика 7., Выход триггера 8 соединен через дифференцирующий элемент 11 с выходной шиной умножителя частоты. Выходы линии 10 задержки подключены также к информационным входам второго регистра 12, соединенного выходами с информационными входами третьего регистра 13 и с входами

первого шифратора 14, Управляющие входы регистров 12 и 13 подключены к- первому в.ыходу блока 1 синхронизации. Выходы шифратора 14 соединены, с первыми входами группы элементов

И 15, подключенных вторыми входами к второму выходу блока 1 синхронизации, а выходами - к установочным входам старших разрядов сумматора 3. Суммирующие, входы младших разрядов сумматора 3 соединены с выходами второго шифратора 16, подключенного входами к выходам регистров 12 и 13.

Шифратор l4 преобразует код, зафиксированный в регистре 12 в двоичный, а шифратор 16 преобразует в двоичный код разность кодов, зафиксированных в регистрах 12 и 13. Мультиплексор 9 осуществляет передачу на выход импульсной последовательности с одного из своих информационных входов, номер которого соответствует,двоичному коду, поступающему на управляющие входы мультиплексора. Мультиплексор 9 может быть выполнен, например, на дешифраторе 17, группе элементов И 18 и-элементе ИЛИ 19. Умножитель частоты работает следующим образом. На входную шину и, соответственно на вход блока 1 синхронизации поступает входйой сигнал, период которого . При переходе через определенный уровень,- например при возрастании сигнала, на выходах блока 1 формируются короткие импульсы, которые .используются для ввода кода из счетчика 5 в регистр 2 (импульсом с первого выхода блока 1) и для обнуления счетчика 5 (импульсом с второго выхода блока 1), причем импульс на первом выходе .блока 1 формируется раньше, чем импульс на втором выходе этого блока. За период входного сигнала в счетчик 5 от генератора 6 опорной частоты (период которой раве TO) поступает количество импульсов, равное Г,,.1 - целая часть отношения (также как и В последующих формулах). Возникающая при этом погрешность дискретизации начала и конца периода входного сигнала может быть определе на путем фиксации.состояния выходов линии 10 задержки, на вход которой поступают импульсы от генератора опорной частоты, С выходов этой линии 10 снимаются импульсные последовательности, сдвинутые друг относительно друга на величину , . где га - величина задержки на каждой из секций линии 10. Поэтому, зафиксировав состояние выходов линии 10 задержкив какой-либо момент времени можно определить интервал времени от начала импульса, на первом выходе линии задержки до момента фиксации состояния выходов линии задержки. В начале следующего периода входного сигнала..импульсом с первого выхода блока 1 код счетчика 5 переписывается в регистр 2, состояние выходс в линии 10 задержки фиксируется в регистре,12, предыдущее значение кода регистра 12 переписывается в регистр 13, а также обнуляется сумматор 3. Состояние регистров 12 и 1J. в шифраторах 14 и 16 кодируется в двоичном коде, причем с выходово шифратора 14 снимается код Nj, а с выходов шифратора 16 снимается код, равный (N, - N) , Импульс с второгр выхода блока 1 обнуляет счетчик 5, заносит в старшие разряды сумматора 3 через группу элементов И 15 код J Na с выхода шифратора 14, а через элемент ИЛИ 4 поступает на управляющий вход счетчика 7 и заносит в него код N из старших разрядов регистра 2 N ГН fTjiL. -1 Ln J inToJ, где n - коэффициент умножения частоты. В сумматоре 3, общая емкость которого равна ntm, i находи ся код NWO -N3. После того, как на счетный вход счетчика 7 поступает N,( импульсов, код этого счетчика равняется нулю и на его выходе переполнения выработается сигнал, который через элемент ИЛИ 4 записывает .в счетчик 7 код N из регистра 2.. Кроме этого, сигнал с выхода переполнения счетчика 7 устанавливает в единичное состояние триггер 8 и поступает на вход управления суммированием, сумматора 3. При этом суммируются содер- . жимое сумматора 3 с/ г код Nj младших разрядов регистра 2 и выходной код (Ы Щ шифратора 16. После первого импульса на выходе переполнения счетчика 7 код сумматора 3 равен NCW NcMo+mN2+ (N 3-N4) nN ,+niN, +(N3 -N4) . После выполнения суммирования код сумматора 3 изменяется,а,следовательно, изменяется и импульсная последовательность на выходе мультиплексора 9, управляемого кодом старших разрядов сумматора Э, Первый импульс с выхода мультиплексора 9 устанавливает в нулевое состояние триггер 8, перепад напряжения на выходе которого выделяется дифференцирующим элементом 11 и поступает на выходную шину умножителя частоты, В дальнейшем цикл работы умножителя частоты повторяется. Импульс на выходе счетчика 7 появляется Через время , Так как происходит переключение импульсной последовательности, про.ходящей на выход мультиплексора 9, то к времени TQ добавляется соответствующий временной интервгш.и первый импульс на выходной шине умножителя частоты в момент времени равен t N Т SB: С rSfittJ. - Г NcAifi. N 1 о m VL n J L n J/. Соответственно, момент появления i-го импульса на выходе умножителя частоты определяется выражением t.MT..il. 1 1 о L п Jm Погрешность рассмотренного умножителя определяется суммой погрешности от дискретизации периода входного сигнала и погрешности от определения периода выходного сигнала. При этом погрешность от дискретизации периода входного сигнала в отличии от ноге не превосходит величины TO/I п. По скольку погрешность, от определения периода выходного сигнала у обоих устройств эквивалентна и не превышае величины Tolw; то точность рассматри ваемого устройства выше, чем у известного не менее чем в т/2 раз. Формула изобретения Умножитель частоты, содержащий блок синхронизации, подключенный вхо дом к шине- ввода умножаемой частоты первым выходом.- к управляющему вход первого регистра и к входу обнулени накапливающего сумматора а вторым выходом - к .первому входу элемента ИЛИ и к входу обнуления суммирующего счетчика, счетный вход которого соединен с выходом генератора опорной частоты, а выходы разрядов - с информационными входами первого регист ра, подключенного выходами старших разрядов к установочным входам вычитающего .счетчика, а выходами млада1их разрядов - к суммирующим вхо дам старших разрядов накапливающего сумматора, вход управления суммированием которого подключен к выходу переполнения вычитающего счетчика, второму входу элемента ИЛИ и к первому у;становочному входу триггера, соединенного вторым установочным входом с счетчным входом вычитающего счетчика и С выходом мультиплексора управляющие входы которого подключе ны к выходам старших разрядов накап ливающего сумматора, а информационные входы - к выходам линии задержки, соединенной входом с выходом генератора опорной частоты, причем выход .элемента ИЛИ подключен к входу управления установкой кода вычитающего счетчика, а выход триггера соединен через дифференцирующий элемент с выходной шиной умножителя частоты, отличающийся тем, что, с целью повышения точности умножения частоты за счет уменьшения погрешности от дискретизации периода входного сигнала, в умножитель частоты .дополнительно введены второй и третий регистры, шифраторы и группа элементов И,, подключенных первыми входами к выходам первого шифратора, вторыми входами - к второму выходу блока синхронизации,. а В1лходами к установочным, входам старших разрядов накапливающего сумматора, соединенного суммирующими входами младших разрядов с выходами второго шифратора, причем выходы линии задержки подключены к информационным входам второго регистра, соединенного выходами с входами первого шифратора и с информационными входами третьего регистра, а входы второго шифратора подключены к выходам второго и третьего регистров, соединенных управляющими входами с первым выходом блока синхронизации. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке 2510430/18-24, кл. G Об F 7/52, 1977. 2.Авторское свидетельство СССР по заявке 2552193/18-24, кл. G Об F 7/52, 1977. 3.Авторское свидетельство СССР по заявке 2693991/18-24, кл, G Об G 7/16, 1978 (прототип).

Авторы

Даты

1981-02-23—Публикация

1979-03-01—Подача