(54) УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь длительности импульсов | 1985 |

|

SU1307556A1 |

| Двоичный счетчик с обнаружением ошибок | 1984 |

|

SU1169163A1 |

| Устройство для контроля параметров | 1979 |

|

SU842721A1 |

| Устройство для контроля резервированного генератора | 1980 |

|

SU907887A1 |

| Устройство для контроля импульсных последовательностей | 1986 |

|

SU1338034A1 |

| Устройство для контроля продолжительности работы электродвигателя подъемно-транспортного средства | 1988 |

|

SU1608715A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

| @ -Разрядный счетчик с контролем | 1983 |

|

SU1138944A1 |

| Шифратор | 1985 |

|

SU1298802A2 |

1

Устройство задержки импульсов относится к импульсной технике и может быть использовано в устройствах вычислительной и измерительной техники.

Известны устройства задержки импульсов, которые осуществляют задержку импульсов с сохранением длительности импульсов 1.

Недостатком таких устройств является невозможность осуществлять задержку на величину, превышающую период следования импульсов.

Известны также устройства, содержащие задержку импульсов на величину, превышающую длительность серии входных импульсов 2.

Недостатком таких устройств является невозможность осуществления задержки на величину меньшую длительности серии входных импульсов. Кроме того,такие устройства имеют недостаточно высокую точность формирования задержки и длительности импульсов, которые определяются точностью цепочки последовательно срабатывающих аналоговых элементов задержки.

Наиболее близкими к предлагаемому являются устройства задержки, содержащие генератор импульсов, первый

элемент И, элемент задержки переднего фронта импульса, формирователь импульсов, первый N-разрядный счетчик импульсов, элементы И перезаписи,

5 второй N-разрядный счетчик импульсов, суммирующий триггер, триггер управления. Это устройство обеспечивает сдвиг импульсного сигнала со скважностью, равной двум. Для скважности

10 произвольно варьируемой в процессе работы (но постоянной в пределах пачки), удваивается число счетчиков З.

Недостатком известного устройства

15 регулируемой задержки импульсов является то, что оно обеспечивает временной сдвиг (задержку) только таких пачек импульсов, у которых скважность равна двум. При удвоении числа

20 счетчиков известное устройство сможет осуществлять задержку пачки импульсов с произвольной скважностью, но постоянной в пределах пачки. Таким образом, известное устройство мо2S жет осуществлять задержку таких пачек импульсов, в которых импульсы имеют одинаковую длительность и следуют с постоянным периодом. Задержку пачек, в которых импульсы имеют разную длительность и следуют с переменным периодом, известное устройство не обеспечивает.

Цель изобретения - расширение функциональных возможностей.

Указанная цель достигается тем, что в устройство задержки импульсов , содержащее генератор импульсов, подключенный к первому элементу И и к первому входу формирователя импульсов, первый N-разрядный счетчик импульсов, неразрядные -выходы которого соединены через соответствующие элементы И перезаписи с установочными входами второго М-разрядного счетчика импульсов, суммирующий триггер и триггер управления, выход которого соединен со вторым входом первого эле мента И, введены по N входных элементов И первой группы, входных элементов И второй группы, входных элементов И контроля нуля, выходных элементов И контроля нуля, установочних элементов И, М-1 элементов ИЛИ, N+1 выходной элемент И, N+1 дифференцирующая цепь, дополнительный элемент ИЛИ и дифференцирующая цепь, инвертор, формирователь сброса, (М+1)-разрядный регистр управления вычитанием и N-разрядный регистр управления сложением, поразрядные выходы которого подключены через соответствующие входные элементы И первой группы к поразрядным входам первого счетчика, нулевые входы триггеров регистра управления сложением подключены к первому выходу формирователя импульсов и ко BTopHBvj входам элементов И перезаписи, единичные входы триггеров со второго по Н-регистра управления сложением соединены с выходами установочных элементов И с первого по N-1 соответственно и с единичными вхо дами соответствующих разрядов со второго по М регистра управления вычитанием, единичный вход N+1 триггера регистра управления вычитанием соединен с выходом N-ro установочного элемента И, первые входы установочных зле.ментов И подключены к прямым выходам второго счетчика, инверсные выходы которого подключены к первым входам выходных элементов И контроля нуля н первым,входам входных элементов И контроля нуля, вторые входы которых с первого по N-1 соединены с выходами последу ощих элементов И контроля нуля и со вторыми входами соответствующих установочных элементов И, выход первого входного элемента И контроля нуля подключен к единичным входам первых разрядов регистров управления сложением и вычитанием,, второй вход N-ro входного элемента К контроля нуля соединен с вторым входом N-ro установочного элемента И, со входом установки в нуль первого счетчика, с единичным входом триггера упрвлёния и со вторым выходом формирователя импульсов, второй

вход которого подключен к выходу генератора, поразрядные входы второго счетчика подключены к выходам соответствующих входных элементов И второй группы, первые входы которых соединены с выходами регистра управлен вычитанием и с первыми входами выходных элементов И, вторые входы входных элементов И второй группы подключены к выходу первого элемента И и ко вторым входам входных элементов И первой группы, причем третьи входы входных элементов И второй группы подключены ко вторым входам выходньис элементов И и ко вторым входам выходных элементов И контроля нуля, кроме того, вышеупомянутые входы входных элементов И второй группы со второго по М подключены к выходам элементов И контроля нуля предыдудего разряда, а первого - к выходу элемента задержки переднего фронта импульса, выход Н-го выходного элемента И контроля нуля подключе к первому входу (N+l)-ro выходного элемента И и через дополнительную дифференцирующую цепь - к первому входу формирователя сброса и к нулевому входу триггера управления, при этом второй вход (N-fl)-ro выходного элемента И подключен к выходу (М4-1)-го триггера регистра управления вычитанием, единичный вход которого соединен с выходом N-ro установочного элемента И, выходы выходных элементов И через дифференцирующие цепи подключеныКО входам дополнительного элемента ИЛИ, кроме того, выходы дифференцирующих цепей со второго по N соединены с первыми входам элементов ИЛИ с первого по N-1 соответственно, вторые входы которых соединены с нулевыми входами триггеров со второго по N-регистра управления вычитанием, кроме того вторые входы элементов ИЛИ с первого по N-2 соединены с выходами элементов ИЛИ предьщщих разрядов, а второй вход N-1 элемента ИЛИ соединен с выходом N+l дифференцирующей цепи, при этом выход первого элемента ИЛИ соединен с нулевым входом первого разряда регистра управления вычитанием, выход дополнительного элемента ИЛИ подключен ко входу суммирующего триггера, инверсный выход которого соединен со вторш входом формирователя сброса, третий вход которого подключен через инвертор ко входу устройства.

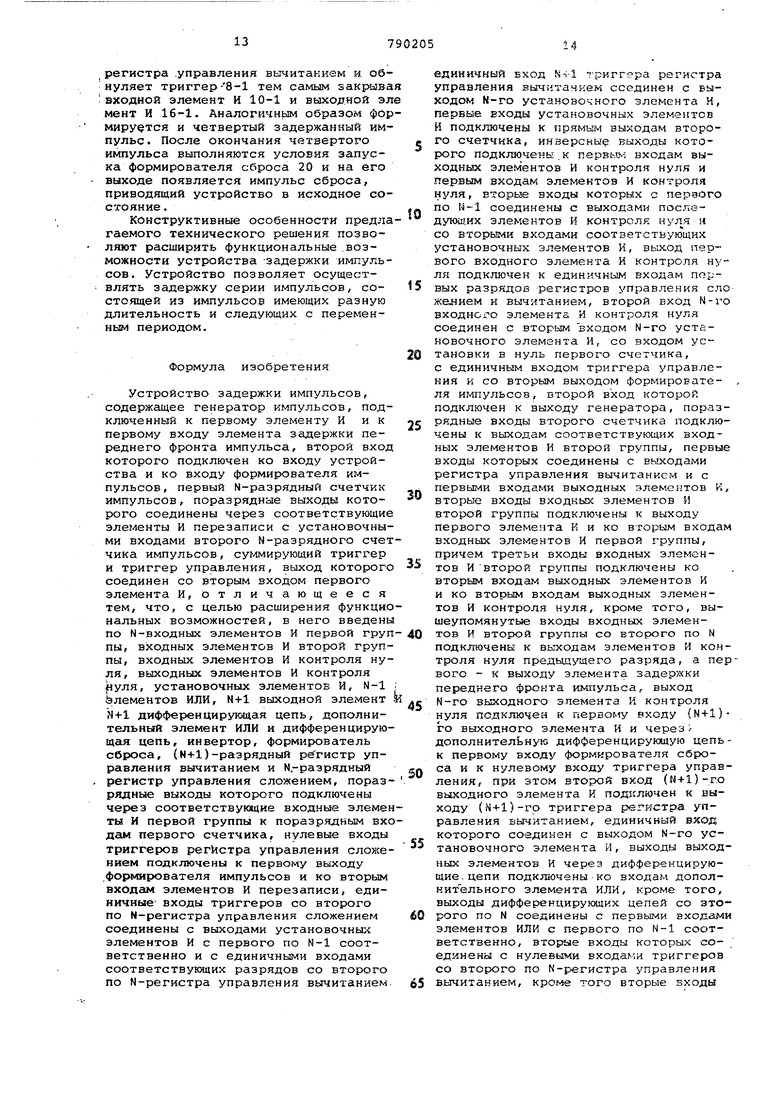

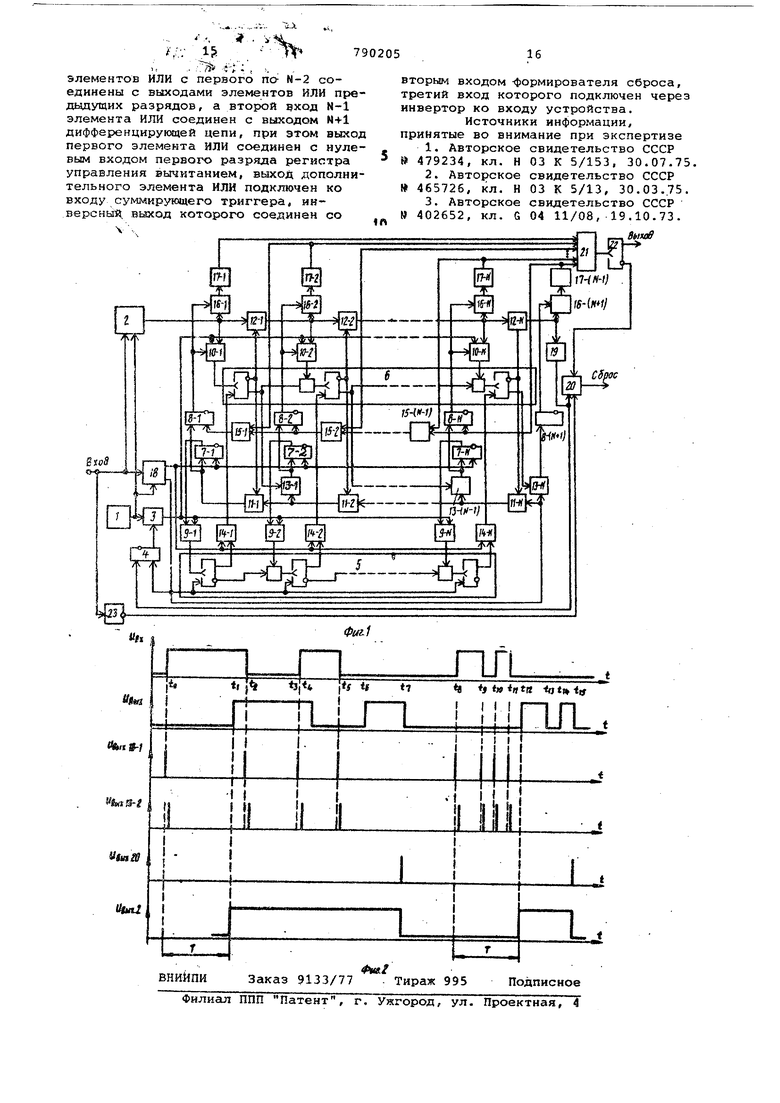

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - диаграмма работы устройства.

Устройство задержки импульсов содержит генератор 1 импульсов, элемент 2 задержки переднего фронта импульса, элемент И 3, триггер 4 управления, N-разрядные счетчики 5 и 6, триггеры 7-1 - 7-N регистра управления сложением, триггеры 8-1 - 8-{N+l) регистра управления вычитанием, вход ые элементы И 9-1 - 9-N первой груп) пы, входные элементы И 10-1 - 10-N второй группы, входные элементы И 11-1 - 11-N контроля нуля, выходные элементы И 12-1 -12-N контроля нуля, .установочные элементы И 13-1 - 13-N, элементы И 14-1 -14-N перезаписи, элементы ИЛИ 15-1 -15-N, выходные элементы И 16-1 - 16-(N+1), дифференцируэщие цепи 17-1 - 17-(N-f-l), формирователь 18 импульсов, дополнительную дифференциальную цепь 19, формирователь 20 импульсов сброса, дополнительный элемент ИЛИ 21, суммирующий триггер 22, инвертор 23. Выходы триггеров 7-1 - 7-N регистра управления сложением подключены через соответствующие входные элементы И 9-1 - 9-N первой группы к поразрядным входам первого счетчика 5, нулевые входы триггеров 7-1 - 7-N регистра управления сложением подключены к первому выходу формирователя 18 импульсов и ко вторым входам элементов И 14-1 -14-N перезаписи. Единичные входы триггеров 7-2 - 7-к регистра управления сложением соединены с выходами установочных элементов И 13-1 - 13-(N-1) соответственно и с единичными входами триггеров 8-2 -8регистра управления вычитанием. Единичный вход триггера 8-() регистра управления вычитанием соединен с выходом установочного элемента И 13Первые входы установочных элементов И 13-1 13-N подключены к прямым вых6дс1М триггеров 6 счетчика, инверсные выходы которых подключены к первым входам выходных элементов И 12-1 12-N контроля нуля и к первым входам входных элементов И 11-1 - 11-N контроля нуля. Вторые входы элементов И 11-1 - ll-(N-l) соединены с выходами последующих элементов И 11-2 11-N и со вторыми входами соответствующих установочных элементов И 13-1 - 13-(N-1). Выход элемента И 11-1 подключен к единичным входам триггеров 7-1 и 8-1 регистров управле ния сложением и вычитанием. Второй вход N-ro входного элемента И 11-N соединен с вторым входом Н-го установочного элемента И 13-М, со входом установки в нуль первого счетчика 5, с единичным входом триггера 4 управления и со вторым выходом формирователя 18 импульсов, второй вход которого подключен к выходу генератора 1 Поразрядные входы второго счетчика 6 подключены к выходам соответствующих входных элементов И 10-1 - 10-N, первые входы которых соединены с выходами триггеров 8-1 - 8-N регистра управления вычитанием и с первыми входа ми выходных элементов И 16-1 - 16-М, бторые входы входных элементов И И 10-1 - 10-Н подключены к выходу

элемента И 3 и ко вторым входам входных элементов И 9-1 9-N. Третьи входы входных элементов И 10-1 - 10-N подключены ко вторым входам выходных элементов И 16-1 - 16-Ми ко вторым входам выходных элементов И 12-1 -12-N контроля нуля, кроме того, вышеупомянутые входы входных элементов И 10-2 - 10-N подключены к выходам элементов И 12-1 - 12-К-1 предыдущего разряда, а первого входного

0 элемента И 10-1 к выходу элемента 2 задержки переднего фронта импульса. Выход N-ro выходного элемента. И 12 контроля нуля подключен к первому входу (N+l)-ro выходного элемента

S И 16-(N+1) и через дополнительную диффеоенциальную цепь 19 - к первому входу формирователя 20 импульсов сброса и к нулевому входу триггера 4 управления. Второй иход (N+1)-го выходного элемента И 16-(Nfl) подключен

0 к выходу триггера 8-(bi-i-11 регистра управления вычитанном, единичный вход которого соединен с выходом установочного элемента И I.l-N. Выходы выходных элементов И 16-1 - 16-fM+-lJ

5 через диффсренцирукхцие цепи 17-1 -17-{М+1) подключены ко входам дополнительного элемента ИЛИ 21. Кроме того, выходы дифференцирующих цепей 17-2 - 17- соединены с первы0ми входами элементов ИЛИ 15-1 15- (N-I) соответственно, вторые входы которых соединены с нулевыми входами триггеров 8-2 - 8-N регистра управления вычитанием. Кроме того вто5рые входы элементов ИЛИ 15-1 15- (м-2) соединены с вь/ходами элементов ИЛИ 15-2 15-(N-1) соответственно, а второй вход элемента ИЛИ 15-(N-l) соединен с выходом дифференцирующей цепи 17-(Н+1). Выход первого элемента ИЛИ 15-1 соединен с нулевым входом триггера 8-1 регистра управления вычитанием.

Выход дополнительного элемента ИЛ 21 подключен ко входу суммирую5щего триггера 22, инверсный выход которого соединен со вторым входом формирователя 20 импульсов сброса, третий вход которого подк.пючен через инвертор 23 ко входу устройства и к

0 Первому входу элемента 2 задержки переднего Фронта импульса. Второй вход элемента задержки переднего фронта импульса 2 подключен к выходу генератора 1 и к первому входу

5 элемента И 3, второй вхол которого соединен с выходом триггера 4 управления. Прямые выходы триггеров 5 перГвого счетчика чераз элементы И 14-1 - 14-N перезаписи соединены с установочными входами второго

0 счетчика б соответственно.

Примем состояние триггеров, при котором на прямом выходе разрешающий (высокий) потенциал, за единичное - 1, а состояние триггеров, при

s

котором на инверсном выходе разрешающий 3 высокий:} потенциал, за нулевое - О.

Устройство работает следующим образом.

В исходном состоянии счетчики 5 и б, триггеры 7-1 - 7-N и 8-1-8-(N+1 регистров управления сложением и вычитанием, а также триггер 4 управления и суммирующий триггер 22 находятся в нулевом состоянии. Элемент И 3 закрыт по второму входу низким потенциалом прямого выхода триггера 4 управления. Входные элементы И 9-1 -9первой группы закрыт низкими потенциалами выходов триггеров 7-1 - 7-N pervscTpa управления сложением. Входные элементы И 10-1 - 10-N второй группы и выходные элементы И 16-1 -16закрыт низкими потенциалами выходов триггеров 8-1 8-N регистра управления вычитанием, аэлемент И 1б-(ц+1) закрыт низким потенциалом выхода триггера 8-(М+1). Входные элементы И 11-1 - 11-N и выходные элементы И 12-1-- 12-N контроля нуля открыты по первым входам высокими потенциалами инверсных выходов разрядов счетчика 6, а по вторым входам закрыты низким потенциалом выхода элемента И контроля нуля преды,цущего разряда. Элемент И 12-1 закрыт низким потенциалом выкода элемента 2 задержки переднего фронта импульса. Установочные элементы И 13-1 - 13-N закрыты низким потенциалом прямых выходов триггеров соответствующих разрядов счетчика б. ЭлелДекты И 14-1 - 14-N перезаписи закрыты по первым входам низкими потенциалами прямых выходов счетчика 5.

По приколу серии импульсов, состоящей , напр1№дар из четырех импульсов, первым импульсом запускается элемент 2 задержки переднего фронта г2мпульса. По переднему фронту импульса на выходах формируются два коротких следующих друг за другом импульса {фиг. 2). При этом импульс с первого выхода формирователя 18 поступает на объединеннь входы элементов И 14-1 - 14-N перезаписи, закрытых по другим входам низкими потенциалами прямых вьаходов триггеров счетчика 5, и на нулевые входы триггеров 7-1 7-N регистра управления сложением, подтверждая нулевое состояние триггеров. Импульс со второго выхода формирователя 18 поступает на .установочные нулевые входы счетчика 5, подтверждая нулевое состояние, на единичный вход триггера 4 управления, устанавливая его в единичное состояние, и на входной элемент И 11-N контроля нуля, открывая последовательно элементы И 11 от М-го до первого. Кш1упъс с выхода элемента И 11-N устанавливает триггеры 7-1 и 8-1 в единичное состояние.При этом установочные элементы И 13 остаются эакрыты1 1И

по первым входам низкими потенциалами прямых выходов триггеров счетчика 6. Импульсы генератора 1 ПРОХОДЯТ через бткрытый высоким потенциалом прямого выхода триггера 4 управления элемент И 3 и черев открытый высоким потенциалом прямого выхода триггера 7-1 входной элемент и , на первый разряд счетчика 5, работающего в режиме сложения. Счетчик 5 заполняется импульсами генератора 1.

Спустя нео6ходк7«юе время сдвига, т.е. в момент времени t (фиг. 2) на выходе элемента 2 задержки появляется высокий потенциал, который проходит последовательно через открытые выходные элементы И 12-1 - 12-N контроля нуля на вход дифференцирующей цепи 19, с выхода которой короткий импульс поступает на нулевой вход триггера 4 управления, возвращая его в исходное состояние, при этом закрывается элемент И 3 и прекращается поступление импульсов генератора 1 на вход счетчика 5. Кроме того высокий потенциал выхода элемента задержки 2 открывает выходной элемент И 16-1, дифференцируется дифференцирующей цепью 17-1 и короткий импульс через дополнительный элемент ИЛИ 21 поступает на вход суммирующего триггера 22. Суммирующий триггер 22 уси на его прямом

танавливается в

выходе на выходе устройства) формируется передний фронт первого задер анного импульса серии. В таком со1::тоянии устройство находится до окончания первого входного импульса серии (момент времени t по диаграмме на фиг. 2).

По концу первого входного импульса серии на выходах формирователя 18 снова формируются два коротких импульса. При этом импульс с первого выхода формирователя 18, гюступая на нулевые входы триггеров 7-1 - 7-N регистра управления сложением, возвращает в исходное состояние триггер 7-1; и, поступая на вторые входы элементов И 14-1 - 14-Нперезаписи, переносит содержимое счетчика 5 в счетчик 6, Допустим, что старшим разрядом числа, записанного в счетчике 6 (находящимся в состоянии 1), будет i-ый разряд. Тогда высоким потенциалом прямого выхода i-го разряда счетчика 6 откроется по первому входу установочный элемент И 13i i+1 разряда, а низким потенциалом инверсного выхода триггера закроется входной Элемент И 11 контроля нуля i-го разряда. В результате этого закроются элементу И 11 всех предыдущих разрядов. Импульс со второго выхода формирователя 18 обнуляет счетчик 5, устанавливает в 1 триггер 4 и, проходя последовательно через элементы И 11-N, И ll-(N-l) и т.д., открывает элемент И ll-(i-«-l) выходной сигнал которого через установочный элемент .И 13 устанавливается в 1 триггеры 7-(i+l), 8-(i-H) регистров. При установке в 1 триггера 8-(i+l) открываются по первым входа 4 элементы И 10-{i+l) и И 16-(i+l), при установ ке в 1 триггера управления 4 откры вается элемент И 3, при установке в 1 триггера 7 открывается элемент И 9-{i+l) и и 1пульсы эталонной частоты с его выхода начинают поступать через соответствующий элемент ИЛИ счетчика 5 на вход триггера i+jL разряда счетчика 5. После открывания элемента И 3 импульсы эталонной частоты начинают поступать также через элемент И 10-1, открытый высоким потенциалом выхода триггера 8-1 и вы соким потенциалом выхода элемента 2 задержки, на вход счетчика 6, работающего в режиме вычитания. К приходу второго входного импульса серии в счетчике 5 записывается число с j+i по f разряд, соответствующее длительности паузы между первым и вторым импульсами серии. С приходом второго входного импульса (по переднему фронту импульса) формирователь 18 снова формирует два коротких импульса. Импульс с первого выхода формирователя 18, поступая на нулевые входы триггеров 7-1 - 7-N возвращает в исходное состояние триггер 7-(i+1), кроме того поступая на вторые входы элементов И 14-1 - 14-N перезаписи, переносит содержимое счетчика 5 (число, соответствующее паузе и находящееся с i+1 поj разряд счетчика 5) в счетчик 6. При этом число, соответствующее паузе, запишется соответственно с J+1 по разряд в счетчик 6. Тогда высоким потенциалом прямого выхода 1-го разряда счетчика 6 откроется по переднему входу установочный элемент И 13 J+1 разряда, а низким потенциалом инверсного выхода триггера закроется входной элемент И 11 j контроля нуля j-ro разряда. В резуль .тате этого закроются элементы И 11 всех предьшущих разрядов. Импульсы со второго выхода формирователя 18 обнуляет счетчик 5, подтверждает .единичное состояние триггера управления 4 и через элементы И ll-(j+l) и И 13-J устанавливает в 1 триггеры 7-(j-H), 8-(j+l), j+1 разряда. При этом открываиотся по первым входа рходной элемент И 10-(j+l) и выходно элемент И 16-(j+l) входной элемент и 9-(j+l) и импульсы опорной частот с его выходг ми начинают поступать че рез соответствующий элемент ИЛИ сче чика 5 на вход триггера j+1 разряда счетчика 5. в момент времени t(cM. диагрг1М му), что соответствует окончанию пе вого выходного импульса серии, все разряды с первого по i счетчика 6, работающего на вычитание, переходят в нулевое состояние и открывают инверсными выходами выходные элементы И 12-1 - 12-J контроля нуля. При этом открываются входной элемент И 10-(-(+1) выходной элемент И 16-(i+l) и на его выходе появляется высокий потенциал, который дифференцируется дифференцирующей цепью 17-(-)1). с выхода диф1 еренцирующей цепи 17- (I-fl) короткий импульс через дополнительный элемент ИЛИ 21 возвргцдает суммирующий триггер 22 в исходное состояние, формируя на его выходе задний фронт первого задержанного импульса, а через элементы ИЛИ 15 с J+1 по I первый поступает на нулевой вход триггера 8-1 регистра управления вычитанием и возвращает его в исходное состояние. Кмпульсы .опорной частоты с выхода элемента И 3 через открытый входной элемент И 10-(j4-l) начинает поступать через соответствующий элемент ИЛИ счетчика 6 на вход триг:гера j+1 разряда счетчика 6. Начинается вычитание числа, соответствующего паузе. К концу второго входного импульса серии (момент времени t на диаграмме) в счетчике 5 с j+1 по I разряд записывается число, соответствующее длительности второго входного импульса. По окончании второго входного импульса (по заднему фронту импульса) формирователь 18 вновь формирует два коротких импульса. Импульс с первого выхода формирователя 18, поступая на нулевые входы триггеров 7-1 - 7-N возвращает в исходное состояние триггер 7-(j+l), кроме того, поступая на вторые входы элементов И 14-1 - 14-N перезаписи, переносит содержимое счетчика 5 (число соответствующее длительности второго импульса и находящееся с j+l по t разряд в счетчике 5) в счетчик 6. При этом число в счетчик б запишется соответственно с J+1 по Е разряд. Тогда высоким потенциалом прямого выхода триггера 1-го разряда счетчика 6 откроется по первому входу установочный элемент И 13-1 1-4-1 разряда, а низким потенциалом инверсного выхода триггера закроется входной элемент И 11 С контроля нуля 1-го разряда. В результате этого ракроются элементы И 11 всех предьду щих разрядов. Импульс со второго выхода формирователя 18 обнуляет счетчик 5, подтверждает единичное состояние триггера управления 4 и через элементы И 11-(1+1) и И 13-Е устанавливает в 1 триггеры 7-( Е-ь) ,8-( f-H) . При этом открываются по первым входам входной элемент И lO-(f-H) и выходной элемент И 16-(В-И) входной элемент И 9-() и импульсы опорной частоты с его выхода начинают поступать через соответствующий элемент ИЛИ счетчика 5 на вход триггера 1+1 разряда счетчика 5.

В гломент времени t, что соответствует началу второго вьрсодного импульса серии, все разряды с i+1 по j счетчика б переходят в нулевое состояние и открывают инверсными выходаими соответствующие вьгходные элементы И 12 контроля нуля с i+1 по J, при этом открываются входной элемент И 10-(j4- 1), выходной элемент И ) И на его выходе появляется высокий потенциал, который дифференцируется дифференцирующей цепью 17-(J+1), С выхода лифференцирукйдей цепи 17-{J+1) короткий импульс через дополнительный элемент ИЛИ 21 устанавливает в 1 суммирующий триггер 22, формируя на его з йходе передний фронт второго задержаниогс импульса, а через элементы. ИЛИ 15 c(i + l): по j первый поступает на нулевые вхо ды соогаетствующих триггеров 8 и возвращает триггер 8- (i+1) в исходное состояние. Импульсы опорной частоты с выхода элемента И 3 через открытый вхолной элемент И 10-(j+l) начинаютпоступат{з через соответствующий элемент ИЛИ счетчика б на вход триггера J+1 разряда счетчика 6 Начинается вычитание числа, соответствующего длительности второго импульса.

В момент времени, t, что соответствует окончанию второго выходного импульса серии, все разряды с j 4-1 по & счетчика 6 переходят в нулевое состояние и открывают икверсныз ш выходами соответствующие выходные, элементы И 12 контроля нуля с j-t-1 по I При этом открываются входной элемент И 10-(С+1/, выходной элемент И 16- (f+1 ) и на его выходе появляется высокий потенциал, который дифференцируется дифференцирующей цепью 17(S -f-1). С выхода дифференцирующей цепи 17() короткий импульс через дополнительный элемент ИЛИ 21 возвращает суммирующий триггер 22 в исходное состояние, формируя задний фронт второго задержанного импульса, а через элементы ИЛИ 15 с j-fl по t перэый поступает на нулевые входы соответствующих триггеров 8 и возвращает риггер 8-(j+l) в исходное состояние Кроме того, так как счетчик б полностью обнуляется, то инверсные выходы его открывают соответствующие выходные элементы И 12 контроля нуля с первого по W. На выходе элемента И 12-N контроля нуля появляется высокий потенциал, который дифференцирует дифференцирующей цепью 19. Импульс с выхода дифференцирующей цепи 19 поступает на вход формирователя импульсов сбрюса 20, открытого по другим входам высоким потенциалом инверюного выхода суммирующего триггера 22 и высоким потенциалом выхода инвертора 23. Выходной импульс формирователя 20 устанавливает все элементы схемы в исходное состояние (момент времени t7 на диаграмме, фиг.2). С момента времени t по tg устройство находится в исходном состоянии.

В момент времени tg происходит третий импульс серии, по которому вновь запускается элемент 2 задержки переднего фронта импульса. По переднему фронту третьего импульса на выходах формирователя 18 снова формируется два коротких следующих друг за другом импульса. Импульсом со второго выхода взводится триггер 4 управления и в триггеры 7-1 и 8-1 через элементы 11-N - 11-1 записывается 1 при этом в счетчике 5 с момента времени tg по t записывается число, с первого по in разряц счетчика 5, соответствунйцее длительности третьего импульса. По концу третьего импульса число из счетчика 5 переписывается в счётчик 6, обнуляются триггер 7-1 и счетчик 5 и записывается 1 в триггера 7-(п4-1) и 8-(т+1) и т.д.

Таким образом, после окончания четвертого импульса в счетчик 6 с первого по m разряд записывается число, соответствуккдее длительности третьего импульса, с т+1 по разряд Записывается число соответствующее паузе между третьим и четвертым импульсами, с Р+1 по г разряд записывается число, соответствуклцее длительности четвертого импульса. Соответственно записывается 1 в

96-(р+1), 7-(г+1) , 8-{r-t-l) триггеры. Спустя необходимое время сдвига Т, т.е. в момент t,j на выходе элемента 2 задержки появляется высокий потенциал, который открывает входной элемент И 10-1 и выходной элемент И 16-1 дифференцируется дифференцирующей цепью 17-1 и через дополнительный элемент ИЛИ 21 поступает на счетный вход суммирующего триггера 22, на выходе которого появляется высокий потенциал задержанного третьего импУльса. Кроме того, через Открытый входной элемент И 10-1 на Ьход-счетчика 6 поступают импульсы счета. После вычета из счетчика б числа импульсов, соответствующего дл тельности третьего импульса открываются выходные элементы И 12 с первого по m разряд. При этом открываются входной элемент И 10-{m-fl) и выходно элемент И 16-(т-И), на выходе которого появляется высокий потенциал,поступающий на вход дифференцирующей цепи 17-(т+1). Короткий импульс РЫХОда дифференцирующей цепи 17-(тч-1) через дополнительный элемент ИЛИ 21 поступает на счетный вход суммирующего триггера 22 и возвращает его в исходное состояние, кроме того коре; кий импульс выхода дифференцирующей цепи 17-() через элементы ИЛИ 15 с п по первый поступают на нулевые входы соответствующих триггеров 8 регистра .управления вычитанием и об- нуляет триггер-8-1 тем самым закрыва входной элемент И 10-1 и вьаходной эл мент И 16-1. Аналогичным образом фор мируется и четвертый задержанный импульс. После окончания четвертого импульса выполняются условия запуска формирователя сброса 20 и на его выходе появляется импульс сброса, приводящий устройство в исходное состояние. конструктивные особенности предла гаемого технического решения позволяют расширить функциональные .возможности устройства -задержки импульсов. Устройство позволяет осуществлять задержку серии импульсов, состоящей из импульсов имеющих разную длительность и следующих с переменным периодом. Формула изобретения Устройство задержки импульсов, содерж 1щее генератор импульсов, подключенный к первому элементу И и к первому входу элемента задержки переднего фронта импульса, второй вход которого подключен ко входу устройства и ко входу формирователя импульсов, первый М-разрядный счетчкк импульсов, поразрядные выходы которого соединены через соответствующие элементы И перезаписи с установочными входами второго N-разрядного счет чика импульсов, суг мирующий триггер и триггер управления, выход которого соединен со вторым входом первого элемента И, отличающееся тем, что, с целью расширения функцио нальных возможностей, в него введены по N-входных элементов И первой груп пы, входных элементов И второй группы, входных элементов И контроля нуля, выходных элементов И контроля нуля, установочных элементов И, N-1 ёлементов ИЛИ, N+1 выходной элемент N+1 дифференцирующая цепь, дополнительный элемент ИЛИ и дифференцирую цепь, инвертор, формирователь сброса, (N4-1)-разрядный рбгистр управления вычитанием и N-разрядный регистр управления сложением, пораз рядные выходы которого подключены через соответствующие входные элеме ты И первой группы к поразрядным вх дам первого счетчика, нулевые входы триггеров регистра управления сложе нием подключены к первому выходу .формирователя импульсов и ко вторым входам элементов И перезаписи, единичные входы триггеров со второго по N-регистра управления сложением соединены с выходами установочных элементов И с первого по N-1 соответственно и с единичными входами соответствующих разрядов со второго по N-регистра управления вычитанием единичный вход триггера регистра управления вычнтанкем соединен с выходом Н-го установочного элемента И, первые входы установочных элементов И подключены к пряь-адм выходам второго счетчика, инверсны выходы которого подключены .к первь -; входам выходных элементов И контроля нуля и первьаи входам элементов И контроля нуля, вторые входы которых с первого по Н-1 соединены с выходами посяедьпощих элементов И КОНТРОЛЕ нул.я и со вторыми входами соответствующих установочных элементов И, выход первого входного элемента И контроля нуля подключен к единичным входам первых разрядов регистров управления ело желием и вычитанием, второй вход N-ro входного элемента И контроля нуля соединен с вторым входом N-ro установочного элемента И, со входом установки в нуль первого счетчика, с единичным входом триггера управления и со вторым выходом формирователя импульсов, второй вход которой подключен к выходу генератора, поразрядные входы второго счетчика подключены к выходам соответствующих входных элементов И второй группы, первые входы которых соединены с выходами регистра управления вычитанием и с первыми входами выходных элементов К, вторьте входы входных элементов И второй группы подключены к выходу первого элемента И и ко вторым входам входных элементов И первой группы, причем третьи входы входных элементов И второй группы подключены ко вторым входс м выходных элементов И и ко вторым входам выходных элементов И контроля нуля, кроме того, вышеупомянутые входы входных элементов И второй группы со второго по N подключены к выходам элементов И контроля нуля предыдущего разряда, а первого - к выходу элемента задержки переднего фронта импульса, выход N-ro выходного э.пемента И контроля нуля подключен к первому входу {N+1)го выходного элемента И и через .дополнительную дифференцирующую цепьк первому входу формирователя сброса и к нулевому входу триггера управления, при этом второй вход (N-M)-ro выходного элемента К подключен к выходу {N-fl)-rp триггера регистра управления вычитанием, единичный вход которого соединен с выходом N-ro установочного элемента И, выходы выходных элементов И через дифференцирующие, цепи подключены ко входам дополнительного элемента ИЛИ, кроме того, выходы дифференцирующих цепей со второго по N соединены с первыми входами элементов ИЛИ с первого по N-1 соответственно, вторые входы которых соединены с нулевыми входами триггеров со второго по N-регистра управления вычитанием, кроме того вторые входы .. . , элементов ИЛИ с первого по- N-2 соединены с выходами элементов ИЛИ предьадущих разрядов, а второй эход N-1 элемента ИЛИ соединен с выходом N+1 диФФеренцирукхцей цепи, при этом выход первого элемента ИЛИ соединен с нулевым входом первого разряда регистра управления вычитанием, выход дополнительного элемента ИЛИ подключен ко входу суммирующего триггера, инверсный, выход которого соединен со 79 орым входом -формирователя сброса, етий вход которого подключен через вертор ко входу устройства. Источники информации, инятые во внимание при экспертизе 1.Авторское свидетельство СССР 479234, кл. Н 03 К 5/153, 30.07.75. 2.Авторское свидетельство СССР 465726, кл. Н 03 К 5/13, 30,03.75. 3.Авторское свидетельство СССР 402652, кл. G 04 11/08, 19.10.73.

Авторы

Даты

1980-12-23—Публикация

1978-06-02—Подача