1

Изобретение относится к автоматике, а именно к автоматизированным системам регулирования с цифровым управлением, и может найти применение в системах регулирования скорости вращения и положения различных механизмов .

Цель изобретения - новьпиение быстродействия и точности регулирования.

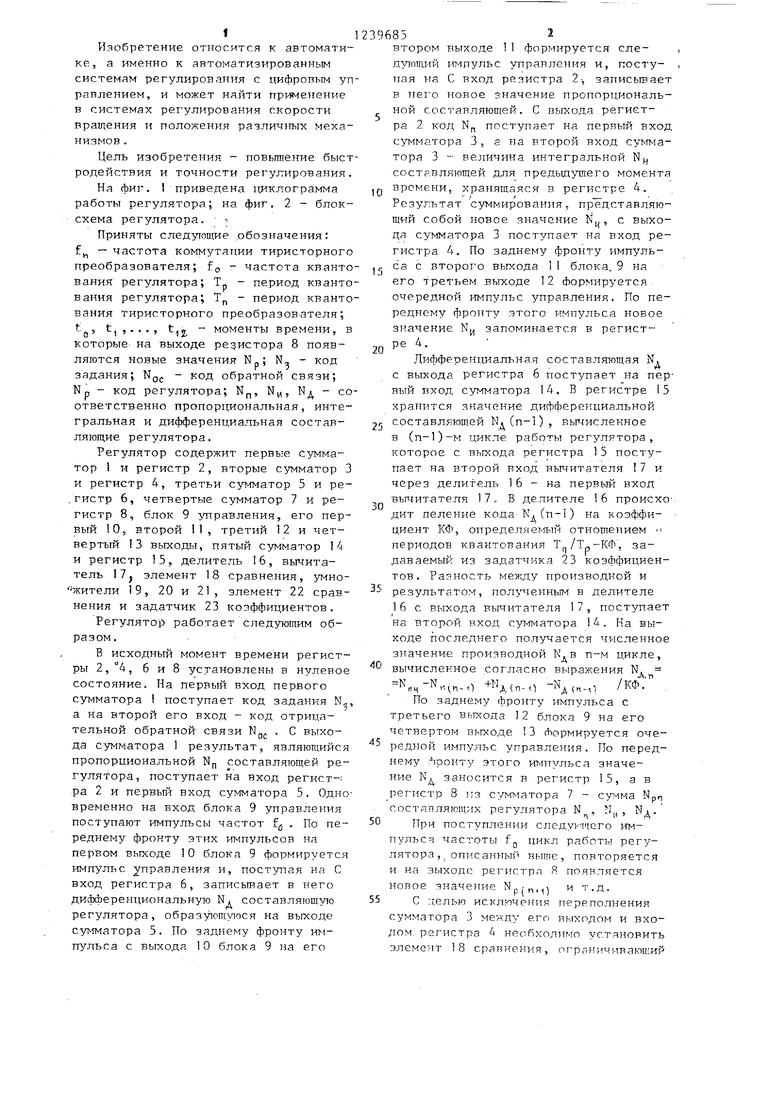

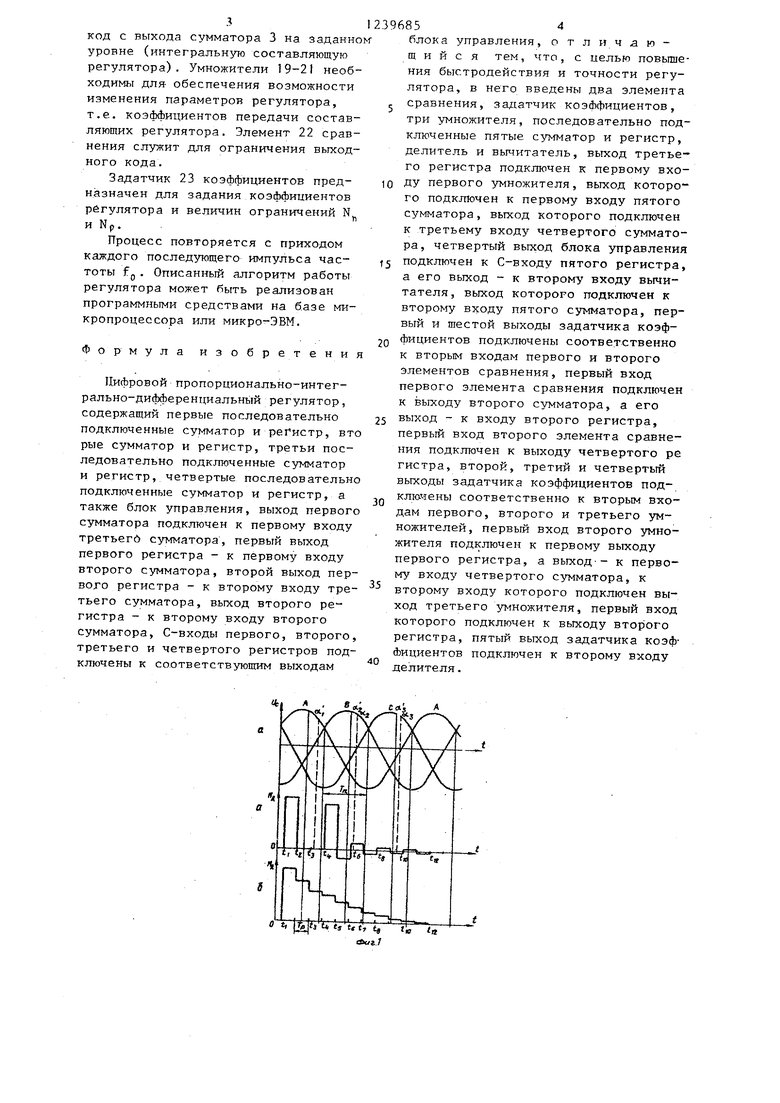

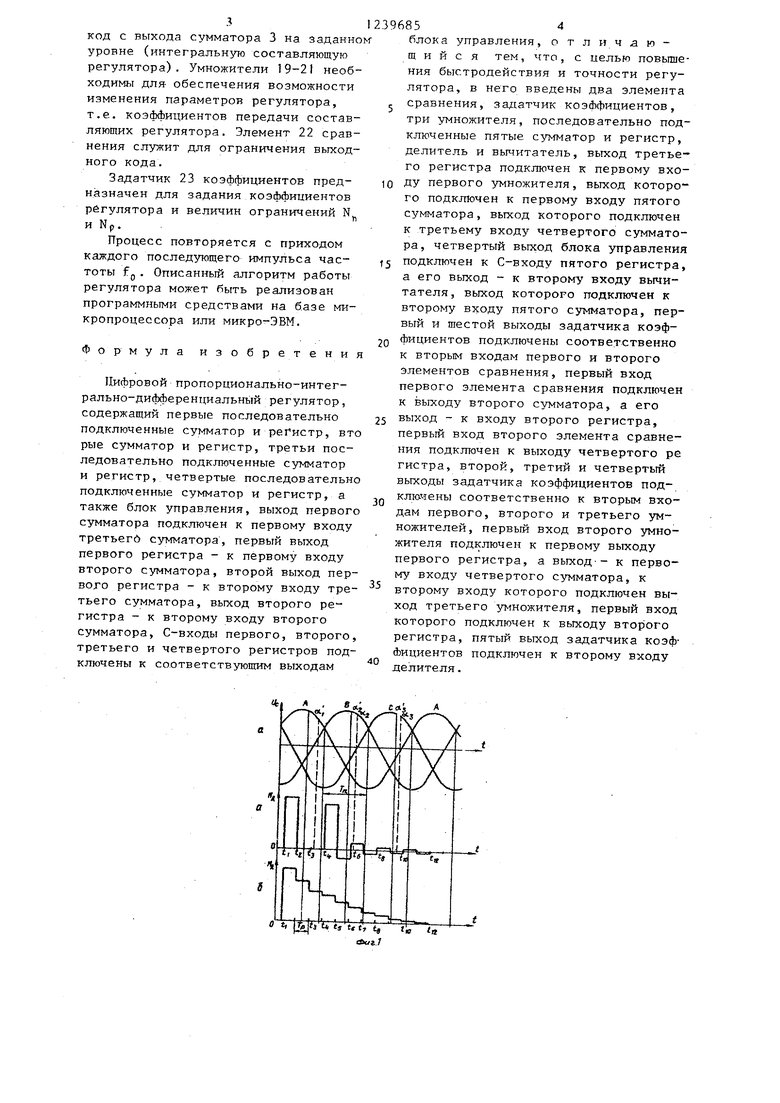

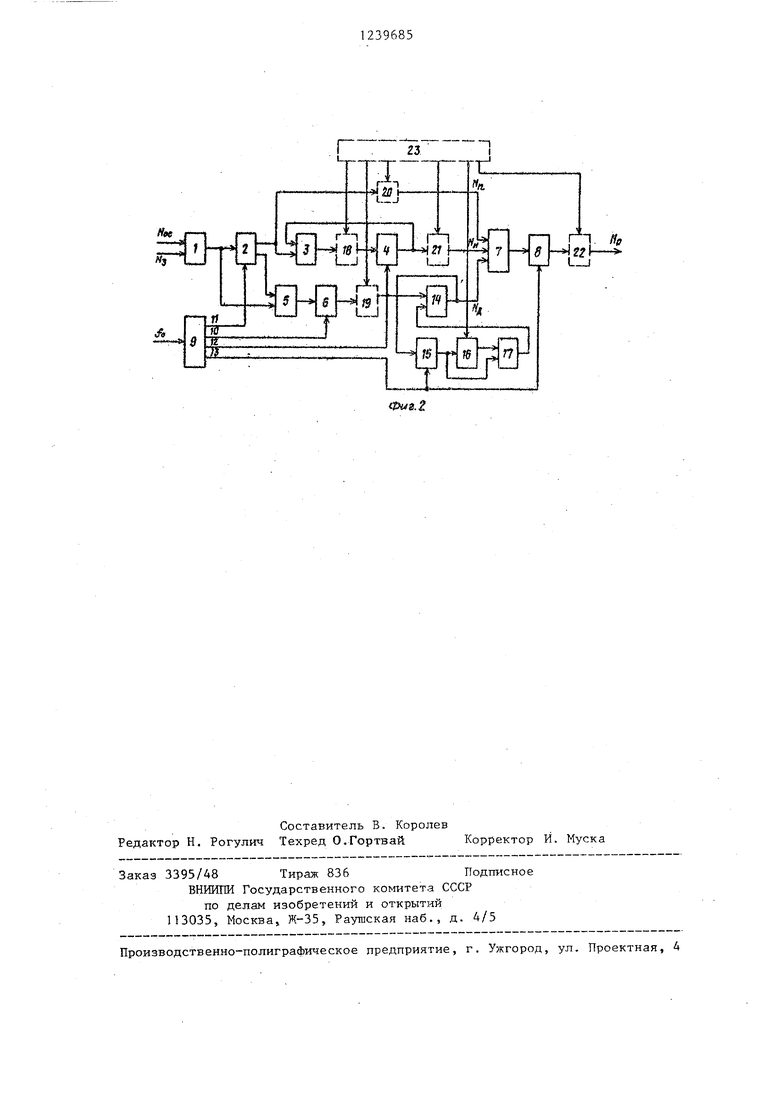

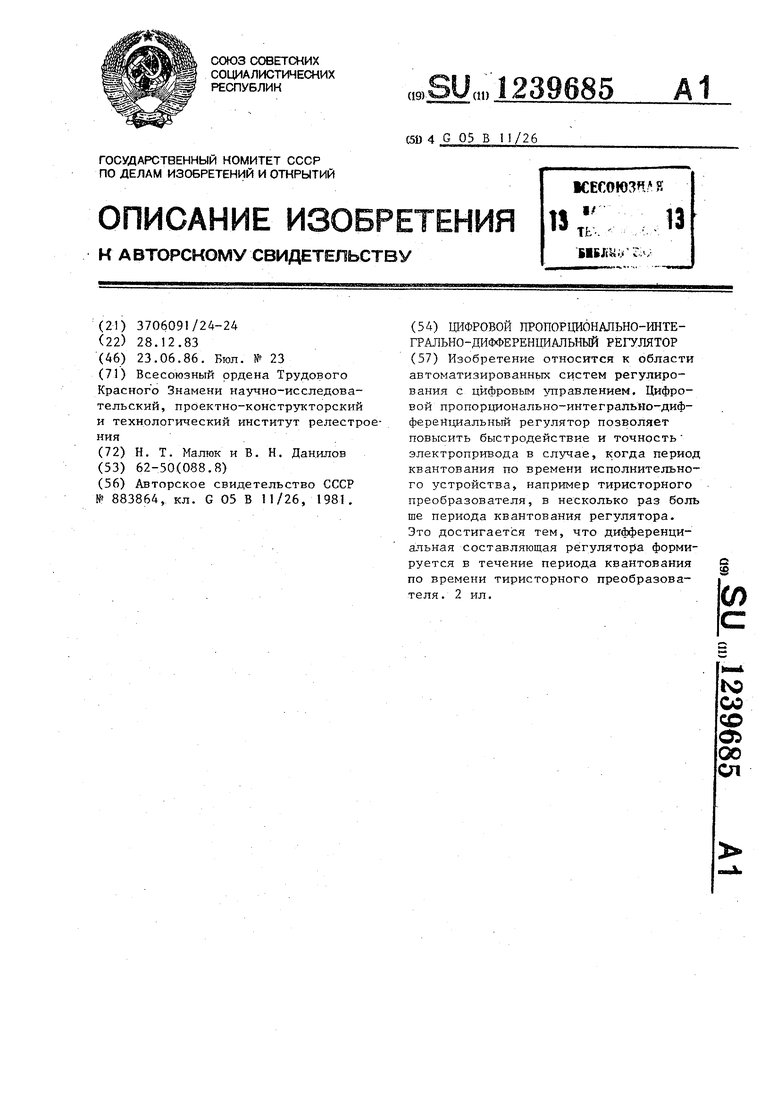

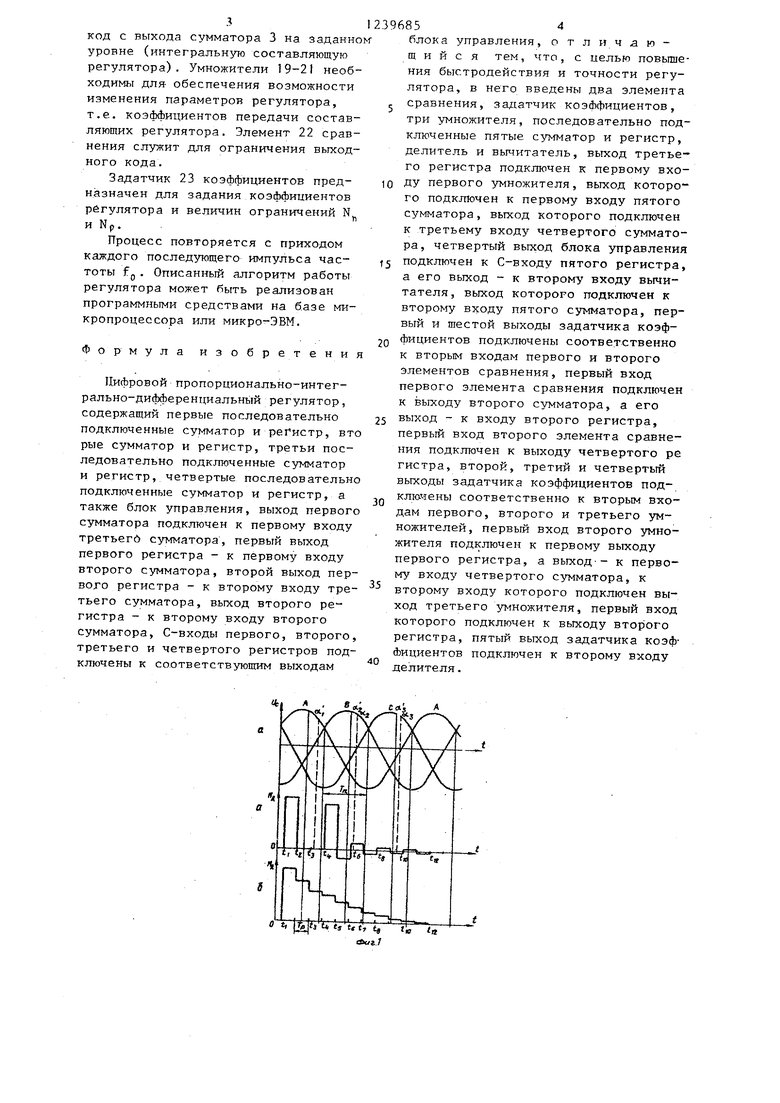

На фиг. 1 приведена циклограмма работы регулятора; на фиг. 2 - блок- схема регулятора. .

Приняты следующие .обозначения: fj - частота коммутании тиристорного преобразователя; fj, - частота квантования регулятора; Т- - период квантования регулятора; Т - период квантования тиристорного преобразователя; t , t ,..., -- моменты времени, в которые на выходе резистора 8 появляются новые значения N-; N - код задания; Ng,, - код обратной связи; NP код регулятора; N, N,, Нд - соответственно пропорциональная, интегральная и дифференциальная составляющие регулятора.

Регулятор содержит первьзе сумматор 1 и регистр 2, вторые сумматор 3 и регистр 4, третьи сумматор 5 и ре- .гистр 6, четвертые сумматор 7 и регистр 8, блок 9 ллтравления, его первый 10, второй 11 , третий 12 и четвертый 13 выходы, пятый сумматор 14 и регистр 15, делитель 16, вычита- тель I7j элемент 18 сравнения, умно- жители 19, 20 и 21 , элемент 22 сравнения и задатчик 23 коэффициентов.

Регулятор работает следующим образом.

В исходный момент времени регистры 2 , 4 , 6 и 8 установлены в нулевое состояние. На первый вход первого сумматора поступает код задания М, а на второй его вход - код отрицательной обратной связи Ng . С выхода С умматора 1 результат, являющийся пропорциональной Np составляющей регулятора, поступает на вход регист-; ра 2 и первый вход сумматора 5. Одновременно на вход блока 9 управления поступают импульсы частот f, . По переднему фронту этих импульсов на первом выходе 10 блока 9 формируется импульс управления и, поступая на С вход регистра 6, записьгоает в него дифференциональнуто Нд составляюпхую регулятора, образуют тася на выходе сумматора 5. По заднему фронту пульса с выхода 10 блока 9 на его

5

20

396852

втором выходе 11 формируется сле- дутотций импульс управления и, поступая 1га С вход резистра 2-, записывает в него новое значение пропорциональной составляющей. С выхода регистра 2 код N поступает на первый вход сумматора 3, а на второй вход сумматора 3 - величина интегральной N составляющей для предыдущего момента

д времени, хранящаяся в регистре 4. Результат суммир ования, пр1 дставляю- щий собой новое значение N, с выхода сумматора 3 поступает на вход регистра 4. По заднему фронту импуль,г са с BTopoi o выхода 1 1 блока. 9 на его третьем выходе 12 формируется очередной импульс управления. По пе- редршму фронту этого импульса новое значение N запоминается в регистре 4.

Дифференциальная составляющая N. с выхода регистра 6 поступает на первый вход сумматора 14, В регистре 15 хратп1тся значение дифференциальной

2J составляющей 1-1 (п-1) , вычисленное в (n-l)-M цикле работы регулятора, которое с выхода регистра 15 поступает на второй вход вычитателя 17 и через дели-гель 1 6 - на первый вход вычитателя 17. В делителе 16 происходит деление кода-1 д(п-1) на коэффициент КФ, определяемый отношением периодов квантования Т /Тр--КФ , задаваемый из задатчика 23 коэффициентов. Разность между производной и

результатом, пол 11енным в делителе 16 с выхода вычитателя 17, поступает на второй вход cyi- iaTopa i4. На ходе последнего получается численное значение; производной N. в п-м цикле,

вычисленное согласно вырал :ения N N«H-N,,.,, (п-,1 -N,„-,1 /Кф . .

По заднему фронту 1-гмпульса с третьего выхода 12 блока 9 на его четвертом выходе 13 Нормируется оче 5 редной импульс управления. По переднему r lpoHTy этого импульса значение Кд заносится в регистр 15, а в регистр 8 с: тчматора 7 - сутмма Np

. составляющих регулятора N, N,, , N.

50 При поступлении следур-щего им- пульсч частоты fg цикл работы регулятора ,, описанный вьппе, повторяется и на выходе регистра Я появляется

30

новое значение Np/f и т.д. 55 С ::7,елью исключешш переполнения сумматора 3 ме-дду его выходом и входом регистра 4 необходимо установить элемент 18 сравнения, (-)г-рлнич.1вающий

код с выхода сумматора 3 на заданнок уровне (интегральную составляющую регулятора). Умножители 19-21 необходимы для обеспечения возможности изменения параметров регулятора, т.е. коэффициентов передачи составляющих регулятора. Элемент 22 сравнения служит для ограничения выходного кода.

Задатчик 23 коэффициентов предназначен для задания коэффициентов регулятора и величин ограничений N и Np.

Процесс повторяется с приходом каждого последующего импульса частоты fp. Описанный алгоритм работы регулятора может быть реализован программными средствами на базе микропроцессора или микро-ЭВМ.

Формула изобретения

Цифровой пропорционально-интегрально-дифференциальный регулятор, содержащий первые последовательно подключенные сумматор и регистр, вто рые сумматор и регистр, третьи последовательно подключенные сумматор и регистр, четвертые последовательно подключенные су1 матор и регистр, а также блок управления, выход первого сумматора подключен к первому входу третьего сумматора, первый выход первого регистра - к первому входу второго сумматора, второй выход первого регистра - к второму входу третьего сумматора, выход второго регистра - к второму входу второго сумматора, С-входы первого, второго, третьего и четвертого регистров подключены к соответствующим выходам

239685

, 10

t5

20

25

30

35

40

блока управления, отличающийся тем, что, с целью повышения быстродействия и точности регулятора, в него введены два элемента сравнения, задатчик коэффициентов, три умножителя, последовательно подключенные пятые сумматор и регистр, делитель и вычитатель, выход третьего регистра подключен к первому входу первого умножителя, выход которого подключен к первому входу пятого сумматора, выход которого подключен к третьему входу четвертого сумматора, четвертый выход блока управления подключен к С-входу пятого регистра, а его выход - к второму входу вычи- тателя, выход которого подключен к второму входу пятого сумматора, первый и шестой выходы задатчика коэффициентов подключены соответственно к вторым входам первого и второго элементов сравнения, первый вход первого элемента сравнения подключен к выходу второго сумматора, а его выход - к входу второго регистра, первый вход второго элемента сравнения подключен к выходу четвертого ре гистра, второй, третий и четвертый выходы задатчика коэффициентов подключены соответственно к вторым входам первого, второго и третьего умножителей, первый вход второго умножителя подключен к первому выходу первого регистра, а выход-- к первому входу четвертого сумматора, к второму входу которого подключен выход третьего у 1ножителя, первый вход которого подключен к выходу второго регистра, пятый выход задатчика коэффициентов подключен к второму входу делителя.

о t, tiU «5 ttt, tf ta t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля аналого-цифровых преобразователей | 1988 |

|

SU1711327A1 |

| Устройство для регулирования температуры | 1985 |

|

SU1335950A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ДАВЛЕНИЯ | 1992 |

|

RU2072548C1 |

| Устройство для регулирования давления | 1988 |

|

SU1674075A1 |

| Установка для присоединения проволочных выводов | 1988 |

|

SU1549698A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| СПОСОБ РЕГУЛИРОВАНИЯ ЖИДКОСТНОГО РАКЕТНОГО ДВИГАТЕЛЯ И УСТРОЙСТВА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2085755C1 |

| Система адаптивного управления параметром технологического процесса | 1988 |

|

SU1620989A1 |

| РАДИАЦИОННЫЙ ТОЛЩИНОМЕР ПОКРЫТИЙ | 1988 |

|

SU1805736A1 |

| РАДИОИЗОТОПНЫЙ ТОЛЩИНОМЕР | 1992 |

|

RU2116620C1 |

Изобретение относится к области автоматизированньгх систем регулирования с цйфровь управлением. Цифровой пропорционально-интегрально-диф- фереНциальный регулятор позволяет повысить быстродействие и точность электропривода в случае, когда период квантования по времени исполнительного устройства, например тиристорного преобразователя, в несколько раз боль ше периода квантования регулятора. Это достигается тем, что дифференциальная составляющая регулятора формируется в течение периода квантования по времени тиристорного преобразователя. 2 ил. С $ (Л IN5 СО х Oi 00 СП

| Цифровой пропорционально-интегрально-дифференциальный регулятор | 1979 |

|

SU883864A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-06-23—Публикация

1983-12-28—Подача